KR20080098368A - 다양한 메사 치수를 갖는 높은 셀 밀도의 트랜치 모스펫 - Google Patents

다양한 메사 치수를 갖는 높은 셀 밀도의 트랜치 모스펫 Download PDFInfo

- Publication number

- KR20080098368A KR20080098368A KR1020087019275A KR20087019275A KR20080098368A KR 20080098368 A KR20080098368 A KR 20080098368A KR 1020087019275 A KR1020087019275 A KR 1020087019275A KR 20087019275 A KR20087019275 A KR 20087019275A KR 20080098368 A KR20080098368 A KR 20080098368A

- Authority

- KR

- South Korea

- Prior art keywords

- cells

- cell

- trench gate

- trench

- width

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/668—Vertical DMOS [VDMOS] FETs having trench gate electrodes, e.g. UMOS transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P10/00—Bonding of wafers, substrates or parts of devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/01—Manufacture or treatment

- H10D12/031—Manufacture or treatment of IGBTs

- H10D12/032—Manufacture or treatment of IGBTs of vertical IGBTs

- H10D12/038—Manufacture or treatment of IGBTs of vertical IGBTs having a recessed gate, e.g. trench-gate IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/411—Insulated-gate bipolar transistors [IGBT]

- H10D12/441—Vertical IGBTs

- H10D12/461—Vertical IGBTs having non-planar surfaces, e.g. having trenches, recesses or pillars in the surfaces of the emitter, base or collector regions

- H10D12/481—Vertical IGBTs having non-planar surfaces, e.g. having trenches, recesses or pillars in the surfaces of the emitter, base or collector regions having gate structures on slanted surfaces, on vertical surfaces, or in grooves, e.g. trench gate IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

- H10D30/0295—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs using recessing of the source electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

- H10D30/0297—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs using recessing of the gate electrodes, e.g. to form trench gate electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/101—Integrated devices comprising main components and built-in components, e.g. IGBT having built-in freewheel diode

- H10D84/141—VDMOS having built-in components

- H10D84/148—VDMOS having built-in components the built-in components being breakdown diodes, e.g. Zener diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/512—Disposition of the gate electrodes, e.g. buried gates

- H10D64/513—Disposition of the gate electrodes, e.g. buried gates within recesses in the substrate, e.g. trench gates, groove gates or buried gates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/517—Gate electrodes for field-effect devices for FETs for IGFETs characterised by the conducting layers

Landscapes

- Electrodes Of Semiconductors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

Description

Claims (20)

- 트랜치 게이트 전력 모스펫(trench-gate power MOSFET) 디바이스에 있어서,고농도 본체 식각을 이용하여 형성된, 제1 셀 피치(pitch)를 갖는 복수의 제1 셀; 및상기 고농도 본체 식각을 이용하지 않고 형성된, 상기 제1 셀 피치보다 폭이 좁은 제2 셀 피치를 갖는 복수의 제2 셀을 포함하는 트랜치 게이트 전력 모스펫 디바이스.

- 제1항에 있어서,상기 복수의 제1 셀에 대한 본체-다이오드 간 항복 전압을 제어하기 위하여 상기 고농도 본체 식각이 이용되는 트랜치 게이트 전력 모스펫 디바이스.

- 제1항에 있어서,상기 복수의 제1 셀에 대한 본체-다이오드 간 항복 전압을 제어하기 위하여 트랜치의 폭이 이용되는 트랜치 게이트 전력 모스펫 디바이스.

- 제1항에 있어서,상기 복수의 제1 셀 내의 셀의 개수를 정하기 위하여 원하는 턴-오프 전류 사양(turn off current specification)이 이용되는 트랜치 게이트 전력 모스펫 디바이스.

- 제4항에 있어서,상기 복수의 제2 셀 내의 셀의 개수를 정하기 위하여 원하는 온 저항(on resistance)이 이용되는 트랜치 게이트 전력 모스펫 디바이스.

- 제1항에 있어서,상기 제2 피치는 최소 설계 규칙(minimum design rules)에 의해 정해지는 트랜치 게이트 전력 모스펫 디바이스.

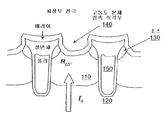

- 트랜치 게이트 전력 모스펫 디바이스에 있어서,제1 트랜치 게이트;상기 제1 트랜치 게이트로부터 제1 거리에 놓인 제2 트랜치 게이트;상기 제2 트랜치 게이트로부터 제2 거리에 놓인 제3 트랜치 게이트;제1 웰을 포함하고 상기 제1 트랜치 게이트와 상기 제2 트랜치 게이트 사이에 위치된 제1 본체 영역; 및제2 웰을 포함하고 상기 제2 트랜치 게이트와 상기 제3 트랜치 게이트 사이에 위치된 제2 본체 영역을 포함하되,상기 제1 본체 영역은, 상기 제2 본체 영역보다 낮은 핀치 베이스(pinched-base) 저항과 상기 제2 본체 영역보다 낮은 드레인-벌크 간(drain-to-bulk) 항복 전압을 갖도록 처리되고,상기 제1 거리는 상기 제2 거리보다 큰 값을 갖는 트랜치 게이트 전력 모스펫 디바이스.

- 제7항에 있어서,상기 제1 본체 영역은 고농도 본체 식각을 이용하여 처리되는 트랜치 게이트 전력 모스펫 디바이스.

- 트랜치 게이트 전력 모스펫 디바이스를 제조하는 방법에 있어서,드레인-벌크 간 항복 사양(specification)을 이용하여 폭이 넓은 셀의 폭을 정하는 단계;상기 드레인-벌크 간 항복 사양을 이용하여 폭이 넓은 셀에 대한 트랜치 게 이트의 제1 폭을 정하는 단계;전자 사태(avalanche) 전류 사양을 이용하여 폭이 넓은 셀의 개수인 제1 개수를 정하는 단계;설계 규칙 제한(design rule limitations)을 이용하여 폭이 좁은 셀의 폭을 정하는 단계; 및온 저항 사양을 이용하여 폭이 좁은 셀의 개수인 제2 개수를 정하는 단계를 포함하는 트랜치 게이트 전력 모스펫 디바이스 제조 방법.

- 제9항에 있어서,상기 제1 개수의 폭이 넓은 셀; 및상기 제2 개수의 폭이 좁은 셀을 포함하는 디바이스의 레이아웃(layout)을 정하는 단계를 더 포함하되,상기 폭이 넓은 셀은 상기 제1 폭을 갖는 트랜치 게이트에 의해 경계가 지어지는 트랜치 게이트 전력 모스펫 디바이스 제조 방법.

- 트랜치 게이트 전력 모스펫을 설계하는 방법에 있어서,제1 셀 타입에 대한 제1의 전기적 특성이 제1 요건을 충족시키도록, 상기 제1 셀 타입에 대한 제1의 물리적 파라미터를 정하는 단계;제2 셀 타입에 대한 상기 제1의 전기적 특성이 상기 제1 셀 타입에 대한 상기 제1 전기적 특성을 초과하도록, 상기 제2 셀 타입에 대한 제2의 물리적 파라미터를 정하는 단계;제2 요건을 충족시키기 위해 필요한 상기 제1 셀 타입의 개수인 제1 개수를 정하는 단계; 및제3 요건을 충족시키기 위해 필요한 상기 제2 셀 타입의 개수인 제2 개수를 정하는 단계를 포함하는 트랜치 게이트 전력 모스펫 설계 방법.

- 제11항에 있어서,상기 제1의 물리적 파라미터는 셀의 폭인 트랜치 게이트 전력 모스펫 설계 방법.

- 제11항에 있어서,상기 제1의 물리적 파라미터는 고농도 본체 식각의 깊이인 트랜치 게이트 전력 모스펫 설계 방법.

- 제11항에 있어서,상기 제1의 물리적 파라미터는 트랜치의 폭인 트랜치 게이트 전력 모스펫 설계 방법.

- 제11항에 있어서,상기 제1의 전기적 특성은 본체-다이오드 간 항복 전압인 트랜치 게이트 전력 모스펫 설계 방법.

- 제11항에 있어서,상기 제2의 물리적 파라미터는 셀의 폭인 트랜치 게이트 전력 모스펫 설계 방법.

- 제16항에 있어서,상기 폭은 최소 설계 규칙에 의해 정해지는 트랜치 게이트 전력 모스펫 설계 방법.

- 제11항에 있어서,상기 제2 요건은 원하는 턴-오프 전류 사양인 트랜치 게이트 전력 모스펫 설계 방법.

- 제11항에 있어서,상기 제3 요건은 온 저항 사양인 트랜치 게이트 전력 모스펫 설계 방법.

- 제11항에 있어서,상기 제1의 개수의 상기 제1 셀 타입과 상기 제2의 개수의 상기 제2 셀 타입을 포함하는 디바이스의 레이아웃을 정하는 단계를 더 포함하는 트랜치 게이트 전력 모스펫 설계 방법.

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US76356706P | 2006-01-30 | 2006-01-30 | |

| US60/763,567 | 2006-01-30 | ||

| US11/482,676 | 2006-07-07 | ||

| US11/482,676 US7667265B2 (en) | 2006-01-30 | 2006-07-07 | Varying mesa dimensions in high cell density trench MOSFET |

| PCT/US2007/001846 WO2007089489A2 (en) | 2006-01-30 | 2007-01-23 | Varying mesa dimensions in high cell density trench mosfet |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20080098368A true KR20080098368A (ko) | 2008-11-07 |

| KR101404827B1 KR101404827B1 (ko) | 2014-06-09 |

Family

ID=38321209

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020087019275A Active KR101404827B1 (ko) | 2006-01-30 | 2007-01-23 | 다양한 메사 치수를 갖는 높은 셀 밀도의 트랜치 모스펫 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US7667265B2 (ko) |

| JP (1) | JP2009525597A (ko) |

| KR (1) | KR101404827B1 (ko) |

| CN (1) | CN101375401B (ko) |

| AT (1) | AT505497A2 (ko) |

| DE (1) | DE112007000270T5 (ko) |

| TW (1) | TWI443825B (ko) |

| WO (1) | WO2007089489A2 (ko) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090096027A1 (en) * | 2007-10-10 | 2009-04-16 | Franz Hirler | Power Semiconductor Device |

| US8604560B2 (en) * | 2008-11-27 | 2013-12-10 | Freescale Semiconductor, Inc. | Power MOS transistor device |

| WO2010061244A1 (en) * | 2008-11-27 | 2010-06-03 | Freescale Semiconductor, Inc. | Power mos transistor device and switch apparatus comprising the same |

| EP2467876A1 (en) * | 2009-08-18 | 2012-06-27 | Freescale Semiconductor, Inc. | Transistor power switch device and method of measuring its characteristics |

| JP5656608B2 (ja) * | 2010-12-17 | 2015-01-21 | 三菱電機株式会社 | 半導体装置 |

| DE112013002751B4 (de) * | 2012-05-30 | 2019-08-29 | Kyushu Institute Of Technology | Leistungshalbleitervorrichtung vom Typ mit hochspannungsisoliertem Gate und Verfahren zum Herstellen derselben |

| US10411111B2 (en) | 2012-05-30 | 2019-09-10 | Kyushu Institute Of Technology | Method for fabricating high-voltage insulated gate type bipolar semiconductor device |

| US20140131766A1 (en) | 2012-11-15 | 2014-05-15 | Infineon Technologies Ag | Inhomogenous Power Semiconductor Devices |

| US20240145537A1 (en) * | 2022-10-31 | 2024-05-02 | Wolfspeed, Inc. | Semiconductor devices with additional mesa structures for reduced surface roughness |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5072266A (en) * | 1988-12-27 | 1991-12-10 | Siliconix Incorporated | Trench DMOS power transistor with field-shaping body profile and three-dimensional geometry |

| JPH06163907A (ja) * | 1992-11-20 | 1994-06-10 | Hitachi Ltd | 電圧駆動型半導体装置 |

| US5592005A (en) * | 1995-03-31 | 1997-01-07 | Siliconix Incorporated | Punch-through field effect transistor |

| US6049108A (en) * | 1995-06-02 | 2000-04-11 | Siliconix Incorporated | Trench-gated MOSFET with bidirectional voltage clamping |

| US6140678A (en) * | 1995-06-02 | 2000-10-31 | Siliconix Incorporated | Trench-gated power MOSFET with protective diode |

| JP2000058823A (ja) * | 1998-08-13 | 2000-02-25 | Toshiba Corp | 半導体装置およびその製造方法 |

| US6413822B2 (en) * | 1999-04-22 | 2002-07-02 | Advanced Analogic Technologies, Inc. | Super-self-aligned fabrication process of trench-gate DMOS with overlying device layer |

| JP4568929B2 (ja) * | 1999-09-21 | 2010-10-27 | 株式会社デンソー | 炭化珪素半導体装置及びその製造方法 |

| US20030060013A1 (en) * | 1999-09-24 | 2003-03-27 | Bruce D. Marchant | Method of manufacturing trench field effect transistors with trenched heavy body |

| US6348712B1 (en) * | 1999-10-27 | 2002-02-19 | Siliconix Incorporated | High density trench-gated power MOSFET |

| JP2001345445A (ja) * | 2000-06-02 | 2001-12-14 | Nec Corp | 半導体装置 |

| US6921939B2 (en) * | 2000-07-20 | 2005-07-26 | Fairchild Semiconductor Corporation | Power MOSFET and method for forming same using a self-aligned body implant |

| US6696726B1 (en) * | 2000-08-16 | 2004-02-24 | Fairchild Semiconductor Corporation | Vertical MOSFET with ultra-low resistance and low gate charge |

| JP2002100770A (ja) * | 2000-09-22 | 2002-04-05 | Toshiba Corp | 絶縁ゲート型半導体装置 |

| US6710403B2 (en) * | 2002-07-30 | 2004-03-23 | Fairchild Semiconductor Corporation | Dual trench power MOSFET |

| US7345342B2 (en) * | 2001-01-30 | 2008-03-18 | Fairchild Semiconductor Corporation | Power semiconductor devices and methods of manufacture |

| JP2003101027A (ja) * | 2001-09-27 | 2003-04-04 | Toshiba Corp | 半導体装置及びその製造方法 |

| GB0125710D0 (en) * | 2001-10-26 | 2001-12-19 | Koninkl Philips Electronics Nv | Transistor device |

| DE10223699B4 (de) * | 2002-05-28 | 2007-11-22 | Infineon Technologies Ag | MOS-Transistoreinrichtung vom Trenchtyp |

| JP2004241413A (ja) * | 2003-02-03 | 2004-08-26 | Toshiba Corp | 半導体装置 |

| US7423299B2 (en) * | 2003-05-13 | 2008-09-09 | Nxp B.V. | Semiconductor devices with a field shaping region |

| JP2006278826A (ja) * | 2005-03-30 | 2006-10-12 | Toshiba Corp | 半導体素子及びその製造方法 |

-

2006

- 2006-07-07 US US11/482,676 patent/US7667265B2/en active Active

-

2007

- 2007-01-23 JP JP2008552374A patent/JP2009525597A/ja active Pending

- 2007-01-23 WO PCT/US2007/001846 patent/WO2007089489A2/en not_active Ceased

- 2007-01-23 DE DE112007000270T patent/DE112007000270T5/de not_active Withdrawn

- 2007-01-23 AT AT0904007A patent/AT505497A2/de not_active Application Discontinuation

- 2007-01-23 CN CN200780003837XA patent/CN101375401B/zh not_active Expired - Fee Related

- 2007-01-23 KR KR1020087019275A patent/KR101404827B1/ko active Active

- 2007-01-29 TW TW096103187A patent/TWI443825B/zh active

Also Published As

| Publication number | Publication date |

|---|---|

| US20070176231A1 (en) | 2007-08-02 |

| TWI443825B (zh) | 2014-07-01 |

| TW200805652A (en) | 2008-01-16 |

| DE112007000270T5 (de) | 2008-12-11 |

| CN101375401B (zh) | 2011-11-16 |

| JP2009525597A (ja) | 2009-07-09 |

| KR101404827B1 (ko) | 2014-06-09 |

| WO2007089489A2 (en) | 2007-08-09 |

| WO2007089489A3 (en) | 2008-06-26 |

| US7667265B2 (en) | 2010-02-23 |

| AT505497A2 (de) | 2009-01-15 |

| CN101375401A (zh) | 2009-02-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10229993B2 (en) | LDMOS transistors including resurf layers and stepped-gates, and associated systems and methods | |

| KR101404827B1 (ko) | 다양한 메사 치수를 갖는 높은 셀 밀도의 트랜치 모스펫 | |

| JP4212288B2 (ja) | 半導体装置およびその製造方法 | |

| CN101454882B (zh) | 具有集成肖特基二极管的高密度沟槽fet及制造方法 | |

| US8860098B2 (en) | Vjfet devices | |

| JP5423882B2 (ja) | 超接合半導体装置 | |

| US20110233664A1 (en) | Semiconductor device and a method of manufacturing the same | |

| CN104576737B (zh) | 半导体器件 | |

| US9190504B2 (en) | Semiconductor device | |

| EP3457440A1 (en) | Semiconductor device | |

| CN104979401A (zh) | 半导体器件和集成电路 | |

| TWI714749B (zh) | 垂直碳化矽金屬氧化物半導體場效電晶體 | |

| US20160079350A1 (en) | Semiconductor device and manufacturing method thereof | |

| US10103140B2 (en) | Switch circuit with controllable phase node ringing | |

| CN110176500A (zh) | 平面结构沟道金氧半场效晶体管及其加工方法 | |

| EP1870940A1 (en) | Semiconductor device | |

| CN210224042U (zh) | 平面结构沟道金氧半场效晶体管 | |

| US11152353B2 (en) | Semiconductor device and method of manufacturing the same | |

| JPH11284187A (ja) | 半導体装置およびその製造方法 | |

| KR20160016520A (ko) | 반도체 장치 | |

| US20250311286A1 (en) | Semiconductor device | |

| KR101870824B1 (ko) | 전력 반도체 소자 및 그 제조방법 | |

| Zhu | Performance improvements of the vertical, double-diffused power metal-oxide-silicon field-effect transistor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

St.27 status event code: A-0-1-A10-A15-nap-PA0105 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| A201 | Request for examination | ||

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| T11-X000 | Administrative time limit extension requested |

St.27 status event code: U-3-3-T10-T11-oth-X000 |

|

| AMND | Amendment | ||

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E601 | Decision to refuse application | ||

| PE0601 | Decision on rejection of patent |

St.27 status event code: N-2-6-B10-B15-exm-PE0601 |

|

| AMND | Amendment | ||

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| J201 | Request for trial against refusal decision | ||

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| PJ0201 | Trial against decision of rejection |

St.27 status event code: A-3-3-V10-V11-apl-PJ0201 |

|

| PB0901 | Examination by re-examination before a trial |

St.27 status event code: A-6-3-E10-E12-rex-PB0901 |

|

| B701 | Decision to grant | ||

| PB0701 | Decision of registration after re-examination before a trial |

St.27 status event code: A-3-4-F10-F13-rex-PB0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U12-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20190430 Year of fee payment: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 7 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 8 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 9 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 10 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 11 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 12 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |