KR101689077B1 - 시간 동기화 방법 및 그 장치 - Google Patents

시간 동기화 방법 및 그 장치 Download PDFInfo

- Publication number

- KR101689077B1 KR101689077B1 KR1020150052757A KR20150052757A KR101689077B1 KR 101689077 B1 KR101689077 B1 KR 101689077B1 KR 1020150052757 A KR1020150052757 A KR 1020150052757A KR 20150052757 A KR20150052757 A KR 20150052757A KR 101689077 B1 KR101689077 B1 KR 101689077B1

- Authority

- KR

- South Korea

- Prior art keywords

- time

- correction

- data

- error

- reception

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0638—Clock or time synchronisation among nodes; Internode synchronisation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0016—Arrangements for synchronising receiver with transmitter correction of synchronization errors

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0638—Clock or time synchronisation among nodes; Internode synchronisation

- H04J3/0658—Clock or time synchronisation among packet nodes

- H04J3/0661—Clock or time synchronisation among packet nodes using timestamps

- H04J3/0664—Clock or time synchronisation among packet nodes using timestamps unidirectional timestamps

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0685—Clock or time synchronisation in a node; Intranode synchronisation

- H04J3/0697—Synchronisation in a packet node

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0004—Initialisation of the receiver

Abstract

본 발명은 발명은 시간 동기화 방법 및 그 장치에 관한 것으로, 특히 장치간 시간 동기화를 위한 방법 및 그 장치에 관한 것이다.

본 발명에 따른 시간 동기화 방법은 제1 장치로부터 데이터를 수신하는 단계; 상기 수신된 데이터에 포함되는 제1 장치의 시간 정보를 확인하는 단계; 상기 확인된 시간 정보에 기초하여 시간 오차를 보정하는 단계;를 포함하고, 상기 시간 오차 보정은 상기 제1 장치와의 오차 시간에 따른 보정 상수에 의해 보정되는 것을 특징으로 한다.

본 발명에 따른 시간 동기화 방법은 제1 장치로부터 데이터를 수신하는 단계; 상기 수신된 데이터에 포함되는 제1 장치의 시간 정보를 확인하는 단계; 상기 확인된 시간 정보에 기초하여 시간 오차를 보정하는 단계;를 포함하고, 상기 시간 오차 보정은 상기 제1 장치와의 오차 시간에 따른 보정 상수에 의해 보정되는 것을 특징으로 한다.

Description

본 발명은 시간 동기화 방법 및 그 장치에 관한 것으로, 특히 장치간 시간 동기화를 위한 방법 및 그 장치에 관한 것이다.

장치간의 데이터 송수신을 위해서는 각 장치간의 동기화를 시도한다. 이때 일반적으로 장치들 중 특정 하나의 장치 또는 마스터 장치에서 전송되는 시간 정보에 기초하여 상기 장치와 연동되는 적어도 하나의 장치가 마스터 장치의 시간을 추종하게 된다.

즉, 통신 네트워크로 연결되는 장치들 중 마스터 장치는 데이터를 전송 시 타임 스탬프를 포함하는 메시지를 전송한다. 이때 타임 스탬프를 메시지가 전송되는 순간의 시간 또는 장치의 시간 정보를 포함할 수 있다. 상기 마스터 장치와 연결되는 슬레이브 장치들은 마스터 장치로부터 수신되는 메시지에 포함된 타임 스탬프를 기초하여 시간 동기화를 수행할 수 있다.

도 1은 종래의 장치간 시간 동기화 동작을 설명하기 위한 블록 구성도이다.

도 1을 참조하면, 종래의 서버(10) 및 클라이언트(20)로 구성되는 통신 시스템은 시간 동기화를 위하여 소프트웨어 핸드쉐이킹 방식으로 수행될 수 있다. 소프트웨어 핸드쉐이킹 방식은 클라이언트(20)가 서버(10)에 시간 요청 패킷을 전송하면(S11) 서버(10)는 클라이언트(20)로부터 요청된 시간요청 패킷에 응답하여 서버의 현재 시간 정보(T)를 응답 패킷으로 전송할 수 있다.(S12)

클라이언트(20)는 서버(10)로부터 수신한 현지 시간 정보를 기초하여 하기의 [수학식 1]을 기초하여 현재 시간을 설정할 수있다.

[수학식 1]

클라이언트의 현재 시간=T+RTT/2

즉, 클라이언트(20)는 서버(10)에 시간 요청 패킷을 전송하고, 그에 따른 응답신호에 포함된 서버의 현재 시간 정보(T)에 시간 요청 패킷 송신 후 응답 수신까지 소요된 시간 중 패킷 전송 시간을 제외한 시간(RTT/2)을 합하여 클라이언트의 현재 시간을 설정할 수있다.

상기와 같은 소프트웨어 핸드쉐이킹 방식에 따른 장치간 시간 동기화는 장치간 통신 패킷에 대한 송수신 및 해석이 요구되므로 데이터 송수신 장치 및 시스템에 따라 수 ms의 장치간 시간 오차가 발생할 수 있다. 또한 이러한 방식으로 정밀한 시간 동기를 구현하는 것이 불가능한 것은 아니나, 이러한 방식을 채용하는 경우 통신 패킷 해석이 우선 처리되어야 함에 따른 장치의 추가적인 부하가 요구된다. 따라서, 시스템 운영에 제약이 따르거나, 그에 따른 시간적 손실이 발생할 수 있다.

따라서 본 발명은 장치간 효율적인 시간 동기화를 위한 시간 동기화 방법 및 그 장치를 제공한다. 그리고 본 발명은 장치간 동작에 요구되는 부하를 최소화하고, 정밀한 시간 동기를 구현할 수 있는 시간 동기화 방법 및 장치를 제공한다.

상기 과제를 해결하기 위한 본 발명에 따른 시간 동기화 방법은 제1 장치로부터 데이터를 수신하는 단계; 상기 수신된 데이터에 포함되는 제1 장치의 시간 정보를 확인하는 단계; 상기 확인된 시간 정보에 기초하여 시간 오차를 보정하는 단계;를 포함하고, 상기 시간 오차 보정은 상기 제1 장치와의 오차 시간에 따른 보정 상수에 의해 보정되는 것을 특징으로 한다.

본 발명에 따른 시간 동기화 방법 및 그 장치는 용이하게 장치간의 시간 동기화 작업을 수행할 수 있다. 아울러, 장치간 동작 부하를 최소화하고, 정밀하고, 신속하게 시간 동기화 작업 및 상태를 유지할 수 있다. 이로 인하여, 정확한 데이터 송수신 및 그에 다른 데이터 처리에 대한 효율을 향상 시킬 수 있다.

도 1은 종래의 시간 동기화 동작을 설명하기 위한 블록 구성도.

도 2는 본 발명의 실시 예 에 따른 시간 동기화 동작을 설명하기 위한 블록 구성도.

도 3은 본 발명의 실시 예에 따른 제1 장치의 데이터 송수신 동작 흐름도.

도 4는 본 발명의 실시 예에 따른 제2 장치의 데이터 송수신 동작 흐름도.

도 5는 본 발명의 실시 예에 따른 장치간 시간 동기화 동작 흐름도.

도 2는 본 발명의 실시 예 에 따른 시간 동기화 동작을 설명하기 위한 블록 구성도.

도 3은 본 발명의 실시 예에 따른 제1 장치의 데이터 송수신 동작 흐름도.

도 4는 본 발명의 실시 예에 따른 제2 장치의 데이터 송수신 동작 흐름도.

도 5는 본 발명의 실시 예에 따른 장치간 시간 동기화 동작 흐름도.

이하, 첨부된 도면을 참조하면 본 발명의 실시 예를 보다 상세하게 설명하고자 한다. 이때 첨부된 도면에서 동일한 구성 요소는 가능한 동일한 부호로 나타내고 있음에 유의해야 한다. 그리고 본 발명의 요지를 흐리게 할 수 잇는 공지 기능 및 구성에 대한 상세한 설명은 생략할 것이다.

도 2는 본 발명의 실시 예 에 따른 시간 동기화 동작을 설명하기 위한 블록 구성도이다.

도 1을 참조하면, 본 발명의 실시 예에 따른 데이터 송수신 시스템(1000)은 제1 장치(100) 및 적어도 하나의 제2 장치(200)로 구성될 수 있다. 본 발명의 실시 예에 따른 데이터 송수신 시스템(1000)은 제1 장치(100)가 마스터 장치이고, 제2 장치가 슬레이브 장치로 예를 개시할 것이나, 제1 및 제2 장치가 동일한 장치로 구성되거나 시스템 구성에 따라 유동적으로 마스터 장치가 설정될 수 있다. 따라서 시스템의 구성은 한정된 것이 아니다. 또한 상기 제2 장치는 복수 개로 구성될 수 있으나, 이에 한정하는 것은 아니다.

마스터 장치(100)는 제1 통신부(110), 제1 제어부(120) 및 제 1저장부(130)를 포함하여 구성될 수 있다.

제1 통신부(110)는 제1 발진기(111) 및 제1 시간 보정부(112)를 포함하여 구성될 수 있다.

제1 발진기(111)는 클럭 신호를 생성하고, 생성된 클럭 신호에 기초하여 장치의 동작을 실행할 수 있다. 상기 제1 발진기(111)는 제1 통신부(110)에 포함되지 않고 별도로 구성될 수 있다.

제1 시간 보정부(112)는 제1 발진기(111)의 신호에 의하여 소정 주기에 따라 장치의 시간을 설정할 수 있다.

제1 제어부(120)는 전송하고자 하는 데이터를 송신 버퍼에 기록하고, 수신하고자 하는 데이터를 수신 버퍼로 수신할 수 있도록 제 1통신부(110)를 제어할 수 있다. 또한, 제1 제어부(120)는 제1 통신부(110)의 클럭 신호에 기초하여 데이터를 송수신하도록 제어할 수 있다. 또한 제1 제어부(120)는 슬레이브 장치(200)로부터 수신되는 데이터를 확인하고, 데이터 송신 시 마스터 장치(100)의 시간 정보를 포함하여 전송하도록 할 수 있다.

제1 저장부(130)는 장치간 송수신할 수 있는 데이터를 저장할 수 있다. 또한 제1 저장부(130)는 네트워크로 연결되는 장치들의 식별정보 및 상태정보를 저장할 수 있다. 제1 저장부(130)는 장치의 특성에 따라 슬레이브 장치로 동작하는 경우 마스터 장치로부터 수신되는 시간 정보 및 그에 따른 시간 보정 정보를 저장할 수 있다.

슬레이브 장치(200)는 마스터 장치(100)와 유사한 구성을 가질 수 있다. 슬레이브 장치(200)는 제2 통신부(210), 제2 제어부(220) 및 제2 저장부(230)를 포함하여 구성될 수 있다.

슬레이브 장치(200)의 제2 통신부(210)는 제2 발진기(211) 및 제2 시간 보정부(212)를 포함하여 구성될 수 있다.

슬레이브 장치(200)의 제2 통신부(210)에 구성되는 제2 발진기(211)는 마스터 장치(100)와 동일한 구성의 제2 발진기(211)를 포함할 수 있다. 제2 발진기(211) 역시 소정 주기마다 클럭을 발생하고 상기 클럭에 따라 슬레이브 장치(200)의 동작을 실행할 수 있다.

제2 시간 보정부(212)는 마스터 장치(100)로부터 수신되는 시간 정보에 기초하여 슬레이브 장치(200)의 시간을 마스터 장치(100)의 시간에 수렴하도록 시간을 보정할 수 있다. 상세하게, 제2 시간 보정부(212)는 마스터 장치(100)의 시간 정보를 취득하고 상기 취득된 시간 정보와 현재 슬레이브 장치(200)의 시간 정보 및 시간 보정 상수를 이용하여 마스터 장치(100)의 시간과 슬레이브 장치(200) 간의 시간을 동기화할 수 있다. 상기 제2 시간 보정부(212)의 동작 및 본 발명의 실시 예에 따른 시간 보정 동작은 도 5을 참조하여 상세히 설명할 것이다.

제어부(220)는 마스터 장치(100)로부터 취득되는 시간 정보에 기초하여 시간 제2 보정부(212)에서 오차 시간을 보정 및 보상할 수 있도록 제어할 수 있다. 제2 제어부(220)는 보정된 시간에 기초하여 데이터를 송수신할 수 있도록 제어할 수 있다.

제2 저장부(230)는 마스터 장치(100) 및 네트워크로 연결되는 장치들간에 송수신할 수 있는 데이터를 저장할 수 있다. 제2 저장부(230)는 마스터 장치(100) 또는 네트워크로 연결된 장치들로부터 취득되는 시간 정보를 저장하고, 제2 시간 보정부(212)에서 보정할 시간 보정 정보 데이터 및 보정된 시간 정보를 저장할 수 있다. 제2 저장부(230)에 저장되는 시간 보정 정보 데이터는 마스터 장치(100)로부터 수신한 시간 정보에 따른 보정 상수 및 보정 시행 횟수 등을 포함할 수 있다. 제2 저장부(230)는 보정된 시간 정보 및 그에 따른 보정 상수를 저장할 수 있다.

상술한 바와 같이 본 발명의 실시 예에 따른 장치의 구성을 기초하여 도 3 내지 도 5를 참조하여 본 발명의 실시 예에 따른 데이터 송수신 동작에 대해 상세히 설명한다.

도 3은 본 발명의 실시 예에 따른 제1 장치의 데이터 송수신 동작 흐름이고, 도 4는 본 발명의 실시 예에 따른 제2 장치의 데이터 송수신 동작 흐름도이다.

도 3을 참조하면, 제1 장치(100) 즉 본 발명의 실시 예에 따른 마스터 장치(100)의 제1 제어부(120)는 슬레이브 장치(200)로 전송할 데이터를 송신 버퍼에 기록할 수 있다.(S310)

제1 제어부(120)는 송신 버퍼에 데이터 쓰기가 완료되면, CS(Chip Select)신호를 인에이블할 수 있다..(S320)

제1 제어부(120)는 슬레이브 장치(200)의 인에이블(Enable)신호가 인에이블 되었는지를 판단할 수 있다.(S330)

제1 제어부(120)는 슬레이브 장치(200)로부터 데이터 수신이 가능하도록 인에이블 신호가 인에이블 되었다고 판단되면 제1 발진기(111)에서 클럭 신호를 생성할 수 있다.(S340)

제1 제어부(120)는 생성되는 클럭 신호에 기초하여 송신 버퍼에 기록된 데이터를 해당 슬레이브 장치(200)로 전송할 수 있다.

상기 마스터 장치(100)의 동작에 따라 데이터를 송수신하기 위한 슬레이브 장치(200)의 데이터 송수신 동작을 도 4를 참조하여 설명한다.

도 4를 참조하면 슬레이브 장치(200)는 제2 제어부(220)의 제어에 기초하여 마스터 장치(100)로 전송하기 위한 데이터를 송신 버퍼에 기록할 수 있다.(S410)

제2 제어부(230)는 송신 버퍼에 데이터 쓰기가 완료되면, 마스터 장치(100)의 CS신호가 인에이블 되었는지를 판단할 수 있다.(S420)

제2 제어부(230)는 마스터 장치(100)의 CS신호가 인에이블 되었다고 판단되면 인에이블 신호를 인에이블할 수 있다.(S430) 즉, 슬레이브 장치(200)의 제2 제어부(230)는 송신 버퍼에 기록한 데이터를 마스터 장치(100)로 전송하기 위하여 마스터 장치(100)의 CS신호가 인에이블되면 인에이블 신호를 인에이블한다. 따라서, 마스터 장치(100)로부터 데이터를 수신할 수 있거나 전송할 수 있는 상태가 될 수 잇다.

제2 제어부(230)는 인에이블 신호가 인에이블되면 제2 발진기(211)에서 클럭 신호를 생성할 수 있다. 상기 생성된 제2 발진기(211)의 클럭 신호에 기초하여 데이터를 송신 하거나 수신할 수 잇다.

이때 본 발명의 실시 예에 따라 제2장치 즉, 슬레이브 장치는 마스터 장치로부터 수신되는 데이터에 포함되는 마스터 장치의 시간 정보를 확인하고, 확인된 시간 정보에 기초하여 슬레이브 장치의 시간을 보정할 수 있다.

이하, 도 5를 참조하여 본 발명의 실시 예에 따른 장치간 시간 동기화 방법을 상세히 설명한다.

도 5는 본 발명의 실시 예에 따른 장치간 시간 동기화 동작 흐름도이다.

도 5를 참조하면, 본 발명의 실시 예에 따른 제1 장치(100)와 제2 장치(200)는 앞서 설명한 장치간 데이터 송수신 시 포함되는 시간 정보를 기초하여 장치간의 시간 동기화를 실행할 수 있다.

제1 장치(100) 및 제2 장치(200) 즉, 마스터 장치(100)와 적어도 하나의 슬레이브 장치(200)는 시간 동기화를 실행하기 위해 각각의 장치의 시간 정보를 초기화 할 수 있다.(S502)

마스터 장치(100) 및 슬레이브 장치(200)의 시간 정보 초기화가 완료되면, 상술한 도 3 및 도 4의 설명과 같이 장치간의 상호 데이터를 송수신할 수 잇다.(S504)

이때, 슬레이브 장치(200)는 마스터 장치(100)로부터 수신되는 데이터에 포함되는 마스터 장치(100)의 시간 정보를 확인할 수 있다.(S506)

슬레이브 장치(200)는 마스터 장치(100)와의 데이터 송수신이 완료된 시점 즉, 데이터 송수신 시 마지막으로 수신한 마스터 장치(100)의 데이터에 포함된 시간 정보를 기초하여 슬레이브 장치(200)의 시간 정보를 보정할 수 있다.(S508)

슬레이브 장치(200)의 시간 정보는 하기의 [수학식 2]에 의하여 보정될 수 있다.

[수학식 2]

제2 장치_Time[1]=제2 장치_Time[1]- α X (제2 장치 시간-제1 장치 시간), (0<α<1)

상기 [수학식 2]와 같이 데이터 송수신이 완료된 시점에 마스터 장치(100)의 시간 정보를 기초하여 보정되는 슬레이브 장치(200)의 시간은 슬레이브 장치의 시간과 슬레이브 장치의 시간 및 수신된 마스터 장치의 시간의 차에 보정 상수(α)를 곱한 값에 대한 차로 산출될 수 잇다. 이때, 보정 상수(α)는 0과 1사이의 값일 수 있다.

상기와 같이 [수학식 2]에 의하여 보정된 슬레이브 장치(200)는 마스터 장치(100)와 시간이 동기화되고, 다음 데이터 송수신 동작이 발생할 때까지 보정된 시간에 기초하여 시간을 카운트할 수 있다. 도5의 실시 예에서는 제1 데이터 송수신이 완료된 이후 소정 시간(Ta, Tb)(또는 주기(1T))이후에 제2 데이터 송수신이 실행되는 것을 예를 들어 설명한다.

마스터 장치(100)와 슬레이브 장치(200)는 Ta, Tb시간(1T) 이후에 데이터 송수신 동작을 실행할 수 있다.

슬레이브 장치(200)는 제2 데이터 송수신 동작이 완료되면, 제1 데이터 송수신 동작이 완료된 시점에 수행한 시간 보정 동작을 재 실행할 수 있다.

즉, 슬레이브 장치(200)는 제2 데이터 송수신 동작이 완료되면, 마스터 장치(100)와의 데이터 송수신이 완료된 시점 즉, 데이터 송수신 시 마지막으로 수신한 마스터 장치(100)의 데이터에 포함된 시간 정보를 확인할 수 있다.(S512)

슬레이브 장치(200)는 상기 확인된 시간 정보를 기초하여 슬레이브 장치(200)의 시간 정보를 보정할 수 있다.(S514)

제2 데이터 송수신 이후에 슬레이브 장치(200)의 시간 보정은 상기한 수학식 2에 기초하여 실행될 수 있다.

이때, 마스터 장치(100)로부터 수신된 시간은 제1 데이터 송수신 시 전송한 시간 정보에 제2 데이터 전송 시점 즉, Ta시간이 경과한 만큼 더해진 시간이 될 수 있다.

따라서, 슬레이브 장치(200)의 시간은 [수학식 2]에 의하여 보정될 수 잇다.

제2 장치 시간[2]=제2 장치_Time[2]-α X(제2 장치 시간 ?? 제1 장치 시간)=2Tb- αX(Tb-Ta) (0< α<1)

즉, 제1 데이터 송수신 이후 Ta, Tb 시간이 경과한 시점에 실행한 제2 데이터 송수신 동작이 완료된 시점의 슬레이브 장치(200)의 시간은 제1 데이터 송수신 시 보정된 시간에 증가된 시간을 더하여 산출될 수 있다.

마스터 장치(100)와 슬레이브 장치(200)는 Ta, Tb(2T)이후에 상술한 바와 같은 동작에 기초하여 제3 데이터 송수신 동작을 실행할 수 있다.(S516)

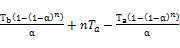

상술한 바와 같이 마스터 장치(100)와 슬레이브 장치(200)는 데이터 송수신을 실행하고, 상기 마스터 장치(100)로부터 수신된 데이터에 포함된 시간 정보에 기초하여 슬레이브 장치(200)는 시간을 보정함으로써, 마스터 장치(100)와 시간 동기화를 수행할 수 있다. 따라서 슬레이브 장치(200)는 n회 마스터 장치(100)와 데이터 송수신 및 시간 보정을 실행하게 되었을 때의 시간은 하기의 [수학식 3]과 같이 정의될 수 있다.

[수학식 3]

상기 [수학식 3]에 따르면, 마스터 장치(100)와 슬레이브 장치(200) 즉, 제1 장치와 제2 장치가 데이터를 송수신 하고, 제2 장치가 제1 장치의 시간 정보에 기초하여 시간을 보정한 횟수(n)이 커질수록 제1 및 제2 장치간의 시간 오차는 으로 수렴할 수 있다. 즉, 제1 및 제2 장치간의 데이터 송수신 주기의 차(Tb-Ta)에 보정 상수(α)를 나눈 값으로 오차가 수렴할 수 있다.

또한, 보정 상수(α)는 0에서 1 사이 값으로 설정될 수 있다. 보정 상수(α )가 1의 근사치일수록 보정값이 커질 수 있다. 따라서 일시적 오차 발생 시에는 오차 보정을 위한 변동 값이 커질 수 있다. 또한, 보정 상수(α)가 0의 근사치일수록 오차값이 0으로 수렴할 수 있다. 따라서 제1 및 제2 장치간 또는 장치들 간의 오차가 기준 오차 이상인 경우 보정 상수(α)를 1의 근사치로 설정하여 시간 보정을 실행하고, 오차가 기준 오차 미만 경우 보정 상수(α)를 0의 근사치로 설정하여 시간 보정을 실행할 수 있다.

한편, 본 명세서와 도면에 개시된 본 발명의 실시 예는 본 발명의 기술 내용을 쉽게 설명하고 본 발명의 이해를 돕기 위해 특정 예를 제시한 것일 뿐이며, 본 발명의 범위를 한정하고자 하는 것은 아니다. 즉 본 발명의 기술적 사상에 바탕을 둔 다른 변형 예들이 실시 가능하다는 것은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 자명한 것이다.

1000: 데이터 송수신 시스템

100: 제1 장치(마스터 장치)

110: 제1 통신부

111: 제1 발진기 112: 제1 시간 보정부

120: 제1 제어부

130: 제1 저장부

200: 제2 장치(슬레이브 장치)

210: 제2 통신부

211: 제2 발진기 212: 제2 시간 보정부

220: 제2 제어부

230: 제2 저장부

100: 제1 장치(마스터 장치)

110: 제1 통신부

111: 제1 발진기 112: 제1 시간 보정부

120: 제1 제어부

130: 제1 저장부

200: 제2 장치(슬레이브 장치)

210: 제2 통신부

211: 제2 발진기 212: 제2 시간 보정부

220: 제2 제어부

230: 제2 저장부

Claims (10)

- 제1 장치로부터 데이터를 수신하는 단계;

상기 수신된 데이터에 포함되는 상기 제1 장치의 시간 정보를 확인하는 단계;

상기 확인된 시간 정보에 기초하여 시간 오차를 보정하는 단계;를 포함하고,

상기 시간 오차의 보정은

제2 장치와 상기 제1 장치의 시간 오차값에, 상기 시간 오차 값에 따른 보정 상수(α)를 곱한 값에 대한 현재 시간 값(제2 장치_Time[1])의 차로 산출되고, 보정된 시간은 하기의 수학식과 같이 표현되고,

제2 장치_Time[1]=제2 장치_Time[1]- α X (제2 장치 시간-제1 장치 시간), (0<α<1)

상기 시간 오차의 보정 후 임계시간 (Ta, Tb) 경과 후 데이터 송수신이 완료되면, 상기 보정된 시간(제2 장치_Time[1])에 상기 경과된 시간을 부가하여 산출하고,

상기 시간 오차 보정된 값은

상기 제1 장치와 데이터 송수신을 n회 실행하는 경우 보정 상수(α) 및 보정 횟수(데이터 송수신 횟수)(n)에 기초하여 결정되고, 하기의 수학식과 같이 표현되는

시간 동기화 방법. - 제1항에 있어서,

상기 제1 장치로부터 데이터를 수신하는 단계는

상기 제1 장치로부터 CS신호가 인에이블되면 인에이블 신호를 인에이블하여 클럭 신호에 기초하여 데이터를 송수신하는 시간 동기화 방법. - 제1항에 있어서,

상기 시간 오차 보정 전에 기 설정된 시간 정보를 초기화하는 단계;를 더 포함하는 시간 동기화 방법. - 제1항에 있어서,

상기 시간 오차의 보정은

제1 장치와 데이터 송수신 시 마지막으로 수신한 데이터에 포함된 상기 제1 장치의 시간 정보에 기초하여 실행되는 시간 동기화 방법. - 삭제

- 제1항에 있어서,

상기 보정된 시간 정보 및 그에 따른 보정 상수를 저장하는 단계;를 포함하는 시간 동기화 방법. - 삭제

- 제1항에 있어서,

상기 보정 상수(α)는 제1 장치와의 시간 오차 범위가 기준값 이상인 경우 1의 근사치로 설정하여 상기 시간 오차의 보정을 실행하는 시간 동기화 방법. - 삭제

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150052757A KR101689077B1 (ko) | 2015-04-14 | 2015-04-14 | 시간 동기화 방법 및 그 장치 |

| EP16164153.5A EP3082282A1 (en) | 2015-04-14 | 2016-04-07 | Method for time synchronization |

| US15/095,551 US10263760B2 (en) | 2015-04-14 | 2016-04-11 | Method for time synchronization |

| CN201610225397.3A CN106059697B (zh) | 2015-04-14 | 2016-04-12 | 用于时间同步的方法 |

| JP2016080293A JP6471368B2 (ja) | 2015-04-14 | 2016-04-13 | 時間同期化方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150052757A KR101689077B1 (ko) | 2015-04-14 | 2015-04-14 | 시간 동기화 방법 및 그 장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20160122601A KR20160122601A (ko) | 2016-10-24 |

| KR101689077B1 true KR101689077B1 (ko) | 2016-12-22 |

Family

ID=55745578

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020150052757A KR101689077B1 (ko) | 2015-04-14 | 2015-04-14 | 시간 동기화 방법 및 그 장치 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10263760B2 (ko) |

| EP (1) | EP3082282A1 (ko) |

| JP (1) | JP6471368B2 (ko) |

| KR (1) | KR101689077B1 (ko) |

| CN (1) | CN106059697B (ko) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102208677B1 (ko) * | 2016-11-17 | 2021-01-28 | 한국전자통신연구원 | Tdma 기반 메쉬망 위성 통신 시스템의 망동기화 장치 및 그 방법 |

| US10057869B2 (en) * | 2016-11-17 | 2018-08-21 | Electronics And Telecommunications Research Institute | Network synchronization apparatus and method of time division multiple access (TDMA)-based mesh network satellite communication system |

| CN108449206B (zh) * | 2018-03-12 | 2020-11-27 | 新华三技术有限公司 | 一种时间同步方法、装置、设备及存储介质 |

| JP7243695B2 (ja) * | 2020-08-25 | 2023-03-22 | 横河電機株式会社 | 情報処理装置、情報処理システム、及び情報処理方法 |

| KR102606377B1 (ko) * | 2021-02-10 | 2023-11-29 | (주)청파이엠티 | 실내 공기질 측정 시스템 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20120300859A1 (en) * | 2011-05-27 | 2012-11-29 | Cisco Technology, Inc. | Precision Timing in a Data Over Cable Service Interface Specification (DOCSIS) System |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE4215380A1 (de) * | 1992-05-11 | 1993-11-18 | Siemens Ag | Verfahren zum Synchronisieren von lokalen Zeitgebern eines Automatisierungssystems |

| US5566180A (en) * | 1994-12-21 | 1996-10-15 | Hewlett-Packard Company | Method for recognizing events and synchronizing clocks |

| JP2000285069A (ja) * | 1999-03-31 | 2000-10-13 | Copyer Co Ltd | 同期式シリアル通信方法及び同期式シリアル通信システム |

| US7251199B2 (en) * | 2001-12-24 | 2007-07-31 | Agilent Technologies, Inc. | Distributed system time synchronization including a timing signal path |

| DE102004028071B3 (de) | 2004-06-09 | 2005-11-03 | Siemens Ag | Dezentrale Zeitintervallsynchronisation in verteilten Netzwerken |

| CN100407796C (zh) | 2005-03-17 | 2008-07-30 | 华为技术有限公司 | 一种节目参考时钟调整的方法及装置 |

| TWI334547B (en) * | 2007-06-07 | 2010-12-11 | Via Tech Inc | System and method for serial peripheral interface data transmission |

| KR20090059471A (ko) * | 2007-12-06 | 2009-06-11 | 에스케이 텔레콤주식회사 | 시간 동기를 위한 이동통신 시스템 |

| JP5243786B2 (ja) * | 2007-12-28 | 2013-07-24 | サンリツオートメイション株式会社 | リモートi/oシステム及びリモートi/oシステムにおける時刻同期方法 |

| US8473638B2 (en) * | 2008-05-02 | 2013-06-25 | James Aweya | Method and apparatus for time and frequency transfer in communication networks |

| US8308205B2 (en) * | 2008-07-31 | 2012-11-13 | D & D Group Pty Ltd | Toggle latch |

| US8213406B2 (en) | 2010-04-12 | 2012-07-03 | Motorola Mobility, Inc. | Uplink time synchronization in a communication system |

| CN101834712B (zh) | 2010-04-19 | 2012-11-14 | 浙江大学 | 利用ieee1588协议实现精确时间同步的方法 |

| EP2424136B1 (en) * | 2010-08-24 | 2013-10-02 | Siemens Aktiengesellschaft | System and method for time synchronization in a communication network |

| CN102412954B (zh) | 2011-11-19 | 2014-10-22 | 西安邮电学院 | 一种分组网中时钟频率同步方法 |

| CN104247529B (zh) | 2012-03-02 | 2018-05-25 | 富士通株式会社 | 节点和通信控制方法 |

| JP2014096853A (ja) | 2014-02-13 | 2014-05-22 | Mitsubishi Electric Corp | 時刻同期装置 |

-

2015

- 2015-04-14 KR KR1020150052757A patent/KR101689077B1/ko active IP Right Grant

-

2016

- 2016-04-07 EP EP16164153.5A patent/EP3082282A1/en not_active Withdrawn

- 2016-04-11 US US15/095,551 patent/US10263760B2/en active Active

- 2016-04-12 CN CN201610225397.3A patent/CN106059697B/zh not_active Expired - Fee Related

- 2016-04-13 JP JP2016080293A patent/JP6471368B2/ja not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20120300859A1 (en) * | 2011-05-27 | 2012-11-29 | Cisco Technology, Inc. | Precision Timing in a Data Over Cable Service Interface Specification (DOCSIS) System |

Also Published As

| Publication number | Publication date |

|---|---|

| US10263760B2 (en) | 2019-04-16 |

| KR20160122601A (ko) | 2016-10-24 |

| US20160308663A1 (en) | 2016-10-20 |

| JP2016208506A (ja) | 2016-12-08 |

| JP6471368B2 (ja) | 2019-02-20 |

| CN106059697B (zh) | 2019-03-22 |

| CN106059697A (zh) | 2016-10-26 |

| EP3082282A1 (en) | 2016-10-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101689077B1 (ko) | 시간 동기화 방법 및 그 장치 | |

| JP6408461B2 (ja) | デバイスを同期するための機構、システム、及び方法 | |

| JPWO2007125670A1 (ja) | 信号伝送方法、送受信装置及び通信システム | |

| JP6798280B2 (ja) | 攻撃検知装置、攻撃検知方法、および、攻撃検知プログラム | |

| US11677515B2 (en) | Retransmission control device, method, and computer readable medium for time sensitive network communications | |

| JP2012083891A (ja) | フェイルオーバシステム、記憶処理装置及びフェイルオーバ制御方法 | |

| EP2584778B1 (en) | Display device and display system | |

| US9781691B2 (en) | Wireless communication device, non-transitory computer readable medium, and wireless communication system | |

| US10567400B2 (en) | Attack detection device, attack detection method, and non-transitory computer-readable recording medium | |

| US20160057068A1 (en) | System and method for transmitting data embedded into control information | |

| EP2672386A2 (en) | Apparatus and method for processing asynchronous event information | |

| US9882680B2 (en) | Surveillance system including network camera and gateway and method of driving the same | |

| US20110255470A1 (en) | Data processing device, system and method for data processing, recording medium with program recorded therein, data transfer device, system and method for data transfer, and recording medium with program recorded therein | |

| US11882015B2 (en) | Estimation system, addition apparatus, estimation method, addition method, estimation program and addition program | |

| US10721171B2 (en) | Data transfer system and corresponding methods | |

| US11646865B2 (en) | Transmission device | |

| US9998405B2 (en) | Packet reception apparatus | |

| KR101442485B1 (ko) | 데이터 통신 시스템 및 그 방법 | |

| JP7332660B2 (ja) | 中継装置、プログラム、システム、通信端末及び方法 | |

| KR102016029B1 (ko) | 차량 통신의 부하 분산 장치 및 방법 | |

| JP4173159B2 (ja) | 画像信号処理装置及び撮像装置 | |

| CN107710662A (zh) | 数据处理的方法及接收设备 | |

| CN111866363A (zh) | 摄像机远程升级方法、装置、电子设备及可读存储介质 | |

| JP6237367B2 (ja) | データ伝送システム、送信装置、受信装置、送信プログラム、受信プログラムおよびデータ伝送方法 | |

| US20180375779A1 (en) | Terminal and method for transmitting data via a strained channel |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E90F | Notification of reason for final refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20191001 Year of fee payment: 4 |