KR101010501B1 - 초퍼안정화된 증폭기 및 초퍼안정화된 증폭기를 동작시키는 방법 - Google Patents

초퍼안정화된 증폭기 및 초퍼안정화된 증폭기를 동작시키는 방법 Download PDFInfo

- Publication number

- KR101010501B1 KR101010501B1 KR1020087020774A KR20087020774A KR101010501B1 KR 101010501 B1 KR101010501 B1 KR 101010501B1 KR 1020087020774 A KR1020087020774 A KR 1020087020774A KR 20087020774 A KR20087020774 A KR 20087020774A KR 101010501 B1 KR101010501 B1 KR 101010501B1

- Authority

- KR

- South Korea

- Prior art keywords

- notch filter

- output

- signal

- input

- chopper

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45479—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection

- H03F3/45928—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection using IC blocks as the active amplifying circuit

- H03F3/45968—Differential amplifiers with semiconductor devices only characterised by the way of common mode signal rejection using IC blocks as the active amplifying circuit by offset reduction

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/02—Modifications of amplifiers to raise the efficiency, e.g. gliding Class A stages, use of an auxiliary oscillation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/26—Modifications of amplifiers to reduce influence of noise generated by amplifying elements

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/005—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements using switched capacitors, e.g. dynamic amplifiers; using switched capacitors as resistors in differential amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/38—Dc amplifiers with modulator at input and demodulator at output; Modulators or demodulators specially adapted for use in such amplifiers

- H03F3/387—Dc amplifiers with modulator at input and demodulator at output; Modulators or demodulators specially adapted for use in such amplifiers with semiconductor devices only

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H19/00—Networks using time-varying elements, e.g. N-path filters

- H03H19/004—Switched capacitor networks

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/261—Amplifier which being suitable for instrumentation applications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/459—Ripple reduction circuitry being used in an amplifying circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45212—Indexing scheme relating to differential amplifiers the differential amplifier being designed to have a reduced offset

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H11/00—Networks using active elements

- H03H11/02—Multiple-port networks

- H03H11/04—Frequency selective two-port networks

- H03H2011/0488—Notch or bandstop filters

Abstract

Description

Claims (14)

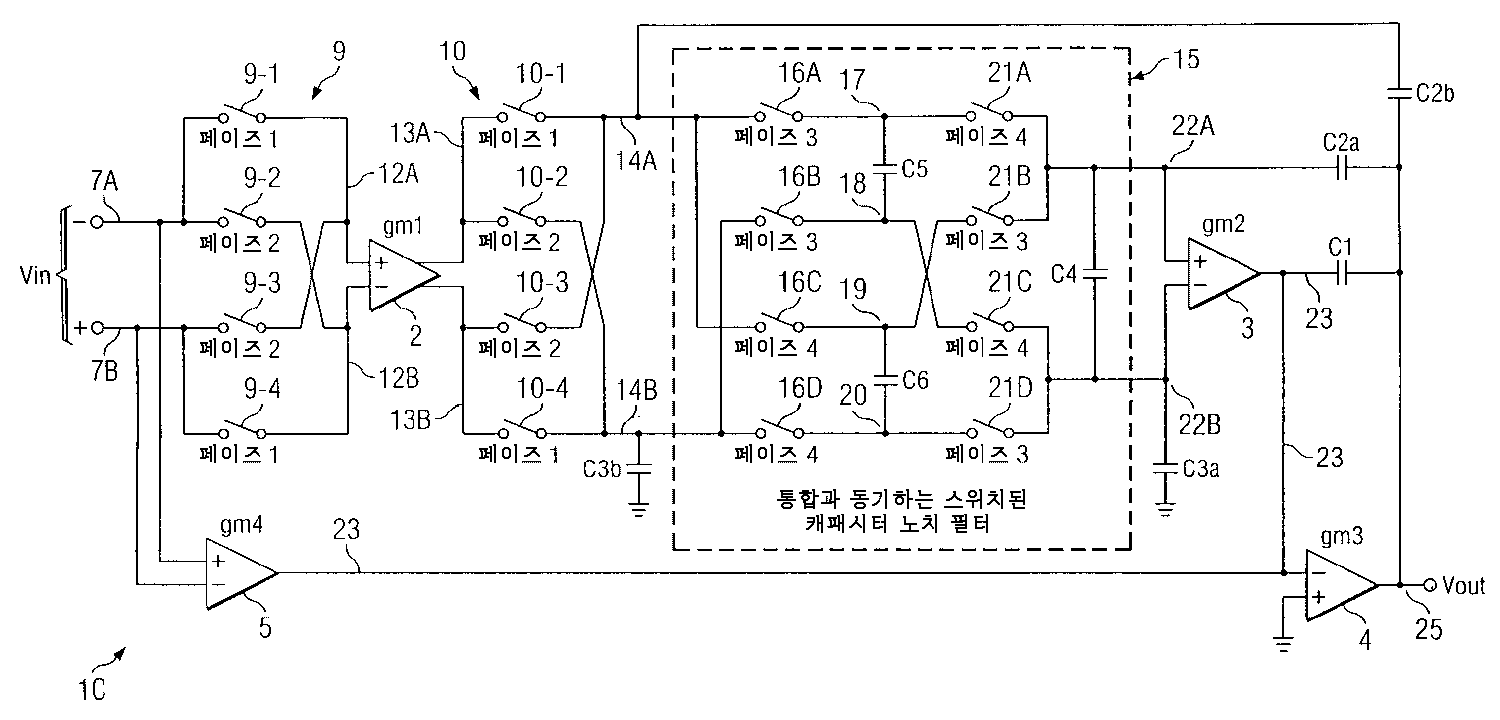

- 초퍼-안정화된 증폭기(chopper-stabilized amplifier)로서,(a) 제1 연산 트랜스컨덕턴스 증폭기(operational transconductance amplifier);(b) 상기 제1 연산 트랜스컨덕턴스 증폭기의 입력에 결합되며, 입력 신호를 초핑(chopping)하고 상기 초핑된 입력 신호를 상기 제1 연산 트랜스컨덕턴스 증폭기의 입력에 인가하기 위한 제1 초퍼 회로(chopper circuitry) 및, 상기 제1 연산 트랜스컨덕턴스 증폭기의 출력에 결합되며, 상기 제1 연산 트랜스컨덕턴스 증폭기에 의해 생성되는 출력 신호를 초핑하기 위한 제2 초퍼 회로; 및(c) 입력이 상기 제2 초퍼 회로의 출력에 결합되어 있고, 상기 제2 초퍼 회로에 의해 생성되는 초핑된 출력 신호에 대한 통합 및 전달 기능(integrate and transfer function)을 수행하며, 상기 제2 초퍼 회로의 초핑 주파수와 동기하여 동작하여, 노치 필터링(notch filter)하지 않을 경우 상기 제2 초퍼 회로의 출력에서 발생할 수 있는 리플 전압들(ripple voltages)을 노치 필터링함으로써 상기 제2 초퍼 회로에 의해 생성되는 초핑된 출력 신호를 필터링하는 스위치된 캐패시터 노치 필터(switched capacitor notch filter)를 포함하고,상기 노치 필터의 입력은 제1 및 제2 입력 단자들(terminals)을 포함하고, 상기 노치 필터는 제1 및 제2 출력 단자들을 포함하며, 상기 노치 필터는,i. 상기 제1 입력 단자와 제1 도체(conductor) 사이에서 결합되는 제1 스위치, 상기 제1 도체와 상기 제1 출력 단자 사이에서 결합되는 제2 스위치, 상기 제2 입력 단자와 제2 도체 사이에서 결합되는 제3 스위치, 및 상기 제2 도체와 상기 제2 출력 단자 사이에서 결합되는 제4 스위치를 포함하는 제1 경로(path),ii. 상기 제1 입력 단자와 제3 도체 사이에서 결합되는 제5 스위치, 상기 제3 도체와 상기 제1 출력 단자 사이에서 결합되는 제6 스위치, 상기 제2 입력 단자와 제4 도체 사이에서 결합되는 제7 스위치, 및 상기 제4 도체와 상기 제2 출력 단자 사이에서 결합되는 제8 스위치를 포함하는 제2 경로, 및,iii. 상기 제1 도체와 상기 제2 도체 사이에서 결합되는 제1 통합 및 전달 캐패시터(integrate and transfer capacitor) 및, 상기 제3 도체와 상기 제4 도체 사이에서 결합되는 제2 통합 및 전달 캐패시터를 포함하는 초퍼-안정화된 증폭기.

- 제1항에 있어서, 입력이 상기 노치 필터의 출력에 결합되는 제2 연산 트랜스 컨덕턴스 증폭기를 포함하는 초퍼-안정화된 증폭기.

- 삭제

- 제2항에 있어서, 상기 제1, 제3, 제6 및 제8 스위치들은 제1 클럭 신호에 의해 제어되며, 상기 제2, 제4, 제5 및 제7 스위치들은 제2 클럭 신호에 의해 제어되며, 상기 제1 및 제2 클럭 신호들은 서로 위상이 어긋나 있는(the first and second clock signals are out of phase with each other) 초퍼-안정화된 증폭기.

- 제4항에 있어서, 상기 제1 및 상기 제2 클럭 신호들의 천이들(transitions)은 상기 제2 초퍼 회로의 초핑 신호의 천이들에 대하여 시프트(shift)되는 초퍼-안정화된 증폭기.

- 제5항에 있어서, 상기 제1 및 상기 제2 클럭 신호들의 천이들은 상기 제2 초퍼 회로의 초핑 신호의 천이들에 대하여 90˚만큼 시프트되는 초퍼-안정화된 증폭기.

- 제1항 또는 제2항에 있어서, 상기 노치 필터는, 상기 제2 초퍼 회로의 초핑 신호와 동기하여 동작하여, 상기 노치 필터의 입력에서의 전하가 상기 제1 클럭 신호 동안 상기 제1 통합 및 전달 캐패시터 상에서 그리고 상기 제2 클럭 신호 동안 상기 제2 통합 및 전달 캐패시터 상에서 통합되게 하고, 상기 제1 통합 및 전달 캐패시터 상에서 유지되는(held) 전하가 상기 제2 클럭 신호 동안 상기 노치 필터의 출력으로 전달되게 하고, 상기 제2 통합 및 전달 캐패시터 상에서 유지되는 전하로 하여금 상기 제1 클럭 신호 동안 상기 노치 필터의 출력으로 전달되게 하는 초퍼-안정화된 증폭기.

- 제2항에 있어서, 입력이 상기 제2 연산 트랜스컨덕턴스 증폭기의 출력에 결합되는 제3 연산 트랜스컨덕턴스 증폭기와, 입력이 상기 입력 신호를 수신하도록 결합되고 출력이 상기 제2 연산 트랜스컨덕턴스 증폭기의 출력에 결합되는 제4 연산 트랜스컨덕턴스 증폭기를 포함하는 초퍼-안정화된 증폭기.

- 제8항에 있어서, 상기 노치 필터의 입력 측에 그리고 상기 노치 필터의 출력 측에 결합되는 보상 캐패시턴스(compensation capacitance)를 포함하는 초퍼-안정화된 증폭기.

- 제9항에 있어서, 상기 노치 필터의 입력 측에 결합되는 보상 캐패시턴스의 양은, 상기 노치 필터의 출력 측에 결합되는 보상 캐패시턴스의 양보다 실질적으로 더 커서, 상기 초퍼-안정화된 증폭기에서의 안정성과 신속한 신호 세틀링(signal settling)을 제공하는 초퍼-안정화된 증폭기.

- 제1 연산 트랜스컨덕턴스 증폭기를 포함하는 초퍼-안정화된 증폭기를 동작시키는 방법으로서,(a) 입력 신호를 초핑하고, 상기 초핑된 입력 신호를 상기 제1 연산 트랜스컨덕턴스 증폭기의 입력에 인가하고, 상기 제1 연산 트랜스컨덕턴스 증폭기에 의해 생성되는 출력 신호를 초핑 주파수에서 초핑하여 초핑된 출력 신호를 생성하는 단계; 및(b) 노치 필터링하지 않을 경우 상기 초핑된 출력 신호에서 발생할 수 있는 리플 전압들을 노치 필터링하기 위해, 초핑 주파수와 동기하여 제2 초퍼 회로에 의해 생성되는 초핑된 출력 신호에 대해 통합 및 전달 기능을 수행함으로써, 입력이 상기 초핑된 출력 신호를 수신하도록 결합되어 있는 스위치된 캐패시터 노치 필터를 동작시키는 단계를 포함하고,상기 스위치된 캐패시터 노치 필터는 제1 스위치 신호 경로 및 제2 스위치 신호 경로를 포함하고, 상기 제1 스위치 신호 경로는 제1 통합 및 전달 캐패시터를 포함하고, 상기 제2 스위치 신호 경로는 제2 통합 및 전달 캐패시터를 포함하며,상기 스위치된 캐패시터 노치 필터를 동작시키는 단계는노치 필터 스위칭 사이클의 절반 동안, 상기 제1 스위치 신호 경로는 상기 제1 통합 및 전달 캐패시터를 이용하여 상기 제1 연산 트랜스컨덕턴스 증폭기로부터의 증폭되고 초핑된 신호를 통합하는 단계,동일한 간격 동안, 상기 제2 스위치 신호 경로는 상기 제2 통합 및 전달 캐패시터에서 제2 연산 트랜스컨덕턴스 증폭기로 증폭된 신호를 전달하는 단계, 및상기 스위치된 캐패시터 노치 필터의 동작 사이클의 다음 절반 동안, 상기 두 개의 신호 경로의 통합 및 전달 기능이 역으로 되는 단계를 포함하는 초퍼-안정화된 증폭기 동작 방법.

- 제11항에 있어서, 상기 스위치된 캐패시터 노치 필터의 스위칭은, 상기 제1 연산 트랜스컨덕턴스 증폭기에 의해 생성되는 출력 신호의 초핑과 90˚ 만큼 위상이 어긋나 있는(switching of the switched capacitor notch filter is 90 degrees out of phase with the chopping of the output signal produced by the first operational transconductance amplifier) 초퍼-안정화된 증폭기 동작 방법.

- 제11항 또는 제12항에 있어서, 신호 전하의 손실 없이 상기 통합 및 전달 기능을 수행하는 단계를 포함하는 초퍼-안정화된 증폭기 동작 방법.

- 삭제

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/340,223 US7292095B2 (en) | 2006-01-26 | 2006-01-26 | Notch filter for ripple reduction in chopper stabilized amplifiers |

| US11/340,223 | 2006-01-26 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20080091376A KR20080091376A (ko) | 2008-10-10 |

| KR101010501B1 true KR101010501B1 (ko) | 2011-01-21 |

Family

ID=38284943

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020087020774A KR101010501B1 (ko) | 2006-01-26 | 2007-01-26 | 초퍼안정화된 증폭기 및 초퍼안정화된 증폭기를 동작시키는 방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7292095B2 (ko) |

| EP (1) | EP1982411B1 (ko) |

| KR (1) | KR101010501B1 (ko) |

| CN (1) | CN101536306B (ko) |

| WO (1) | WO2007087630A2 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9762227B2 (en) | 2014-07-28 | 2017-09-12 | Samsung Electronics Co., Ltd. | Apparatus and method for processing signal |

Families Citing this family (120)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007049285A (ja) * | 2005-08-08 | 2007-02-22 | Seiko Instruments Inc | チョッパアンプ回路および半導体装置 |

| US7463087B2 (en) * | 2005-10-27 | 2008-12-09 | International Rectifier Corporation | Operational amplifier with zero offset |

| KR100921517B1 (ko) * | 2006-12-05 | 2009-10-15 | 한국전자통신연구원 | Nauta 연산 상호 컨덕턴스 증폭기 |

| US7495508B2 (en) * | 2007-03-12 | 2009-02-24 | Texas Instruments Incorporated | Switched capacitor notch filter circuits |

| US8099073B1 (en) * | 2007-05-22 | 2012-01-17 | Marvell International Ltd. | Noise reduction in amplifier circuitry using single-sideband chopper stabilization |

| US9356568B2 (en) | 2007-06-05 | 2016-05-31 | Analog Devices, Inc. | Apparatus and methods for chopper amplifiers |

| US7605646B2 (en) * | 2007-07-06 | 2009-10-20 | Texas Instruments Incorporated | Low glitch offset correction circuit for auto-zero sensor amplifiers and method |

| US7518440B1 (en) * | 2007-11-26 | 2009-04-14 | Texas Instruments Incorporated | Dual path chopper stabilized amplifier and method |

| US7586368B2 (en) * | 2007-12-13 | 2009-09-08 | Texas Instruments Incorproated | Simultaneous filtering and compensation circuitry and method in chopping amplifier |

| US9823090B2 (en) | 2014-10-31 | 2017-11-21 | Allegro Microsystems, Llc | Magnetic field sensor for sensing a movement of a target object |

| US7605647B1 (en) * | 2008-04-29 | 2009-10-20 | Allegro Microsystems, Inc. | Chopper-stabilized amplifier and magnetic field sensor |

| US7733169B2 (en) * | 2008-05-07 | 2010-06-08 | Texas Instruments Incorporated | Slew rate and settling time improvement circuitry and method for 3-stage amplifier |

| TWI372957B (en) * | 2008-05-20 | 2012-09-21 | Novatek Microelectronics Corp | Current generator |

| US7724080B2 (en) * | 2008-06-11 | 2010-05-25 | Intersil Americas Inc. | Chopper stabilized amplifier |

| US7764118B2 (en) * | 2008-09-11 | 2010-07-27 | Analog Devices, Inc. | Auto-correction feedback loop for offset and ripple suppression in a chopper-stabilized amplifier |

| US7839212B2 (en) * | 2008-12-04 | 2010-11-23 | Oracle America, Inc. | Method and apparatus for a high bandwidth amplifier with wide band peaking |

| US8447556B2 (en) * | 2009-02-17 | 2013-05-21 | Allegro Microsystems, Inc. | Circuits and methods for generating a self-test of a magnetic field sensor |

| JP2010283713A (ja) * | 2009-06-08 | 2010-12-16 | Sanyo Electric Co Ltd | オフセットキャンセル回路 |

| US7990209B2 (en) * | 2009-06-19 | 2011-08-02 | Allegro Microsystems, Inc. | Switched capacitor notch filter |

| JP5620989B2 (ja) | 2009-07-22 | 2014-11-05 | アレグロ・マイクロシステムズ・エルエルシー | 磁界センサの診断動作モードを生成するための回路および方法 |

| US7952428B2 (en) * | 2009-08-18 | 2011-05-31 | Intersil Americas Inc. | Dynamically adjustable low noise, low power instrumentation amplifier |

| US8125262B2 (en) * | 2009-08-19 | 2012-02-28 | Analog Devices, Inc. | Low power and low noise switched capacitor integrator with flexible input common mode range |

| KR101087246B1 (ko) | 2009-09-10 | 2011-11-29 | 연세대학교 산학협력단 | 스위치드 커패시터 회로 |

| US7888996B1 (en) | 2009-10-27 | 2011-02-15 | Texas Instruments Incorporated | Chopper stabilized operational amplifier |

| US8416014B2 (en) * | 2010-03-12 | 2013-04-09 | Allegro Microsystems, Inc. | Switched capacitor notch filter with fast response time |

| GB201006212D0 (en) | 2010-04-14 | 2010-06-02 | Rolls Royce Goodrich Engine Co | A signal processing circuit |

| US8072262B1 (en) | 2010-06-28 | 2011-12-06 | Texas Instruments Incorporated | Low input bias current chopping switch circuit and method |

| US8258863B2 (en) * | 2011-01-05 | 2012-09-04 | Texas Instruments Incorporated | Circuit and method for reducing input leakage in chopped amplifier during overload conditions |

| US8228130B1 (en) | 2011-02-15 | 2012-07-24 | Texas Instruments Incorporated | Circuitry and method for precision amplitude control in quartz and MEMS oscillators |

| US8576002B2 (en) * | 2011-03-21 | 2013-11-05 | Analog Devices, Inc. | ADC preamplifier and the multistage auto-zero technique |

| US8680846B2 (en) | 2011-04-27 | 2014-03-25 | Allegro Microsystems, Llc | Circuits and methods for self-calibrating or self-testing a magnetic field sensor |

| US8624668B2 (en) | 2011-07-12 | 2014-01-07 | Analog Devices, Inc. | Common-mode step response for autozero amplifiers |

| ITFO20110009A1 (it) * | 2011-08-12 | 2013-02-13 | Marco Bennati | Apparato e metodo di riduzione del rumore in amplificatori a tempo campionato. |

| US10720919B2 (en) | 2011-11-16 | 2020-07-21 | Analog Devices, Inc. | Apparatus and methods for reducing charge injection mismatch in electronic circuits |

| CN102545808B (zh) * | 2012-01-17 | 2015-10-21 | 辉芒微电子(深圳)有限公司 | 误差放大器、控制器和原边反馈控制ac/dc转换器 |

| US9201122B2 (en) | 2012-02-16 | 2015-12-01 | Allegro Microsystems, Llc | Circuits and methods using adjustable feedback for self-calibrating or self-testing a magnetic field sensor with an adjustable time constant |

| US9817078B2 (en) | 2012-05-10 | 2017-11-14 | Allegro Microsystems Llc | Methods and apparatus for magnetic sensor having integrated coil |

| US8638166B2 (en) * | 2012-06-13 | 2014-01-28 | Analog Devices, Inc. | Apparatus and methods for notch filtering |

| US8786363B2 (en) | 2012-06-13 | 2014-07-22 | Analog Devices, Inc. | Apparatus and methods for electronic amplification |

| US9817083B2 (en) | 2012-07-05 | 2017-11-14 | Allegro Microsystems, Llc | Magnetic field sensors and associated methods for removing undesirable spectral components |

| US9383425B2 (en) | 2012-12-28 | 2016-07-05 | Allegro Microsystems, Llc | Methods and apparatus for a current sensor having fault detection and self test functionality |

| US9116164B2 (en) * | 2013-03-07 | 2015-08-25 | Robert Bosch Gmbh | Pseudo-differential accelerometer with high electromagnetic interference rejection |

| US10725100B2 (en) | 2013-03-15 | 2020-07-28 | Allegro Microsystems, Llc | Methods and apparatus for magnetic sensor having an externally accessible coil |

| KR101535332B1 (ko) * | 2013-03-29 | 2015-07-09 | 한양대학교 산학협력단 | 전류 궤환 계측 증폭기 |

| JP6363822B2 (ja) * | 2013-05-15 | 2018-07-25 | ルネサスエレクトロニクス株式会社 | 信号処理回路、およびレゾルバデジタルコンバータ |

| US10145908B2 (en) | 2013-07-19 | 2018-12-04 | Allegro Microsystems, Llc | Method and apparatus for magnetic sensor producing a changing magnetic field |

| US9810519B2 (en) | 2013-07-19 | 2017-11-07 | Allegro Microsystems, Llc | Arrangements for magnetic field sensors that act as tooth detectors |

| US10495699B2 (en) | 2013-07-19 | 2019-12-03 | Allegro Microsystems, Llc | Methods and apparatus for magnetic sensor having an integrated coil or magnet to detect a non-ferromagnetic target |

| US9240718B2 (en) | 2013-08-15 | 2016-01-19 | Linear Technology Corporation | Accurate current sensing in H-bridge applications without amplifier having high common mode rejection ratio |

| CN104601127A (zh) * | 2013-10-31 | 2015-05-06 | 上海华虹集成电路有限责任公司 | 运算放大器电路及基准电压产生电路模块 |

| GB2521416B (en) * | 2013-12-19 | 2017-02-01 | Cirrus Logic Int Semiconductor Ltd | Biasing circuitry for MEMS transducers |

| US9391571B2 (en) * | 2014-01-20 | 2016-07-12 | Semiconductor Components Industries, Llc | Chopper-stabilized amplifier and method therefor |

| US9645220B2 (en) | 2014-04-17 | 2017-05-09 | Allegro Microsystems, Llc | Circuits and methods for self-calibrating or self-testing a magnetic field sensor using phase discrimination |

| US9735773B2 (en) | 2014-04-29 | 2017-08-15 | Allegro Microsystems, Llc | Systems and methods for sensing current through a low-side field effect transistor |

| US20150333716A1 (en) | 2014-05-13 | 2015-11-19 | Mediatek Inc. | Method and apparatus for performing signal amplifying with aid of switching control |

| US9634617B2 (en) | 2014-07-02 | 2017-04-25 | Texas Instruments Incorporated | Multistage amplifier circuit with improved settling time |

| US9685933B2 (en) | 2014-08-25 | 2017-06-20 | Linear Technology Corporation | Notch filter for ripple reduction |

| US9739846B2 (en) | 2014-10-03 | 2017-08-22 | Allegro Microsystems, Llc | Magnetic field sensors with self test |

| US10712403B2 (en) | 2014-10-31 | 2020-07-14 | Allegro Microsystems, Llc | Magnetic field sensor and electronic circuit that pass amplifier current through a magnetoresistance element |

| US9823092B2 (en) | 2014-10-31 | 2017-11-21 | Allegro Microsystems, Llc | Magnetic field sensor providing a movement detector |

| US9719806B2 (en) | 2014-10-31 | 2017-08-01 | Allegro Microsystems, Llc | Magnetic field sensor for sensing a movement of a ferromagnetic target object |

| US9720054B2 (en) | 2014-10-31 | 2017-08-01 | Allegro Microsystems, Llc | Magnetic field sensor and electronic circuit that pass amplifier current through a magnetoresistance element |

| US10466298B2 (en) | 2014-11-14 | 2019-11-05 | Allegro Microsystems, Llc | Magnetic field sensor with shared path amplifier and analog-to-digital-converter |

| US9804249B2 (en) | 2014-11-14 | 2017-10-31 | Allegro Microsystems, Llc | Dual-path analog to digital converter |

| US9641142B2 (en) | 2014-12-11 | 2017-05-02 | Texas Instruments Incorporated | Hot-swap current-sensing system |

| US9893705B2 (en) * | 2014-12-31 | 2018-02-13 | General Electric Company | Method and apparatus for dual notch ripple filtering |

| US9614481B2 (en) | 2015-03-31 | 2017-04-04 | Analog Devices, Inc. | Apparatus and methods for chopping ripple reduction in amplifiers |

| US9638764B2 (en) | 2015-04-08 | 2017-05-02 | Allegro Microsystems, Llc | Electronic circuit for driving a hall effect element with a current compensated for substrate stress |

| US9473074B1 (en) * | 2015-09-14 | 2016-10-18 | Ixys Corporation | Chopper stabilized amplifier with synchronous switched capacitor noise filtering |

| TW201713032A (zh) * | 2015-09-17 | 2017-04-01 | 力智電子股份有限公司 | 前置放大器 |

| JP6758037B2 (ja) * | 2015-10-16 | 2020-09-23 | ローム株式会社 | チョッパ安定化アンプ |

| US10107873B2 (en) | 2016-03-10 | 2018-10-23 | Allegro Microsystems, Llc | Electronic circuit for compensating a sensitivity drift of a hall effect element due to stress |

| KR102637488B1 (ko) | 2016-05-18 | 2024-02-20 | 삼성디스플레이 주식회사 | 전원 공급 장치 및 이를 갖는 표시장치 |

| US10012518B2 (en) | 2016-06-08 | 2018-07-03 | Allegro Microsystems, Llc | Magnetic field sensor for sensing a proximity of an object |

| US10041810B2 (en) | 2016-06-08 | 2018-08-07 | Allegro Microsystems, Llc | Arrangements for magnetic field sensors that act as movement detectors |

| US10260905B2 (en) | 2016-06-08 | 2019-04-16 | Allegro Microsystems, Llc | Arrangements for magnetic field sensors to cancel offset variations |

| US10162017B2 (en) | 2016-07-12 | 2018-12-25 | Allegro Microsystems, Llc | Systems and methods for reducing high order hall plate sensitivity temperature coefficients |

| CN106208978B (zh) * | 2016-07-14 | 2019-03-01 | 清华大学 | 基于斩波稳定技术的亚阈值衬底驱动运算跨导放大器 |

| US10097146B2 (en) | 2016-09-29 | 2018-10-09 | Semiconductor Components Industries, Llc | Ripple reduction method for chopper amplifiers |

| US10310028B2 (en) | 2017-05-26 | 2019-06-04 | Allegro Microsystems, Llc | Coil actuated pressure sensor |

| US10641842B2 (en) | 2017-05-26 | 2020-05-05 | Allegro Microsystems, Llc | Targets for coil actuated position sensors |

| US10996289B2 (en) | 2017-05-26 | 2021-05-04 | Allegro Microsystems, Llc | Coil actuated position sensor with reflected magnetic field |

| US10324141B2 (en) | 2017-05-26 | 2019-06-18 | Allegro Microsystems, Llc | Packages for coil actuated position sensors |

| US10837943B2 (en) | 2017-05-26 | 2020-11-17 | Allegro Microsystems, Llc | Magnetic field sensor with error calculation |

| US11428755B2 (en) | 2017-05-26 | 2022-08-30 | Allegro Microsystems, Llc | Coil actuated sensor with sensitivity detection |

| CN109212258B (zh) * | 2017-07-03 | 2021-04-13 | 无锡华润上华科技有限公司 | 加速度计的前端电路及加速度信号处理方法 |

| US10520559B2 (en) | 2017-08-14 | 2019-12-31 | Allegro Microsystems, Llc | Arrangements for Hall effect elements and vertical epi resistors upon a substrate |

| US10444299B2 (en) | 2017-09-11 | 2019-10-15 | Allegro Microsystems, Llc | Magnetic field sensor's front end and associated mixed signal method for removing chopper's related ripple |

| US10481219B2 (en) | 2017-09-11 | 2019-11-19 | Allegro Microsystems, Llc | Magnetic field sensor with feedback loop for test signal processing |

| US10673389B2 (en) | 2017-11-20 | 2020-06-02 | Linear Technology Holding Llc | Chopper amplifiers with high pass filter for suppressing chopping ripple |

| US10530302B2 (en) | 2017-11-21 | 2020-01-07 | Texas Instruments Incorporated | Current mode chopper amplifier |

| US10411664B2 (en) | 2017-12-29 | 2019-09-10 | Semiconductor Components Industries, Llc | Chopper-stabilized amplifier with analog-driven level shifter |

| US10866117B2 (en) | 2018-03-01 | 2020-12-15 | Allegro Microsystems, Llc | Magnetic field influence during rotation movement of magnetic target |

| CN108494370B (zh) * | 2018-05-31 | 2023-12-29 | 福州大学 | 斩波稳定仪表放大器 |

| JP6505297B2 (ja) * | 2018-06-26 | 2019-04-24 | ルネサスエレクトロニクス株式会社 | マルチパスネステッドミラー増幅回路 |

| US11255700B2 (en) | 2018-08-06 | 2022-02-22 | Allegro Microsystems, Llc | Magnetic field sensor |

| US10931247B2 (en) | 2018-09-28 | 2021-02-23 | Texas Instruments Incorporated | Chopper amplifier |

| US10756685B2 (en) * | 2018-09-28 | 2020-08-25 | Texas Instruments Incorporated | Chopper amplifier with decoupled chopping frequency and threshold frequency |

| US10911004B2 (en) | 2018-10-12 | 2021-02-02 | Texas Instruments Incorporated | Sampled moving average notch filter for ripple reduction in chopper stabilized operational amplifiers |

| US10823586B2 (en) | 2018-12-26 | 2020-11-03 | Allegro Microsystems, Llc | Magnetic field sensor having unequally spaced magnetic field sensing elements |

| US10958226B2 (en) | 2019-02-15 | 2021-03-23 | Semiconductor Components Industries, Llc | Method of forming a semiconductor device and structure therefor |

| US11061084B2 (en) | 2019-03-07 | 2021-07-13 | Allegro Microsystems, Llc | Coil actuated pressure sensor and deflectable substrate |

| US11047933B2 (en) | 2019-04-02 | 2021-06-29 | Allegro Microsystems, Llc | Fast response magnetic field sensors and associated methods for removing undesirable spectral components |

| US10955306B2 (en) | 2019-04-22 | 2021-03-23 | Allegro Microsystems, Llc | Coil actuated pressure sensor and deformable substrate |

| WO2021076685A1 (en) * | 2019-10-18 | 2021-04-22 | Massachusetts Institute Of Technology | Systems and methods for suppressing even harmonics in a molecular clock |

| WO2021080957A1 (en) | 2019-10-24 | 2021-04-29 | Massachusetts Institute Of Technology | Integrated circuit-to-waveguide slot array coupler |

| US11237020B2 (en) | 2019-11-14 | 2022-02-01 | Allegro Microsystems, Llc | Magnetic field sensor having two rows of magnetic field sensing elements for measuring an angle of rotation of a magnet |

| US11280637B2 (en) | 2019-11-14 | 2022-03-22 | Allegro Microsystems, Llc | High performance magnetic angle sensor |

| CN111049492B (zh) * | 2019-12-20 | 2023-04-07 | 中国科学院合肥物质科学研究院 | 一种斩波式数字积分电路的丢点补偿电路 |

| US11194004B2 (en) | 2020-02-12 | 2021-12-07 | Allegro Microsystems, Llc | Diagnostic circuits and methods for sensor test circuits |

| US11169223B2 (en) | 2020-03-23 | 2021-11-09 | Allegro Microsystems, Llc | Hall element signal calibrating in angle sensor |

| CN111464136B (zh) * | 2020-04-20 | 2023-08-11 | 上海传泰电子科技有限公司 | 一种集成斩波和自动调零的高精度运算放大电路 |

| US11262422B2 (en) | 2020-05-08 | 2022-03-01 | Allegro Microsystems, Llc | Stray-field-immune coil-activated position sensor |

| CN111697928B (zh) * | 2020-06-15 | 2023-01-31 | 电子科技大学 | 一种电容耦合斩波放大器 |

| US11493361B2 (en) | 2021-02-26 | 2022-11-08 | Allegro Microsystems, Llc | Stray field immune coil-activated sensor |

| US11630130B2 (en) | 2021-03-31 | 2023-04-18 | Allegro Microsystems, Llc | Channel sensitivity matching |

| US11909364B2 (en) * | 2021-05-25 | 2024-02-20 | Cypress Semiconductor Corporation | Fast start up control circuit |

| CN113746491B (zh) * | 2021-07-19 | 2022-07-08 | 成都通量科技有限公司 | 一种适用于零中频接收机的隔直电容补偿系统 |

| US11578997B1 (en) | 2021-08-24 | 2023-02-14 | Allegro Microsystems, Llc | Angle sensor using eddy currents |

| CN114745001B (zh) * | 2022-06-10 | 2023-04-07 | 芯海科技(深圳)股份有限公司 | 模数转换器、芯片、电子设备以及模数转换方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20040140922A1 (en) * | 2003-01-21 | 2004-07-22 | Melanson John L. | Signal processing system with baseband noise modulation and noise filtering |

| US20040140847A1 (en) * | 2003-01-21 | 2004-07-22 | Karl Thompson | Segmented chopping amplifier |

| KR20050053515A (ko) * | 2003-12-03 | 2005-06-08 | 로무 가부시키가이샤 | gm 증폭기를 이용한 액티브 필터 회로, 이를 이용한데이터 독출 회로, 데이터 기록 회로 및 데이터 재생 장치 |

| US7233198B2 (en) | 2002-12-18 | 2007-06-19 | Nxp B.V. | Phase corrected miller compensation of chopper and nested chopper amplifiers |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4138649A (en) * | 1977-03-25 | 1979-02-06 | Emerson Electric Co. | Amplifier system |

| GB8818703D0 (en) * | 1988-08-05 | 1988-09-07 | Gen Electric Co Plc | Delta sigma modulator arrangements |

| US5382956A (en) * | 1992-04-30 | 1995-01-17 | Hewlett Packard Co | Integrated circuit for physiological signal measurement |

| US5663680A (en) * | 1996-04-04 | 1997-09-02 | Nordeng; Arnold E. | Chopper stabilized amplifier having an additional differential amplifier stage for improved noise reduction |

| US6351506B1 (en) | 1999-04-19 | 2002-02-26 | National Semiconductor Corporation | Switched capacitor filter circuit having reduced offsets and providing offset compensation when used in a closed feedback loop |

| WO2003036791A1 (en) * | 2001-10-25 | 2003-05-01 | Koninklijke Philips Electronics N.V. | Operational amplifier with chopped input transistor pair |

| US7202738B1 (en) * | 2005-02-08 | 2007-04-10 | Maxim Integrated Products, Inc. | Accurate voltage to current converters for rail-sensing current-feedback instrumentation amplifiers |

| US7132883B2 (en) * | 2005-02-08 | 2006-11-07 | Maxim Integrated Products, Inc. | Chopper chopper-stabilized instrumentation and operational amplifiers |

-

2006

- 2006-01-26 US US11/340,223 patent/US7292095B2/en active Active

-

2007

- 2007-01-26 WO PCT/US2007/061139 patent/WO2007087630A2/en active Application Filing

- 2007-01-26 CN CN2007800105586A patent/CN101536306B/zh active Active

- 2007-01-26 KR KR1020087020774A patent/KR101010501B1/ko active IP Right Grant

- 2007-01-26 EP EP07762382.5A patent/EP1982411B1/en not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7233198B2 (en) | 2002-12-18 | 2007-06-19 | Nxp B.V. | Phase corrected miller compensation of chopper and nested chopper amplifiers |

| US20040140922A1 (en) * | 2003-01-21 | 2004-07-22 | Melanson John L. | Signal processing system with baseband noise modulation and noise filtering |

| US20040140847A1 (en) * | 2003-01-21 | 2004-07-22 | Karl Thompson | Segmented chopping amplifier |

| KR20050053515A (ko) * | 2003-12-03 | 2005-06-08 | 로무 가부시키가이샤 | gm 증폭기를 이용한 액티브 필터 회로, 이를 이용한데이터 독출 회로, 데이터 기록 회로 및 데이터 재생 장치 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9762227B2 (en) | 2014-07-28 | 2017-09-12 | Samsung Electronics Co., Ltd. | Apparatus and method for processing signal |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20080091376A (ko) | 2008-10-10 |

| US20070170981A1 (en) | 2007-07-26 |

| EP1982411A4 (en) | 2009-05-13 |

| WO2007087630A2 (en) | 2007-08-02 |

| EP1982411A2 (en) | 2008-10-22 |

| CN101536306A (zh) | 2009-09-16 |

| CN101536306B (zh) | 2012-03-28 |

| US7292095B2 (en) | 2007-11-06 |

| WO2007087630A3 (en) | 2008-11-06 |

| EP1982411B1 (en) | 2018-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101010501B1 (ko) | 초퍼안정화된 증폭기 및 초퍼안정화된 증폭기를 동작시키는 방법 | |

| US8072262B1 (en) | Low input bias current chopping switch circuit and method | |

| US7518440B1 (en) | Dual path chopper stabilized amplifier and method | |

| US7764118B2 (en) | Auto-correction feedback loop for offset and ripple suppression in a chopper-stabilized amplifier | |

| US20200091880A1 (en) | Chopper stabilized amplifier with parallel notch filters | |

| US7733169B2 (en) | Slew rate and settling time improvement circuitry and method for 3-stage amplifier | |

| EP2819306A1 (en) | Instrumentation amplifier and signal amplification method | |

| US10911004B2 (en) | Sampled moving average notch filter for ripple reduction in chopper stabilized operational amplifiers | |

| TWI451692B (zh) | 擬差動切換電容電路 | |

| US5909131A (en) | Low-distortion technique to bandlimit a switched-capacitor sampling circuit | |

| US7888996B1 (en) | Chopper stabilized operational amplifier | |

| WO2022049888A1 (ja) | 半導体回路 | |

| EP2293434B1 (en) | Switched amplifier circuit arrangement and method for switched amplification | |

| Sun et al. | A gain-enhanced two-stage fully-differential CMOS op amp with high unity-gain bandwidth | |

| JP3824867B2 (ja) | アナログ信号処理装置 | |

| Liu et al. | A switched-capacitor closed-loop integration sampling front-end for peripheral nerve recording | |

| Leung et al. | Optimum nested Miller compensation for low-voltage low-power CMOS amplifier design | |

| Kusuda | Techniques of Reducing Switching Artifacts in Chopper Amplifiers | |

| Ivanisevic et al. | Area-Efficient Switched-Capacitor Integrator with Flicker Noise Cancellation | |

| US11973476B2 (en) | Chopper amplifiers with low intermodulation distortion | |

| WO2022128289A1 (en) | Differential amplifier arrangement and converter arrangement | |

| JPH051509B2 (ko) | ||

| Hovhannisyan et al. | On-chip Area Effеctive Capacitor Design for Biopotential Recording Systems | |

| Wang et al. | A 10 th order SC band-pass filter and its smooth filter design | |

| Jaya et al. | An ultra low-power cmos emg amplifier with high efficiency in operation frequency per power |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20131227 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20141230 Year of fee payment: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20151230 Year of fee payment: 6 |

|

| FPAY | Annual fee payment |

Payment date: 20161229 Year of fee payment: 7 |

|

| FPAY | Annual fee payment |

Payment date: 20171228 Year of fee payment: 8 |

|

| FPAY | Annual fee payment |

Payment date: 20181227 Year of fee payment: 9 |