以下、本開示における実施形態について、図面を参照して詳細に説明する。以下で説明する実施形態は本開示の一具体例であって、本開示にかかる技術が以下の態様に限定されるものではない。また、本開示の各図に示す各構成要素の配置、寸法、及び寸法比等についても、各図に示すものに限定されるものではない。

なお、説明は以下の順序で行う。

1.撮像装置の構成

2.本開示に係る技術

3.変形例

4.具体例

4.1.実施の形態(3つの基板の積層構造を有する撮像装置)

4.2.変形例1(平面構成の例1)

4.3.変形例2(平面構成の例2)

4.4.変形例3(平面構成の例3)

4.5.変形例4(画素アレイ部の中央部に基板間のコンタクト部を有する例)

4.6.変形例5(プレーナー型の転送トランジスタを有する例)

4.7.変形例6(1つの画素回路に1つの画素が接続される例)

4.8.変形例7(画素分離部の構成例)

4.9.適用例(撮像システム)

4.10.応用例

<<1.撮像装置の構成>>

まず、図1~図13を参照して、本開示に係る技術が適用される撮像装置について説明する。

図1は、本開示の一実施形態に係る撮像装置1の概略構成の一例を示す模式図である。図1に示すように、撮像装置1は、第1基板10、第2基板20、及び第3基板30を備え、これらの3つの基板を貼り合わせることで構成された三次元構造の撮像装置である。なお、第1基板10、第2基板20、及び第3基板30は、この順で積層される。

第1基板10は、光電変換を行う複数のセンサ画素12を有する第1半導体基板11を含む。複数のセンサ画素12は、第1基板10の画素領域13の内部に行列状に配置されて設けられる。

第2基板20は、センサ画素12からの電荷に基づいて画素信号を出力する画素回路22を有する第2半導体基板21を含む。画素回路22は、例えば、4つのセンサ画素12ごとに1つずつ設けられ、4つのセンサ画素12から光電変換された電荷を順次読み出す読み出し回路である。また、第2基板20は、行方向に延伸する複数の画素駆動線23と、列方向に延伸する複数の垂直信号線24とを備える。

第3基板30は、画素信号を信号処理する処理回路32を有する第3半導体基板31を含む。また、処理回路32は、例えば、垂直駆動回路33、カラム信号処理回路34、水平駆動回路35、及びシステム制御回路36を有する。処理回路32は、センサ画素12ごとの出力電圧Voutを水平駆動回路35から外部に出力することができる。

垂直駆動回路33は、例えば、複数のセンサ画素12を行単位で順に選択する。カラム信号処理回路34は、例えば、垂直駆動回路33によって選択された行の各センサ画素12から出力される画素信号に対して、相関二重サンプリング処理を施す。例えば、カラム信号処理回路34は、相関二重サンプリング処理を施すことによって画素信号の信号レベルを抽出し、各センサ画素12の受光量に応じた画素データを保持することができる。水平駆動回路35は、例えば、カラム信号処理回路34に保持されている画素データを順次、外部に出力する。システム制御回路36は、例えば、処理回路32内の各構成の駆動を制御する。これによれば、処理回路32は、センサ画素12の各々の受光量に基づいた画素データを外部に出力することができる。

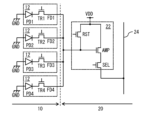

図2は、センサ画素12、及び画素回路22の一例を示す回路図である。図2に示す回路図では、4つのセンサ画素12が1つの画素回路22を共有している。ここでの「共有」とは、4つのセンサ画素12からの出力が共通の1つの画素回路22に入力されることを表す。

センサ画素12の各々は、互いに共通の構成要素を有する。以下では、センサ画素12の各々の構成要素を互いに区別する場合には、構成要素の符号の末尾に識別番号(1、2、3、4)を付与する。一方、センサ画素12の各々を互いに区別しない場合には、構成要素の符号の末尾への識別番号の付与は省略する。

センサ画素12は、例えば、フォトダイオードPDと、フォトダイオードPDに電気的に接続された転送トランジスタTRと、転送トランジスタTRを介してフォトダイオードPDから出力された電荷を一時的に保持するフローティングディフュージョンFDとを有する。フォトダイオードPDは、光電変換を行うことで、受光量に応じた電荷を発生させる光電変換素子である。転送トランジスタTRは、例えば、MOS(Metal Oxide Semiconductor)トランジスタである。

フォトダイオードPDのカソードは、転送トランジスタTRのソースに電気的に接続され、フォトダイオードPDのアノードは、基準電位線に電気的に接続される。転送トランジスタTRのドレインは、フローティングディフュージョンFDに電気的に接続され、転送トランジスタTRのゲートは、画素駆動線23に電気的に接続される。

画素回路22を共有するセンサ画素12の各々のフローティングディフュージョンFDは、互いに電気的に接続され、かつ共通の画素回路22の入力端に電気的に接続される。画素回路22は、例えば、リセットトランジスタRSTと、選択トランジスタSELと、増幅トランジスタAMPとを有する。さらに、画素回路22は、選択トランジスタSELを任意で有する。

リセットトランジスタRSTのソース(すなわち、画素回路22の入力端)は、フローティングディフュージョンFDに電気的に接続され、リセットトランジスタRSTのドレインは、電源線VDD、及び増幅トランジスタAMPのドレインに電気的に接続され、リセットトランジスタRSTのゲートは、画素駆動線23に電気的に接続される。増幅トランジスタAMPのソースは、選択トランジスタSELのドレインに電気的に接続され、増幅トランジスタAMPのゲートは、リセットトランジスタRSTのソースに電気的に接続される。選択トランジスタSELのソース(すなわち、画素回路22の出力端)は、垂直信号線24に電気的に接続され、選択トランジスタSELのゲートは、画素駆動線23に電気的に接続される。

オン状態となった転送トランジスタTRは、フォトダイオードPDにて光電変換された電荷をフローティングディフュージョンFDに転送する。リセットトランジスタRSTは、フローティングディフュージョンFDの電位を所定の電位にリセットする。オン状態となったリセットトランジスタRSTは、フローティングディフュージョンFDの電位を電源線VDDの電位にリセットする。選択トランジスタSELは、画素回路22からの画素信号の出力タイミングを制御する。

増幅トランジスタAMPは、フローティングディフュージョンFDに保持された電荷のレベルに応じた電圧の信号を画素信号として生成する。増幅トランジスタAMPは、いわゆるソースフォロア型の増幅器を構成しており、フォトダイオードPDで発生した電荷のレベルに応じた電圧の画素信号を出力する。選択トランジスタSELがオン状態となった場合、増幅トランジスタAMPは、フローティングディフュージョンFDの電位を増幅し、垂直信号線24を介して、増幅した電位に応じた電圧をカラム信号処理回路34に出力する。リセットトランジスタRST、増幅トランジスタAMP、及び選択トランジスタSELは、例えば、MOSトランジスタである。

図3~図5は、センサ画素12、及び画素回路22の他の例を示す回路図である。

図3に示すように、選択トランジスタSELは、電源線VDD、及び増幅トランジスタAMPの間に設けられてもよい。この場合、リセットトランジスタRSTのドレインは、電源線VDD、及び選択トランジスタSELのドレインに電気的に接続される。選択トランジスタSELのソースは、増幅トランジスタAMPのドレインに電気的に接続され、選択トランジスタSELのゲートは、画素駆動線23に電気的に接続される。増幅トランジスタAMPのソース(すなわち、画素回路22の出力端)は、垂直信号線24に電気的に接続され、増幅トランジスタAMPのゲートは、リセットトランジスタRSTのソースに電気的に接続される。

また、図4又は図5に示すように、リセットトランジスタRSTのソースと増幅トランジスタAMPのゲートとの間に、FD変換ゲイン切替トランジスタFDGがさらに設けられてもよい。

電荷Qは、容量Cと、電圧Vとの積で表されるため、フローティングディフュージョンFDの容量Cが大きい場合、増幅トランジスタAMPでの変換後の電圧Vが低くなってしまう。一方、画素信号の電荷Qが大きい場合、フローティングディフュージョンFDの容量Cが十分に大きくなければ、フローティングディフュージョンFDでフォトダイオードPDからの電荷Qを保持しきれなくなる。また、フローティングディフュージョンFDの容量Cは、増幅トランジスタAMPにて変換された電圧Vが過度に高くなりすぎないように、適度に大きいことも重要である。そこで、FD変換ゲイン切替トランジスタFDGは、画素回路22における電荷-電圧変換効率を切り替えるために設けられる。

FD変換ゲイン切替トランジスタFDGは、オン状態となることで、オフ状態と比較して、FD変換ゲイン切替トランジスタFDGのゲート容量の分だけフローティングディフュージョンFDの容量Cを大きくすることができる。したがって、FD変換ゲイン切替トランジスタFDGのオン又はオフの状態を切り替えてフローティングディフュージョンFDの容量Cを可変とすることで、画素回路22における電荷-電圧変換効率を切り替えることができる。

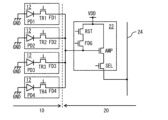

図6は、複数の画素回路22と、複数の垂直信号線24との接続の一例を示す回路図である。

図6に示すように、複数の画素回路22が垂直信号線24の延伸方向(例えば、列方向)に並んで配置されている場合、複数の垂直信号線24は、画素回路22ごとに1つずつ割り当てられてもよい。なお、図6では、垂直信号線24の各々を区別するために、垂直信号線24の各々の符号の末尾に識別番号(1、2、3、4)を付した。

図7は、撮像装置1の積層方向の断面構成の一例を示す縦断面図である。

図7に示すように、撮像装置1は、第1基板10、第2基板20、及び第3基板30をこの順に積層して構成される。第1基板10の光入射面側(裏面側ともいう)には、例えば、センサ画素12ごとにカラーフィルタ40、及び受光レンズ50がそれぞれ設けられる。すなわち、撮像装置1は、いわゆる裏面照射型の撮像装置である。

第1基板10は、第1半導体基板11上に第1絶縁層46を積層して構成される。第1半導体基板11は、シリコン基板であり、例えば、表面の一部及びその近傍に、pウェル層42を有し、それ以外の領域(すなわち、pウェル層42よりも深い領域)にフォトダイオードPDを有する。pウェル層42は、p型の半導体領域で構成され、フォトダイオードPDは、pウェル層42とは異なる導電型(具体的には、n型)の半導体領域で構成される。第1半導体基板11は、pウェル層42の内部にpウェル層42とは異なる導電型(具体的には、n型)の半導体領域であるフローティングディフュージョンFDを有する。

第1基板10は、センサ画素12ごとに、フォトダイオードPD、転送トランジスタTR、及びフローティングディフュージョンFDを有する。第1基板10は、第1半導体基板11の光入射面側と反対側(すなわち、表面側、又は第2基板20側)の部分に転送トランジスタTR、及びフローティングディフュージョンFDを有する。

第1基板10は、センサ画素12の各々を分離する素子分離部43を有する。素子分離部43は、第1半導体基板11の主面の法線方向(第1半導体基板11の表面に対して垂直な方向)に延伸して形成され、互いに隣接するセンサ画素12の各々を電気的に分離する。素子分離部43は、例えば、第1半導体基板11を貫通する酸化シリコンによって構成される。

第1基板10は、例えば、素子分離部43のフォトダイオードPD側の側面に接するpウェル層44を有する。pウェル層44は、フォトダイオードPDとは異なる導電型(具体的にはp型)の半導体領域で構成される。第1基板10は、例えば、第1半導体基板11の裏面に接する固定電荷膜45を有する。固定電荷膜45は、第1半導体基板11の受光面側の界面準位に起因する暗電流の発生を抑制するために、負の固定電荷を有する絶縁膜にて構成される。固定電荷膜45の材料としては、例えば、酸化ハフニウム、酸化ジルコン、酸化アルミニウム、酸化チタン、又は酸化タンタル等を例示することができる。固定電荷膜45は、電界を誘起することによって、第1半導体基板11の受光面側の界面に、界面からの電子の発生を抑制するホール蓄積層を形成することができる。

カラーフィルタ40は、第1半導体基板11の裏面側に設けられる。具体的には、カラーフィルタ40は、例えば、固定電荷膜45に対してセンサ画素12と対向する位置に、固定電荷膜45に接して設けられる。受光レンズ50は、例えば、カラーフィルタ40、及び固定電荷膜45に対してセンサ画素12と対向する位置に、カラーフィルタ40に接して設けられる。

第2基板20は、第2半導体基板21の上に第2絶縁層52を積層して構成される。第2半導体基板21は、シリコン基板であり、4つのセンサ画素12ごとに1つの画素回路22を有する。第2基板20は、第2半導体基板21の第3基板30側(すなわち、表面側)の部分に画素回路22を有する。第2基板20は、第1半導体基板11の表面側に第2半導体基板21の裏面を向けるようにして、第1基板10に貼り合わせられる。つまり、第2基板20は、第1基板10と、フェイストゥーバックにて貼り合わせられる。

第2半導体基板21には、分離絶縁層53が設けられており、分離絶縁層53の内部には、貫通配線54が設けられる。貫通配線54は、分離絶縁層53にて側面を覆われることによって、第2半導体基板21と電気的に絶縁される。貫通配線54は、第2半導体基板21の主面の法線方向に延伸しており、第1基板10の各素子、及び第2基板20の各素子を互いに電気的に接続する。具体的には、貫通配線54は、フローティングディフュージョンFD、及び接続配線55を電気的に接続する。貫通配線54は、例えば、センサ画素12ごとに1つずつ設けられる。

第2基板20は、例えば、第2絶縁層52内に、画素回路22、又は第2半導体基板21と電気的に接続された複数の接続部59を有する。配線層56は、例えば、層間絶縁層57、層間絶縁層57の内部に設けられた複数の画素駆動線23、及び複数の垂直信号線24を有する。配線層56は、例えば、層間絶縁層57の内部に、4つのセンサ画素12ごとに1つずつ接続配線55を有する。接続配線55は、画素回路22を共有する4つのセンサ画素12の貫通配線54を互いに電気的に接続する。

配線層56は、さらに、層間絶縁層57の内部に複数のパッド電極58を有する。パッド電極58の各々は、例えば、銅(Cu)などの金属で形成される。パッド電極58の各々は、配線層56の表面に露出されており、第2基板20と第3基板30との貼り合わせ、及び第2基板20と第3基板30との電気的な接続に用いられる。複数のパッド電極58は、例えば、画素駆動線23、及び垂直信号線24ごとに1つずつ設けられる。

ここで、第2基板20は、複数の半導体基板と、複数の絶縁層との積層構造にて設けられてもよい。

具体的には、第2基板20は、厚み方向に積層された2つの半導体基板を含んでもよい。例えば、第2基板20は、第2半導体基板21の上に積層された第2絶縁層52の上に、さらに半導体基板が積層されることで設けられてもよい。第2絶縁層52の上にさらに設けられた半導体基板には、例えば、トランジスタが設けられ、接続部59を介して第2半導体基板21に設けられたトランジスタと電気的に接続される。

すなわち、第2基板20に設けられる画素回路22は、第2半導体基板21と、第2絶縁層52の上にさらに積層された半導体基板とに分かれて設けられてもよい。具体的には、画素回路22に含まれる増幅トランジスタAMP、リセットトランジスタRST、及び選択トランジスタSELは、少なくとも1つ以上のトランジスタが第2半導体基板21に設けられ、残りのトランジスタが第2絶縁層52の上にさらに積層された半導体基板に設けられてもよい。一例として、第2半導体基板21に増幅トランジスタAMPが設けられ、第2絶縁層52の上にさらに積層された半導体基板にリセットトランジスタRST、及び選択トランジスタSELが設けられてもよい。

または、第2基板20は、厚み方向に積層された3つの半導体基板を含んでもよい。例えば、第2基板20は、第2半導体基板21の上に積層された第2絶縁層52の上にさらに上部第1半導体基板が積層され、上部第1半導体基板の上に絶縁層を介してさらに上部第2半導体基板が積層されることで設けられてもよい。積層された上部第1半導体基板、及び上部第2半導体基板には、例えば、トランジスタが設けられ、接続部59等を介して第2半導体基板21に設けられたトランジスタと電気的に接続される。

すなわち、第2基板20に設けられる画素回路22は、第2半導体基板21と、積層された上部第1半導体基板、及び上部第2半導体基板とに分かれて設けられてもよい。具体的には、画素回路22に含まれる増幅トランジスタAMP、リセットトランジスタRST、及び選択トランジスタSELは、少なくとも1つ以上のトランジスタが第2半導体基板21、上部第1半導体基板、及び上部第2半導体基板の各々に設けられてもよい。一例として、第2半導体基板21に増幅トランジスタAMPが設けられ、第2半導体基板21の上にさらに設けられた上部第1半導体基板にリセットトランジスタRSTが設けられ、上部第1半導体基板の上にさらに設けられた上部第2半導体基板に選択トランジスタSELが設けられてもよい。

厚み方向に積層された複数の半導体基板を含む第2基板20では、半導体基板を分けて積層することにより、1つの画素回路22が占める半導体基板の面積をより小さくすることができる。このような第2基板20を用いることにより、撮像装置1は、撮像装置1のチップ面積をより小さくすることが可能である。

また、このような第2基板20を用いることにより、撮像装置1は、画素回路22に含まれる増幅トランジスタAMP、リセットトランジスタRST、及び選択トランジスタSELのうち、任意のトランジスタの面積を選択的に拡大することができる。これによれば、撮像装置1は、増幅トランジスタAMPの面積を拡大することで、ノイズをより低減することが可能である。

第3基板30は、例えば、第3半導体基板31上に第3絶縁膜61を積層して構成される。第3半導体基板31は、シリコン基板であり、処理回路32を有する。なお、第3基板30は、第2基板20に対して、表面側の面同士で貼り合わせられている。そのため、第3基板30の各構成についての説明では、上下の説明が図面での上下方向とは逆となっている。第3基板30は、第2半導体基板21の表面側に第3半導体基板31の表面を向けるようにして、第2基板20に貼り合わせられている。つまり、第3基板30は、第2基板20と、フェイストゥーフェイスで貼り合わせられている。

第3基板30は、例えば、第3絶縁膜61上に配線層62を有する。配線層62は、例えば、層間絶縁層63と、層間絶縁層63の内部に設けられ、処理回路32と電気的に接続された複数のパッド電極64を有する。パッド電極64の各々は、例えば、銅(Cu)などの金属で形成される。パッド電極64は、配線層62の表面に露出されており、第2基板20と第3基板30との貼り合わせ、及び第2基板20と第3基板30との電気的な接続に用いられる。第2基板20、及び第3基板30は、パッド電極58、64同士の接合によって、互いに電気的に接続される。つまり、転送トランジスタTRのゲート(転送ゲートTG)は、貫通配線54、及びパッド電極58、64を介して、処理回路32に電気的に接続される。

図8及び図9は、撮像装置1の水平方向の断面構成の一例を示す模式図である。図8及び図9の上側の図は、図7における切断面Sec1の断面構成の一例を示す模式図であり、図8及び図9の下側の図は、図7における切断面Sec2の断面構成の一例を示す模式図である。

図8には、第1方向V1に、2×2の4つのセンサ画素12を2組並べた構成が例示されており、図9には、第1方向V1、及び第2方向V2に、2×2の4つのセンサ画素12を4組並べた構成が例示されている。

第1方向V1は、マトリクス状に配置された複数のセンサ画素12の2つの配列方向(例えば行方向、及び列方向)のうち一方の配列方向(例えば、行方向)と平行となっている。また、第2方向V2は、第1方向と直交する配列方向(例えば、列方向)と平行となっている。

貫通配線54は、例えば、センサ画素12ごとに設けられ、フローティングディフュージョンFD、及び後述の接続配線55を電気的に接続する。貫通配線47、48は、例えば、センサ画素12ごとに設けられる。貫通配線47は、第1半導体基板11のpウェル層42と、第2基板20内の配線とを電気的に接続する。貫通配線48は、転送ゲートTG、及び画素駆動線23を電気的に接続する。

図8に示すように、複数の貫通配線54、複数の貫通配線48、及び複数の貫通配線47は、第1基板10の面内において第2方向V2(図8の上下方向)に帯状に並んで配置される。図8には、複数の貫通配線54、複数の貫通配線48、及び複数の貫通配線47が第2方向V2に2列に並んで配置されている場合が例示されている。

図9に示すように、複数の貫通配線54、複数の貫通配線48、及び複数の貫通配線47は、第1基板10の面内において第1方向V1(図9の左右方向)に帯状に並んで配置される。図9には、複数の貫通配線54、複数の貫通配線48、及び複数の貫通配線47が第1方向V1に2列に並んで配置されている場合が例示されている。

画素回路22を共有する4つのセンサ画素12において、4つのフローティングディフュージョンFDは、例えば、素子分離部43を介して互いに近接して配置される。画素回路22を共有する4つのセンサ画素12において、4つの転送ゲートTGは、4つのフローティングディフュージョンFDを囲むように配置されており、例えば、4つの転送ゲートTGによって円環形状を構成している。

図8に示すように、分離絶縁層53は、第2方向V2に延伸する複数のブロックで構成される。第2半導体基板21は、第2方向V2に延伸し、かつ第2方向V2に並んで配置された複数の島状のブロック21Aで構成される。ブロック21Aの各々には、例えば、複数組のリセットトランジスタRST、増幅トランジスタAMP、及び選択トランジスタSELが設けられる。4つのセンサ画素12によって共有される1つの画素回路22は、例えば、4つのセンサ画素12と対応する領域内に存在するリセットトランジスタRST、増幅トランジスタAMP、及び選択トランジスタSELによって構成される。例えば、画素回路22は、分離絶縁層53の左隣りのブロック21A内の増幅トランジスタAMPと、分離絶縁層53の右隣りのブロック21A内のリセットトランジスタRST、及び選択トランジスタSELとによって構成される。

また、図9に示すように、分離絶縁層53は、第1方向V1に延伸する複数のブロックで構成される。第2半導体基板21は、第1方向V1に延伸し、かつ第1方向V1に並んで配置された複数の島状のブロック21Aで構成される。ブロック21Aの各々には、例えば、複数組のリセットトランジスタRST、増幅トランジスタAMP、及び選択トランジスタSELが設けられる。4つのセンサ画素12によって共有される1つの画素回路22は、例えば、4つのセンサ画素12と対応する領域内に存在するリセットトランジスタRST、増幅トランジスタAMP、及び選択トランジスタSELによって構成される。例えば、画素回路22は、分離絶縁層53の左隣りのブロック21A内の増幅トランジスタAMPと、分離絶縁層53の右隣りのブロック21A内のリセットトランジスタRST、及び選択トランジスタSELとによって構成される。

図10~図13は、撮像装置1の水平面内での配線レイアウトの一例を示した模式図である。図10~図13では、図8と同様に、4つのセンサ画素12によって共有された1つの画素回路22が4つのセンサ画素12と対応する領域内に設けられる場合の配線レイアウトの一例を示す。図10~図13では、例えば、配線層56において互いに異なる層内に設けられた配線のレイアウトをそれぞれ示している。

図10に示すように、例えば、互いに隣接する4つの貫通配線54は、接続配線55と電気的に接続される。貫通配線54は、接続配線55、及び接続部59を介して、分離絶縁層53の左隣りブロック21Aに含まれる増幅トランジスタAMPのゲートと、分離絶縁層53の右隣りブロック21Aに含まれるリセットトランジスタRSTのゲートとに電気的に接続される。

図11に示すように、例えば、電源線VDDは、第1方向V1に並んで配置された画素回路22の各々と対応する位置に配置される。電源線VDDは、接続部59を介して、第1方向V1に並んで配置された画素回路22の各々の増幅トランジスタAMPのドレイン、及びリセットトランジスタRSTのドレインに電気的に接続される。例えば、2本の画素駆動線23は、第1方向V1に並んで配置された画素回路22の各々と対応する位置に配置される。画素駆動線23の一方は、例えば、第1方向V1に並んで配置された画素回路22の各々のリセットトランジスタRSTのゲートに電気的に接続された配線RSTGとして機能する。画素駆動線23の他方は、例えば、第1方向V1に並んで配置された画素回路22の各々の選択トランジスタSELのゲートに電気的に接続された配線SELGとして機能する。例えば、増幅トランジスタAMPのソースと、選択トランジスタSELのドレインとは、配線25を介して互いに電気的に接続される。

図12に示すように、例えば、2本の基準電位線VSSは、第1方向V1に並んで配置された画素回路22の各々と対応する位置に配置されている。基準電位線VSSの各々は、第2方向V2に並んで配置された各センサ画素12と対応する位置において、複数の貫通配線47に電気的に接続される。例えば、4本の画素駆動線23は、第1方向V1に並んで配置された各画素回路22と対応する位置に配置される。4本の画素駆動線23の各々は、第1方向V1に並んで配置された画素回路22の各々に対応する1つのセンサ画素12の貫通配線48に電気的に接続された配線TRGとして機能する。4本の画素駆動線23は、第1方向V1に並んで配置されたセンサ画素12の各々の転送トランジスタTRのゲートに電気的に接続される。図12では、配線TRGの各々を区別するために、配線TRGの末尾に識別番号(1、2、3、4)を付与した。

図13に示すように、例えば、垂直信号線24は、第2方向V2に並んで配置された画素回路22の各々と対応する位置に配置される。垂直信号線24は、第2方向V2に並んで配置された画素回路22の各々の増幅トランジスタAMPのソースに電気的に接続される。

本開示に係る技術は、上記にて説明した積層型の撮像装置1に適用される。以下では、本開示に係る技術について、具体的に説明を行う。

<<2.本開示に係る技術>>

図14~図28Dを参照して、本開示の一実施形態に係る技術について説明する。本実施形態に係る技術は、第2基板20の第2半導体基板21、及び分離絶縁層53のレイアウトに関するものである。なお、第2半導体基板21は、本願の特許請求の範囲における「半導体層」に対応し、分離絶縁層53は、本願の特許請求の範囲における「絶縁層」に対応する。

3つの基板を積層することで構成される撮像装置1では、光の入射面から見て、第1半導体基板11に設けられたフォトダイオードPDの奥側に第2半導体基板21が存在する。そのため、長波長の入射光が第1半導体基板11を透過した場合、透過した入射光が第2半導体基板21の裏面にて反射することがあった。

一方で、第1基板10と、第2基板20との間には、フォトダイオードPDにて光電変換された電荷を増幅トランジスタAMPに出力する貫通配線54が設けられる。貫通配線54は、第2半導体基板21を貫通する分離絶縁層53の内部に設けられ、第1基板10に設けられた電極又は配線と、第2基板20に設けられた電極又は配線とを電気的に接続する。分離絶縁層53は、第2半導体基板21の各部を電気的に離隔するために設けられ、貫通配線54と、第2半導体基板21とを電気的に絶縁する。

したがって、第1半導体基板11を透過した光が入射する第2半導体基板21の裏面には、第2半導体基板21と、分離絶縁層53とが画素領域13の全面に亘って混在することになる。分離絶縁層53は、第2半導体基板21よりも光の反射率が低いため、分離絶縁層53の大きさ、及び配置によっては、第2半導体基板21、及び分離絶縁層53から第1半導体基板11への反射光の分布が不均一になることがあり得る。

ここで、第2半導体基板21、及び分離絶縁層53から第1半導体基板11への反射光は、センサ画素12における感度低下、又は隣接画素への漏れ込み(クロストーク)を発生させる。そのため、第1半導体基板11への反射光の分布が不均一になることは、センサ画素12における同色画素間の感度差、又は隣接画素へのクロストークの不均一性を増加させ、撮像装置1にて撮像される画像の画質を低下させてしまう。

第2半導体基板21、及び分離絶縁層53のレイアウトは、一般的には、分離絶縁層53の内部を貫通する貫通配線54の配置、及び画素回路22における配線のレイアウト等を考慮して設計される。しかしながら、撮像装置1の三次元構造化、及び高性能化によって、撮像装置1の内部にて反射される光の影響が強まることにより、撮像画像の面内ばらつきが顕在化する可能性がある。そのため、撮像装置1にて撮像される画像の不均一性を抑制することが望まれる。

本実施形態に係る技術は、かかる事情を鑑みて想到されたものである。本実施形態に係る技術は、第1半導体基板11におけるセンサ画素12のレイアウトと対応するように、第2半導体基板21における分離絶縁層53のレイアウトを決定するものである。具体的には、本実施形態に係る技術は、第2半導体基板21を分断する分離絶縁層53の中心位置、又は分離絶縁層53にて分断された第2半導体基板21の中心位置がセンサ画素12の光学中心の位置(例えば、フォトダイオードPDの中心位置)に対応するように分離絶縁層53を配置するものである。これによれば、本実施形態に係る技術は、第2半導体基板21にて反射される入射光の分布をより均一化することができるため、撮像装置1にて撮像される画像の不均一性を抑制し、撮像画像の画質を向上させることができる。

続いて、図14を参照して、本実施形態に係る技術についてより具体的に説明する。図14は、本実施形態に係る撮像装置1の積層方向の断面構成の一例を示す縦断面図である。

図14に示す断面構成は、図7にて示した断面構成と比較して、分離絶縁層53が形成される位置が異なる。具体的には、図14に示すように、分離絶縁層53は、分離絶縁層53の中心位置がセンサ画素12の光学中心OCの位置と略一致するように設けられる。センサ画素12の光学中心OCとは、例えば、入射光の光軸方向に垂直な平面にて、フォトダイオードPDが設けられる領域の一方向における中心である。換言すると、センサ画素12の光学中心OCとは、撮像装置1を積層方向に切断した一断面において、積層方向と直交する方向でのフォトダイオードPDの幅の中心である。

または、センサ画素12の光学中心OCの位置は、フォトダイオードPDが形成される領域以外の要素に基づいて定義されてもよい。例えば、センサ画素12の光学中心OCの位置は、撮像装置1を積層方向に切断した一断面において、積層方向と直交する方向での素子分離部43にて画定された領域の幅の中心、カラーフィルタ40の幅の中心、又は受光レンズ50の幅の中心として定義されてもよい。

センサ画素12の光学中心OCとは、入射光の光軸方向に垂直な平面にて、光学情報の取得単位にて光電変換が行われる領域の一方向における中心である。そのため、センサ画素12の光学中心OCは、撮像装置1の各画素における光学情報の取得様態に基づいて、適宜、適切な定義にて設定され得る。

光学情報の取得単位とは、1つの光学情報を形成するために用いられる1又は複数の画素を表し、例えば、画素単体、複数のサブ画素からなる画素全体、又は画素に含まれるサブ画素の各々のいずれであってもよい。光学情報の取得単位は、画素回路22において、画素信号がいずれのセンサ画素12から出力された電荷に基づいて生成されるかを確認することで把握することが可能である。

分離絶縁層53の中心位置は、センサ画素12の光学中心OCの位置に対して、入射光の光軸方向に垂直な平面の少なくとも一方向において略一致していればよい。換言すると、分離絶縁層53の中心位置は、撮像装置1を積層方向に切断した一断面において、積層方向と直交する面内のいずれかの方向で、センサ画素12の光学中心OCの位置と略一致していればよい。これによれば、撮像装置1は、センサ画素12にて光学情報が取得される領域に対して、分離絶縁層53をより対称性が高くなるように配置することができるため、第2半導体基板21、及び分離絶縁層53から第1半導体基板11への反射光の均一性を向上させることができる。

また、分離絶縁層53の中心位置は、センサ画素12の光学中心OCの位置に対して、入射光の光軸方向に垂直な平面の複数の方向において(又は、全周に亘って)、略一致していてもよい。これによれば、撮像装置1は、第2半導体基板21、及び分離絶縁層53から第1半導体基板11への反射光の均一性をさらに向上させることができる。

ただし、分離絶縁層53の中心位置は、センサ画素12の光学中心OCの位置と完全一致していなくともよい。例えば、フォトダイオードPDが設けられた領域の中心位置と、分離絶縁層53の中心位置とは、フォトダイオードPDの形成ピッチの1/3以下の大きさでずれていてもよい。分離絶縁層53の中心位置と、フォトダイオードPDが設けられた領域の中心位置とがフォトダイオードPDの形成ピッチの1/3以下でずれている場合、両者は、略一致しているとみなすことが可能であり、撮像装置1は、上述した効果を奏することが可能である。

ここで、光は、波長が長くなるほど透過性が高くなるため、より長波長の光のほうが第1半導体基板11をより多く透過し、第2半導体基板21、及び分離絶縁層53に入射する。したがって、第2半導体基板21、及び分離絶縁層53から第1半導体基板11への反射光は、より長波長の光のほうがより多くなる。

そのため、分離絶縁層53の中心位置は、少なくとも撮像装置1にて受光する光のうち最も長波長の光を光電変換するセンサ画素12では、上述したようにセンサ画素12の光学中心OCの位置と略一致していることが好ましい。具体的には、撮像装置1が赤色、緑色、及び青色に対応する光をセンサ画素12にてそれぞれ受光する場合、少なくとも最も長波長である赤色を受光するセンサ画素12では、分離絶縁層53の中心位置は、センサ画素12の光学中心OCの位置と略一致していることが好ましい。また、緑色光を受光するセンサ画素12、及び青色光を受光するセンサ画素12の各々でも、分離絶縁層53の中心位置は、センサ画素12の光学中心OCの位置と略一致していてもよい。

本実施形態に係る技術によれば、入射光の光軸方向に垂直な平面の一方向において、第1半導体基板11に設けられるフォトダイオードPDの中心に対して対称となるように分離絶縁層53を設けることができる。よって、本実施形態に係る技術は、第2半導体基板21からフォトダイオードPDへの反射光の分布を均一化することができる。したがって、本実施形態に係る撮像装置1は、同色画素間の感度の不均一性、又は隣接画素へのクロストーク量の不均一性を低減することができる。

なお、第2基板20が厚み方向に積層された複数の半導体基板を含む場合、積層された複数の半導体基板(すなわち、第2半導体基板21、及び第2半導体基板21の上に設けられた少なくとも1つ以上の半導体基板)における分離絶縁層53は、それぞれ中心位置がセンサ画素12の光学中心OCの位置と略一致するように設けられてもよい。これによれば、本実施形態に係る撮像装置1は、第2基板20からフォトダイオードPDへの反射光の分布をより均一化することができるため、同色画素間の感度の不均一性、又は隣接画素へのクロストーク量の不均一性をより低減することができる。

図示しないが、分離絶縁層53は、分離絶縁層53にて分断された第2半導体基板21の中心位置がセンサ画素12の光学中心OCの位置と略一致するように設けられてもよい。本実施形態に係る技術では、入射光の光軸方向に垂直な平面の一方向において、反射光を発生させる分離絶縁層53、及び第2半導体基板21をフォトダイオードPDの中心に対して対称となるように配置することが重要となる。そのため、第2半導体基板21を分断する分離絶縁層53に替えて、分離絶縁層53によって分断される第2半導体基板21の中心位置をセンサ画素12の光学中心OCに対して略一致させることによっても、上述した効果を奏することが可能である。

次に、図15~図26を参照して、本実施形態に係る技術を適用した撮像装置1におけるセンサ画素12と、分離絶縁層53との平面配置のバリエーションについて説明する。図15~図26は、センサ画素12の各々と、第2半導体基板21との平面配置のバリエーションを示す平面図である。

なお、図15~図26において、第2半導体基板21が設けられた領域以外の領域には、図示しないが、分離絶縁層53が設けられる。また、図15~図26では、各色に対応する画素の違いをハッチング種の違いにて表現する。すなわち、同種のハッチングが施された画素は、同色の光を光電変換する画素であり、異種のハッチングが施された画素は、異種の光を光電変換する画素である。

(第1のバリエーション)

図15に示すように、例えば、画素領域13は、赤色に対応する光を光電変換する赤色画素PixR、緑色に対応する光を光電変換する緑色画素PixG、及び青色に対応する光を光電変換する青色画素PixBを行列状に配列することで構成される。具体的には、画素領域13は、1つの赤色画素PixR、2つの緑色画素PixG、及び1つの青色画素PixBを繰り返し単位として、該繰り返し単位を互いに直交する第1方向V1、及び第2方向V2に行列状に配列することで構成される。

また、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、それぞれ4つのサブ画素を行列状に配列することで構成される。例えば、赤色画素PixRは、サブ画素12R1、12R2、12R3、及び12R4を2×2の行列状に配列することで構成される。なお、以下では、赤色画素PixR、緑色画素PixG、及び青色画素PixBに含まれるサブ画素を互いに区別しない場合、これらをサブ画素12Nと総称する。

ここで、センサ画素12の光学中心OCの位置は、同色のサブ画素12Nの間を通り第2方向V2に延伸する直線上の位置となる。具体的には、赤色画素PixRの光学中心OCの位置は、例えば、サブ画素12R1、12R2の間、及びサブ画素12R3、12R4の間を通り、第2方向V2に延伸する直線上の位置となる。これは、このような画素領域13を有する撮像装置1では、サブ画素12Nの各々にて個別に光学情報を取得する場合に加えて、同色のサブ画素12N全体で光学情報を取得する場合があるためである。すなわち、光学情報を取得する単位が赤色画素PixR、緑色画素PixG、及び青色画素PixBとなり得るため、光学中心OCの位置は、同色のサブ画素12Nの間を通り第2方向V2に延伸する直線上の位置となる。

一方、第2半導体基板21は、赤色画素PixR、緑色画素PixG、及び青色画素PixBに含まれるサブ画素12Nの各々に対応するように、正方形形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第1方向V1、及び第2方向V2に分断されることで、サブ画素12Nの各々よりも一回り小さい正方形形状にて、行列状に互いに離隔されて設けられる。

したがって、図15に示す平面配置では、第1方向V1において、分離絶縁層53が設けられた領域の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第2半導体基板21、及び分離絶縁層53からフォトダイオードPDへの反射光の分布をより均一化することができる。

(第2のバリエーション)

図16に示すように、第2のバリエーションでは、第1のバリエーションと同様に、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、行列状に画素領域13に配列される。また、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、第1のバリエーションと同様に、それぞれ4つのサブ画素を行列状に配列することで構成される。

ここで、センサ画素12の光学中心OCの位置は、第1のバリエーションと同様に、同色のサブ画素12Nの間を通り第2方向V2に延伸する直線上の位置となる。具体的には、赤色画素PixRの光学中心OCの位置は、例えば、サブ画素12R1、12R2の間、及びサブ画素12R3、12R4の間を通り、第2方向V2に延伸する直線上の位置となる。

一方、第2半導体基板21は、赤色画素PixR、緑色画素PixG、及び青色画素PixBに含まれるサブ画素12Nの各々に対応するように、第2方向V2に延伸する長手形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第1方向V1に分断されることで、第2方向V2に延伸する長手形状にて、行方向に互いに離隔されて設けられる。

したがって、図16に示す平面配置では、第1方向V1において、分離絶縁層53が設けられた領域の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第1のバリエーションよりも単純な平面配置の分離絶縁層53によって、第2半導体基板21、及び分離絶縁層53からフォトダイオードPDへの反射光の分布を均一化することができる。

(第3のバリエーション)

図17に示すように、第3のバリエーションでは、第1のバリエーションと同様に、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、行列状に画素領域13に配列される。また、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、第1のバリエーションと同様に、それぞれ4つのサブ画素を行列状に配列することで構成される。

ここで、センサ画素12の光学中心OCの位置は、第1のバリエーションとは異なり、同色のサブ画素12Nの間を通り第1方向V1に延伸する直線上の位置としてもよい。具体的には、赤色画素PixRの光学中心OCの位置は、例えば、サブ画素12R1、12R3の間、及びサブ画素12R2、12R4の間を通り、第1方向V1に延伸する直線上の位置としてもよい。赤色画素PixR、緑色画素PixG、及び青色画素PixBが行列状に配置された画素領域13では、第1方向V1と第2方向V2とは交換可能である。そのため、センサ画素12の光学中心OCは、第1方向V1に設定されてもよく、第2方向V2に設定されてもよい。

一方、第2半導体基板21は、赤色画素PixR、緑色画素PixG、及び青色画素PixBに含まれるサブ画素12Nの各々に対応するように、第1方向V1に延伸する長手形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第2方向V2に分断されることで、第1方向V1に延伸する長手形状にて、列方向に互いに離隔されて設けられる。

したがって、図17に示す平面配置では、第2方向V2において、分離絶縁層53が設けられた領域の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第2のバリエーションと同様に、第2半導体基板21、及び分離絶縁層53からフォトダイオードPDへの反射光の分布を均一化することができる。

(第4のバリエーション)

図18に示すように、第4のバリエーションでは、第1のバリエーションと同様に、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、行列状に画素領域13に配列される。また、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、第1のバリエーションと同様に、それぞれ4つのサブ画素を行列状に配列することで構成される。

ここで、センサ画素12の光学中心OCの位置は、第1のバリエーションと同様に、同色のサブ画素12Nの間を通り第2方向V2に延伸する直線上の位置となる。具体的には、赤色画素PixRの光学中心OCの位置は、例えば、サブ画素12R1、12R2の間、及びサブ画素12R3、12R4の間を通り、第2方向V2に延伸する直線上の位置となる。

一方、第2半導体基板21は、赤色画素PixR、緑色画素PixG、及び青色画素PixBに含まれるサブ画素12Nの第1方向V1における画素境界に対応するように、正方形形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第1方向V1、及び第2方向V2に分断されることで、サブ画素12Nよりも一回り小さい正方形形状にて、行列状に互いに離隔されて設けられる。すなわち、第2半導体基板21は、サブ画素12Nの行列配置から第1方向V1に1/2ピッチずれた行列配置にて設けられる。

したがって、図18に示す平面配置では、第1方向V1において、分離絶縁層53によって分断された第2半導体基板21の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第1のバリエーションと同様に、第2半導体基板21、及び分離絶縁層53からフォトダイオードPDへの反射光の分布をより均一化することができる。

(第5のバリエーション)

図19に示すように、第5のバリエーションでは、第1のバリエーションと同様に、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、行列状に画素領域13に配列される。また、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、第1のバリエーションと同様に、それぞれ4つのサブ画素を行列状に配列することで構成される。

ここで、センサ画素12の光学中心OCの位置は、第1のバリエーションと同様に、同色のサブ画素12Nの間を通り第2方向V2に延伸する直線上の位置となる。具体的には、赤色画素PixRの光学中心OCの位置は、例えば、サブ画素12R1、12R2の間、及びサブ画素12R3、12R4の間を通り、第2方向V2に延伸する直線上の位置となる。

一方、第2半導体基板21は、赤色画素PixR、緑色画素PixG、及び青色画素PixBに含まれるサブ画素12Nの第1方向V1における画素境界に対応するように、第2方向V2に延伸する長手形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第1方向V1に分断されることで、第2方向V2に延伸する長手形状にて、行方向に互いに離隔されて設けられる。すなわち、第2半導体基板21は、サブ画素12Nの行列配置から第1方向V1に1/2ピッチずれて第2方向V2に延伸するストライプ配置にて設けられる。

したがって、図19に示す平面配置では、第1方向V1において、分離絶縁層53によって分断された第2半導体基板21の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第1のバリエーションよりも単純な平面配置の分離絶縁層53によって、第2半導体基板21、及び分離絶縁層53からフォトダイオードPDへの反射光の分布を均一化することができる。

(第6のバリエーション)

図20に示すように、第6のバリエーションでは、第4のバリエーションと同様に、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、行列状に画素領域13に配列される。また、赤色画素PixR、緑色画素PixG、及び青色画素PixBは、第1のバリエーションと同様に、それぞれ4つのサブ画素を行列状に配列することで構成される。

ここで、センサ画素12の光学中心OCの位置は、同色のサブ画素12Nの間を通り第1方向V1に延伸する直線上の位置としてもよい。具体的には、赤色画素PixRの光学中心OCの位置は、例えば、サブ画素12R1、12R3の間、及びサブ画素12R2、12R4の間を通り、第1方向V1に延伸する直線上の位置としてもよい。赤色画素PixR、緑色画素PixG、及び青色画素PixBが行列状に配置された画素領域13では、第1方向V1と第2方向V2とは交換可能である。そのため、センサ画素12の光学中心OCは、第1方向V1に設定されてもよく、第2方向V2に設定されてもよい。

一方、第2半導体基板21は、赤色画素PixR、緑色画素PixG、及び青色画素PixBに含まれるサブ画素12Nの第2方向V2における画素境界に対応するように、第1方向V1に延伸する長手形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第2方向V2に分断されることで、第1方向V1に延伸する長手形状にて、列方向に互いに離隔されて設けられる。すなわち、第2半導体基板21は、サブ画素12Nの行列配置から第2方向V2に1/2ピッチずれて第1方向V1に延伸するストライプ配置にて設けられる。

したがって、図20に示す平面配置では、第2方向V2において、分離絶縁層53によって分断された第2半導体基板21の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第5のバリエーションと同様に、第2半導体基板21及び分離絶縁層53からフォトダイオードPDへの反射光の分布を均一化することができる。

(第7のバリエーション)

図21に示すように、例えば、画素領域13は、赤色に対応する光を光電変換する赤色画素12R、緑色に対応する光を光電変換する緑色画素12G、及び青色に対応する光を光電変換する青色画素12Bを行列状に配列することで構成される。具体的には、画素領域13は、1つの赤色画素12R、2つの緑色画素12G、及び1つの青色画素12Bを繰り返し単位として、該繰り返し単位を互いに直交する第1方向V1、及び第2方向V2に行列状に配列することで構成される。以下では、赤色画素12R、緑色画素12G、及び青色画素12Bを互いに区別しない場合、これらをセンサ画素12と総称する。

ここで、センサ画素12の光学中心OCの位置は、センサ画素12の第1方向V1における中心を通り、第2方向V2に延伸する直線上の位置となる。このような画素領域13を有する撮像装置1では、赤色画素12R、緑色画素12G、及び青色画素12Bの各々が光学情報を取得する単位となるため、センサ画素12の中心を通る直線上の位置が光学中心OCの位置となる。また、画素領域13では、赤色光、緑色光、及び青色光のうち最も長波長である赤色光を光電変換する赤色画素12Rについて光学中心OCが設定される。これは、赤色光、緑色光、及び青色光のうち最も長波長である赤色光が最も第1半導体基板11を透過しやすく、第2半導体基板21、及び分離絶縁層53にて反射されやすいためである。

一方、第2半導体基板21は、赤色画素12Rの斜方に配置された青色画素12Bに対応するように、正方形形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第1方向V1、及び第2方向V2に分断されることで、青色画素12Bよりも一回り大きくした正方形形状にて、行列状に互いに離隔されて設けられる。

したがって、図21に示す平面配置では、第1方向V1において、分離絶縁層53が設けられた領域の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第2半導体基板21、及び分離絶縁層53からフォトダイオードPDへの反射光の分布をより均一化することができる。

(第8のバリエーション)

図22に示すように、第8のバリエーションでは、第7のバリエーションと同様に、赤色画素12R、緑色画素12G、及び青色画素12Bは、行列状に画素領域13に配列される。

ここで、センサ画素12の光学中心OCの位置は、第7のバリエーションと同様に、センサ画素12の第1方向V1における中心を通り、第2方向V2に延伸する直線上の位置となる。また、画素領域13では、赤色光、緑色光、及び青色光のうち最も長波長である赤色光を光電変換する赤色画素12Rについて光学中心OCが設定される。

一方、第2半導体基板21は、緑色画素12G、及び青色画素12Bが配列された列に対応するように、第2方向V2に延伸する長手形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第1方向V1に分断されることで、第2方向V2に延伸する長手形状にて、行方向に互いに離隔されて設けられる。

したがって、図22に示す平面配置では、第1方向V1において、分離絶縁層53が設けられた領域の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第7のバリエーションよりも単純な平面配置の分離絶縁層53によって、第2半導体基板21、及び分離絶縁層53からフォトダイオードPDへの反射光の分布を均一化することができる。

(第9のバリエーション)

図23に示すように、第9のバリエーションでは、第7のバリエーションと同様に、赤色画素12R、緑色画素12G、及び青色画素12Bは、行列状に画素領域13に配列される。

ここで、センサ画素12の光学中心OCの位置は、第7のバリエーションとは異なり、センサ画素12の第2方向V2における中心を通り、第1方向V1に延伸する直線上の位置としてもよい。光学中心OCは、赤色光、緑色光、及び青色光のうち最も長波長である赤色光を光電変換する赤色画素12Rについて設定される。赤色画素12R、緑色画素12G、及び青色画素12Bが行列状に配置された画素領域13では、第1方向V1と第2方向V2とは交換可能であるため、センサ画素12の光学中心OCは、第1方向V1に設定されてもよく、第2方向V2に設定されてもよい。

一方、第2半導体基板21は、緑色画素12G、及び青色画素12Bが配列された行に対応するように、第1方向V1に延伸する長手形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第2方向V2に分断されることで、第1方向V1に延伸する長手形状にて、列方向に互いに離隔されて設けられる。

したがって、図23に示す平面配置では、第2方向V2において、分離絶縁層53が設けられた領域の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第8のバリエーションと同様に第2半導体基板21及び分離絶縁層53からフォトダイオードPDへの反射光の分布を均一化することができる。

(第10のバリエーション)

図24に示すように、第10のバリエーションでは、第7のバリエーションと同様に、赤色画素12R、緑色画素12G、及び青色画素12Bは、行列状に画素領域13に配列される。

ここで、センサ画素12の光学中心OCの位置は、第7のバリエーションと同様に、センサ画素12の第1方向V1における中心を通り、第2方向V2に延伸する直線上の位置となる。また、画素領域13では、赤色光、緑色光、及び青色光のうち最も長波長である赤色光を光電変換する赤色画素12Rについて光学中心OCが設定される。

一方、第2半導体基板21は、赤色画素12Rに対応するように、正方形形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第1方向V1、及び第2方向V2に分断されることで、赤色画素12Rを一回り大きくした正方形形状にて、行列状に互いに離隔されて設けられる。

したがって、図24に示す平面配置では、第1方向V1において、分離絶縁層53によって分断された第2半導体基板21の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第7のバリエーションと同様に、第2半導体基板21、及び分離絶縁層53からフォトダイオードPDへの反射光の分布をより均一化することができる。

(第11のバリエーション)

図25に示すように、第11のバリエーションでは、第7のバリエーションと同様に、赤色画素12R、緑色画素12G、及び青色画素12Bは、行列状に画素領域13に配列される。

ここで、センサ画素12の光学中心OCの位置は、第7のバリエーションと同様に、センサ画素12の第1方向V1における中心を通り、第2方向V2に延伸する直線上の位置となる。また、画素領域13では、赤色光、緑色光、及び青色光のうち最も長波長である赤色光を光電変換する赤色画素12Rについて光学中心OCが設定される。

一方、第2半導体基板21は、赤色画素12R、及び緑色画素12Gが配列された列に対応するように、第2方向V2に延伸する長手形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第1方向V1に分断されることで、第2方向V2に延伸する長手形状にて、行方向に互いに離隔されて設けられる。

したがって、図25に示す平面配置では、第1方向V1において、分離絶縁層53によって分断された第2半導体基板21の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第7のバリエーションよりも単純な平面配置の分離絶縁層53によって、第2半導体基板21、及び分離絶縁層53からフォトダイオードPDへの反射光の分布を均一化することができる。

(第12のバリエーション)

図26に示すように、第12のバリエーションでは、第7のバリエーションと同様に、赤色画素12R、緑色画素12G、及び青色画素12Bは、行列状に画素領域13に配列される。

ここで、センサ画素12の光学中心OCの位置は、第7のバリエーションとは異なり、センサ画素12の第2方向V2における中心を通り、第1方向V1に延伸する直線上の位置としてもよい。光学中心OCは、赤色光、緑色光、及び青色光のうち最も長波長である赤色光を光電変換する赤色画素12Rについて設定される。赤色画素12R、緑色画素12G、及び青色画素12Bが行列状に配置された画素領域13では、第1方向V1と第2方向V2とは交換可能であるため、センサ画素12の光学中心OCは、第1方向V1に設定されてもよく、第2方向V2に設定されてもよい。

一方、第2半導体基板21は、赤色画素12R、及び緑色画素12Gが配列された行に対応するように、第1方向V1に延伸する長手形状にて設けられる。具体的には、第2半導体基板21は、分離絶縁層53によって第2方向V2に分断されることで、第1方向V1に延伸する長手形状にて、列方向に互いに離隔されて設けられる。

したがって、図26に示す平面配置では、第2方向V2において、分離絶縁層53によって分断された第2半導体基板21の中心位置と、センサ画素12の光学中心OCの位置とが略一致している。このような平面配置によれば、撮像装置1は、第11のバリエーションと同様に第2半導体基板21、及び分離絶縁層53からフォトダイオードPDへの反射光の分布を均一化することができる。

続いて、図27A~図28Dを参照して、本実施形態に係る技術のさらなるバリエーションについて説明する。図27A~図27Dは、第13のバリエーションに係る撮像装置1の部分的な断面構成を模式的に示した縦断面図である。図28A~図28Dは、第14のバリエーションに係る撮像装置1の部分的な断面構成を模式的に示した縦断面図である。

(第13のバリエーション)

図27A~図27Dに示すように、第13のバリエーションに係る撮像装置1は、第1半導体基板11と、カラーフィルタ40R、40Gと、受光レンズ50と、第1絶縁層46と、第2半導体基板21と、第1反射防止膜71とを含む。すなわち、第13のバリエーションに係る撮像装置1は、第1絶縁層46と、第2半導体基板21との間に第1反射防止膜71が設けられる点が図14等で示した撮像装置1と異なる。

第1半導体基板11は、素子分離部43にて互いに分離されたフォトダイオードPD1、PD2、PD3、PD4(互いを区別しない場合には、フォトダイオードPDと表記する)を備える。図27A~図27Dでは、便宜的に、フォトダイオードPD1、PD2、PD3、PD4のみ示したが、フォトダイオードPDは、図27A~図27Dの紙面上、及び図27A~図27Dの紙面の法線方向に広がって行列配列されていることは言うまでもない。

カラーフィルタ40R、40G、及び受光レンズ50は、第1半導体基板11の裏面側(受光面側)に設けられる。

カラーフィルタ40Rは、例えば、赤色に対応する波長帯域の光を選択的に透過させる光学フィルタであり、カラーフィルタ40Gは、緑色に対応する波長帯域の光を選択的に透過させる光学フィルタである。受光レンズ50は、例えば、マイクロレンズであり、フォトダイオードPDに入射する光を集光する。なお、青色光に対応する波長帯域の光を選択的に透過させるカラーフィルタは、図27A~図27Dの紙面の手前側又は奥側に設けられているため、図27A~図27Dでは図示されない。

ここで、図27A~図27Cは、フォトダイオードPDと、カラーフィルタ40R、40G、及び受光レンズ50との対応関係がそれぞれ異なる。また、図27Dは、図27A~図27Cに示した構造に対して、フォトダイオードPDと、第2半導体基板21又は分離絶縁層53との対応関係が異なる。

図27Aに示す一例では、フォトダイオードPD1、PD2、PD3、PD4のそれぞれに対して、1対1対応でカラーフィルタ40R又は40Gと、受光レンズ50とが設けられている。

図27Bに示す一例では、2つのフォトダイオードPD1、PD2に対して、1つのカラーフィルタ40Rが設けられており、2つのフォトダイオードPD3、PD4に対して、1つのカラーフィルタ40Gが設けられている。また、フォトダイオードPD1、PD2、PD3、PD4のそれぞれに対して、1対1対応で受光レンズ50が設けられている。

図27Cに示す一例では、2つのフォトダイオードPD1、PD2に対して、1つのカラーフィルタ40Rが設けられており、2つのフォトダイオードPD3、PD4に対して、1つのカラーフィルタ40Gが設けられている。また、2つのフォトダイオードPD1、PD2に対して、1つの受光レンズ50が設けられており、2つのフォトダイオードPD3、PD4に対して、1つの受光レンズ50が設けられている。

図27A~図27Cに示すように、カラーフィルタ40R、40G、及び受光レンズ50は、1つのフォトダイオードPD(すなわち、1画素)に対して1対1対応して設けられてもよく、複数のフォトダイオードPD(すなわち、複数の画素)にて共有されてもよい。

図27A~図27Cでは、センサ画素12の光学中心OCの位置と、分離絶縁層53にて分断された第2半導体基板21の中心位置とが略一致している例を示した。一方で、図27Dに示すように、センサ画素12の光学中心OCの位置は、分離絶縁層53の中心位置と略一致していてもよい。本実施形態に係る技術では、分離絶縁層53、及び第2半導体基板21がセンサ画素12の光学中心OCの位置に対して、対称に配置されることが重要である。したがって、センサ画素12の光学中心OCの位置は、分離絶縁層53の中心位置と略一致していてもよく、第2半導体基板21の中心位置と略一致していてもよい。

第1絶縁層46は、第1半導体基板11の表面側に積層され、第2半導体基板21の裏面側と貼り合わせられる。第2半導体基板21は、分離絶縁層53によって分断されており、裏面側にて第1絶縁層46と貼り合わせられる。

第13のバリエーションでは、第2半導体基板21、及び第1絶縁層46の間に、第1反射防止膜71が設けられる。第1反射防止膜71は、第1絶縁層46を構成する材料の屈折率と、第2半導体基板21を構成する材料の屈折率との間の値の屈折率を有する材料で構成される薄膜である。第1反射防止膜71は、第1絶縁層46から第2半導体基板21への光路において、より段階的に屈折率を変化させることで、第1絶縁層46、及び第2半導体基板21の間での入射光の反射を抑制することができる。

例えば、第1絶縁層46が酸化アルミニウム(AlOx)で形成され、第2半導体基板21がシリコン(Si)で形成される場合、第1反射防止膜71は、酸化アルミニウムの屈折率と、シリコンの屈折率との間の屈折率を有する窒化シリコン(SiN)にて形成することができる。

第13のバリエーションに係る撮像装置1では、第1絶縁層46と、第2半導体基板21との貼り合わせ界面に第1反射防止膜71を設けることで、第2半導体基板21から第1半導体基板11への反射自体を抑制することができる。したがって、第13のバリエーションに係る撮像装置1は、同色画素間の感度の不均一性、又は隣接画素へのクロストーク量の不均一性をさらに低減することができる。

(第14のバリエーション)

図28A~図28Dに示すように、第14のバリエーションに係る撮像装置1は、第1半導体基板11と、カラーフィルタ40R、40Gと、受光レンズ50と、第1絶縁層46と、第2半導体基板21と、第1反射防止膜71と、第2反射防止膜72とを含む。すなわち、第14のバリエーションに係る撮像装置1は、第1絶縁層46と、第2半導体基板21との間に第1反射防止膜71、及び第2反射防止膜72が設けられる点が図14等で示した撮像装置1と異なる。

第1半導体基板11は、素子分離部43にて互いに分離されたフォトダイオードPD1、PD2、PD3、PD4(互いを区別しない場合には、フォトダイオードPDと表記する)を備える。図28A~図28Dでは、便宜的に、フォトダイオードPD1、PD2、PD3、PD4のみ示したが、フォトダイオードPDは、図28A~図28Dの紙面上、及び図28A~図28Dの紙面の法線方向に広がって行列配列されていることは言うまでもない。

カラーフィルタ40R、40G、及び受光レンズ50は、第1半導体基板11の裏面側(受光面側)に設けられる。

カラーフィルタ40Rは、例えば、赤色に対応する波長帯域の光を選択的に透過させる光学フィルタであり、カラーフィルタ40Gは、緑色に対応する波長帯域の光を選択的に透過させる光学フィルタである。受光レンズ50は、例えば、マイクロレンズであり、フォトダイオードPDに入射する光を集光する。なお、青色光に対応する波長帯域の光を選択的に透過させるカラーフィルタは、図28A~図28Dの紙面の手前側又は奥側に設けられているため、図28A~図28Dでは図示されない。

ここで、図28A~図28Cは、フォトダイオードPDと、カラーフィルタ40R、40G、及び受光レンズ50との対応関係がそれぞれ異なる。また、図28Dは、図28A~図28Cに示した構造に対して、フォトダイオードPDと、第2半導体基板21又は分離絶縁層53との対応関係が異なる。

図28Aに示す一例では、フォトダイオードPD1、PD2、PD3、PD4のそれぞれに対して、1対1対応でカラーフィルタ40R又は40Gと、受光レンズ50とが設けられている。

図28Bに示す一例では、2つのフォトダイオードPD1、PD2に対して、1つのカラーフィルタ40Rが設けられており、2つのフォトダイオードPD3、PD4に対して、1つのカラーフィルタ40Gが設けられている。また、フォトダイオードPD1、PD2、PD3、PD4のそれぞれに対して、1対1対応で受光レンズ50が設けられている。

図28Cに示す一例では、2つのフォトダイオードPD1、PD2に対して、1つのカラーフィルタ40Rが設けられており、2つのフォトダイオードPD3、PD4に対して、1つのカラーフィルタ40Gが設けられている。また、2つのフォトダイオードPD1、PD2に対して1つの受光レンズ50が設けられており、2つのフォトダイオードPD3、PD4に対して1つの受光レンズ50が設けられている。

図28A~図28Cに示すように、カラーフィルタ40R、40G、及び受光レンズ50は、1つのフォトダイオードPD(すなわち、1画素)に対して1対1対応して設けられてもよく、複数のフォトダイオードPD(すなわち、複数の画素)にて共有されてもよい。

図28A~図28Cでは、センサ画素12の光学中心OCの位置と、分離絶縁層53にて分断された第2半導体基板21の中心位置とが略一致している例を示した。一方で、図28Dに示すように、センサ画素12の光学中心OCの位置は、分離絶縁層53の中心位置と略一致していてもよい。本実施形態に係る技術では、分離絶縁層53、及び第2半導体基板21がセンサ画素12の光学中心OCの位置に対して、対称に配置されることが重要である。したがって、センサ画素12の光学中心OCの位置は、分離絶縁層53の中心位置と略一致していてもよく、第2半導体基板21の中心位置と略一致していてもよい。

第1絶縁層46は、第1半導体基板11の表面側に積層され、第2半導体基板21の裏面側と貼り合わせられる。第2半導体基板21は、分離絶縁層53によって分断されており、裏面側にて第1絶縁層46と貼り合わせられる。

第14のバリエーションでは、第2半導体基板21、及び第1絶縁層46の間には、第1反射防止膜71、及び第2反射防止膜72が設けられる。第2反射防止膜72は、第1絶縁層46を構成する材料の屈折率と、第1反射防止膜71を構成する材料の屈折率との間の値の屈折率を有する材料で構成される薄膜である。また、第1反射防止膜71は、第2反射防止膜72を構成する材料の屈折率と、第2半導体基板21を構成する材料の屈折率との間の値の屈折率を有する材料で構成される薄膜である。第1反射防止膜71、及び第2反射防止膜72は、第1絶縁層46から第2半導体基板21への光路において、第13のバリエーションよりもさらに段階的に屈折率を変化させることで、第1絶縁層46、及び第1反射防止膜71の間での入射光の反射をさらに抑制することができる。

例えば、第1絶縁層46が酸化アルミニウム(AlOx)で形成され、第2半導体基板21がシリコン(Si)で形成される場合、第1反射防止膜71、及び第2反射防止膜72は、酸化アルミニウムの屈折率と、シリコンの屈折率との間の屈折率を有する窒化シリコン(SiN)にてそれぞれ形成することができる。

第14のバリエーションに係る撮像装置1では、第1絶縁層46と、第2半導体基板21との貼り合わせ界面に第1反射防止膜71、及び第2反射防止膜72を設けることで、第2半導体基板21から第1半導体基板11への反射自体を抑制することができる。したがって、第14のバリエーションに係る撮像装置1は、同色画素間の感度の不均一性、又は隣接画素へのクロストーク量の不均一性をさらに低減することができる。

<<3.変形例>>

以下では、本開示に係る技術が適用される撮像装置1の変形例について説明する。なお、以下の変形例では、上記で説明した撮像装置1と共通の構成に対しては、同一の符号を付す。

(第1の変形例)

まず、図29を参照して、撮像装置1の積層方向の断面構成の一変形例である第1の変形例について説明する。図29は、図7に記載の断面構成の一変形例を示す縦断面図である。

図29に示すように、第1の変形例に係る撮像装置1では、転送トランジスタTRは、平面型の転送ゲートTGを有する。そのため、転送ゲートTGは、pウェル層42を貫通しておらず、第1半導体基板11の表面に形成される。転送トランジスタTRに平面型の転送ゲートTGが用いられる場合であっても、撮像装置1は、上記と同様の効果を奏することができる。

(第2の変形例)

次に、図30を参照して、撮像装置1の積層方向の断面構成の一変形例である第2の変形例について説明する。図30は、図7に記載の断面構成の一変形例を示す縦断面図である。

図30に示すように、第2の変形例に係る撮像装置1では、第2基板20と第3基板30との電気的な接続が第1基板10における周辺領域14と対応する領域で形成されている。周辺領域14は、第1基板10の画素領域13の周縁に設けられた額縁領域に対応する領域である。第2の変形例に係る撮像装置1では、第2基板20は、周辺領域14と対応する領域に複数のパッド電極58を有し、第3基板30は、周辺領域14と対応する領域に、複数のパッド電極64を有する。これにより、第2基板20、及び第3基板30は、周辺領域14と対応する領域に設けられたパッド電極58、64同士の接合にて、互いに電気的に接続される。したがって、第2の変形例に係る撮像装置1では、画素領域13に対応する領域にてパッド電極58、64同士を接合する場合と比較して、パッド電極58、64同士の接合による影響が画素領域13に及ぶ可能性を低減することができる。

(第3の変形例)

さらに、図31~図36を参照して、第3の変形例に係る撮像装置1Bの構成例について説明する。図31~図33は、第3の変形例に係る撮像装置1Bの構成例を示す厚さ方向の断面図である。図34~図36は、第3の変形例に係る撮像装置1Bの複数の画素ユニットPUのレイアウト例を示す水平方向の断面図である。なお、図34~図36に示す断面図は、あくまで模式図であり、実際の構造を厳密に正しく示すことを目的とした図ではない。図34~図36に示す断面図は、撮像装置1Bの構成を紙面でわかり易く説明するために、位置sec1からsec3で、トランジスタや不純物拡散層の水平方向における位置を意図的に変えて示している。

具体的には、図31に示す撮像装置1Bの画素ユニットPUにおいて、位置sec1における断面は図34をA1-A1’線で切断した断面に対応し、位置sec2における断面は図35をB1-B1’線で切断した断面に対応し、位置sec3における断面は図36をC1-C1’線で切断した断面に対応する。同様に、図32に示す撮像装置1Bにおいて、位置sec1における断面は図34をA2-A2’線で切断した断面に対応し、位置sec2における断面は図35をB2-B2’線で切断した断面に対応し、位置sec3における断面は図36をC2-C2’線で切断した断面に対応する。図33に示す撮像装置1Bにおいて、位置sec1における断面は図34をA3-A3’線で切断した断面に対応し、位置sec2における断面は図35をB3-B3’線で切断した断面に対応し、位置sec3における断面は図36をC3-C3’線で切断した断面に対応する。

図31~図36に示すように、第1基板(ボトム基板)10のおもて面10a(一方の面)側に第2基板20が積層されている。第1基板10のおもて面10a側に、フォトダイオードPD、転送トランジスタTR、及びフローティングディフュージョンFDが設けられている。フォトダイオードPD、転送トランジスタTRおよびフローティングディフュージョンFDは、それぞれ、センサ画素12ごとに設けられている。

第1基板10の他方の面(例えば、裏面)は光入射面である。撮像装置1Bは、裏面照射型の撮像装置であり、裏面にカラーフィルタおよび受光レンズが設けられている。カラーフィルタおよび受光レンズは、それぞれ、センサ画素12ごとに設けられている。

第1基板10が有する第1半導体基板11は、例えばシリコン基板で構成されている。第1半導体基板11のおもて面の一部およびその近傍には、第1導電型(例えば、p型)のウェル層WEが設けられており、ウェル層WEよりも深い領域に第2導電型(例えば、n型)のフォトダイオードPDが設けられている。また、ウェル層WE内には、ウェル層WEよりもp型の濃度が高いウェルコンタクト層と、n型のフローティングディフュージョンFDとが設けられている。ウェルコンタクト層は、ウェル層WEと配線との接触抵抗を低減するために設けられている。

第1半導体基板11には、互いに隣り合うセンサ画素12同士を電気的に分離する素子分離層16が設けられている。素子分離層16は、例えばSTI(Shallow Trench Isolation)構造を有し、第1半導体基板11の深さ方向に延在している。素子分離層16は、例えば、酸化シリコンによって構成されている。また、第1半導体基板11において、素子分離層16とフォトダイオードPDとの間には、不純物拡散層17が設けられている。例えば、不純物拡散層17は、第1半導体基板11の厚さ方向に延設されたp型層とn型層とを有する。素子分離層16側にp型層が位置し、フォトダイオードPD側にn型層が位置する。

第1半導体基板11のおもて面11a側には、絶縁膜2015が設けられている。絶縁膜2015は、例えば、シリコン酸化膜(SiO)、シリコン窒化膜(SiN)、シリコン酸窒化膜(SiON)又はシリコン炭窒化膜(SiCN)のうちの1つ、又は、これらのうち2つ以上を積層した膜である。

第2基板20は、下側基板2210と上側基板2220とを有する。下側基板2210は、半導体基板2211を有する。半導体基板2211は、例えば単結晶シリコンで構成されるシリコン基板である。半導体基板2211の一方の面(例えば、おもて面2211a)側に、増幅トランジスタAMPと、増幅トランジスタAMPの周囲を囲む素子分離層2213とが設けられている。素子分離層2213によって、隣り合う画素ユニットPUの一方の増幅トランジスタAMPと他方の増幅トランジスタAMPは電気的に分離されている。

下側基板2210は、半導体基板2211のおもて面2211aを覆う絶縁膜2215を有する。絶縁膜2215によって、増幅トランジスタAMP及び素子分離層2213は覆われている。また、下側基板2210は、半導体基板2211の他方の面(例えば、裏面2211b)を覆う絶縁膜2217を有する。絶縁膜2215、2217は、例えば、SiO、SiN、SiON又はSiCNのうちの1つ、又は、これらのうち2つ以上を積層した膜である。第1基板10の絶縁膜2015と下側基板2210の絶縁膜2217は互いに接合されて、層間絶縁膜2051を構成している。

上側基板2220は、半導体基板2221を有する。半導体基板2221は、例えば単結晶シリコンで構成されるシリコン基板である。半導体基板2221の一方の面(例えば、おもて面2221a)側に、リセットトランジスタRST及び選択トランジスタSELと、素子分離層2223とが設けられている。例えば、素子分離層2223は、リセットトランジスタRSTと選択トランジスタSELとの間、及び、選択トランジスタSELと半導体基板2221のウェル層との間にそれぞれ設けられている。

上側基板2220は、半導体基板2221のおもて面2221a、裏面2221b及び側面を覆う絶縁膜2225を有する。絶縁膜2225は、例えば、SiO、SiN、SiON又はSiCNのうちの1つ、又は、これらのうち2つ以上を積層した膜である。下側基板2210の絶縁膜2215と上側基板2220の絶縁膜2225は互いに接合されて、層間絶縁膜2053を構成している。

撮像装置1Bは、層間絶縁膜2051、2053中に設けられて、第1基板10又は第2基板20の少なくとも一方に電気的に接続する複数の配線L1からL10を備える。配線L1は、増幅トランジスタAMPのドレインと電源線VDDとを電気的に接続している。配線L2は、1つの画素ユニットPUに含まれる4つのフローティングディフュージョンFDと、増幅トランジスタAMPのゲート電極AGとを電気的に接続している。配線L3は、増幅トランジスタAMPのソースと選択トランジスタSELのドレインとを電気的に接続している。配線L4は、選択トランジスタSELのゲート電極SGと画素駆動線とを電気的に接続している。

配線L5は、選択トランジスタSELのソースと垂直信号線とを電気的に接続している。配線L6は、リセットトランジスタRSTのドレインと電源線VDDとを電気的に接続している。配線L7は、リセットトランジスタRSTのゲート電極RGと画素駆動線とを電気的に接続している。配線L8は、リセットトランジスタRSTのソースと配線L2とを電気的に接続している。配線L9は、転送トランジスタTRのゲート電極TGと画素駆動線とを電気的に接続している。配線L10は、ウェルコンタクト層と、基準電位(例えば、接地電位:0V)を供給する基準電位線とを電気的に接続している。

配線L1~L10において、積層体の厚さ方向に延設されている部分はタングステン(W)で構成されており、積層体の厚さ方向と直交する方向(例えば、水平方向)に延設されている部分は銅(Cu)又はCuを主成分とするCu合金で構成されている。ただし、配線L1~L10を構成する材料は、これらに限定されず、他の材料で構成されていてもよい。

第2基板20は、上記の配線L1~L10のうちの任意の配線(例えば、配線L1、L4~L7、L9、L10)に接続する複数のパッド電極2227を有する。複数のパッド電極2227は、例えばCu又はCu合金で構成されている。

第3基板30は、第2基板20において第1基板10と向かい合う面の反対側(例えば、おもて面側)に配置されている。第3基板30は、半導体基板2301と、半導体基板2301のおもて面2301a側を覆う絶縁膜2304と、半導体基板2301のおもて面2301a側に設けられた複数の配線L30と、複数の配線L30にそれぞれ接続するパッド電極2305と、を備える。なお、第3基板30は、後述するように、第2基板20とおもて面同士が貼り合わされている。このため、半導体基板2301のおもて面2301aは下側を向いている。

半導体基板2301は、例えば単結晶シリコンで構成されるシリコン基板である。半導体基板2301のおもて面2301a側には、ロジック回路を構成する複数のトランジスタ及び不純物拡散層が設けられている。絶縁膜2304は、ロジック回路を構成する複数のトランジスタや不純物拡散層を覆っている。絶縁膜2304には、これらのトランジスタや不純物拡散層に接続するコンタクトホールが設けられている。

配線L30は、コンタクトホール内に設けられている。配線L30において、第3基板30の厚さ方向に延設されている部分はチタン(Ti)又はコバルト(Co)で構成されており、第3基板30厚さ方向と直交する方向(例えば、水平方向)に延設されている部分はCu又はCuを主成分とするCu合金で構成されている。ただし、配線L30を構成する材料は、これらに限定されず、他の材料で構成されていてもよい。

配線L30と半導体基板2301との接続部には、シリサイド2303(例えば、チタンシリサイド(TiSi)又はコバルトシリサイド(CoSi2)が形成されている。シリサイド2303によって、配線L30と半導体基板2301との接続がよりオーミックコンタクトに近いものとなり、接触抵抗が低減されている。これにより、ロジック回路の演算速度の高速化が図られている。

なお、第1基板10及び第2基板20には、シリサイドは形成されていない。これにより、第1基板10と第2基板20とを形成する際に、シリサイドの耐熱温度を超える温度での熱処理等が可能となっている。ただし、第1基板10及び第2基板20の少なくとも一方にシリサイドが形成されていてもよい。

複数のパッド電極2305は、例えばCu又はCu合金で構成されている。撮像装置1Bの厚さ方向において、第3基板30のパッド電極2305は、第2基板20のパッド電極2227と向かい合って電気的に接続している。例えば、パッド電極2305、2227は、互いに向かい合った状態でCu-Cu接合されて一体化している。これにより、第2基板20と第3基板30とが電気的に接続されるとともに、第2基板20と第3基板30との貼り合わせの強度が高められている。

第3の変形例に係る撮像装置1Bでは、複数のセンサ画素12ごとに、1つのフローティングディフュージョン用コンタクトが配置されていてもよい。例えば、互いに隣り合う4つのセンサ画素12が、1つのフローティングディフュージョン用コンタクトを共有していてもよい。同様に、複数のセンサ画素12ごとに、1つのウェル用コンタクトが配置されていてもよい。例えば、互いに隣り合う4つのセンサ画素12が、1つのウェル用コンタクトを共有していてもよい。

具体的には、図32及び図36に示すように、撮像装置1Bは、複数のセンサ画素12に跨るように配置された共通パッド電極2102と、共通パッド電極2102上に設けられた1つの配線L2と、を共有してもよい。例えば、撮像装置1Bには、平面視で、4つのセンサ画素12の各フローティングディフュージョンFD1~FD4が素子分離層16を介して互いに隣り合う領域が存在する。この領域に共通パッド電極2102が設けられている。共通パッド電極2102は、4つのフローティングディフュージョンFD1~FD4に跨るように配置されており、4つのフローティングディフュージョンFD1~FD4とそれぞれ電気的に接続している。共通パッド電極2102は、例えば、n型不純物又はp型不純物がドープされたポリシリコン膜で構成されている。

共通パッド電極2102の中心部上に1つの配線L2(すなわち、フローティングディフュージョン用コンタクト)が設けられている。図32、図34~図36に示すように、共通パッド電極2102の中心部上に設けられた配線L2は、第1基板10から、第2基板20の下側基板2210を貫いて第2基板20の上側基板2220まで延設されており、上側基板2220に設けられた配線等を介して、増幅トランジスタAMPのゲート電極AGに接続している。

また、図31及び図36に示すように、撮像装置1Bは、複数のセンサ画素12に跨るように配置された共通パッド電極2110と、共通パッド電極2110上に設けられた1つの配線L10と、を共有してもよい。例えば、撮像装置1Bには、平面視で、4つのセンサ画素12の各ウェル層WEが素子分離層16を介して互いに隣り合う領域が存在する。この領域に共通パッド電極2110が設けられている。共通パッド電極2110は、4つのセンサ画素12の各ウェル層WEに跨るように配置されており、4つのセンサ画素12の各ウェル層WEとそれぞれ電気的に接続している。一例を挙げると、共通パッド電極2110は、Y軸方向に並ぶ一方の共通パッド電極2102と他方の共通パッド電極2102との間に配置されている。Y軸方向において、共通パッド電極2102、2110は交互に並んで配置されている。共通パッド電極2110は、例えば、n型不純物又はp型不純物がドープされたポリシリコン膜で構成されている。

共通パッド電極2110の中心部上に1つの配線L10(すなわち、ウェル用コンタクト)が設けられている。図31、図34~図36に示すように、共通パッド電極2110の中心部上に設けられた配線L10は、第1基板10から、第2基板20の下側基板2210を貫いて第2基板20の上側基板2220まで延設されており、上側基板2220に設けられた配線等を介して、基準電位(例えば、接地電位:0V)を供給する基準電位線に接続している。

共通パッド電極2110の中心部上に設けられた配線L10は、共通パッド電極2110の上面と、下側基板2210に設けられた貫通孔の内側面と、上側基板2220に設けられた貫通孔の内側面とに、それぞれ電気的に接続している。これにより、第1基板10の第1半導体基板11のウェル層WEと、第2基板20の下側基板2210のウェル層及び上側基板2220のウェル層は、基準電位(例えば、接地電位:0V)に接続される。

第3の変形例に係る撮像装置1Bは、第1基板10を構成する第1半導体基板11のおもて面11a側に設けられ、互いに隣り合う複数(例えば、4つ)のセンサ画素12に跨るように配置された共通パッド電極2102、2110をさらに備える。共通パッド電極2102は、4つのセンサ画素12のフローティングディフュージョンFDと電気的に接続しているため、4つのセンサ画素12ごとに、フローティングディフュージョンFDに接続する配線L2を共通化することができる。また、共通パッド電極2110は、4つのセンサ画素12のウェル層WEと電気的に接続しているため、4つのセンサ画素12ごとに、ウェル層WEに接続する配線L10を共通化することができる。これにより、配線L2、L10の本数が低減されるため、センサ画素12の面積低減が可能であり、撮像装置1Bの小型化が可能である。

(第4の変形例)

続いて、図37及び図38を参照して、撮像装置1の水平方向の断面構成の一変形例である第4の変形例について説明する。図37及び図38の上側の図は、図7における切断面Sec1の断面構成の一変形例を示す模式図であり、図37及び図38の下側の図は、図7における切断面Sec2の断面構成の一変形例を示す模式図である。

図37及び図38に示すように、複数の貫通配線54、複数の貫通配線48、及び複数の貫通配線47は、第1基板10の面内において第1方向V1(図37及び図38の左右方向)に帯状に並んで配置される。図37及び図38では、複数の貫通配線54、複数の貫通配線48、及び複数の貫通配線47が第1方向V1に2列に並んで配置されている場合が例示されている。

画素回路22を共有する4つのセンサ画素12において、4つのフローティングディフュージョンFDは、例えば、素子分離部43を介して互いに近接して配置される。画素回路22を共有する4つのセンサ画素12において、4つの転送ゲートTG(TG1、TG2、TG3、TG4)は、4つのフローティングディフュージョンFDを囲むように配置される。例えば、4つの転送ゲートTGは、円環形状となるように配置される。

分離絶縁層53は、第1方向V1に延伸する複数のブロックで構成されている。第2半導体基板21は、第1方向V1に延伸し、かつ第1方向V1に並んで配置された複数の島状のブロック21Aで構成される。ブロック21Aの各々には、例えば、リセットトランジスタRST、増幅トランジスタAMP、及び選択トランジスタSELが設けられる。4つのセンサ画素12によって共有される1つの画素回路22は、例えば、4つのセンサ画素12と対応して配置されておらず、第2方向V2にずれて配置される。

図37では、4つのセンサ画素12によって共有される1つの画素回路22は、第2基板20において、4つのセンサ画素12と対応する領域を第2方向V2にずらした領域内にあるリセットトランジスタRST、増幅トランジスタAMP、及び選択トランジスタSELによって構成される。例えば、4つのセンサ画素12によって共有される1つの画素回路22は、1つのブロック21A内の増幅トランジスタAMP、リセットトランジスタRST、及び選択トランジスタSELによって構成される。

図38では、4つのセンサ画素12によって共有される1つの画素回路22は、第2基板20において、4つのセンサ画素12と対応する領域を第2方向V2にずらした領域内にあるリセットトランジスタRST、増幅トランジスタAMP、選択トランジスタSEL、及びFD変換ゲイン切替トランジスタFDGによって構成される。例えば、4つのセンサ画素12によって共有される1つの画素回路22は、1つのブロック21A内の増幅トランジスタAMP、リセットトランジスタRST、選択トランジスタSEL、及びFD変換ゲイン切替トランジスタFDGによって構成される。

第4の変形例に係る撮像装置1では、4つのセンサ画素12によって共有される1つの画素回路22は、4つのセンサ画素12と正対して配置されておらず、4つのセンサ画素12と正対する位置から第2方向V2にずれて配置されている。この構成によれば、第4の変形例に係る撮像装置1は、配線25を短くしたり、配線25を省略して増幅トランジスタAMPのソースと、選択トランジスタSELのドレインとを共通の不純物領域で構成したりすることが可能となる。したがって、第4の変形例に係る撮像装置1は、画素回路22のサイズを小さくすることが可能となる。

(第5の変形例)

次に、図39を参照して、撮像装置1の水平方向の断面構成の一変形例である第5の変形例について説明する。図39は、図7における切断面Sec1、及び切断面Sec2の断面構成の一変形例を示す模式図である。

図39に示すように、第2半導体基板21は、分離絶縁層53を介して第1方向V1、及び第2方向V2に並んで配置された複数の島状のブロック21Aで構成されている。ブロック21Aの各々には、例えば、一組のリセットトランジスタRST、増幅トランジスタAMP、及び選択トランジスタSELが設けられている。このような場合、第5の変形例に係る撮像装置1は、互いに隣接する画素回路22同士でのクロストークを分離絶縁層53によって抑制することができるため、画像の解像度低下、又は混色による画質低下を抑制することができる。

(第6の変形例)

続いて、図40を参照して、撮像装置1の水平方向の断面構成の一変形例である第6の変形例について説明する。図40は、図7における切断面Sec1、及び切断面Sec2の断面構成の一変形例を示す模式図である。

図40では、第2半導体基板21は、4つのセンサ画素12によって共有される1つの画素回路22は、例えば、4つのセンサ画素12と対応して配置されておらず、第1方向V1にずれて配置されている。また、第6の変形例に係る撮像装置1では、第2半導体基板21は、分離絶縁層53を介して第1方向V1、及び第2方向V2に並んで配置された複数の島状のブロック21Aで構成される。ブロック21Aの各々には、例えば、一組のリセットトランジスタRST、増幅トランジスタAMP、及び選択トランジスタSELが設けられる。さらに、第6の変形例に係る撮像装置1では、複数の貫通配線47、及び複数の貫通配線54が、第2方向V2に配列される。

これにより、複数の貫通配線47は、1つの画素回路22を共有する4つの貫通配線54と、該画素回路22の第2方向V2に隣接する他の画素回路22を共有する4つの貫通配線54との間に配置される。これによれば、第6の変形例に係る撮像装置1は、互いに隣接する画素回路22同士のクロストークを分離絶縁層53、及び貫通配線47によって抑制することができるため、画像の解像度低下、又は混色による画質低下を抑制することができる。

(第7の変形例)

次に、図41~図43を参照して、撮像装置1の水平方向の断面構成の一変形例である第7の変形例について説明する。図41は、図7における切断面Sec1、及び切断面Sec2の断面構成の一変形例を示す模式図である。

図41に示すように、第7の変形例に係る撮像装置1では、第1基板10は、フォトダイオードPD、及び転送トランジスタTR(すなわち、転送ゲートTG)をセンサ画素12ごとに有し、フローティングディフュージョンFDを4つのセンサ画素12ごとに共有している。そのため、第7の変形例に係る撮像装置1は、4つのセンサ画素12ごとに1つの貫通配線54が設けられている。

また、第7の変形例に係る撮像装置1では、1つのフローティングディフュージョンFDを共有する4つのセンサ画素12に対応する単位領域を1つのセンサ画素12分だけ第2方向V2にずらした領域ごとに、貫通配線47が設けられている。すなわち、第7の変形例に係る撮像装置1では、1つのフローティングディフュージョンFDを共有する4つのセンサ画素12に対応する単位領域と、該単位領域と第2方向V2に隣接する隣接単位領域との間に貫通配線47が設けられる。また、貫通配線47は、貫通配線47の周囲に存在する単位領域の2つのセンサ画素12、及び貫通配線47の周囲に存在する隣接単位領域の2つのセンサ画素12にて共有されている。

さらに、第7の変形例に係る撮像装置1では、第1基板10は、フォトダイオードPD、及び転送トランジスタTRをセンサ画素12ごとに分離する素子分離部43を有する。第1半導体基板11の主面を法線方向から平面視した場合、素子分離部43は、センサ画素12の周囲を完全に囲っておらず、フローティングディフュージョンFD(すなわち、貫通配線54)の近傍、及び貫通配線47の近傍に間隙(未形成領域)を有している。この間隙によって、4つのセンサ画素12による貫通配線54の共有、及び単位領域と隣接単位領域との間での4つのセンサ画素12による貫通配線47の共有が可能となる。なお、第7の変形例に係る撮像装置1では、第2基板20は、フローティングディフュージョンFDを共有する4つのセンサ画素12ごとに画素回路22を有する。

図42及び図43は、第7の変形例に係る撮像装置1の切断面Sec2の断面構成の他の例を示す模式図である。図42に示すように、第1基板10は、フォトダイオードPD、及び転送トランジスタTRをセンサ画素12ごとに有し、フローティングディフュージョンFDを4つのセンサ画素12ごとに共有していてもよい。さらに、第1基板10は、フォトダイオードPD、及び転送トランジスタTRをセンサ画素12ごとに分離する素子分離部43を有していてもよい。また、図43に示すように、フォトダイオードPD、及び転送トランジスタTRをセンサ画素12ごとに有し、フローティングディフュージョンFDを4つのセンサ画素12ごとに共有していてもよい。さらに、第1基板10は、フォトダイオードPD、及び転送トランジスタTRをセンサ画素12ごとに分離する素子分離部43を有していてもよい。

(第8の変形例)

続いて、図44を参照して、撮像装置1の回路構成の一変形例である第8の変形例について説明する。図44は、列並列ADC(Analog to Digital Converter)搭載のCMOSイメージセンサの回路構成を示す模式図である。

図44に示すように、第8の変形例に係る撮像装置1は、光電変換素子を含む複数のセンサ画素12が行列状(すなわち、マトリクス状)に二次元配置された画素領域13と、垂直駆動回路33と、カラム信号処理回路34と、参照電圧供給部38と、水平駆動回路35と、水平出力線37と、システム制御回路36とを備える。

システム制御回路36は、マスタークロックMCKに基づいて、垂直駆動回路33、カラム信号処理回路34、参照電圧供給部38、及び水平駆動回路35などの動作の基準となるクロック信号、及び制御信号などを生成する。システム制御回路36は、さらに、生成したクロック信号、及び制御信号を垂直駆動回路33、カラム信号処理回路34、参照電圧供給部38、及び水平駆動回路35に供給する。

垂直駆動回路33は、画素領域13のセンサ画素12の各々が形成された第1基板10、及び画素回路22が形成された第2基板20にそれぞれ形成される。カラム信号処理回路34、参照電圧供給部38、水平駆動回路35、水平出力線37、及びシステム制御回路36は、第3基板30に形成される。

ここでの図示は省略するが、センサ画素12は、例えば、フォトダイオードPDと、フォトダイオードPDで光電変換された電荷をフローティングディフュージョンFDに転送する転送トランジスタTRとを有する。画素回路22は、例えば、フローティングディフュージョンFDの電位を制御するリセットトランジスタRSTと、フローティングディフュージョンFDの電位に応じた信号を出力する増幅トランジスタAMPと、画素選択を行うための選択トランジスタSELとを有する。

画素領域13には、センサ画素12が二次元配置される。例えば、n行m列のマトリクス状にセンサ画素12が配置された画素領域13では、行ごとに画素駆動線23が配線され、列ごとに垂直信号線24が配線される。複数の画素駆動線23の一端には、垂直駆動回路33の各行に対応した出力端がそれぞれ接続されている。垂直駆動回路33は、シフトレジスタなどによって構成され、複数の画素駆動線23を介して画素領域13の行アドレス又は行走査の制御を行う。

カラム信号処理回路34は、例えば、画素領域13の画素列ごと、すなわち垂直信号線24ごとに設けられたADC(アナログ-デジタル変換回路)34-1~34-mを有する。カラム信号処理回路34は、ADCによって、画素領域13のセンサ画素12の各々から列ごとに出力されるアナログ信号をデジタル信号に変換して出力する。

参照電圧供給部38は、例えば、DAC(デジタル-アナログ変換回路)38Aを有し、時間が経過するにつれてレベルが傾斜状に変化する、いわゆるランプ(RAMP)波形の参照電圧Vrefを生成する。なお、参照電圧供給部38は、DAC38A以外の手段を用いて、ランプ波形の参照電圧Vrefを生成してもよい。

DAC38Aは、システム制御回路36からの制御信号CS1、及びクロックCKに基づいてランプ波形の参照電圧Vrefを生成し、生成した参照電圧Vrefをカラム信号処理回路34のADC34-1~34-mに対して供給する。

なお、ADC34-1~34-mの各々は、センサ画素12全ての情報を読み出すプログレッシブ走査方式での通常フレームレートモードと、通常フレームレートモード時に比べてセンサ画素12の露光時間を1/Nに設定することでフレームレートをN倍(例えば、2倍)に引き上げる高速フレームレートモードとの各動作モードに対応したAD変換動作を選択的に実行可能に構成される。この動作モードの切り替えは、システム制御回路36からの制御信号CS2、CS3による制御によって行われる。また、システム制御回路36は、外部のシステムコントローラ(図示せず)からの指示情報に基づいて、通常フレームレートモードと高速フレームレートモードの各動作モードとを切り替えるための制御信号CS2、CS3を生成する。

ADC34-1~34-mは、全て同じ構成であるため、ここではADC34-mを例に挙げて説明する。

ADC34-mは、比較器34Aと、アップ/ダウンカウンタ(U/DCNT)34Bと、転送スイッチ34Cと、メモリ装置34Dとを有する。

比較器34Aは、画素領域13のm列目のセンサ画素12の各々から出力される信号に応じた垂直信号線24の信号電圧Vxと、参照電圧供給部38から供給されるランプ波形の参照電圧Vrefとを比較する。比較器34Aは、例えば、参照電圧Vrefが信号電圧Vxよりも大きい場合に出力Vcoを「H」レベルとし、参照電圧Vrefが信号電圧Vx以下の場合に出力Vcoを「L」レベルとする。

アップ/ダウンカウンタ34Bは、非同期カウンタである。アップ/ダウンカウンタ34Bは、システム制御回路36から与えられる制御信号CS2に基づいて、システム制御回路36からクロックCKを供給される。アップ/ダウンカウンタ34Bは、該クロックCKに同期してダウン(DOWN)カウント、又はアップ(UP)カウントを行うことにより、比較器34Aでの比較動作の開始から終了までの比較期間を計測する。

具体的には、通常フレームレートモードでは、アップ/ダウンカウンタ34Bは、1つのセンサ画素12からの1回目の読み出し動作時にダウンカウントを行うことにより1回目の読み出し時の比較時間を計測する。また、アップ/ダウンカウンタ34Bは、2回目の読み出し動作時にアップカウントを行うことにより2回目の読み出し時の比較時間を計測する。

一方、高速フレームレートモードでは、アップ/ダウンカウンタ34Bは、ある行のセンサ画素12についてのカウント結果をそのまま保持する。その後、アップ/ダウンカウンタ34Bは、次の行のセンサ画素12について、前回のカウント結果を引き継いで1回目の読み出し動作時のダウンカウントを行うことで1回目の読み出し時の比較時間を計測する。また、アップ/ダウンカウンタ34Bは、2回目の読み出し動作時にアップカウントを行うことで2回目の読み出し時の比較時間を計測する。

転送スイッチ34Cは、システム制御回路36から与えられる制御信号CS3に基づいて動作する。転送スイッチ34Cは、通常フレームレートモードでは、ある行のセンサ画素12についてのアップ/ダウンカウンタ34Bのカウント動作が完了した時点でオン(閉)状態となることで、アップ/ダウンカウンタ34Bのカウント結果をメモリ装置34Dに転送する。

一方、例えばN=2の高速フレームレートでは、転送スイッチ34Cは、ある行のセンサ画素12についてのアップ/ダウンカウンタ34Bのカウント動作が完了した時点でオフ(開)状態のままとなる。その後、転送スイッチ34Cは、次の行のセンサ画素12についてのアップ/ダウンカウンタ34Bのカウント動作が完了した時点でオン状態となることで、アップ/ダウンカウンタ34Bの垂直2画素分についてのカウント結果をメモリ装置34Dに転送する。

このようにして、画素領域13のセンサ画素12の各々から垂直信号線24を経由して列ごとに供給されるアナログ信号は、ADC34-1~34-mにおける比較器34A、及びアップ/ダウンカウンタ34Bの動作により、Nビットのデジタル信号に変換されてメモリ装置34Dに格納される。

水平駆動回路35は、シフトレジスタなどによって構成され、カラム信号処理回路34におけるADC34-1~34-mの列アドレス、及び列走査の制御を行う。水平駆動回路35は、ADC34-1~34-mの各々を制御することで、AD変換されたNビットのデジタル信号を順に水平出力線37に読み出させる。読み出されたNビットのデジタル信号は、水平出力線37を経由して撮像データとして出力される。

なお、本特に図示しないが、水平出力線37を経由して出力される撮像データに対して各種の信号処理を施す回路等を上記構成要素以外に設けることも可能である。

第8の変形例に係る撮像装置1では、転送スイッチ34Cを介してアップ/ダウンカウンタ34Bのカウント結果を選択的にメモリ装置34Dに転送することができる。これによれば、第8の変形例に係る撮像装置1では、アップ/ダウンカウンタ34Bのカウント動作と、アップ/ダウンカウンタ34Bのカウント結果の水平出力線37への読み出し動作とを独立して制御することが可能である。

(第9の変形例)

次に、図45を参照して、撮像装置1の積層構造の一変形例である第9の変形例について説明する。図45は、図38に示す撮像装置1を3つの基板を積層して構成した一例を示す模式図である。

図45に示すように、第9の変形例に係る撮像装置1は、第1基板10、第2基板20、及び第3基板を積層して構成される。第1基板10では、中央部分に複数のセンサ画素12を含む画素領域13が形成されており、画素領域13の周囲に垂直駆動回路33が形成されている。また、第2基板20では、中央部分に、複数の画素回路22を含む画素回路領域15が形成されており、画素回路領域15の周囲に垂直駆動回路33が形成されている。さらに、第3基板30では、カラム信号処理回路34、水平駆動回路35、システム制御回路36、水平出力線37、及び参照電圧供給部38が形成されている。なお、垂直駆動回路33は、上述したように第1基板10、及び第2基板20の両方に形成されてもよく、第1基板10のみに形成されてもよく、第2基板20のみに形成されてもよい。

第9の変形例に係る撮像装置1は、基板同士を電気的に接続する構造に起因するチップサイズの拡大、又は画素面積の拡大を抑制することができる。これによれば、第9の変形例に係る撮像装置1は、1画素あたりの面積をより微細化することが可能となる。

(第10の変形例)

続いて、図46及び図47を参照して、撮像装置1の断面構成の一変形例である第10の変形例について説明する。図46は、第10の変形例に係る撮像装置1の断面構成の一例を示す模式図である。

上記で説明した実施形態、及び変形例では、撮像装置1は、第1基板10、第2基板20、及び第3基板30の3つの基板を積層して構成される例を示した。しかしながら、本開示に係る技術は、上記例示に限定されない。例えば、撮像装置1は、第1基板10、及び第2基板20の2つの基板を積層して構成されてもよい。

図46に示すように、このような場合、処理回路32は、例えば、第1基板10と、第2基板20とに分けて形成される。

処理回路32のうち第1基板10側に設けられた回路32Aでは、高温プロセスに耐え得る材料(例えば、high-k材料)からなる高誘電率膜と、メタルゲート電極とを積層したゲート構造を有するトランジスタが設けられる。

一方、処理回路32のうち第2基板20側に設けられた回路32Bでは、ソース電極及びドレイン電極と接する不純物拡散領域の表面に、CoSi2又はNiSiなどのシリサイドからなる低抵抗領域26が形成されている。シリサイドからなる低抵抗領域は、半導体基板の材料と金属との化合物で形成されており、耐熱性が高い。したがって、センサ画素12を形成する際に熱酸化などの高温プロセスを用いることができるようになる。また、CoSi2又はNiSiなどのシリサイドからなる低抵抗領域26は、接触抵抗を低減することができるため、処理回路32での演算速度を高速化することができる。

なお、CoSi2又はNiSiなどのシリサイドからなる低抵抗領域26は、上記で説明した実施形態、及び変形例に係る撮像装置1に設けられてもよい。具体的には、第1基板10、第2基板20、及び第3基板30の3つの基板を積層して構成される撮像装置1においても、CoSi2又はNiSiなどのシリサイドからなる低抵抗領域26が設けられてもよい。図47は、3つの基板を積層して構成される撮像装置1にCoSi2又はNiSiなどのシリサイドからなる低抵抗領域26を適用した例を示す模式図である。

図47に示すように、第3基板30の処理回路32において、ソース電極及びドレイン電極と接する不純物拡散領域の表面に、CoSi2又はNiSiなどのシリサイドからなる低抵抗領域26が形成されてもよい。これにより、センサ画素12を形成する際に、熱酸化などの高温プロセスを用いることができるようになる。また、CoSi2又はNiSiなどのシリサイドからなる低抵抗領域26は、接触抵抗を低減することができるため、処理回路32での演算速度を高速化することができる。

<<4.具体例>>

上記で説明した本開示に係る技術は、種々の撮像装置等に適用することが可能である。以下では、本開示に係る技術が適用される撮像装置、及び該撮像装置を備える機器について、具体例を挙げて説明する。

<4.1.実施の形態>

[撮像装置1の機能構成]

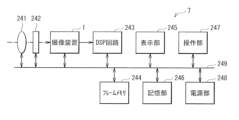

図48は、本開示の一実施の形態に係る撮像装置(撮像装置1)の機能構成の一例を示すブロック図である。

図48の撮像装置1は、例えば、入力部510A、行駆動部520、タイミング制御部530、画素アレイ部540、列信号処理部550、画像信号処理部560および出力部510Bを含んでいる。

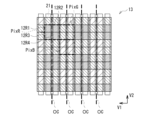

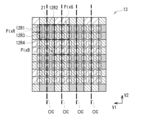

画素アレイ部540には、画素541がアレイ状に繰り返し配置されている。より具体的には、複数の画素を含んだ画素共有ユニット539が繰り返し単位となり、これが、行方向と列方向とからなるアレイ状に繰り返し配置されている。なお、本明細書では、便宜上、行方向をH方向、行方向と直交する列方向をV方向、と呼ぶ場合がある。図48の例において、1つの画素共有ユニット539が、4つの画素(画素541A,541B,541C,541D)を含んでいる。画素541A,541B,541C,541Dは各々、フォトダイオードPD(後述の図53等に図示)を有している。画素共有ユニット539は、1つの画素回路(後述の図50の画素回路210)を共有する単位である。換言すれば、4つの画素(画素541A,541B,541C,541D)毎に、1つの画素回路(後述の画素回路210)を有している。この画素回路を時分割で動作させることにより、画素541A,541B,541C,541D各々の画素信号が順次読み出されるようになっている。画素541A,541B,541C,541Dは、例えば2行×2列で配置されている。画素アレイ部540には、画素541A,541B,541C,541Dとともに、複数の行駆動信号線542および複数の垂直信号線(列読出し線)543が設けられている。行駆動信号線542は、画素アレイ部540において行方向に並んで配列された、複数の画素共有ユニット539各々に含まれる画素541を駆動する。画素共有ユニット539のうち、行方向に並んで配列された各画素を駆動する。後に図51を参照して詳しく説明するが、画素共有ユニット539には、複数のトランジスタが設けられている。これら複数のトランジスタをそれぞれ駆動するために、1つの画素共有ユニット539には複数の行駆動信号線542が接続されている。垂直信号線(列読出し線)543には、画素共有ユニット539が接続されている。画素共有ユニット539に含まれる画素541A,541B,541C,541D各々から、垂直信号線(列読出し線)543を介して画素信号が読み出される。

行駆動部520は、例えば、画素駆動するための行の位置を決める行アドレス制御部、言い換えれば、行デコーダ部と、画素541A,541B,541C,541Dを駆動するための信号を発生させる行駆動回路部とを含んでいる。

列信号処理部550は、例えば、垂直信号線543に接続され、画素541A,541B,541C,541D(画素共有ユニット539)とソースフォロア回路を形成する負荷回路部を備える。列信号処理部550は、垂直信号線543を介して画素共有ユニット539から読み出された信号を増幅する増幅回路部を有していてもよい。列信号処理部550は、ノイズ処理部を有していてもよい。ノイズ処理部では、例えば、光電変換の結果として画素共有ユニット539から読み出された信号から、系のノイズレベルが取り除かれる。

列信号処理部550は、例えば、アナログデジタルコンバータ(ADC)を有している。アナログデジタルコンバータでは、画素共有ユニット539から読み出された信号もしくは上記ノイズ処理されたアナログ信号がデジタル信号に変換される。ADCは、例えば、コンパレータ部およびカウンタ部を含んでいる。コンパレータ部では、変換対象となるアナログ信号と、これと比較対象となる参照信号とが比較される。カウンタ部では、コンパレータ部での比較結果が反転するまでの時間が計測されるようになっている。列信号処理部550は、読出し列を走査する制御を行う水平走査回路部を含んでいてもよい。

タイミング制御部530は、装置へ入力された基準クロック信号やタイミング制御信号を基にして、行駆動部520および列信号処理部550へ、タイミングを制御する信号を供給する。

画像信号処理部560は、光電変換の結果得られたデータ、言い換えれば、撮像装置1における撮像動作の結果得られたデータに対して、各種の信号処理を施す回路である。画像信号処理部560は、例えば、画像信号処理回路部およびデータ保持部を含んでいる。画像信号処理部560は、プロセッサ部を含んでいてもよい。

画像信号処理部560において実行される信号処理の一例は、AD変換された撮像データが、暗い被写体を撮影したデータである場合には階調を多く持たせ、明るい被写体を撮影したデータである場合には階調を少なくするトーンカーブ補正処理である。この場合、撮像データの階調をどのようなトーンカーブに基づいて補正するか、トーンカーブの特性データを予め画像信号処理部560のデータ保持部に記憶させておくことが望ましい。

入力部510Aは、例えば、上記基準クロック信号、タイミング制御信号および特性データなどを装置外部から撮像装置1へ入力するためのものである。タイミング制御信号は、例えば、垂直同期信号および水平同期信号などである。特性データは、例えば、画像信号処理部560のデータ保持部へ記憶させるためのものである。入力部510Aは、例えば、入力端子511、入力回路部512、入力振幅変更部513、入力データ変換回路部514および電源供給部(不図示)を含んでいる。

入力端子511は、データを入力するための外部端子である。入力回路部512は、入力端子511へ入力された信号を撮像装置1の内部へと取り込むためのものである。入力振幅変更部513では、入力回路部512で取り込まれた信号の振幅が、撮像装置1の内部で利用しやすい振幅へと変更される。入力データ変換回路部514では、入力データのデータ列の並びが変更される。入力データ変換回路部514は、例えば、シリアルパラレル変換回路により構成されている。このシリアルパラレル変換回路では、入力データとして受け取ったシリアル信号がパラレル信号へと変換される。なお、入力部510Aでは、入力振幅変更部513および入力データ変換回路部514が、省略されていてもよい。電源供給部は、外部から撮像装置1へ供給された電源をもとにして、撮像装置1の内部で必要となる各種の電圧に設定された電源を供給する。

撮像装置1が外部のメモリデバイスと接続されるとき、入力部510Aには、外部のメモリデバイスからのデータを受け取るメモリインタフェース回路が設けられていてもよい。外部のメモリデバイスは、例えば、フラッシュメモリ、SRAMおよびDRAM等である。

出力部510Bは、画像データを装置外部へと出力する。この画像データは、例えば、撮像装置1で撮影された画像データ、および、画像信号処理部560で信号処理された画像データ等である。出力部510Bは、例えば、出力データ変換回路部515、出力振幅変更部516、出力回路部517および出力端子518を含んでいる。

出力データ変換回路部515は、例えば、パラレルシリアル変換回路により構成されており、出力データ変換回路部515では、撮像装置1内部で使用したパラレル信号がシリアル信号へと変換される。出力振幅変更部516は、撮像装置1の内部で用いた信号の振幅を変更する。変更された振幅の信号は、撮像装置1の外部に接続される外部デバイスで利用しやすくなる。出力回路部517は、撮像装置1の内部から装置外部へとデータを出力する回路であり、出力回路部517により、出力端子518に接続された撮像装置1外部の配線が駆動される。出力端子518では、撮像装置1から装置外部へとデータが出力される。出力部510Bでは、出力データ変換回路部515および出力振幅変更部516が、省略されていてもよい。

撮像装置1が外部のメモリデバイスと接続されるとき、出力部510Bには、外部のメモリデバイスへとデータを出力するメモリインタフェース回路が設けられていてもよい。外部のメモリデバイスは、例えば、フラッシュメモリ、SRAMおよびDRAM等である。

[撮像装置1の概略構成]

図49および図50は、撮像装置1の概略構成の一例を表したものである。撮像装置1は、3つの基板(第1基板100、第2基板200、第3基板300)を備えている。図49は、第1基板100、第2基板200、第3基板300各々の平面構成を模式的に表したものであり、図50は、互いに積層された第1基板100、第2基板200および第3基板300の断面構成を模式的に表している。図50は、図49に示したIII-III’線に沿った断面構成に対応する。撮像装置1は、3つの基板(第1基板100、第2基板200、第3基板300)を貼り合わせて構成された3次元構造の撮像装置である。第1基板100は、半導体層100Sおよび配線層100Tを含む。第2基板200は、半導体層200Sおよび配線層200Tを含む。第3基板300は、半導体層300Sおよび配線層300Tを含む。ここで、第1基板100、第2基板200および第3基板300の各基板に含まれる配線とその周囲の層間絶縁膜を合せたものを、便宜上、それぞれの基板(第1基板100、第2基板200および第3基板300)に設けられた配線層(100T、200T、300T)と呼ぶ。第1基板100、第2基板200および第3基板300は、この順に積層されており、積層方向に沿って、半導体層100S、配線層100T、半導体層200S、配線層200T、配線層300Tおよび半導体層300Sの順に配置されている。第1基板100、第2基板200および第3基板300の具体的な構成については後述する。図50に示した矢印は、撮像装置1への光Lの入射方向を表す。本明細書では、便宜上、以降の断面図で、撮像装置1における光入射側を「下」「下側」「下方」、光入射側と反対側を「上」「上側」「上方」と呼ぶ場合がある。また、本明細書では、便宜上、半導体層と配線層を備えた基板に関して、配線層の側を表面、半導体層の側を裏面と呼ぶ場合がある。なお、明細書の記載は、上記の呼び方に限定されない。撮像装置1は、例えば、フォトダイオードを有する第1基板100の裏面側から光が入射する、裏面照射型撮像装置となっている。

画素アレイ部540および画素アレイ部540に含まれる画素共有ユニット539は、ともに、第1基板100および第2基板200の双方を用いて構成されている。第1基板100には、画素共有ユニット539が有する複数の画素541A,541B,541C,541Dが設けられている。これらの画素541のそれぞれが、フォトダイオード(後述のフォトダイオードPD)および転送トランジスタ(後述の転送トランジスタTR)を有している。第2基板200には、画素共有ユニット539が有する画素回路(後述の画素回路210)が設けられている。画素回路は、画素541A,541B,541C,541D各々のフォトダイオードから転送トランジスタを介して転送された画素信号を読み出し、あるいは、フォトダイオードをリセットする。この第2基板200は、このような画素回路に加えて、行方向に延在する複数の行駆動信号線542および列方向に延在する複数の垂直信号線543を有している。第2基板200は、更に、行方向に延在する電源線544(後述の電源線VDD等)を有している。第3基板300は、例えば、入力部510A,行駆動部520、タイミング制御部530、列信号処理部550、画像信号処理部560および出力部510Bを有している。行駆動部520は、例えば、第1基板100、第2基板200および第3基板300の積層方向(以下、単に積層方向という)において、一部が画素アレイ部540に重なる領域に設けられている。より具体的には、行駆動部520は、積層方向において、画素アレイ部540のH方向の端部近傍に重なる領域に設けられている(図49)。列信号処理部550は、例えば、積層方向において、一部が画素アレイ部540に重なる領域に設けられている。より具体的には、列信号処理部550は、積層方向において、画素アレイ部540のV方向の端部近傍に重なる領域に設けられている(図49)。図示は省略するが、入力部510Aおよび出力部510Bは、第3基板300以外の部分に配置されていてもよく、例えば、第2基板200に配置されていてもよい。あるいは、第1基板100の裏面(光入射面)側に入力部510Aおよび出力部510Bを設けるようにしてもよい。なお、上記第2基板200に設けられた画素回路は、別の呼称として、画素トランジスタ回路、画素トランジスタ群、画素トランジスタ、画素読み出し回路または読出回路と呼ばれることもある。本明細書では、画素回路との呼称を用いる。

第1基板100と第2基板200とは、例えば、貫通電極(後述の図53の貫通電極120E,121E)により電気的に接続されている。第2基板200と第3基板300とは、例えば、コンタクト部201,202,301,302を介して電気的に接続されている。第2基板200にコンタクト部201,202が設けられ、第3基板300にコンタクト部301,302が設けられている。第2基板200のコンタクト部201が第3基板300のコンタクト部301に接し、第2基板200のコンタクト部202が第3基板300のコンタクト部302に接している。第2基板200は、複数のコンタクト部201が設けられたコンタクト領域201Rと、複数のコンタクト部202が設けられたコンタクト領域202Rとを有している。第3基板300は、複数のコンタクト部301が設けられたコンタクト領域301Rと、複数のコンタクト部302が設けられたコンタクト領域302Rとを有している。コンタクト領域201R,301Rは、積層方向において、画素アレイ部540と行駆動部520との間に設けられている(図50)。換言すれば、コンタクト領域201R,301Rは、例えば、行駆動部520(第3基板300)と、画素アレイ部540(第2基板200)とが積層方向に重なる領域、もしくはこの近傍領域に設けられている。コンタクト領域201R,301Rは、例えば、このような領域のうち、H方向の端部に配置されている(図49)。第3基板300では、例えば、行駆動部520の一部、具体的には行駆動部520のH方向の端部に重なる位置にコンタクト領域301Rが設けられている(図49,図50)。コンタクト部201,301は、例えば、第3基板300に設けられた行駆動部520と、第2基板200に設けられた行駆動信号線542とを接続するものである。コンタクト部201,301は、例えば、第3基板300に設けられた入力部510Aと電源線544および基準電位線(後述の基準電位線VSS)とを接続していてもよい。コンタクト領域202R,302Rは、積層方向において、画素アレイ部540と列信号処理部550との間に設けられている(図50)。換言すれば、コンタクト領域202R,302Rは、例えば、列信号処理部550(第3基板300)と画素アレイ部540(第2基板200)とが積層方向に重なる領域、もしくはこの近傍領域に設けられている。コンタクト領域202R,302Rは、例えば、このような領域のうち、V方向の端部に配置されている(図49)。第3基板300では、例えば、列信号処理部550の一部、具体的には列信号処理部550のV方向の端部に重なる位置にコンタクト領域301Rが設けられている(図49,図50)。コンタクト部202,302は、例えば、画素アレイ部540が有する複数の画素共有ユニット539各々から出力された画素信号(フォトダイオードでの光電変換の結果発生した電荷の量に対応した信号)を、第3基板300に設けられた列信号処理部550へと接続するためのものである。画素信号は、第2基板200から第3基板300に送られるようになっている。

図50は、上記のように、撮像装置1の断面図の一例である。第1基板100、第2基板200、第3基板300は、配線層100T、200T、300Tを介して電気的に接続される。例えば、撮像装置1は、第2基板200と第3基板300とを電気的に接続する電気的接続部を有する。具体的には、導電材料で形成された電極でコンタクト部201,202,301,302を形成する。導電材料は、例えば、銅(Cu)、アルミニウム(Al)、金(Au)、などの金属材料で形成される。コンタクト領域201R、202R、301R、302Rは、例えば電極として形成された配線同士を直接接合することで、第2基板と第3基板とを電気的に接続し、第2基板200と第3基板300との信号の入力及び/又は出力を可能にする。

第2基板200と第3基板300とを電気的に接続する電気的接続部は、所望の箇所に設けることができる。例えば、図50においてコンタクト領域201R、202R、301R、302Rとして述べたように、画素アレイ部540と積層方向に重なる領域に設けても良い。また、電気的接続部を画素アレイ部540と積層方向に重ならない領域に設けても良い。具体的には、画素アレイ部540の外側に配置された周辺部と、積層方向に重なる領域に設けても良い。

第1基板100および第2基板200には、例えば、接続孔部H1,H2が設けられている。接続孔部H1,H2は、第1基板100および第2基板200を貫通している(図50)。接続孔部H1,H2は、画素アレイ部540(または画素アレイ部540に重なる部分)の外側に設けられている(図49)。例えば、接続孔部H1は、H方向において画素アレイ部540より外側に配置されており、接続孔部H2は、V方向において画素アレイ部540よりも外側に配置されている。例えば、接続孔部H1は、第3基板300に設けられた入力部510Aに達しており、接続孔部H2は、第3基板300に設けられた出力部510Bに達している。接続孔部H1,H2は、空洞でもよく、少なくとも一部に導電材料を含んでいても良い。例えば、入力部510A及び/又は出力部510Bとして形成された電極に、ボンディングワイヤを接続する構成がある。または、入力部510A及び/又は出力部510Bとして形成された電極と、接続孔部H1,H2に設けられた導電材料とを接続する構成がある。接続孔部H1,H2に設けられた導電材料は、接続孔部H1,H2の一部または全部に埋め込まれていても良く、導電材料が接続孔部H1,H2の側壁に形成されていても良い。

なお、図50では第3基板300に入力部510A、出力部510Bを設ける構造としたが、これに限定されない。例えば、配線層200T、300Tを介して第3基板300の信号を第2基板200へ送ることで、入力部510A及び/又は出力部510Bを第2基板200に設けることもできる。同様に、配線層100T、200Tを介して、第2基板200の信号を第1基板100へ送ることで、入力部510A及び/又は出力部510Bを第1基板100に設けることもできる。

図51は、画素共有ユニット539の構成の一例を表す等価回路図である。画素共有ユニット539は、複数の画素541(図51では、画素541A,541B,541C,541Dの4つの画素541を表す)と、この複数の画素541に接続された1の画素回路210と、画素回路210に接続された垂直信号線543とを含んでいる。画素回路210は、例えば、4つのトランジスタ、具体的には、増幅トランジスタAMP、選択トランジスタSEL、リセットトランジスタRSTおよびFD変換ゲイン切替トランジスタFDGを含んでいる。上述のように、画素共有ユニット539は、1の画素回路210を時分割で動作させることにより、画素共有ユニット539に含まれる4つの画素541(画素541A,541B,541C,541D)それぞれの画素信号を順次垂直信号線543へ出力するようになっている。複数の画素541に1の画素回路210が接続されており、この複数の画素541の画素信号が、1の画素回路210により時分割で出力される態様を、「複数の画素541が1の画素回路210を共有する」という。

画素541A,541B,541C,541Dは、互いに共通の構成要素を有している。以降、画素541A,541B,541C,541Dの構成要素を互いに区別するために、画素541Aの構成要素の符号の末尾には識別番号1、画素541Bの構成要素の符号の末尾には識別番号2、画素541Cの構成要素の符号の末尾には識別番号3、画素541Dの構成要素の符号の末尾には識別番号4を付与する。画素541A,541B,541C,541Dの構成要素を互いに区別する必要のない場合には、画素541A,541B,541C,541Dの構成要素の符号の末尾の識別番号を省略する。

画素541A,541B,541C,541Dは、例えば、フォトダイオードPDと、フォトダイオードPDと電気的に接続された転送トランジスタTRと、転送トランジスタTRに電気的に接続されたフローティングディフュージョンFDとを有している。フォトダイオードPD(PD1,PD2,PD3,PD4)では、カソードが転送トランジスタTRのソースに電気的に接続されており、アノードが基準電位線(例えばグラウンド)に電気的に接続されている。フォトダイオードPDは、入射した光を光電変換し、その受光量に応じた電荷を発生する。転送トランジスタTR(転送トランジスタTR1,TR2,TR3,TR4)は、例えば、n型のCMOS(Complementary Metal-Oxide-Semiconductor)トランジスタである。転送トランジスタTRでは、ドレインがフローティングディフュージョンFDに電気的に接続され、ゲートが駆動信号線に電気的に接続されている。この駆動信号線は、1の画素共有ユニット539に接続された複数の行駆動信号線542(図48参照)のうちの一部である。転送トランジスタTRは、フォトダイオードPDで発生した電荷をフローティングディフュージョンFDへと転送する。フローティングディフュージョンFD(フローティングディフュージョンFD1,FD2,FD3,FD4)は、p型半導体層中に形成されたn型拡散層領域である。フローティングディフュージョンFDは、フォトダイオードPDから転送された電荷を一時的に保持する電荷保持手段であり、かつ、その電荷量に応じた電圧を発生させる、電荷―電圧変換手段である。

1の画素共有ユニット539に含まれる4つのフローティングディフュージョンFD(フローティングディフュージョンFD1,FD2,FD3,FD4)は、互いに電気的に接続されるとともに、増幅トランジスタAMPのゲートおよびFD変換ゲイン切替トランジスタFDGのソースに電気的に接続されている。FD変換ゲイン切替トランジスタFDGのドレインはリセットトランジスタRSTのソースに接続され、FD変換ゲイン切替トランジスタFDGのゲートは駆動信号線に接続されている。この駆動信号線は、1の画素共有ユニット539に接続された複数の行駆動信号線542のうちの一部である。リセットトランジスタRSTのドレインは電源線VDDに接続され、リセットトランジスタRSTのゲートは駆動信号線に接続されている。この駆動信号線は、1の画素共有ユニット539に接続された複数の行駆動信号線542のうちの一部である。増幅トランジスタAMPのゲートはフローティングディフュージョンFDに接続され、増幅トランジスタAMPのドレインは電源線VDDに接続され、増幅トランジスタAMPのソースは選択トランジスタSELのドレインに接続されている。選択トランジスタSELのソースは垂直信号線543に接続され、選択トランジスタSELのゲートは駆動信号線に接続されている。この駆動信号線は、1の画素共有ユニット539に接続された複数の行駆動信号線542のうちの一部である。

転送トランジスタTRは、転送トランジスタTRがオン状態となると、フォトダイオードPDの電荷をフローティングディフュージョンFDに転送する。転送トランジスタTRのゲート(転送ゲートTG)は、例えば、いわゆる縦型電極を含んでおり、後述の図53に示すように、半導体層(後述の図53の半導体層100S)の表面からPDに達する深さまで延在して設けられている。リセットトランジスタRSTは、フローティングディフュージョンFDの電位を所定の電位にリセットする。リセットトランジスタRSTがオン状態となると、フローティングディフュージョンFDの電位を電源線VDDの電位にリセットする。選択トランジスタSELは、画素回路210からの画素信号の出力タイミングを制御する。増幅トランジスタAMPは、画素信号として、フローティングディフュージョンFDに保持された電荷のレベルに応じた電圧の信号を生成する。増幅トランジスタAMPは、選択トランジスタSELを介して垂直信号線543に接続されている。この増幅トランジスタAMPは、列信号処理部550において、垂直信号線543に接続された負荷回路部(図48参照)とともにソースフォロアを構成している。増幅トランジスタAMPは、選択トランジスタSELがオン状態となると、フローティングディフュージョンFDの電圧を、垂直信号線543を介して列信号処理部550に出力する。リセットトランジスタRST、増幅トランジスタAMPおよび選択トランジスタSELは、例えば、N型のCMOSトランジスタである。

FD変換ゲイン切替トランジスタFDGは、フローティングディフュージョンFDでの電荷―電圧変換のゲインを変更する際に用いられる。一般に、暗い場所での撮影時には画素信号が小さい。Q=CVに基づき、電荷電圧変換を行う際に、フローティングディフュージョンFDの容量(FD容量C)が大きければ、増幅トランジスタAMPで電圧に変換した際のVが小さくなってしまう。一方、明るい場所では、画素信号が大きくなるので、FD容量Cが大きくなければ、フローティングディフュージョンFDで、フォトダイオードPDの電荷を受けきれない。さらに、増幅トランジスタAMPで電圧に変換した際のVが大きくなりすぎないように(言い換えると、小さくなるように)、FD容量Cが大きくなっている必要がある。これらを踏まえると、FD変換ゲイン切替トランジスタFDGをオンにしたときには、FD変換ゲイン切替トランジスタFDG分のゲート容量が増えるので、全体のFD容量Cが大きくなる。一方、FD変換ゲイン切替トランジスタFDGをオフにしたときには、全体のFD容量Cが小さくなる。このように、FD変換ゲイン切替トランジスタFDGをオンオフ切り替えることで、FD容量Cを可変にし、変換効率を切り替えることができる。FD変換ゲイン切替トランジスタFDGは、例えば、N型のCMOSトランジスタである。

なお、FD変換ゲイン切替トランジスタFDGを設けない構成も可能である。このとき、例えば、画素回路210は、例えば増幅トランジスタAMP、選択トランジスタSELおよびリセットトランジスタRSTの3つのトランジスタで構成される。画素回路210は、例えば、増幅トランジスタAMP、選択トランジスタSEL、リセットトランジスタRSTおよびFD変換ゲイン切替トランジスタFDGなどの画素トランジスタの少なくとも1つを有する。

選択トランジスタSELは、電源線VDDと増幅トランジスタAMPとの間に設けられていてもよい。この場合、リセットトランジスタRSTのドレインが電源線VDDおよび選択トランジスタSELのドレインに電気的に接続されている。選択トランジスタSELのソースが増幅トランジスタAMPのドレインに電気的に接続されており、選択トランジスタSELのゲートが行駆動信号線542(図48参照)に電気的に接続されている。増幅トランジスタAMPのソース(画素回路210の出力端)が垂直信号線543に電気的に接続されており、増幅トランジスタAMPのゲートがリセットトランジスタRSTのソースに電気的に接続されている。なお、図示は省略するが、1の画素回路210を共有する画素541の数は、4以外であってもよい。例えば、2つまたは8つの画素541が1の画素回路210を共有してもよい。

図52は、複数の画素共有ユニット539と、垂直信号線543との接続態様の一例を表したものである。例えば、列方向に並ぶ4つの画素共有ユニット539が4つのグループに分けられており、この4つのグループ各々に垂直信号線543が接続されている。図52には、説明を簡単にするため、4つのグループが各々、1つの画素共有ユニット539を有する例を示したが、4つのグループが各々、複数の画素共有ユニット539を含んでいてもよい。このように、撮像装置1では、列方向に並ぶ複数の画素共有ユニット539が、1つまたは複数の画素共有ユニット539を含むグループに分けられていてもよい。例えば、このグループそれぞれに、垂直信号線543および列信号処理部550が接続されており、それぞれのグループから画素信号を同時に読み出すことができるようになっている。あるいは、撮像装置1では、列方向に並ぶ複数の画素共有ユニット539に1つの垂直信号線543が接続されていてもよい。このとき、1つの垂直信号線543に接続された複数の画素共有ユニット539から、時分割で順次画素信号が読み出されるようになっている。

[撮像装置1の具体的構成]

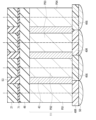

図53は、撮像装置1の第1基板100、第2基板200および第3基板300の主面に対して垂直方向の断面構成の一例を表したものである。図53は、構成要素の位置関係を分かりやすくするため、模式的に表したものであり、実際の断面と異なっていてもよい。撮像装置1では、第1基板100、第2基板200および第3基板300がこの順に積層されている。撮像装置1は、さらに、第1基板100の裏面側(光入射面側)に受光レンズ401を有している。受光レンズ401と第1基板100との間に、カラーフィルタ層(図示せず)が設けられていてもよい。受光レンズ401は、例えば、画素541A,541B,541C,541D各々に設けられている。撮像装置1は、例えば、裏面照射型の撮像装置である。撮像装置1は、中央部に配置された画素アレイ部540と、画素アレイ部540の外側に配置された周辺部540Bとを有している。

第1基板100は、受光レンズ401側から順に、絶縁膜111、固定電荷膜112、半導体層100Sおよび配線層100Tを有している。半導体層100Sは、例えばシリコン基板により構成されている。半導体層100Sは、例えば、表面(配線層100T側の面)の一部およびその近傍に、pウェル層115を有しており、それ以外の領域(pウェル層115よりも深い領域)に、n型半導体領域114を有している。例えば、このn型半導体領域114およびpウェル層115によりpn接合型のフォトダイオードPDが構成されている。pウェル層115は、p型半導体領域である。

図54Aは、第1基板100の平面構成の一例を表したものである。図54Aは、主に、第1基板100の画素分離部117、フォトダイオードPD、フローティングディフュージョンFD、VSSコンタクト領域118および転送トランジスタTRの平面構成を表している。図53とともに、図54Aを用いて第1基板100の構成について説明する。

半導体層100Sの表面近傍には、フローティングディフュージョンFDおよびVSSコンタクト領域118が設けられている。フローティングディフュージョンFDは、pウェル層115内に設けられたn型半導体領域により構成されている。画素541A,541B,541C,541D各々のフローティングディフュージョンFD(フローティングディフュージョンFD1,FD2,FD3,FD4)は、例えば、画素共有ユニット539の中央部に互いに近接して設けられている(図54A)。詳細は後述するが、この画素共有ユニット539に含まれる4つのフローティングディフュージョン(フローティングディフュージョンFD1,FD2,FD3,FD4)は、第1基板100内(より具体的には配線層100Tの内)で、電気的接続手段(後述のパッド部120)を介して互いに電気的に接続されている。更に、フローティングディフュージョンFDは、第1基板100から第2基板200へ(より具体的には、配線層100Tから配線層200Tへ)と電気的手段(後述の貫通電極120E)を介して接続されている。第2基板200(より具体的には配線層200Tの内部)では、この電気的手段により、フローティングディフュージョンFDが、増幅トランジスタAMPのゲートおよびFD変換ゲイン切替トランジスタFDGのソースに電気的に接続されている。

VSSコンタクト領域118は、基準電位線VSSに電気的に接続される領域であり、フローティングディフュージョンFDと離間して配置されている。例えば、画素541A,541B,541C,541Dでは、各画素のV方向の一端にフローティングディフュージョンFDが配置され、他端にVSSコンタクト領域118が配置されている(図54A)。VSSコンタクト領域118は、例えば、p型半導体領域により構成されている。VSSコンタクト領域118は、例えば接地電位や固定電位に接続されている。これにより、半導体層100Sに基準電位が供給される。

第1基板100には、フォトダイオードPD、フローティングディフュージョンFDおよびVSSコンタクト領域118とともに、転送トランジスタTRが設けられている。このフォトダイオードPD、フローティングディフュージョンFD、VSSコンタクト領域118および転送トランジスタTRは、画素541A,541B,541C,541D各々に設けられている。転送トランジスタTRは、半導体層100Sの表面側(光入射面側とは反対側、第2基板200側)に設けられている。転送トランジスタTRは、転送ゲートTGを有している。転送ゲートTGは、例えば、半導体層100Sの表面に対向する水平部分TGbと、半導体層100S内に設けられた垂直部分TGaとを含んでいる。垂直部分TGaは、半導体層100Sの厚み方向に延在している。垂直部分TGaの一端は水平部分TGbに接し、他端はn型半導体領域114内に設けられている。転送トランジスタTRを、このような縦型トランジスタにより構成することにより、画素信号の転送不良が生じにくくなり、画素信号の読み出し効率を向上させることができる。

転送ゲートTGの水平部分TGbは、垂直部分TGaに対向する位置から例えば、H方向において画素共有ユニット539の中央部に向かって延在している(図54A)。これにより、転送ゲートTGに達する貫通電極(後述の貫通電極TGV)のH方向の位置を、フローティングディフュージョンFD、VSSコンタクト領域118に接続される貫通電極(後述の貫通電極120E,121E)のH方向の位置に近づけることができる。例えば、第1基板100に設けられた複数の画素共有ユニット539は、互いに同じ構成を有している(図54A)。

半導体層100Sには、画素541A,541B,541C,541Dを互いに分離する画素分離部117が設けられている。画素分離部117は、半導体層100Sの法線方向(半導体層100Sの表面に対して垂直な方向)に延在して形成されている。画素分離部117は、画素541A,541B,541C,541Dを互いに仕切るように設けられており、例えば格子状の平面形状を有している(図54A,図54B)。画素分離部117は、例えば、画素541A,541B,541C,541Dを互いに電気的および光学的に分離する。画素分離部117は、例えば、遮光膜117Aおよび絶縁膜117Bを含んでいる。遮光膜117Aには、例えば、タングステン(W)等が用いられる。絶縁膜117Bは、遮光膜117Aとpウェル層115またはn型半導体領域114との間に設けられている。絶縁膜117Bは、例えば、酸化シリコン(SiO)によって構成されている。画素分離部117は、例えば、FTI(Full Trench Isolation)構造を有しており、半導体層100Sを貫通している。図示しないが、画素分離部117は半導体層100Sを貫通するFTI構造に限定されない。例えば、半導体層100Sを貫通しないDTI(Deep Trench Isolation)構造であっても良い。画素分離部117は、半導体層100Sの法線方向に延在して、半導体層100Sの一部の領域に形成される。

半導体層100Sには、例えば、第1ピニング領域113および第2ピニング領域116が設けられている。第1ピニング領域113は、半導体層100Sの裏面近傍に設けられており、n型半導体領域114と固定電荷膜112との間に配置されている。第2ピニング領域116は、画素分離部117の側面、具体的には、画素分離部117とpウェル層115またはn型半導体領域114との間に設けられている。第1ピニング領域113および第2ピニング領域116は、例えば、p型半導体領域により構成されている。

半導体層100Sと絶縁膜111との間には、負の固定電荷を有する固定電荷膜112が設けられている。固定電荷膜112が誘起する電界により、半導体層100Sの受光面(裏面)側の界面に、ホール蓄積層の第1ピニング領域113が形成される。これにより、半導体層100Sの受光面側の界面準位に起因した暗電流の発生が抑えられる。固定電荷膜112は、例えば、負の固定電荷を有する絶縁膜によって形成されている。この負の固定電荷を有する絶縁膜の材料としては、例えば、酸化ハフニウム、酸化ジルコン、酸化アルミニウム、酸化チタンまたは酸化タンタルが挙げられる。

固定電荷膜112と絶縁膜111との間には、遮光膜117Aが設けられている。この遮光膜117Aは、画素分離部117を構成する遮光膜117Aと連続して設けられていてもよい。この固定電荷膜112と絶縁膜111との間の遮光膜117Aは、例えば、半導体層100S内の画素分離部117に対向する位置に選択的に設けられている。絶縁膜111は、この遮光膜117Aを覆うように設けられている。絶縁膜111は、例えば、酸化シリコンにより構成されている。

半導体層100Sと第2基板200との間に設けられた配線層100Tは、半導体層100S側から、層間絶縁膜119、パッド部120,121、パッシベーション膜122、層間絶縁膜123および接合膜124をこの順に有している。転送ゲートTGの水平部分TGbは、例えば、この配線層100Tに設けられている。層間絶縁膜119は、半導体層100Sの表面全面にわたって設けられており、半導体層100Sに接している。層間絶縁膜119は、例えば酸化シリコン膜により構成されている。なお、配線層100Tの構成は上述の限りでなく、配線と絶縁膜とを有する構成であれば良い。

図54Bは、図54Aに示した平面構成とともに、パッド部120,121の構成を表している。パッド部120,121は、層間絶縁膜119上の選択的な領域に設けられている。パッド部120は、画素541A,541B,541C,541D各々のフローティングディフュージョンFD(フローティングディフュージョンFD1,FD2,FD3,FD4)を互いに接続するためのものである。パッド部120は、例えば、画素共有ユニット539毎に、平面視で画素共有ユニット539の中央部に配置されている(図54B)。このパッド部120は、画素分離部117を跨ぐように設けられており、フローティングディフュージョンFD1,FD2,FD3,FD4各々の少なくとも一部に重畳して配置されている(図53,図54B)。具体的には、パッド部120は、画素回路210を共有する複数のフローティングディフュージョンFD(フローティングディフュージョンFD1,FD2,FD3,FD4)各々の少なくとも一部と、その画素回路210を共有する複数のフォトダイオードPD(フォトダイオードPD1,PD2,PD3,PD4)の間に形成された画素分離部117の少なくとも一部とに対して、半導体層100Sの表面に対して垂直な方向に重なる領域に形成される。層間絶縁膜119には、パッド部120とフローティングディフュージョンFD1,FD2,FD3,FD4とを電気的に接続するための接続ビア120Cが設けられている。接続ビア120Cは、画素541A,541B,541C,541D各々に設けられている。例えば、接続ビア120Cにパッド部120の一部が埋め込まれることにより、パッド部120とフローティングディフュージョンFD1,FD2,FD3,FD4とが電気的に接続されている。

パッド部121は、複数のVSSコンタクト領域118を互いに接続するためのものである。例えば、V方向に隣り合う一方の画素共有ユニット539の画素541C,541Dに設けられたVSSコンタクト領域118と、他方の画素共有ユニット539の画素541A,541Bに設けられたVSSコンタクト領域118とがパッド部121により電気的に接続されている。パッド部121は、例えば、画素分離部117を跨ぐように設けられており、これら4つのVSSコンタクト領域118各々の少なくとも一部に重畳して配置されている。具体的には、パッド部121は、複数のVSSコンタクト領域118各々の少なくとも一部と、その複数のVSSコンタクト領域118の間に形成された画素分離部117の少なくとも一部とに対して、半導体層100Sの表面に対して垂直な方向に重なる領域に形成される。層間絶縁膜119には、パッド部121とVSSコンタクト領域118とを電気的に接続するための接続ビア121Cが設けられている。接続ビア121Cは、画素541A,541B,541C,541D各々に設けられている。例えば、接続ビア121Cにパッド部121の一部が埋め込まれることにより、パッド部121とVSSコンタクト領域118とが電気的に接続されている。例えば、V方向に並ぶ複数の画素共有ユニット539各々のパッド部120およびパッド部121は、H方向において略同じ位置に配置されている(図54B)。

パッド部120を設けることで、チップ全体において、各フローティングディフュージョンFDから画素回路210(例えば増幅トランジスタAMPのゲート電極)へ接続するための配線を減らすことができる。同様に、パッド部121を設けることで、チップ全体において、各VSSコンタクト領域118への電位を供給する配線を減らすことができる。これにより、チップ全体の面積の縮小、微細化された画素における配線間の電気的干渉の抑制、及び/又は部品点数の削減によるコスト削減などが可能になる。

パッド部120、121は、第1基板100、第2基板200の所望の位置に設けることができる。具体的には、パッド部120、121を配線層100T、半導体層200Sの絶縁領域212のいずれかに設けることができる。配線層100Tに設ける場合には、パッド部120、121を半導体層100Sに直接接触させても良い。具体的には、パッド部120、121が、フローティングディフュージョンFD及び/又はVSSコンタクト領域118の各々の少なくとも一部と直接接続される構成でも良い。また、パッド部120、121に接続するフローティングディフュージョンFD及び/又はVSSコンタクト領域118の各々から接続ビア120C,121Cを設け、配線層100T、半導体層200Sの絶縁領域212の所望の位置にパッド部120、121を設ける構成でも良い。

特に、パッド部120、121を配線層100Tに設ける場合には、半導体層200Sの絶縁領域212におけるフローティングディフュージョンFD及び/又はVSSコンタクト領域118に接続される配線を減らすことができる。これにより、画素回路210を形成する第2基板200のうち、フローティングディフュージョンFDから画素回路210に接続するための貫通配線を形成するための絶縁領域212の面積を削減することができる。よって、画素回路210を形成する第2基板200の面積を大きく確保することができる。画素回路210の面積を確保することで、画素トランジスタを大きく形成することができ、ノイズ低減などによる画質向上に寄与することができる。

特に、画素分離部117にFTI構造を用いた場合、フローティングディフュージョンFD及び/又はVSSコンタクト領域118は、各画素541に設けることが好ましいため、パッド部120、121の構成を用いることで、第1基板100と第2基板200とを接続する配線を大幅に削減することができる。

また、図54Bのように、例えば複数のフローティングディフュージョンFDが接続されるパッド部120と、複数のVSSコンタクト領域118が接続されるパッド部121とは、V方向において直線状に交互に配置される。また、パッド部120、121は、複数のフォトダイオードPDや、複数の転送ゲートTGや、複数のフローティングディフュージョンFDに囲まれる位置に形成される。これにより、複数の素子を形成する第1基板100において、フローティングディフュージョンFDとVSSコンタクト領域118以外の素子を自由に配置することができ、チップ全体のレイアウトの効率化を図ることができる。また、各画素共有ユニット539に形成される素子のレイアウトにおける対称性が確保され、各画素541の特性のばらつきを抑えることができる。

パッド部120,121は、例えば、ポリシリコン(Poly Si)、より具体的には、不純物が添加されたドープドポリシリコンにより構成されている。パッド部120,121はポリシリコン、タングステン(W)、チタン(Ti)および窒化チタン(TiN)等の耐熱性の高い導電性材料により構成されていることが好ましい。これにより、第1基板100に第2基板200の半導体層200Sを貼り合わせた後に、画素回路210を形成することが可能となる。以下、この理由について説明する。なお、以下の説明において、第1基板100と第2基板200の半導体層200Sを貼り合わせた後に、画素回路210を形成する方法を、第1の製造方法と呼ぶ。

ここで、第2基板200に画素回路210を形成した後に、これを第1基板100に貼り合わせることも考え得る(以下第2の製造方法という)。この第2の製造方法では、第1基板100の表面(配線層100Tの表面)および第2基板200の表面(配線層200Tの表面)それぞれに、電気的接続用の電極を予め形成しておく。第1基板100と第2基板200を貼り合わせると、これと同時に、第1基板100の表面と第2基板200の表面のそれぞれに形成された電気的接続用の電極同士が接触する。これにより、第1基板100に含まれる配線と第2基板200に含まれる配線との間で電気的接続が形成される。よって、第2の製造方法を用いた撮像装置1の構成とすることで、例えば第1基板100と第2基板200の各々の構成に応じて適切なプロセスを用いて製造することができ、高品質、高性能な撮像装置を製造することができる。

このような第2の製造方法では、第1基板100と第2基板200とを貼り合わせる際に、貼り合せ用の製造装置に起因して、位置合わせの誤差が生じることがある。また、第1基板100および第2基板200は、例えば、直径数十cm程度の大きさを有するが、第1基板100と第2基板200とを貼り合わせる際に、この第1基板100、第2基板200各部の微視的領域で、基板の伸び縮みが発生するおそれがある。この基板の伸び縮みは、基板同士が接触するタイミングが多少ずれることに起因する。このような第1基板100および第2基板200の伸び縮みに起因して、第1基板100の表面および第2基板200の表面それぞれに形成された電気的接続用の電極の位置に、誤差が生じることがある。第2の製造方法では、このような誤差が生じても、第1基板100および第2基板200それぞれの電極同士が接触するように対処しておくことが好ましい。具体的には、第1基板100および第2基板200の電極の少なくとも一方、好ましくは両方を、上記誤差を考慮して大きくしておく。このため、第2の製造方法を用いると、例えば、第1基板100または第2基板200の表面に形成された電極の大きさ(基板平面方向の大きさ)が、第1基板100または第2基板200の内部から表面に厚み方向へ延在する内部電極の大きさよりも大きくなる。

一方、パッド部120,121を耐熱性の導電材料により構成することで、上記第1の製造方法を用いることが可能となる。第1の製造方法では、フォトダイオードPDおよび転送トランジスタTRなどを含む第1基板100を形成した後、この第1基板100と第2基板200(半導体層2000S)とを貼り合わせる。このとき、第2基板200は、画素回路210を構成する能動素子および配線層などのパターンは未形成の状態である。第2基板200はパターンを形成する前の状態であるため、仮に、第1基板100と第2基板200を貼り合わせる際、その貼り合せ位置に誤差が生じたとしても、この貼り合せ誤差によって、第1基板100のパターンと第2基板200のパターンとの間の位置合わせに誤差が生じることはない。なぜならば、第2基板200のパターンは、第1基板100と第2基板200を貼り合わせた後に、形成するからである。なお、第2基板にパターンを形成する際には、例えば、パターン形成のための露光装置において、第1基板に形成されたパターンを位置合わせの対象としながらパターン形成する。上記理由により、第1基板100と第2基板200との貼り合せ位置の誤差は、第1の製造方法においては、撮像装置1を製造する上で問題とならない。同様の理由で、第2の製造方法で生じる基板の伸び縮みに起因した誤差も、第1の製造方法においては、撮像装置1を製造する上で問題とならない。

第1の製造方法では、このようにして第1基板100と第2基板200(半導体層200S)とを貼り合せた後、第2基板200上に能動素子を形成する。この後、貫通電極120E,121Eおよび貫通電極TGV(図53)を形成する。この貫通電極120E,121E,TGVの形成では、例えば、第2基板200の上方から、露光装置による縮小投影露光を用いて貫通電極のパターンを形成する。縮小露光投影を用いるため、仮に、第2基板200と露光装置との位置合わせに誤差が生じても、その誤差の大きさは、第2基板200においては、上記第2の製造方法の誤差の数分の一(縮小露光投影倍率の逆数)にしかならない。よって、第1の製造方法を用いた撮像装置1の構成とすることで、第1基板100と第2基板200の各々に形成される素子同士の位置合わせが容易になり、高品質、高性能な撮像装置を製造することができる。

このような第1の製造方法を用いて製造された撮像装置1は、第2の製造方法で製造された撮像装置と異なる特徴を有する。具体的には、第1の製造方法により製造された撮像装置1では、例えば、貫通電極120E,121E,TGVが、第2基板200から第1基板100に至るまで、略一定の太さ(基板平面方向の大きさ)となっている。あるいは、貫通電極120E,121E,TGVがテーパー形状を有するときには、一定の傾きのテーパー形状を有している。このような貫通電極120E,121E,TGVを有する撮像装置1は、画素541を微細化しやすい。

ここで、第1の製造方法により撮像装置1を製造すると、第1基板100と第2基板200(半導体層200S)とを貼り合わせた後に、第2基板200に能動素子を形成するので、第1基板100にも、能動素子の形成の際に必要な加熱処理の影響が及ぶことになる。このため、上記のように、第1基板100に設けられたパッド部120,121には、耐熱性の高い導電材料を用いることが好ましい。例えば、パッド部120,121には、第2基板200の配線層200Tに含まれる配線材の少なくとも一部よりも、融点の高い(すなわち耐熱性の高い)材料を用いていることが好ましい。例えば、パッド部120,121にドープトポリシリコン、タングステン、チタンあるいは窒化チタン等の耐熱性の高い導電材を用いる。これにより、上記第1の製造方法を用いて撮像装置1を製造することが可能となる。

パッシベーション膜122は、例えば、パッド部120,121を覆うように、半導体層100Sの表面全面にわたって設けられている(図53)。パッシベーション膜122は、例えば、窒化シリコン(SiN)膜により構成されている。層間絶縁膜123は、パッシベーション膜122を間にしてパッド部120,121を覆っている。この層間絶縁膜123は、例えば、半導体層100Sの表面全面にわたって設けられている。層間絶縁膜123は、例えば酸化シリコン(SiO)膜により構成されている。接合膜124は、第1基板100(具体的には配線層100T)と第2基板200との接合面に設けられている。即ち、接合膜124は、第2基板200に接している。この接合膜124は、第1基板100の主面全面にわたって設けられている。接合膜124は、例えば、窒化シリコン膜により構成されている。

受光レンズ401は、例えば、固定電荷膜112および絶縁膜111を間にして半導体層100Sに対向している(図53)。受光レンズ401は、例えば画素541A,541B,541C,541D各々のフォトダイオードPDに対向する位置に設けられている。

第2基板200は、第1基板100側から、半導体層200Sおよび配線層200Tをこの順に有している。半導体層200Sは、シリコン基板で構成されている。半導体層200Sでは、厚み方向にわたって、ウェル領域211が設けられている。ウェル領域211は、例えば、p型半導体領域である。第2基板200には、画素共有ユニット539毎に配置された画素回路210が設けられている。この画素回路210は、例えば、半導体層200Sの表面側(配線層200T側)に設けられている。撮像装置1では、第1基板100の表面側(配線層100T側)に第2基板200の裏面側(半導体層200S側)が向かうようにして、第2基板200が第1基板100に貼り合わされている。つまり、第2基板200は、第1基板100に、フェイストゥーバックで貼り合わされている。

図55~図59は、第2基板200の平面構成の一例を模式的に表している。図55には、半導体層200Sの表面近傍に設けられた画素回路210の構成を表す。図56は、配線層200T(具体的には後述の第1配線層W1)と、配線層200Tに接続された半導体層200Sおよび第1基板100の各部の構成を模式的に表している。図57~図59は、配線層200Tの平面構成の一例を表している。以下、図53とともに、図55~図59を用いて第2基板200の構成について説明する。図55および図56ではフォトダイオードPDの外形(画素分離部117とフォトダイオードPDとの境界)を破線で表し、画素回路210を構成する各トランジスタのゲート電極に重なる部分の半導体層200Sと素子分離領域213または絶縁領域212との境界を点線で表す。増幅トランジスタAMPのゲート電極に重なる部分では、チャネル幅方向の一方に、半導体層200Sと素子分離領域213との境界、および素子分離領域213と絶縁領域212との境界が設けられている。

第2基板200には、半導体層200Sを分断する絶縁領域212と、半導体層200Sの厚み方向の一部に設けられた素子分離領域213とが設けられている(図53)。例えば、H方向に隣り合う2つの画素回路210の間に設けられた絶縁領域212に、この2つの画素回路210に接続された2つの画素共有ユニット539の貫通電極120E,121Eおよび貫通電極TGV(貫通電極TGV1,TGV2,TGV3,TGV4)が配置されている(図56)。

絶縁領域212は、半導体層200Sの厚みと略同じ厚みを有している(図53)。半導体層200Sは、この絶縁領域212により分断されている。この絶縁領域212に、貫通電極120E,121Eおよび貫通電極TGVが配置されている。絶縁領域212は、例えば酸化シリコンにより構成されている。

貫通電極120E,121Eは、絶縁領域212を厚み方向に貫通して設けられている。貫通電極120E,121Eの上端は、配線層200Tの配線(後述の第1配線層W1,第2配線層W2,第3配線層W3,第4配線層W4)に接続されている。この貫通電極120E,121Eは、絶縁領域212、接合膜124、層間絶縁膜123およびパッシベーション膜122を貫通して設けられ、その下端はパッド部120,121に接続されている(図53)。貫通電極120Eは、パッド部120と画素回路210とを電気的に接続するためのものである。即ち、貫通電極120Eにより、第1基板100のフローティングディフュージョンFDが第2基板200の画素回路210に電気的に接続される。貫通電極121Eは、パッド部121と配線層200Tの基準電位線VSSとを電気的に接続するためのものである。即ち、貫通電極121Eにより、第1基板100のVSSコンタクト領域118が第2基板200の基準電位線VSSに電気的に接続される。

貫通電極TGVは、絶縁領域212を厚み方向に貫通して設けられている。貫通電極TGVの上端は、配線層200Tの配線に接続されている。この貫通電極TGVは、絶縁領域212、接合膜124、層間絶縁膜123、パッシベーション膜122および層間絶縁膜119を貫通して設けられ、その下端は転送ゲートTGに接続されている(図53)。このような貫通電極TGVは、画素541A,541B,541C,541D各々の転送ゲートTG(転送ゲートTG1,TG2,TG3,TG4)と、配線層200Tの配線(行駆動信号線542の一部、具体的には、後述の図58の配線TRG1,TRG2,TRG3,TRG4)とを電気的に接続するためのものである。即ち、貫通電極TGVにより、第1基板100の転送ゲートTGが第2基板200の配線TRGに電気的に接続され、転送トランジスタTR(転送トランジスタTR1,TR2,TR3,TR4)各々に駆動信号が送られるようになっている。

絶縁領域212は、第1基板100と第2基板200とを電気的に接続するための前記貫通電極120E,121Eおよび貫通電極TGVを、半導体層200Sと絶縁して設けるための領域である。例えば、H方向に隣り合う2つの画素回路210(画素共有ユニット539)の間に設けられた絶縁領域212に、この2つの画素回路210に接続された貫通電極120E,121Eおよび貫通電極TGV(貫通電極TGV1,TGV2,TGV3,TGV4)が配置されている。絶縁領域212は、例えば、V方向に延在して設けられている(図55,図56)。ここでは、転送ゲートTGの水平部分TGbの配置を工夫することにより、垂直部分TGaの位置に比べて、貫通電極TGVのH方向の位置が貫通電極120E,121EのH方向の位置に近づくように配置されている(図54A,図56)。例えば、貫通電極TGVは、H方向において、貫通電極120E,120Eと略同じ位置に配置されている。これにより、V方向に延在する絶縁領域212に、貫通電極120E,121Eおよび貫通電極TGVをまとめて設けることができる。別の配置例として、垂直部分TGaに重畳する領域のみに水平部分TGbを設けることも考え得る。この場合には、垂直部分TGaの略直上に貫通電極TGVが形成され、例えば、各画素541のH方向およびV方向の略中央部に貫通電極TGVが配置される。このとき、貫通電極TGVのH方向の位置と貫通電極120E,121EのH方向の位置とが大きくずれる。貫通電極TGVおよび貫通電極120E,121Eの周囲には、近接する半導体層200Sから電気的に絶縁するため、例えば、絶縁領域212を設ける。貫通電極TGVのH方向の位置と貫通電極120E,121EのH方向の位置とが大きく離れる場合には、貫通電極120E,121E,TGV各々の周囲に絶縁領域212を独立して設けることが必要となる。これにより、半導体層200Sが細かく分断されることになる。これに比べ、V方向に延在する絶縁領域212に、貫通電極120E,121Eおよび貫通電極TGVをまとめて配置するレイアウトは、半導体層200SのH方向の大きさを大きくすることができる。よって、半導体層200Sにおける半導体素子形成領域の面積を大きく確保することができる。これにより、例えば、増幅トランジスタAMPのサイズを大きくし、ノイズを抑えることが可能となる。

画素共有ユニット539は、図51を参照して説明したように、複数の画素541のそれぞれに設けられたフローティングディフュージョンFDの間を電気的に接続し、これら複数の画素541が1つの画素回路210を共有する構造を有している。そして、前記フローティングディフュージョンFD間の電気的接続は、第1基板100に設けられたパッド部120によってなされている(図53、図54B)。第1基板100に設けられた電気的接続部(パッド部120)と第2基板200に設けられた画素回路210は、1つの貫通電極120Eを介して電気的に接続されている。別の構造例として、フローティングディフュージョンFD間の電気的接続部を第2基板200に設けることも考え得る。この場合、画素共有ユニット539には、フローティングディフュージョンFD1,FD2,FD3,FD4各々に接続される4つの貫通電極が設けられる。したがって、第2基板200において、半導体層200Sを貫通する貫通電極の数が増え、これら貫通電極の周囲を絶縁する絶縁領域212が大きくなる。これに比べ、第1基板100にパッド部120を設ける構造(図53,図54B)は、貫通電極の数を減らし、絶縁領域212を小さくすることができる。よって、半導体層200Sにおける半導体素子形成領域の面積を大きく確保することができる。これにより、例えば、増幅トランジスタAMPのサイズを大きくし、ノイズを抑えることが可能となる。

素子分離領域213は、半導体層200Sの表面側に設けられている。素子分離領域213は、STI(Shallow Trench Isolation)構造を有している。この素子分離領域213では、半導体層200Sが厚み方向(第2基板200の主面に対して垂直方向)に掘り込まれており、この掘り込みに絶縁膜が埋め込まれている。この絶縁膜は、例えば、酸化シリコンにより構成されている。素子分離領域213は、画素回路210を構成する複数のトランジスタ間を、画素回路210のレイアウトに応じて素子分離するものである。素子分離領域213の下方(半導体層200Sの深部)には、半導体層200S(具体的には、ウェル領域211)が延在している。

ここで、図54A,図54Bおよび図55を参照して、第1基板100での画素共有ユニット539の外形形状(基板平面方向の外形形状)と、第2基板200での画素共有ユニット539の外形形状との違いを説明する。

撮像装置1では、第1基板100および第2基板200の両方にわたり、画素共有ユニット539が設けられている。例えば、第1基板100に設けられた画素共有ユニット539の外形形状と、第2基板200に設けられた画素共有ユニット539の外形形状とは互いに異なっている。

図54A,図54Bでは、画素541A,541B,541C,541Dの外形線を一点鎖線で表し、画素共有ユニット539の外形形状を太線で表している。例えば、第1基板100の画素共有ユニット539は、H方向に隣接して配置された2つの画素541(画素541A,541B)と、これにV方向に隣接して配置された2つの画素541(画素541C,541D)により構成されている。即ち、第1基板100の画素共有ユニット539は、隣接する2行×2列の4つの画素541により構成されており、第1基板100の画素共有ユニット539は、略正方形の外形形状を有している。画素アレイ部540では、このような画素共有ユニット539が、H方向へ2画素ピッチ(画素541の2個分に相当するピッチ)、かつ、V方向へ2画素ピッチ(画素541の2個分に相当するピッチ)、で隣接して配列されている。

図55および図56では、画素541A,541B,541C,541Dの外形線を一点鎖線で表し、画素共有ユニット539の外形形状を太線で表している。例えば、第2基板200の画素共有ユニット539の外形形状は、H方向において第1基板100の画素共有ユニット539よりも小さく、V方向において第1基板100の画素共有ユニット539よりも大きくなっている。例えば、第2基板200の画素共有ユニット539は、H方向には画素1個分に相当する大きさ(領域)で形成され、V方向には、画素4個分に相当する大きさで形成されている。即ち、第2基板200の画素共有ユニット539は、隣接する1行×4列に配列された画素に相当する大きさで形成されており、第2基板200の画素共有ユニット539は、略長方形の外形形状を有している。

例えば、各画素回路210では、選択トランジスタSEL、増幅トランジスタAMP、リセットトランジスタRSTおよびFD変換ゲイン切替トランジスタFDGがこの順にV方向に並んで配置されている(図55)。各画素回路210の外形形状を、上記のように、略長方形状に設けることにより、一方向(図55ではV方向)に4つのトランジスタ(選択トランジスタSEL、増幅トランジスタAMP、リセットトランジスタRSTおよびFD変換ゲイン切替トランジスタFDG)を並べて配置することができる。これにより、増幅トランジスタAMPのドレインと、リセットトランジスタRSTのドレインとを一の拡散領域(電源線VDDに接続される拡散領域)で共有することができる。例えば、各画素回路210の形成領域を略正方形状に設けることも可能である(後述の図68参照)。この場合には、一方向に沿って2つのトランジスタが配置され、増幅トランジスタAMPのドレインと、リセットトランジスタRSTのドレインとを一の拡散領域で共有することが困難となる。よって、画素回路210の形成領域を略長方形状に設けることにより、4つのトランジスタを近接して配置しやすくなり、画素回路210の形成領域を小さくすることができる。即ち、画素の微細化を行うことができる。また、画素回路210の形成領域を小さくすることが不要であるときには、増幅トランジスタAMPの形成領域を大きくし、ノイズを抑えることが可能となる。

例えば、半導体層200Sの表面近傍には、選択トランジスタSEL、増幅トランジスタAMP、リセットトランジスタRSTおよびFD変換ゲイン切替トランジスタFDGに加えて、基準電位線VSSに接続されるVSSコンタクト領域218が設けられている。VSSコンタクト領域218は、例えば、p型半導体領域により構成されている。VSSコンタクト領域218は、配線層200Tの配線および貫通電極121Eを介して第1基板100(半導体層100S)のVSSコンタクト領域118に電気的に接続されている。このVSSコンタクト領域218は、例えば、素子分離領域213を間にして、FD変換ゲイン切替トランジスタFDGのソースと隣り合う位置に設けられている(図55)。

次に、図54Bおよび図55を参照して、第1基板100に設けられた画素共有ユニット539と第2基板200に設けられた画素共有ユニット539との位置関係を説明する。例えば、第1基板100のV方向に並ぶ2つの画素共有ユニット539のうち、一方(例えば図54Bの紙面上側)の画素共有ユニット539は、第2基板200のH方向に並ぶ2つの画素共有ユニット539のうちの一方(例えば、図55の紙面左側)の画素共有ユニット539に接続されている。例えば、第1基板100のV方向に並ぶ2つの画素共有ユニット539のうち、他方(例えば図54Bの紙面下側)の画素共有ユニット539は、第2基板200のH方向に並ぶ2つの画素共有ユニット539のうちの他方(例えば、図55の紙面右側)の画素共有ユニット539に接続されている。

例えば、第2基板200のH方向に並ぶ2つの画素共有ユニット539では、一方の画素共有ユニット539の内部レイアウト(トランジスタ等の配置)が、他方の画素共有ユニット539の内部レイアウトをV方向およびH方向に反転させたレイアウトに略等しくなっている。以下、このレイアウトによって得られる効果を説明する。

第1基板100のV方向に並ぶ2つの画素共有ユニット539では、各々のパッド部120が、画素共有ユニット539の外形形状の中央部、即ち、画素共有ユニット539のV方向およびH方向の中央部に配置される(図54B)。一方、第2基板200の画素共有ユニット539は、上記のように、V方向に長い略長方形の外形形状を有しているので、例えば、パッド部120に接続される増幅トランジスタAMPは、画素共有ユニット539のV方向の中央から紙面上方にずれた位置に配置されている。例えば、第2基板200のH方向に並ぶ2つの画素共有ユニット539の内部レイアウトが同じであるとき、一方の画素共有ユニット539の増幅トランジスタAMPと、パッド部120(例えば、図7の紙面上側の画素共有ユニット539のパッド部120)との距離は比較的短くなる。しかし、他方の画素共有ユニット539の増幅トランジスタAMPと、パッド部120(例えば、図7の紙面下側の画素共有ユニット539のパッド部120)との距離が長くなる。このため、この増幅トランジスタAMPとパッド部120との接続に要する配線の面積が大きくなり、画素共有ユニット539の配線レイアウトが複雑になるおそれがある。このことは、撮像装置1の微細化に影響を及ぼす可能性がある。

これに対して、第2基板200のH方向に並ぶ2つの画素共有ユニット539で、互いの内部レイアウトを少なくともV方向に反転させることにより、これら2つの画素共有ユニット539の両方の増幅トランジスタAMPとパッド部120との距離を短くすることができる。したがって、第2基板200のH方向に並ぶ2つの画素共有ユニット539の内部レイアウトを同じにした構成と比べて、撮像装置1の微細化を行いやすくなる。なお、第2基板200の複数の画素共有ユニット539各々の平面レイアウトは、図55に記載の範囲では左右対称であるが、後述する図56に記載の第1配線層W1のレイアウトまで含めると、左右非対称のものとなる。

また、第2基板200のH方向に並ぶ2つの画素共有ユニット539の内部レイアウトは、互いに、H方向にも反転されていることが好ましい。以下、この理由について説明する。図56に示したように、第2基板200のH方向に並ぶ2つの画素共有ユニット539はそれぞれ、第1基板100のパッド部120,121に接続されている。例えば、第2基板200のH方向に並ぶ2つの画素共有ユニット539のH方向の中央部(H方向に並ぶ2つの画素共有ユニット539の間)にパッド部120,121が配置されている。したがって、第2基板200のH方向に並ぶ2つの画素共有ユニット539の内部レイアウトを、互いに、H方向にも反転させることにより、第2基板200の複数の画素共有ユニット539それぞれとパッド部120,121との距離を小さくすることができる。即ち、撮像装置1の微細化を更に行いやすくなる。

また、第2基板200の画素共有ユニット539の外形線の位置は、第1基板100の画素共有ユニット539のいずれかの外形線の位置に揃っていなくてもよい。例えば、第2基板200のH方向に並ぶ2つの画素共有ユニット539のうち、一方(例えば図56の紙面左側)の画素共有ユニット539では、V方向の一方(例えば図56の紙面上側)の外形線が、対応する第1基板100の画素共有ユニット539(例えば図54Bの紙面上側)のV方向の一方の外形線の外側に配置されている。また、第2基板200のH方向に並ぶ2つの画素共有ユニット539のうち、他方(例えば図56の紙面右側)の画素共有ユニット539では、V方向の他方(例えば図56の紙面下側)の外形線が、対応する第1基板100の画素共有ユニット539(例えば図54Bの紙面下側)のV方向の他方の外形線の外側に配置されている。このように、第2基板200の画素共有ユニット539と、第1基板100の画素共有ユニット539とを互いに配置することにより、増幅トランジスタAMPとパッド部120との距離を短くすることが可能となる。したがって、撮像装置1の微細化を行いやすくなる。

また、第2基板200の複数の画素共有ユニット539の間で、互いの外形線の位置は揃っていなくてもよい。例えば、第2基板200のH方向に並ぶ2つの画素共有ユニット539は、V方向の外形線の位置がずれて配置されている。これにより、増幅トランジスタAMPとパッド部120との距離を短くすることが可能となる。したがって、撮像装置1の微細化を行いやすくなる。