JP7601261B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP7601261B2 JP7601261B2 JP2023570606A JP2023570606A JP7601261B2 JP 7601261 B2 JP7601261 B2 JP 7601261B2 JP 2023570606 A JP2023570606 A JP 2023570606A JP 2023570606 A JP2023570606 A JP 2023570606A JP 7601261 B2 JP7601261 B2 JP 7601261B2

- Authority

- JP

- Japan

- Prior art keywords

- ceramic substrate

- semiconductor device

- porous sic

- metal

- holding

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/29—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials characterised by the substrates

- H10P14/2901—Materials

- H10P14/2902—Materials being Group IVA materials

- H10P14/2904—Silicon carbide

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/60—Formation of materials, e.g. in the shape of layers or pillars of insulating materials

- H10P14/63—Formation of materials, e.g. in the shape of layers or pillars of insulating materials characterised by the formation processes

- H10P14/6326—Deposition processes

- H10P14/6342—Liquid deposition, e.g. spin-coating, sol-gel techniques or spray coating

- H10P14/6346—Liquid deposition, e.g. spin-coating, sol-gel techniques or spray coating using printing, e.g. ink-jet printing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W40/00—Arrangements for thermal protection or thermal control

- H10W40/10—Arrangements for heating

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W40/00—Arrangements for thermal protection or thermal control

- H10W40/20—Arrangements for cooling

- H10W40/25—Arrangements for cooling characterised by their materials

- H10W40/255—Arrangements for cooling characterised by their materials having a laminate or multilayered structure, e.g. direct bond copper [DBC] ceramic substrates

Landscapes

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

- Die Bonding (AREA)

- Parts Printed On Printed Circuit Boards (AREA)

- Ceramic Products (AREA)

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Ceramic Engineering (AREA)

Description

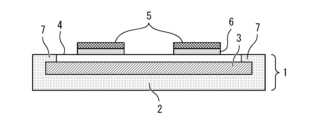

図1は、実施の形態1に係る半導体装置を示す断面図である。図2は、実施の形態1に係る半導体装置を示す上面図である。この半導体装置はパワーモジュールである。一体型ベース板1は、Alを主成分とする金属を含侵させた多孔質SiC2と、セラミック基板3と、セラミック基板3の上に設けられた回路パターン4とを有する。多孔質SiC2は、セラミック基板3を保持する保持部7を有する。保持部7は、セラミック基板3の外周全体を囲んでセラミック基板3を保持する。

図4は、実施の形態2に係る半導体装置を示す上面図である。セラミック基板3は平面視で四角形である。多孔質SiC2は、3箇所以上でセラミック基板3の側面に接してセラミック基板3を保持する保持部7を有する。保持部7は、四角形のセラミック基板3の異なる3辺をそれぞれ保持する。保持部7が設けられていない部分からセラミック基板3を保持部7の内側に挿入する。

図5は、実施の形態3に係る半導体装置を示す断面図である。多孔質SiC2はセラミック基板3を保持する鍵状の保持部7を有する。鍵状の保持部7はセラミック基板3の側面と上面を抱き込むように設けられている。これにより、セラミック基板3が含侵時にずれるのを防ぐことができる。従って、含侵時のプロセスマージンを確保し、生産性を向上させることができる。その他の構成及び効果は実施の形態2と同様である。

図6は、実施の形態4に係る半導体装置を示す断面図である。保持部7はセラミック基板3の異なる3辺をそれぞれ保持するように設けられている。保持部7が設けられていないセラミック基板3の1辺側を、含侵時に金属9を供給する湯口側とする。これにより、湯口側からの金属9の流動性を確保しつつ、セラミック基板3の位置決めと保持を実現することができる。その他の構成及び効果は実施の形態3と同様である。

図7は、実施の形態5に係る半導体装置を示す上面図である。実施の形態1では大判のセラミック基板3を1枚だけ用いていたが、本実施の形態ではセラミック基板3は2枚以上に分割されている。多孔質SiC2は、分割された2枚以上のセラミック基板3を保持する。大判のセラミック基板よりも安価な個片のセラミック基板を使用することで、製造コストを低減することができる。また、セラミック基板3に対する応力を緩和することができる。その他の構成及び効果は実施の形態1と同様である。

Claims (10)

- Alを主成分とする金属を含侵させた多孔質SiCと、

セラミック基板と、

前記セラミック基板の上に設けられた回路パターンと、

前記回路パターンに接合された半導体チップとを備え、

前記多孔質SiCは、前記セラミック基板を保持する保持部を有し、

前記保持部は鍵状であることを特徴とする半導体装置。 - 前記保持部は、前記セラミック基板の外周全体を囲んで前記セラミック基板を保持することを特徴とする請求項1に記載の半導体装置。

- 前記保持部は、3箇所以上で前記セラミック基板の側面に接して前記セラミック基板を保持することを特徴とする請求項1に記載の半導体装置。

- 前記セラミック基板は平面視で四角形であり、

前記保持部は前記セラミック基板の異なる3辺をそれぞれ保持することを特徴とする請求項3に記載の半導体装置。 - 前記セラミック基板は2枚以上に分割されていることを特徴とする請求項1~4の何れか1項に記載の半導体装置。

- 前記半導体チップはワイドバンドギャップ半導体によって形成されていることを特徴とする請求項1~5の何れか1項に記載の半導体装置。

- 保持部を有する多孔質SiCを形成する工程と、

セラミック基板を前記保持部に保持させる工程と、

Alを主成分とする金属を前記多孔質SiCに含侵させる工程と、

前記多孔質SiCに前記金属を含侵させた後に、前記セラミック基板の上面の残った前記金属をエッチングして回路パターンを形成する工程と、

前記回路パターンに半導体チップを接合する工程とを備え、

前記多孔質SiCに前記金属を含侵させる際に無加圧含侵を用いることを特徴とする半導体装置の製造方法。 - 保持部を有する多孔質SiCを形成する工程と、

セラミック基板を前記保持部に保持させる工程と、

Alを主成分とする金属を前記多孔質SiCに含侵させる工程と、

前記多孔質SiCに前記金属を含侵させた後に、前記セラミック基板の上面の残った前記金属をエッチングして回路パターンを形成する工程と、

前記回路パターンに半導体チップを接合する工程とを備え、

前記保持部が設けられていない前記セラミック基板の1辺側を、含侵時に前記金属を供給する湯口側とすることを特徴とする半導体装置の製造方法。 - 前記多孔質SiCを切削加工して前記保持部を形成することを特徴とする請求項7又は8に記載の半導体装置の製造方法。

- 前記保持部を有する前記多孔質SiCと3Dプリンターにより形成することを特徴とする請求項7又は8に記載の半導体装置の製造方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2021/048880 WO2023127130A1 (ja) | 2021-12-28 | 2021-12-28 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2023127130A1 JPWO2023127130A1 (ja) | 2023-07-06 |

| JP7601261B2 true JP7601261B2 (ja) | 2024-12-17 |

Family

ID=86998432

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2023570606A Active JP7601261B2 (ja) | 2021-12-28 | 2021-12-28 | 半導体装置及びその製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20240274500A1 (ja) |

| JP (1) | JP7601261B2 (ja) |

| CN (1) | CN118414700A (ja) |

| DE (1) | DE112021008560T5 (ja) |

| WO (1) | WO2023127130A1 (ja) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003297988A (ja) | 2002-04-05 | 2003-10-17 | Denki Kagaku Kogyo Kk | 構造物 |

| WO2016017689A1 (ja) | 2014-07-31 | 2016-02-04 | 電気化学工業株式会社 | アルミニウム‐炭化珪素質複合体及びその製造方法 |

| JP2021004668A (ja) | 2019-06-27 | 2021-01-14 | 京セラ株式会社 | 流路部材 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08191120A (ja) * | 1995-01-10 | 1996-07-23 | Hitachi Ltd | パワー半導体素子用基板とその製造方法 |

-

2021

- 2021-12-28 CN CN202180105114.0A patent/CN118414700A/zh active Pending

- 2021-12-28 WO PCT/JP2021/048880 patent/WO2023127130A1/ja not_active Ceased

- 2021-12-28 US US18/690,472 patent/US20240274500A1/en active Pending

- 2021-12-28 DE DE112021008560.3T patent/DE112021008560T5/de active Pending

- 2021-12-28 JP JP2023570606A patent/JP7601261B2/ja active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003297988A (ja) | 2002-04-05 | 2003-10-17 | Denki Kagaku Kogyo Kk | 構造物 |

| WO2016017689A1 (ja) | 2014-07-31 | 2016-02-04 | 電気化学工業株式会社 | アルミニウム‐炭化珪素質複合体及びその製造方法 |

| JP2021004668A (ja) | 2019-06-27 | 2021-01-14 | 京セラ株式会社 | 流路部材 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN118414700A (zh) | 2024-07-30 |

| DE112021008560T5 (de) | 2024-10-31 |

| US20240274500A1 (en) | 2024-08-15 |

| WO2023127130A1 (ja) | 2023-07-06 |

| JPWO2023127130A1 (ja) | 2023-07-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8569890B2 (en) | Power semiconductor device module | |

| KR100957078B1 (ko) | 전기적으로 절연된 전력 장치 패키지 | |

| KR102418458B1 (ko) | 전력반도체 모듈 | |

| JP6699742B2 (ja) | 半導体装置 | |

| US20150221525A1 (en) | Semiconductor device and method of manufacture thereof | |

| CN101335263A (zh) | 半导体模块和半导体模块的制造方法 | |

| JP3972821B2 (ja) | 電力用半導体装置 | |

| CN110021565B (zh) | 具有芯片载体的至少部分暴露的内侧壁的包封式无引线封装 | |

| JP2012209470A (ja) | 半導体装置、半導体装置モジュール及び半導体装置の製造方法 | |

| CN111433910B (zh) | 半导体装置以及半导体装置的制造方法 | |

| JP7601261B2 (ja) | 半導体装置及びその製造方法 | |

| EP3739624A1 (en) | Semiconductor arrangement with a compressible contact element encapsulated between two carriers and corresponding manufacturing method | |

| JPH11214612A (ja) | パワー半導体モジュール | |

| KR102588854B1 (ko) | 파워모듈 및 그 제조방법 | |

| CN112447615B (zh) | 半导体器件封装组件及其制造方法 | |

| KR20230034618A (ko) | 파워모듈용 세라믹 기판, 그 제조방법 및 이를 구비한 파워모듈 | |

| JP7480715B2 (ja) | 半導体装置 | |

| KR102603439B1 (ko) | 음각기판을 구비한 반도체 패키지 및 이의 제조방법 | |

| CN118398561A (zh) | 作为半导体本体的侧向边缘部分的应力释放结构 | |

| KR102714726B1 (ko) | 파워모듈용 세라믹 기판, 그 제조방법 및 이를 구비한 파워모듈 | |

| CN119234310A (zh) | 半导体装置及其制造方法 | |

| JP2019040955A (ja) | 半導体モジュールの製造方法 | |

| JP2022044158A (ja) | 半導体モジュールの製造方法 | |

| JP2007027261A (ja) | パワーモジュール | |

| KR102588851B1 (ko) | 파워모듈 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20231211 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240903 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240918 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20241105 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20241118 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7601261 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |