JP7111140B2 - semiconductor equipment - Google Patents

semiconductor equipment Download PDFInfo

- Publication number

- JP7111140B2 JP7111140B2 JP2020158041A JP2020158041A JP7111140B2 JP 7111140 B2 JP7111140 B2 JP 7111140B2 JP 2020158041 A JP2020158041 A JP 2020158041A JP 2020158041 A JP2020158041 A JP 2020158041A JP 7111140 B2 JP7111140 B2 JP 7111140B2

- Authority

- JP

- Japan

- Prior art keywords

- wire

- electrode

- semiconductor element

- bonding

- wiring member

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/0601—Structure

- H01L2224/0603—Bonding areas having different sizes, e.g. different heights or widths

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8312—Aligning

- H01L2224/83136—Aligning involving guiding structures, e.g. spacers or supporting members

- H01L2224/83138—Aligning involving guiding structures, e.g. spacers or supporting members the guiding structures being at least partially left in the finished device

- H01L2224/8314—Guiding structures outside the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8319—Arrangement of the layer connectors prior to mounting

- H01L2224/83192—Arrangement of the layer connectors prior to mounting wherein the layer connectors are disposed only on another item or body to be connected to the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Description

この明細書における開示は、半導体装置に関する。 The disclosure in this specification relates to semiconductor devices.

特許文献1は、はんだ厚を確保するNiボールを開示する。先行技術文献の記載内容は、この明細書における技術的要素の説明として、参照により援用される。

Niボールは、適用対象が限定される。たとえばソルダダイボンドの場合、Niボールは、はんだの溶融炉内において少なからず溶ける。よって、はんだ(接合部材)の最低保証厚みを確保できない虞がある。上述の観点において、または言及されていない他の観点において、半導体装置にはさらなる改良が求められている。 Ni balls are limited in application. For example, in the case of solder die bonding, Ni balls are not a little melted in a solder melting furnace. Therefore, there is a possibility that the minimum guaranteed thickness of the solder (joining member) cannot be ensured. In view of the above or in other aspects not mentioned, semiconductor devices are desired to be further improved.

開示されるひとつの目的は、信頼性の高い半導体装置を提供することにある。 One object of the disclosure is to provide a highly reliable semiconductor device.

ここに開示された半導体装置は、主電極として、表面に形成された表面電極(31)と、板厚方向において表面とは反対の裏面に形成され、表面電極よりも面積の大きい裏面電極(32)と、を有する半導体素子(30)と、第1対向面と第2対向面との間に介在して接合部を形成する接合部材と、接合部材を介して主電極と電気的に接続された配線部材と、接合部材内に配置され、第1対向面に固定されて第1対向面から突起する複数のワイヤ片(90)と、を備え、配線部材は、裏面側に配置され、裏面電極と接続された裏側配線部材(40)を含み、接合部材は、裏面電極と裏側配線部材との接合部を形成し、複数のワイヤ片が配置された裏側接合部材(80)を含み、裏側接合部材は、板厚方向の平面視において、素子中心を含む半導体素子の中央部分と重なる中央領域(80a)と、中央部分を取り囲む半導体素子の外周部分と重なる部分を含み、中央領域を取り囲む外周領域(80b)と、を有し、外周領域には、4つ以上のワイヤ片が少なくとも半導体素子の四隅のそれぞれに対応して配置され、ワイヤ片の少なくともひとつが、平面視において素子中心に向けて延びている。そして、半導体装置のひとつにおいて、ワイヤ片は、主電極と配線部材との接合部において配線部材に固定されており、板厚方向において主電極と対向する側に、配線部材における固定面と平行な平坦部(92)を有し、板厚方向において配線部材と対向する側に、配線部材との固定部(91)と、固定部に連なり、配線部材に固定されていない部分である非固定部(93)と、を有している。半導体装置の他のひとつにおいて、ワイヤ片は、主電極と配線部材との接合部において配線部材に固定されており、ワイヤ片それぞれの体積が、1.0×10 7 μm 3 以下であり、ワイヤ片は、配線部材に接合された部分である接合部(94)と、接合部に連なるとともにワイヤ片の延設方向の両端にそれぞれ設けられ、配線部材に接合されていない部分である非接合部(95、96)と、を有する。半導体装置の他のひとつにおいて、中央領域には、3つ以上のワイヤ片が素子中心を取り囲むように配置されている。半導体装置の他のひとつにおいて、配線部材は、表面側に配置され、表面電極と電気的に接続された表側配線部材(50、55)を含み、接合部材は、表面電極と表側配線部材との接合部を形成し、複数のワイヤ片が配置された表側接合部材(81)を含み、半導体素子は、表面に形成されたゲートパッド(33g)と、表面側に形成され、ゲートパッドに連なるゲート配線(34)と、表面に形成された保護膜の一部分であり、ゲート配線を保護するゲート配線保護部(35)と、を有し、表側接合部材において、ワイヤ片は、ゲート配線保護部と重ならない位置に配置されている。半導体装置の他のひとつにおいて、配線部材は、表面側に配置され、表面電極と電気的に接続された表側配線部材(50、55)を含み、接合部材は、表面電極と表側配線部材との接合部を形成し、複数のワイヤ片が配置された表側接合部材(81)を含み、表側接合部材内のワイヤ片は、裏側接合部材内のワイヤ片と重ならない位置に配置されている。半導体装置の他のひとつにおいて、配線部材は、表面側に配置され、表面電極と電気的に接続された表側配線部材(50、55)を含み、接合部材は、表面電極と表側配線部材との接合部を形成し、複数のワイヤ片が配置された表側接合部材(81)を含み、表側配線部材は、第1配線部材(55)と、第1配線部材を介して表面電極と接続された第2配線部材(50)と、を含み、接合部材は、表面側に配置された接合部材として、表側接合部材である第1接合部材(81)と、第2配線部材と第1配線部材との接合部を形成し、複数のワイヤ片が配置された第2接合部材(82)と、を含み、ワイヤ片の数が、裏側接合部材、第1接合部材、および第2接合部材において互いに異なり、裏側接合部材が最も多く、第2接合部材が最も少ない。 The semiconductor device disclosed herein includes, as main electrodes, a front electrode (31) formed on the front surface and a rear electrode (32) formed on the rear surface opposite to the front surface in the plate thickness direction and having a larger area than the front electrode. ), a bonding member interposed between the first opposing surface and the second opposing surface to form a bonding portion, and electrically connected to the main electrode via the bonding member. and a plurality of wire pieces (90) arranged in the joining member, fixed to the first opposing surface and protruding from the first opposing surface, the wiring member being arranged on the back surface side and a back side wiring member (40) connected to the electrode, the joint member forming a joint between the back electrode and the back side wiring member, and comprising a back side joint member (80) in which a plurality of wire pieces are arranged; The bonding member includes a central region (80a) that overlaps with the central portion of the semiconductor element including the element center and a portion that overlaps with the outer peripheral portion of the semiconductor element surrounding the central portion in plan view in the plate thickness direction, and has an outer circumference surrounding the central region. and a region (80b), in which four or more wire pieces are arranged corresponding to at least four corners of the semiconductor element in the outer peripheral region, and at least one of the wire pieces is oriented toward the center of the element in plan view. extended. In one semiconductor device, the wire piece is fixed to the wiring member at the junction between the main electrode and the wiring member, and is provided on the side facing the main electrode in the plate thickness direction parallel to the fixing surface of the wiring member. It has a flat portion (92), and on the side facing the wiring member in the plate thickness direction, a fixed portion (91) with the wiring member, and a non-fixed portion that is a portion that is connected to the fixed portion and is not fixed to the wiring member. (93). In another semiconductor device, the wire piece is fixed to the wiring member at the junction between the main electrode and the wiring member, the volume of each wire piece is 1.0×10 7 μm 3 or less, and the wire The piece includes a joint portion (94) that is a portion joined to the wiring member, and a non-joint portion that is a portion that is connected to the joint portion and provided at each end in the extending direction of the wire piece and is not joined to the wiring member. (95, 96) and In another semiconductor device, the central region has three or more wire pieces arranged to surround the center of the device. In another semiconductor device, the wiring members include front wiring members (50, 55) arranged on the front surface side and electrically connected to the surface electrodes, and the joining member is a connection member between the front electrodes and the front wiring members. The semiconductor element includes a front side bonding member (81) forming a bonding portion and having a plurality of wire pieces arranged thereon, the semiconductor element having a gate pad (33g) formed on the surface side and a gate formed on the surface side and connected to the gate pad. a wire (34) and a gate wire protection portion (35) which is a part of a protective film formed on the surface and protects the gate wire; placed in a non-overlapping position. In another semiconductor device, the wiring members include front wiring members (50, 55) arranged on the front surface side and electrically connected to the surface electrodes, and the joining member is a connection member between the front electrodes and the front wiring members. It includes a front side joint member (81) forming a joint and having a plurality of wire pieces arranged thereon, the wire pieces in the front side joint member being arranged so as not to overlap the wire pieces in the back side joint member. In another semiconductor device, the wiring members include front wiring members (50, 55) arranged on the front surface side and electrically connected to the surface electrodes, and the joining member is a connection member between the front electrodes and the front wiring members. A front side joint member (81) forming a joint portion and having a plurality of wire pieces arranged therein is included, and the front side wiring member is connected to a first wiring member (55) and a surface electrode via the first wiring member. a second wiring member (50), wherein the bonding members include a first bonding member (81) which is a front side bonding member, the second wiring member, and the first wiring member as bonding members arranged on the front side; and a second joint member (82) having a plurality of wire pieces arranged thereon, the number of wire pieces being different from each other in the back joint member, the first joint member and the second joint member. , the back side joint member is the most and the second joint member is the least.

開示の半導体装置によると、ワイヤ片は、第1対向面に固定されている。第1対向面から突起するワイヤ片により、接合部材の厚みを確保することができる。両面に主電極を有する半導体素子に反りが生じていても、外周領域に設けたワイヤ片によって、接合部材の厚みを確保することができる。また、素子中心に向けて延びるワイヤ片は、はんだが濡れ拡がる際に流れを阻害し難い。以上より、信頼性の高い半導体装置を提供することができる。 According to the disclosed semiconductor device, the wire piece is fixed to the first opposing surface. The wire piece protruding from the first opposing surface can ensure the thickness of the joining member. Even if the semiconductor element having the main electrodes on both sides is warped, the wire piece provided in the outer peripheral region can ensure the thickness of the joining member. Also, the wire pieces extending toward the center of the element are less likely to block the flow of the solder when it spreads. As described above, a highly reliable semiconductor device can be provided.

この明細書における開示された複数の態様は、それぞれの目的を達成するために、互いに異なる技術的手段を採用する。請求の範囲およびこの項に記載した括弧内の符号は、後述する実施形態の部分との対応関係を例示的に示すものであって、技術的範囲を限定することを意図するものではない。この明細書に開示される目的、特徴、および効果は、後続の詳細な説明、および添付の図面を参照することによってより明確になる。 The multiple aspects disclosed in this specification employ different technical means to achieve their respective objectives. Reference numerals in parentheses described in the claims and this section are intended to exemplify the correspondence with portions of the embodiments described later, and are not intended to limit the technical scope. Objects, features, and advantages disclosed in this specification will become clearer with reference to the following detailed description and accompanying drawings.

以下、図面に基づいて複数の実施形態を説明する。複数の実施形態において、機能的におよび/または構造的に対応する部分および/または関連付けられる部分には同一の参照符号が付される場合がある。対応する部分および/または関連付けられる部分については、他の実施形態の説明を参照することができる。 A plurality of embodiments will be described below based on the drawings. In several embodiments, functionally and/or structurally corresponding and/or related parts may be labeled with the same reference numerals. For corresponding and/or associated parts, reference can be made to the description of other embodiments.

(第1実施形態)

先ず、図1に基づき、半導体装置が適用される電力変換装置について説明する。

(First embodiment)

First, based on FIG. 1, a power conversion device to which a semiconductor device is applied will be described.

<電力変換装置>

図1に示す電力変換装置1は、たとえば電気自動車やハイブリッド自動車に搭載される。電力変換装置1は、直流電源2とモータジェネレータ3との間で電力変換を行う。電力変換装置1は、直流電源2およびモータジェネレータ3とともに、車両の駆動システムを構成する。

<Power converter>

A

直流電源2は、リチウムイオン電池やニッケル水素電池などの充放電可能な二次電池である。モータジェネレータ3は、三相交流方式の回転電機である。モータジェネレータ3は、車両の走行駆動源、すなわち電動機として機能する。モータジェネレータ3は、回生時に発電機として機能する。

The

電力変換装置1は、平滑コンデンサ4と、電力変換器であるインバータ5を備えている。平滑コンデンサ4の正極側端子は、直流電源2の高電位側の電極である正極に接続され、負極側端子は、直流電源2の低電位側の電極である負極に接続されている。インバータ5は、入力された直流電力を所定周波数の三相交流に変換し、モータジェネレータ3に出力する。インバータ5は、モータジェネレータ3により発電された交流電力を、直流電力に変換する。インバータ5は、DC-AC変換部である。

The

インバータ5は、三相分の上下アーム回路6を備えて構成されている。上下アーム回路6は、レグと称されることがある。各相の上下アーム回路6は、正極側の電源ラインである高電位電源ライン7と、負極側の電源ラインである低電位電源ライン8の間で、2つのアーム6H、6Lが直列に接続されてなる。各相の上下アーム回路6において、上アーム6Hと下アーム6Lの接続点は、モータジェネレータ3への出力ライン9に接続されている。

The

本実施形態では、各アームを構成するスイッチング素子として、nチャネル型の絶縁ゲートバイポーラトランジスタ6i(以下、IGBT6iと示す)を採用している。IGBT6iのそれぞれには、還流用のダイオードであるFWD6dが逆並列に接続されている。一相分の上下アーム回路6は、2つのIGBT6iを有している。上アーム6Hにおいて、IGBT6iのコレクタ電極が、高電位電源ライン7に接続されている。下アーム6Lにおいて、IGBT6iのエミッタ電極が、低電位電源ライン8に接続されている。そして、上アーム6HにおけるIGBT6iのエミッタ電極と、下アーム6LにおけるIGBT6iのコレクタ電極が相互に接続されている。

In this embodiment, an n-channel insulated gate

電力変換装置1は、上記した平滑コンデンサ4およびインバータ5に加えて、インバータ5とは別の電力変換器であるコンバータ、インバータ5やコンバータを構成するスイッチング素子の駆動回路、フィルタコンデンサなどを備えてもよい。コンバータは、直流電圧を異なる値の直流電圧に変換するDC-DC変換部である。コンバータは、直流電源2と平滑コンデンサ4との間に設けられる。フィルタコンデンサは、直流電源2に並列に接続される。フィルタコンデンサは、たとえば直流電源2からの電源ノイズを除去する。

In addition to the smoothing

<半導体装置>

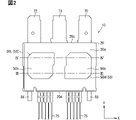

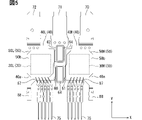

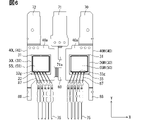

次に、図2~図6に基づき、半導体装置の一例について説明する。図3、図4は、図2のIII-III線、IV-IV線に沿う断面図である。図5は、図2に対して封止樹脂体を省略した図である。図6は、図5に対してエミッタ電極側のヒートシンクを省略した図である。半導体装置を構成する要素の一部について、符号末尾に上アーム6H側を示す「H」を付与し、下アーム6L側を示す「L」を付与している。要素の他の一部について、便宜上、上アーム6Hと下アーム6Lとで共通の符号を付与している。

<Semiconductor device>

Next, an example of a semiconductor device will be described with reference to FIGS. 2 to 6. FIG. 3 and 4 are cross-sectional views taken along lines III-III and IV-IV in FIG. FIG. 5 is a diagram in which a sealing resin body is omitted from FIG. FIG. 6 is a diagram in which the heat sink on the emitter electrode side is omitted from FIG. Some of the elements constituting the semiconductor device are suffixed with "H" indicating the

以下では、半導体素子の板厚方向をZ方向、Z方向に直交する一方向、具体的には2つの半導体素子の並び方向をX方向と示す。また、Z方向およびX方向の両方向に直交する方向をY方向と示す。特に断わりのない限り、Z方向から平面視した形状、換言すればX方向およびY方向により規定されるXY面に沿う形状を平面形状とする。また、Z方向からの平面視を単に平面視と示す。 Hereinafter, the plate thickness direction of a semiconductor element is referred to as the Z direction, and one direction orthogonal to the Z direction, specifically, the direction in which two semiconductor elements are arranged is referred to as the X direction. A direction orthogonal to both the Z direction and the X direction is indicated as the Y direction. Unless otherwise specified, a planar shape is defined as a planar shape viewed from the Z direction, in other words, a planar shape along the XY plane defined by the X and Y directions. A plan view from the Z direction is simply referred to as a plan view.

図2~図6に示すように、半導体装置10は、封止樹脂体20と、半導体素子30と、ヒートシンク40と、ヒートシンク50およびターミナル55と、継手部60~62と、主端子70~72および信号端子75を備えている。半導体装置10は、上記した一相分の上下アーム回路6を構成する。

As shown in FIGS. 2 to 6, the

封止樹脂体20は、半導体装置10を構成する他の要素の一部を封止している。他の要素の残りの部分は、封止樹脂体20の外に露出している。封止樹脂体20は、たとえばエポキシ系樹脂を材料とする。封止樹脂体20は、たとえばトランスファモールド法により成形されている。図2~図4に示すように、封止樹脂体20は平面略矩形状をなしている。封止樹脂体20は、表面20aと、Z方向において表面20aとは反対の裏面20bを有している。表面20aおよび裏面20bは、たとえば平坦面となっている。

The encapsulating

半導体素子30は、シリコン(Si)、シリコンよりもバンドギャップが広いワイドバンドギャップ半導体などを材料とする半導体基板に、素子が形成されてなる。ワイドバンドギャップ半導体としては、たとえばシリコンカーバイド(SiC)、窒化ガリウム(GaN)、酸化ガリウム(Ga2O3)、ダイヤモンドがある。半導体素子30は、半導体チップと称されることがある。

The

素子は、Z方向に主電流が流れるように縦型構造をなしている。縦型素子として、IGBT、MOSFET、ダイオードなどを採用することができる。本実施形態では、縦型素子として、ひとつのアームを構成するIGBT6iおよびFWD6dが形成されている。縦型素子は、RC(Reverse Conducting)-IGBTである。半導体素子30は、図示しないゲート電極を有している。ゲート電極は、たとえばトレンチ構造をなしている。半導体素子30は、自身の板厚方向、すなわちZ方向における両面に、素子の主電極を有している。具体的には、主電極として、表面側にエミッタ電極31を有し、裏面側にコレクタ電極32を有している。エミッタ電極31は、FWD6dのアノード電極を兼ねている。コレクタ電極32は、FWD6dのカソード電極を兼ねている。エミッタ電極31が表面電極に相当し、コレクタ電極32が裏面電極に相当する。

The device has a vertical structure so that the main current flows in the Z direction. IGBTs, MOSFETs, diodes, and the like can be employed as vertical devices. In this embodiment, the

半導体素子30は、平面略矩形状をなしている。図6に示すように、半導体素子30は、表面においてエミッタ電極31とは異なる位置に形成されたパッド33を有している。エミッタ電極31およびパッド33は、半導体基板の表面の図示しない保護膜からそれぞれ露出している。エミッタ電極31は、半導体素子30の表面の一部分に形成されている。コレクタ電極32は、裏面のほぼ全面に形成されている。平面視において、コレクタ電極32は、エミッタ電極31よりも面積が大きい。

The

パッド33は、信号用の電極である。パッド33は、エミッタ電極31と電気的に分離されている。パッド33は、Y方向において、エミッタ電極31の形成領域とは反対側の端部に形成されている。パッド33は、ゲート電極用のゲートパッド33gを含む。本実施形態において、半導体素子30は、5つのパッド33を有している。具体的には、上記したゲートパッド33g、エミッタ電極31の電位を検出するケルビンエミッタ用、電流センス用、半導体素子30の温度を検出する温度センサ(感温ダイオード)のアノード電位用、同じくカソード電位用を有している。5つのパッド33は、平面略矩形状の半導体素子30において、Y方向の一端側にまとめて形成されるとともに、X方向に並んで形成されている。

The

半導体装置10は、2つの半導体素子30を備えている。具体的には、上アーム6Hを構成する半導体素子30Hと、下アーム6Lを構成する半導体素子30Lを備えている。半導体素子30H、30Lは、互いに同様の構成を有している。半導体素子30H、30Lは、X方向に並んでいる。半導体素子30H、30Lは、Z方向において互いにほぼ同じ位置に配置されている。

The

ヒートシンク40は、Z方向において半導体素子30の裏面側に配置され、はんだ80を介して、コレクタ電極32と電気的に接続された配線部材である。はんだ80は、ヒートシンク40とコレクタ電極32とを接続(接合)している。ヒートシンク40が裏側配線部材に相当し、はんだ80が裏側接合部材に相当する。ヒートシンク40は、半導体素子30との対向面である実装面40aと、実装面40aとは反対の面である裏面40bを有している。ヒートシンク40の実装面40aと半導体素子30のコレクタ電極32との間にはんだ80が介在し、はんだ接合部が形成されている。

The

ヒートシンク40は、半導体素子30の熱を外部に放熱する。ヒートシンク40としては、たとえばCu、Cu合金などを材料とする金属板、DBC(Direct Bonded Copper)基板などを採用することができる。表面に、NiやAuなどのめっき膜を備えてもよい。本実施形態において、ヒートシンク40は、Cuを材料とする金属板である。ヒートシンク40は、放熱部材、導電部材、リードフレームと称されることがある。半導体装置10は、2つのヒートシンク40を備えている。具体的には、上アーム6Hを構成するヒートシンク40Hと、下アーム6Lを構成するヒートシンク40Lを備えている。

The

図6に示すように、ヒートシンク40H、40Lは、平面略矩形状をなしている。ヒートシンク40H、40Lは、X方向に並んでいる。図3および図4に示すように、ヒートシンク40H、40Lは、互いにほぼ同じ厚みを有し、Z方向において互いにほぼ同じ位置に配置されている。ヒートシンク40Hの実装面40aと半導体素子30Hのコレクタ電極32との間、および、ヒートシンク40Lの実装面40aと半導体素子30Lのコレクタ電極32との間のそれぞれに、はんだ接合部が形成されている。

As shown in FIG. 6, the

ヒートシンク40H、40Lは、Z方向からの平面視において、対応する半導体素子30を内包している。ヒートシンク40H、40Lの裏面40bは、封止樹脂体20から露出している。裏面40bは、放熱面、露出面と称されることがある。裏面40bは、封止樹脂体20の裏面20bと略面一である。ヒートシンク40H、40Lの裏面40bは、X方向に並んでいる。

The

ヒートシンク50およびターミナル55は、Z方向において半導体素子30の表面側に配置され、はんだ81、82を介して、エミッタ電極31と電気的に接続された配線部材である。ターミナル55は、Z方向において半導体素子30とヒートシンク50との間に介在している。はんだ81は、ターミナル55とエミッタ電極31とを接続(接合)している。はんだ82は、ヒートシンク50とターミナル55とを接続(接合)している。

The

ターミナル55は、半導体素子30との対向面である第1端面55aと、第1端面55aとは反対の面である第2端面55bを有している。ヒートシンク50は、第2端面55bとの対向面である実装面50aと、実装面50aとは反対の面である裏面50bを有している。実装面50aは、ヒートシンク50において半導体素子30側の面である。ターミナル55の第1端面55aと半導体素子30のエミッタ電極31との間にはんだ81が介在し、はんだ接合部が形成されている。ターミナル55の第2端面55bとヒートシンク50の実装面50aとの間にはんだ82が介在し、はんだ接合部が形成されている。ヒートシンク50およびターミナル55が、表側配線部材に相当する。はんだ81が、表側接合部材に相当する。

The terminal 55 has a

ターミナル55は、半導体素子30(エミッタ電極31)とヒートシンク50との電気伝導、熱伝導経路の途中に位置する。ターミナル55は、Cu、Cu合金などの金属材料を含んでいる。表面に、めっき膜を備えてもよい。ターミナル55H、55Lは、平面視においてエミッタ電極31とほぼ同じ大きさを有する平面略矩形状の柱状体である。ターミナル55は、金属ブロック体、中継部材と称されることがある。半導体装置10は、2つのターミナル55を備えている。具体的には、上アーム6Hを構成するターミナル55Hと、下アーム6Lを構成するターミナル55Lを備えている。ターミナル55Hの第1端面55aと半導体素子30Hのエミッタ電極31との間、および、ターミナル55Lの第1端面55aと半導体素子30Lのエミッタ電極31との間に、はんだ接合部がそれぞれ形成されている。

The terminal 55 is located in the middle of the electrical and thermal conduction paths between the semiconductor element 30 (emitter electrode 31 ) and the

ヒートシンク50は、半導体素子30の熱を外部に放熱する。ヒートシンク50は、ヒートシンク40と同様の構成を有している。本実施形態において、ヒートシンク50は、Cuを材料とする金属板である。半導体装置10は、2つのヒートシンク50を備えている。具体的には、上アーム6Hを構成するヒートシンク50Hと、下アーム6Lを構成するヒートシンク50Lを備えている。

The

図5に示すように、ヒートシンク50H、50Lは、平面略矩形状をなしている。ヒートシンク50H、50Lは、X方向に並んでいる。図3および図4に示すように、ヒートシンク50H、50Lは、互いにほぼ同じ厚みを有し、Z方向において互いにほぼ同じ位置に配置されている。ヒートシンク50Hの実装面50aとターミナル55Hの第2端面55bとの間、および、ヒートシンク50Lの実装面50aとターミナル55Lの第2端面55bとの間のそれぞれに、はんだ接合部が形成されている。

As shown in FIG. 5, the

ヒートシンク50H、50Lは、Z方向からの平面視において、対応する半導体素子30およびターミナル55を内包している。ヒートシンク50H、50Lの実装面50aには、溢れたはんだ82を収容する溝51が形成されている。溝51は、実装面50aにおいてはんだ接合部を取り囲んでいる。溝51は、たとえば環状に形成されている。ヒートシンク50H、50Lの裏面50bは、封止樹脂体20から露出している。裏面50bは、放熱面、露出面と称されることがある。裏面50bは、封止樹脂体20の表面20aと略面一である。ヒートシンク50H、50Lの裏面50bは、X方向に並んでいる。

The

継手部60~62は、上下アーム回路6を構成する要素間をつないでいる。継手部は、半導体装置10を構成する要素間をつないでいる。図3および図6に示すように、継手部60は、ヒートシンク40Lに連なっている。継手部60の厚みは、ヒートシンク40Lよりも薄い。継手部60は、ヒートシンク40Lの実装面40aと略面一の状態で、ヒートシンク40Hとの対向面(側面)に連なっている。継手部60は、2つの屈曲部を有することで、ZX平面において略クランク状をなしている。継手部60は、封止樹脂体20によって覆われている。継手部60は、ヒートシンク40Lに対して一体的に設けられることで連なってもよいし、別部材として設けられ、接続により連なってもよい。本実施形態において、継手部60は、リードフレームの一部として、ヒートシンク40Lと一体的に設けられている。

The

図3および図5に示すように、継手部61、62は、対応するヒートシンク50に連なっている。継手部61は、ヒートシンク50Hに連なっている。継手部62は、ヒートシンク50Lに連なっている。継手部61、62の厚みは、対応するヒートシンク50よりも薄い。継手部61、62は、封止樹脂体20によって覆われている。継手部61、62は、ヒートシンク50に対して一体的に設けられることで連なってもよいし、別部材として設けられ、接続により連なってもよい。本実施形態において、継手部61、62は、対応するヒートシンク50H、50Lに対して一体的に設けられている。継手部61、62は、2つのヒートシンク50H、50Lにおいて、互いに対向する側面からX方向に延設されている。

As shown in FIGS. 3 and 5 , the

継手部61を含むヒートシンク50Hと、継手部62を含むヒートシンク50Lとが共通部材となっている。継手部61を含むヒートシンク50Hと、継手部62を含むヒートシンク50Lとの配置は、Z軸を回転軸とする2回対称となっている。継手部60と継手部61との対向面間にはんだ83が介在し、はんだ接合部が形成されている。

The

継手部61の接合面には、溢れたはんだ83を収容する溝63が形成されている。溝63は、はんだ接合部を取り囲むように環状に形成されている。同様に、継手部62の接合面にも、溢れたはんだを収容する溝63が形成されている。本実施形態において、溝63がプレス加工により形成されている。このため、継手部61、62は、溝63の裏面側に凸部64を有している。

A

主端子70~72および信号端子75は、外部接続端子である。主端子70、71は、電源端子である。主端子70は、平滑コンデンサ4の正極端子と電気的に接続される。主端子71は、平滑コンデンサ4の負極端子と電気的に接続される。このため、主端子70はP端子、主端子71はN端子と称されることがある。

The

図5および図6に示すように、主端子70は、ヒートシンク40HにおけるY方向の一端に連なっている。主端子70の厚みは、ヒートシンク40Hよりも薄い。主端子70は、実装面40aと略面一でヒートシンク40Hに連なっている。主端子70は、ヒートシンク40HからY方向に延設され、封止樹脂体20の側面20cから外部に突出している。主端子70は、封止樹脂体20により覆われる部分の途中に屈曲部を有し、側面20cにおいてZ方向の中央付近から突出している。

As shown in FIGS. 5 and 6, the

図4および図5に示すように、主端子71は、継手部62に接続されている。主端子71と継手部62との対向面間にはんだ84が介在し、はんだ接合部が形成されている。主端子71は、Y方向に延設されて、主端子70と同じ側面20cから封止樹脂体20の外に突出している。主端子71は、Y方向の一端付近に継手部62との接続部71aを有している。主端子71のうち、接続部71aを含む一部分が封止樹脂体20により覆われ、残りの部分が封止樹脂体20から突出している。接続部71aは、封止樹脂体20から突出した部分よりも板厚が厚い。接続部71aの板厚は、たとえばヒートシンク40とほぼ同じ厚みである。主端子71も、主端子同様に屈曲部を有し、側面20cにおいてZ方向の中央付近から突出している。

As shown in FIGS. 4 and 5, the

主端子72は、上アーム6Hと下アーム6Lとの接続点に接続されている。主端子72は、モータジェネレータ3の対応する相の巻線(固定子コイル)と電気的に接続される。主端子72は、出力端子、交流端子、O端子とも称される。主端子72は、ヒートシンク40LにおけるY方向の一端に連なっている。主端子72の厚みは、ヒートシンク40Lよりも薄い。主端子72は、実装面40aと略面一でヒートシンク40Lに連なっている。主端子72は、ヒートシンク40LからY方向に延設され、主端子70と同じ側面20cから封止樹脂体20の外に突出している。主端子72も、主端子71同様に屈曲部を有し、側面20cにおいてZ方向の中央付近から突出している。3本の主端子70~72は、X方向において主端子70、主端子71、主端子72の順に配置されている。

The

信号端子75は、対応する半導体素子30のパッド33に電気的に接続されている。本実施形態では、ボンディングワイヤ87を介して電気的に接続されている。信号端子75は、Y方向に延設されており、封止樹脂体20の側面20dから外部に突出している。側面20dは、Y方向において側面20cとは反対の面である。本実施形態では、ひとつの半導体素子30に対して5本の信号端子75が設けられている。

The

なお、図2、図5、および図6に示す符号88は、吊りリードである。ヒートシンク40(40H、40L)と、継手部60と、主端子70~72と、信号端子75は、共通部材であるリードフレームに構成されている。このリードフレームは部分的に厚みが異なる異形条である。信号端子75は、カット前の状態で、タイバーを介して吊りリード88に接続される。タイバーなど、リードフレームの不要部分は、封止樹脂体20の成形後にカット(除去)されている。

上記したように、半導体装置10では、封止樹脂体20によって一相分の上下アーム回路6を構成する複数の半導体素子30が封止されている。封止樹脂体20は、複数の半導体素子30、ヒートシンク40それぞれの一部、ヒートシンク50それぞれの一部、ターミナル55、継手部60~62、主端子70~72および信号端子75それぞれの一部を、一体的に封止している。

As described above, in the

Z方向において、ヒートシンク40、50の間に、半導体素子30が配置されている。これにより、半導体素子30の熱を、Z方向において両側に放熱することができる。半導体装置10は、両面放熱構造をなしている。ヒートシンク40の裏面40bは、封止樹脂体20の裏面20bと略面一となっている。ヒートシンク50の裏面50bは、封止樹脂体20の表面20aと略面一となっている。裏面40b、50bが露出面であるため、放熱性を高めることができる。

A

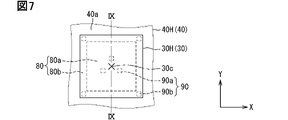

<ワイヤ片>

次に、図7~図9に基づき、ワイヤ片について説明する。図7は、図6において上アーム6H側の半導体素子30H周辺を拡大した平面図である。図7は、半導体素子とワイヤ片との位置関係を示している。図7では、便宜上、ターミナル55H、はんだ81、エミッタ電極31、パッド33、およびボンディングワイヤ87を省略して図示している。図8は、ワイヤ片の配置を示す斜視図である。図9は、図7のIX-IX線に沿う断面図である。

<Wire piece>

Next, the wire piece will be described with reference to FIGS. 7 to 9. FIG. FIG. 7 is an enlarged plan view of the periphery of the

図7~図9に示すように、半導体装置10は、ワイヤ片90をさらに備えている。ワイヤ片90は、主電極と配線部材とを電気的に接続するはんだ接合部の少なくともひとつに設けられている。ワイヤ片90は、はんだ内に配置されている。ひとつ(単一)のはんだに対して、複数のワイヤ片90が分散配置されている。複数のワイヤ片90は、はんだ接合部を構成する対向面のひとつである第1対向面に固定(接合)され、対向面の他のひとつである第2対向面に向けて突起している。

As shown in FIGS. 7-9, the

ワイヤ片90は、はんだの最低膜厚を確保すべく、所定高さを有している。複数のワイヤ片90が第2対向面に接触した状態においても、第1対向面と第2対向面との最短距離が最低膜厚以上となるように、ワイヤ片90の高さが設定されている。最低膜厚とは、所望の接続信頼性を確保するために必要な最低限の厚みである。ワイヤ片90の高さは、たとえば最低膜厚にマージンを加味した値である。ワイヤ片90は、ボンディングワイヤの小片部である。ワイヤ片90は、突起部、スタッドボンディングと称されることがある。

The

本実施形態では、複数のワイヤ片90が、半導体素子30Hのコレクタ電極32とヒートシンク40Hの実装面40aとの間のはんだ80に配置されている。複数のワイヤ片90は、そのすべてがヒートシンク40Hの実装面40aに固定(接合)されており、半導体素子30Hの裏面、すなわちコレクタ電極32上には固定されていない。ヒートシンク40Hの実装面40aが第1対向面に相当し、半導体素子30Hの裏面が第2対向面に相当する。実装面40aには、複数のワイヤ片90が固定されている。ワイヤ片90は、アルミニウムやアルミニウム合金を材料とするボンディングワイヤの小片部である。実装面40aに固定されたすべてのワイヤ片90が、はんだ80内に配置されている。

In this embodiment, a plurality of

はんだ80は、平面視において、半導体素子30Hの中央部分と重なる中央領域80aと、中央領域80aを取り囲む外周領域80bを有している。半導体素子30Hの中央部分は、素子中心30cとその周囲部分である。半導体素子30Hは、中央部分を取り囲む外周部分を有している。外周部分は、たとえば平面矩形状の4辺のそれぞれから所定範囲の部分である。たとえば中央部分は素子が形成されたアクティブ領域であり、外周部分はアクティブ領域を取り囲む外周耐圧領域である。外周領域80bは、半導体素子30Hの外周部分と重なる部分を含んでいる。中央領域80aおよび外周領域80bのそれぞれに、複数のワイヤ片90が配置されている。

The

実装面40aに固定されたワイヤ片90の一部である複数のワイヤ片90aは、平面視において素子中心30cを取り囲むように、中央領域80aに配置されている。図7に示す中心線CLは、素子中心30cを通り、Z方向に延びる仮想線である。中央領域80aのワイヤ片90aは、この中心線CLを取り囲んでいる。素子中心30cを取り囲むために、中央領域80aには3つ以上のワイヤ片90aが配置されている。本実施形態では、中央領域80aに3つのワイヤ片90aが配置されている。3つのワイヤ片90aは、素子中心30cに対して3回対称の位置関係となっている。

A plurality of

実装面40aに固定されたワイヤ片90の他の一部である複数のワイヤ片90bは、平面視において素子中心30cを取り囲むように、外周領域80bに配置されている。複数のワイヤ片90bは、少なくとも平面矩形状をなす半導体素子30Hの四隅のそれぞれに対応して配置されている。このため、外周領域80bには、4つ以上のワイヤ片90bが配置されている。本実施形態では、外周領域80bに4つのワイヤ片90bが配置されている。ワイヤ片90bは、半導体素子30Hの四隅と重なる部分に配置されている。なお、四隅とは、平面矩形状の4つの角(頂点)を指すのではなく、頂点を含む所定範囲の部分(角周辺の部分)である。

A plurality of

なお、下アーム6L側も同様の構成を有している。すなわち、半導体素子30Lのコレクタ電極32とヒートシンク40Lの実装面40aとの間のはんだ80に、複数のワイヤ片90が配置されている。複数のワイヤ片90は、実装面40aに固定されている。このため、説明を省略する。

The

<半導体装置の製造方法>

次に、上記した半導体装置10の製造方法について説明する。本実施形態では、ソルダダイボンド法を用いて、半導体装置10を形成する。

<Method for manufacturing a semiconductor device>

Next, a method for manufacturing the

先ず、ワイヤ片90を形成する。リードフレームにおけるヒートシンク40の実装面40aに、アルミニウム系のボンディングワイヤを超音波接合する。ボンディングワイヤは通常、2つの部分を電気的に接続すべく、1stボンド部と2ndボンド部を有する。ここでは、1stボンド部を形成した時点でワイヤをカットし、ワイヤ片90とする。

First, a piece of

次いで、溶融はんだを塗布して積層体を形成する。先ず、実装面40a上に溶融はんだ(はんだ80)を塗布し、コレクタ電極32が実装面40a側となるように、溶融はんだ上に半導体素子30を配置する。次いで、半導体素子30のエミッタ電極31上に溶融はんだ(はんだ81)を塗布し、第1端面55aが半導体素子30側となるように、溶融はんだ上にターミナル55を配置する。さらにターミナル55の第2端面55b上に溶融はんだ(はんだ82)を塗布する。また、継手部60および接続部71a上にも溶融はんだ(はんだ83、84)を塗布する。溶融はんだは、たとえば転写法を用いて塗布することができる。塗布した溶融はんだが固化(凝固)することで、ヒートシンク40、半導体素子30、およびターミナル55の積層体が得られる。

Molten solder is then applied to form a laminate. First, molten solder (solder 80) is applied onto the mounting

すべてのはんだ80~84を一括で固化(凝固)させてもよいし、積層順に固化(凝固)させてもよい。一括で行うことで、製造工程を簡素化(たとえば製造時間を短縮)することができる。ボンディングワイヤ87の接続は、積層体の状態で行ってもよいし、はんだ80が固化した状態で、はんだ81を塗布する前に行ってもよい。すべてのはんだ80~84の塗布が完了した積層体の状態でのボンディングのほうが、塗布装置の接触等による不良を抑制できるため好ましい。

All the

両面放熱構造の半導体装置10は、たとえば図示しない冷却器によってZ方向の両面側から挟まれる。よって、Z方向において表面の高い平行度と表面間の高い寸法精度が求められる。このため、はんだ82については、半導体装置10の高さばらつきを吸収可能な量を配置する。すなわち、多めのはんだ82を配置する。たとえば、はんだ82は、はんだ80、81よりも厚くなる。

A

次いで、実装面50aが上になるように、ヒートシンク50を図示しない台座上に配置する。そして、はんだ82がヒートシンク50の実装面50aと対向するように、積層体をヒートシンク50上に配置し、リフローを実施する。リフローでは、ヒートシンク40側からZ方向に荷重(白抜き矢印)を加えることで、半導体装置10の高さが所定高さとなるようにする。詳しくは、荷重を加えることで、図示しないスペーサを、ヒートシンク40の実装面40aと台座の載置面との両方に接触させる。このようにして、半導体装置10の高さが所定高さとなるようにする。

Next, the

リフローにより、はんだ82を介して、ターミナル55とヒートシンク50が接続(接合)される。すなわち、エミッタ電極31とヒートシンク50とが電気的に接続される。はんだ82は、半導体装置10を構成する要素の寸法公差や組み付け公差による高さばらつきを吸収する。たとえば、半導体装置10の高さを所定高さにするために、はんだ82の全量が必要な場合には、はんだ82の全量が溝51よりも内側の接続領域に留まる。一方、所定高さにするために、はんだ82の一部が溢れた場合、溢れたはんだ82は溝51内に収容される。はんだ83、84についても同様であるため、説明を省略する。

The terminal 55 and the

次いで、トランスファモールド法により封止樹脂体20の成形を行う。図示を省略するが、本実施形態では、ヒートシンク40、50が完全に被覆されるように封止樹脂体20を成形し、成形後に切削を行う。封止樹脂体20をヒートシンク40、50の一部ごと切削する。これにより、裏面40b、50bを露出させる。裏面40bは裏面20bと略面一となり、裏面50bは表面20aと略面一となる。なお、裏面40b、50bを成形金型のキャビティ壁面に押し当て、密着させた状態で、封止樹脂体20を成形してもよい。この場合、封止樹脂体20を成形した時点で、裏面40b、50bが封止樹脂体20から露出する。このため、成形後の切削が不要となる。

Next, molding of the sealing

次いで、図示しないタイバーなどを除去することで、半導体装置10を得ることができる。

Then, the

なお、積層体を形成後に、ヒートシンク50を配置し、リフローを実施する例を示したが、これに限定されない。ターミナル55の第2端面55b上に溶融はんだ(はんだ82)を塗布した後、溶融はんだ上にヒートシンク50を配置してもよい。また、すべてのはんだ80~84を一括で固化(凝固)させ、ヒートシンク50まで含む積層体を一括で形成してもよい。すなわち、リフローを実施せずに、半導体装置10を得ることもできる。

Although an example in which the

<第1実施形態のまとめ>

ヒートシンク40を、種々(複数品番)の半導体素子30に対する共通部品とすることで、部品点数の削減、コストの低減等を図ることがある。半導体素子30は、表面にエミッタ電極31を有し、裏面にコレクタ電極32を有しており、エミッタ電極31とコレクタ電極32の面積が異なる。このような構成では、膜厚、成膜方法、チップサイズ、電極面積等により、品種によって異なる方向に反りが生じ得る。たとえば、ある品種ではヒートシンク40側に凸、すなわち下に凸の反りを生じ、別の品種ではヒートシンク40とは反対側に凸、すなわち上に凸の反りを生じる。同等の素子サイズ(チップサイズ)でも、たとえば成膜方法(膜構成)が異なることで、反りの方向が異なることがある。さらには、製造条件のばらつきにより、同一品種において反りの方向が異なることがある。

<Summary of the first embodiment>

By using the

これに対し、本実施形態では、半導体素子30のコレクタ電極32とヒートシンク40との間のはんだ接合部に、複数のワイヤ片90を設けている。ワイヤ片90は、第1対向面であるヒートシンク40の実装面40aに固定されており、第2対向面である半導体素子30の裏面側に突起している。はんだ80の中央領域80aには、素子中心30cを取り囲むように3つ以上のワイヤ片90aが配置されている。はんだ80の外周領域80bには、少なくとも半導体素子30の四隅のそれぞれに対応するように、4つ以上のワイヤ片90bが配置されている。

In contrast, in this embodiment, a plurality of

よって、図10に示すように、半導体素子30が下に凸の反りを生じている場合、素子中心30cを取り囲むように配置されたワイヤ片90aにより、はんだ80の最低膜厚を確保することができる。たとえば、素子中心30cを取り囲むように配置された3つ以上のワイヤ片90aにより半導体素子30を支持することができる。これにより半導体素子30の傾きを抑制し、全面において最低膜厚を確保することができる。

Therefore, as shown in FIG. 10, when the

また、半導体素子30が上に凸の反りを生じている場合、少なくとも半導体素子30の四隅に対応して配置されたワイヤ片90bにより、はんだ80の最低膜厚を確保することができる。たとえば、少なくとも四隅に配置されたワイヤ片90bにより半導体素子30を支持することができる。これにより半導体素子30の傾きを抑制し、全面において最低膜厚を確保することができる。このように、ワイヤ片90がコレクタ電極32に接触する場合でも、ワイヤ片90の高さによってはんだ80の最低膜厚を確保することができる。

Moreover, when the

さらに、ワイヤ片90は、ヒートシンク40に固定されている。すなわち、はんだの溶融炉内に投入し、溶融はんだとともに塗布するものではない。ワイヤ片90は、溶融はんだが塗布されても、その形状を維持できる。

Additionally, the

以上より、半導体素子30に下に凸、上に凸のいずれの反りが生じても、はんだ80の膜厚を保証することができる。種々の半導体素子30を用いても、はんだ80の膜厚を保証することができる。これにより、信頼性の高い半導体装置10を提供することができる。また、はんだ厚を確保できるため超音波探傷装置(SAT:Scanning Acoustic Tomograph)によるボイドの検出精度を高めることもできる。さらに、Niボールを用いる方法に較べて、コストを低減することもできる。なお、図10では、便宜上、はんだ80を省略して図示している。

As described above, the film thickness of the

ワイヤ片90を、ヒートシンク40の実装面40aに固定する例を示したがこれに限定されない。ワイヤ片90を、半導体素子30のコレクタ電極32に固定してもよい。すなわち、半導体素子30の裏面を第1対向面としてもよい。しかしながら、ワイヤ片90をヒートシンク40(裏側配線部材)に固定する構造のほうが、ワイヤ片90を接合する際の影響が小さいため、好ましい。

Although an example in which the

ワイヤ片90の個数および配置は、上記した例に限定されない。半導体素子30の反りに応じて、中央領域80aのみにワイヤ片90を配置してもよいし、外周領域80bのみにワイヤ片90を配置してもよい。また、中央領域80aに、素子中心30cを取り囲むように4つ以上のワイヤ片90aを配置してもよい。また、外周領域80bにおいて、四隅とともに、四隅以外の部分にもワイヤ片90bを配置してもよい。すなわち、素子中心30cを取り囲むように5つ以上のワイヤ片90bを配置してもよい。ワイヤ片90の位置を、半導体素子30の大きさ(サイズ)に合わせて、ワイヤ片90を設ける際に調整してもよい。

The number and arrangement of

半導体装置10の構成は、上記した例に限定されない。たとえばターミナル55を備えない構成としてもよい。この場合、エミッタ電極31とヒートシンク50の実装面50aとを接続すればよい。ヒートシンク50の実装面50aに凸部を設け、凸部の先端とエミッタ電極31との間に、はんだ接合部を形成してもよい。

The configuration of the

表側配線部材、すなわちターミナル55およびヒートシンク50を備えない構成にも適用が可能である。たとえばエミッタ電極31にボンディングワイヤを接続し、上アーム6Hと下アーム6Lとの接続、主端子との接続を行ってもよい。ワイヤ片90を、上アーム6H側のはんだ80および下アーム6L側のはんだ80の一方のみに設けてもよい。

It can also be applied to a configuration that does not include front wiring members, that is,

(第2実施形態)

この実施形態は、先行する実施形態を基礎的形態とする変形例であり、先行実施形態の記載を援用できる。

(Second embodiment)

This embodiment is a modification based on the preceding embodiment, and the description of the preceding embodiment can be used.

先行実施形態に示したように、半導体装置10において、ワイヤ片90は第2対向面に接触していてもよいし、非接触でもよい。好ましくは、図11に示すように、ワイヤ片90を第2対向面であるコレクタ電極32に対して非接触するとよい。図11は、本実施形態の半導体装置10において、半導体素子とヒートシンクとの接続部周辺を示す断面図である。図11は、図9に対応している。図11では、便宜上、半導体素子30の表面側の電極を省略して図示している。半導体装置10の構成は、たとえば第1実施形態と同様である。図11に示す構成は、上アーム6H側と下アーム6L側とで同じである。

As shown in the previous embodiment, in the

ワイヤ片90は、ヒートシンク40の実装面40aに固定され、はんだ80内に配置されている。はんだ80による接合部において、実装面40aが第1対向面をなし、コレクタ電極32の表面が第2対向面をなしている。そして、実装面40aを基準とするワイヤ片90の突起高さH1が、はんだ80の厚みT1未満となっている。ワイヤ片90は、コレクタ電極32に接触しておらず、コレクタ電極32との間には間隙がある。突起高さH1は、上記したように最低膜厚を確保できる高さである。突起高さH1は、たとえば50~100μm程度である。はんだ80の狙い値は、たとえば150μm程度である。

The

<第2実施形態のまとめ>

本実施形態によれば、ワイヤ片90の突起高さH1がはんだ80の厚みT1未満である。よって、半導体装置10の形成時において、ワイヤ片90が第2対向面に接触しない。接触によるワイヤ片90の潰れを抑制し、ひいては、所定のはんだ厚を確保することができる。

<Summary of Second Embodiment>

According to this embodiment, the protrusion height H1 of the

また、本実施形態では、主電極が第2対向面となっている。すなわち主電極と対向する面にワイヤ片90が固定されている。このため、突起高さH1がはんだ80の厚みT1未満との条件を満たすことで、ワイヤ片90がコレクタ電極32に接触し、コレクタ電極32を傷つけるのを抑制することもできる。

Moreover, in this embodiment, the main electrode is the second facing surface. That is, the

上記した関係を、第1実施形態の構成に適用する例を示したが、これに限定されない。たとえば、はんだ80に配置されるワイヤ片90の個数が、第1実施形態とは異なる個数(たとえば総数3個)の構成にも適用することができる。なお、はんだ80内に配置するワイヤ片90は、複数、好ましくは3つ以上とするとよい。より好ましくは第1実施形態に記載の構成である。

Although an example in which the relationship described above is applied to the configuration of the first embodiment has been shown, the present invention is not limited to this. For example, a configuration in which the number of

また、はんだ80内のワイヤ片90に限定されない。ワイヤ片90が配置されるはんだであれば適用が可能である。特に主電極のはんだ接合部に好適である。たとえば、はんだ81内にワイヤ片90を設け、ターミナル55にワイヤ片90を固定する構成に適用すると、所定のはんだ厚を確保するとともに、エミッタ電極31を傷つけるのを抑制することができる。なお、上記した関係を、上アーム6H側および下アーム6L側の一方のみで満たすようにしてもよい。

Also, it is not limited to the

(第3実施形態)

この実施形態は、先行する実施形態を基礎的形態とする変形例であり、先行実施形態の記載を援用できる。

(Third Embodiment)

This embodiment is a modification based on the preceding embodiment, and the description of the preceding embodiment can be used.

本実施形態において、ワイヤ片90は、図12に示すように外周領域80bのみに配置されている。図12は、本実施形態の半導体装置10において、半導体素子30とワイヤ片90との位置関係を示す平面図である。図12は、図7に対応している。ワイヤ片90は、外周領域80bにおいて、少なくとも半導体素子30の四隅のそれぞれに対応する位置に配置されている。図12では、ワイヤ片90が、四隅のみに配置されている。ワイヤ片90は、中央領域80aには配置されていない。図12に示す構成は、上アーム6H側と下アーム6L側とで同じである。

In this embodiment, the

図示を省略するが、半導体素子30のエミッタ電極31は、AlSiなどのAl系材料を用いて半導体基板の表面上に形成された下地電極部と、下地電極部上に形成された接続電極部を有している。下地電極部は、たとえばスパッタ法により形成されている。接続電極部は、めっき法により形成されている。接続電極部は、たとえば下地電極部上に形成されたNi層と、Ni層上に形成されたAu層を含む。コレクタ電極32は、スパッタ法により形成されている。コレクタ電極32は、AlSiなどのAl系材料を用いて半導体基板の裏面上に形成されたAl層と、Al層上に形成されたNi層を含む。めっき法を用いるエミッタ電極31のほうがコレクタ電極32よりも厚い。

Although illustration is omitted, the

<第3実施形態のまとめ>

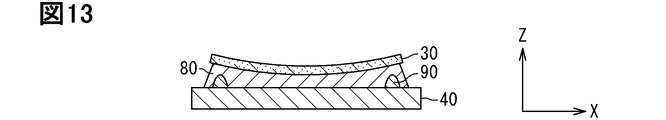

図13は、図12のXIII-XIII線に沿う断面図であり、半導体素子30とヒートシンク40との接続構造を示している。上記した電極構成において、半導体素子30は、図13に示すように下に凸の反りを生じうる。本実施形態では、はんだ80の最低膜厚を確保するように、はんだ80の供給量が設定されている。はんだ80は、半導体素子30(コレクタ電極32)とヒートシンク40との接合部を濡れ拡がった状態で、最低膜厚以上の所定の厚みを確保できるように供給される。図13に示すように、半導体素子30は、はんだ80に支持され、ワイヤ片90に対して非接触である。はんだ付け時において、半導体素子30は、溶融はんだに浮いている。はんだ80は、半導体素子30の凸先端、つまり素子中心と、ヒートシンク40との間のはんだ厚が最低膜厚を確保できるように、供給されている。図13は、ヒートシンク40に対する半導体素子30の配置に傾きのない理想的な状態を示している。

<Summary of Third Embodiment>

FIG. 13 is a cross-sectional view taken along line XIII-XIII of FIG. 12 and shows the connection structure between the

図14は、半導体素子30が傾いて配置されたときの断面図である。図14に示すように、下に凸の反りを生じた半導体素子30が傾いて配置された場合、半導体素子30は、複数のワイヤ片90の一部に接触する。ワイヤ片90が半導体素子30を支持することで、はんだ80の最低膜厚が確保される。ワイヤ片90は、反りが生じた半導体素子30が傾いて配置された場合に、はんだ80の最低膜厚を確保できる高さを有している。ワイヤ片90を外周領域80bの少なくとも四隅に配置しているため、半導体素子30がいずれの方向に傾いても、ワイヤ片90の少なくともひとつにより支持することができる。以上より、本実施形態の半導体装置10によれば、半導体素子30に下に凸の反りが生じても、はんだ80の膜厚を保証することができる。これにより、信頼性(接続信頼性)の高い半導体装置10を提供することができる。

FIG. 14 is a cross-sectional view when the

半導体素子30が下に凸の反りを生じる電極構成は、上記した例に限定されない。

The electrode configuration that causes the

外周領域80bにおいて、四隅とともに、四隅以外の部分にもワイヤ片90を配置してもよい。すなわち、素子中心30cを取り囲むように5つ以上のワイヤ片90bを配置してもよい。

In the outer

(第4実施形態)

この実施形態は、先行する実施形態を基礎的形態とする変形例であり、先行実施形態の記載を援用できる。

(Fourth embodiment)

This embodiment is a modification based on the preceding embodiment, and the description of the preceding embodiment can be used.

ワイヤ片90の延設方向は、第1対向面において特に制限されない。任意の方向に延設することができる。好ましくは、図15に示す所定の方向に、ワイヤ片90を延設するのとよい。図15は、本実施形態の半導体装置10において、半導体素子とヒートシンクとの接続部周辺を示す平面図である。図15は、図7に対応している。図15では、ワイヤ片90の明確化のため、半導体素子30を一点鎖線で示し、ワイヤ片90を実線で示している。半導体装置10の構成は、たとえば第1実施形態と同様である。図15に示す構成は、上アーム6H側と下アーム6L側とで同じである。

The extending direction of the

ワイヤ片90は、ヒートシンク40の実装面40aに固定されている。ワイヤ片90の個数および配置は、第1実施形態(図7参照)と同様である。本実施形態では、ワイヤ片90が、平面視において素子中心30cに向けて延びている。すなわち、ワイヤ片90の延設方向(長手方向)が、該ワイヤ片90と素子中心30cとを結ぶ仮想線に略平行である。ワイヤ片90は、この仮想線に沿って延びている。ワイヤ片90のうち、はんだ80の中央領域80aに配置された3つのワイヤ片90aは、いずれも素子中心30cに向けて延びている。はんだ80の外周領域80bに配置された4つのワイヤ片90bは、いずれも素子中心30cに向けて延びている。

The

<第4実施形態のまとめ>

本実施形態によれば、ワイヤ片90が素子中心30cに向けて延びているため、塗布した溶融はんだが濡れ拡がる際に、ワイヤ片90がその流れを阻害し難い。これにより、はんだ80にボイドが生じたり、対向面間に未充填部分が生じるのを抑制することができる。なお、複数のワイヤ片90の少なくともひとつを上記した延設方向とすることで、少なからず効果を奏することができる。本実施形態では、はんだ80に配置されたすべてのワイヤ片90が、素子中心30cに向けて延びている。これにより、上記した効果を高め、ひいては接続信頼性を高めることができる。

<Summary of the fourth embodiment>

According to this embodiment, since the

上記した関係を、第1実施形態の構成に適用する例を示したが、これに限定されない。たとえば、はんだ80に配置されるワイヤ片90の個数や配置が、第1実施形態とは異なる構成にも適用することができる。たとえば図16に示す変形例のように、第3実施形態(図12参照)の構成に適用してもよい。はんだ80の外周領域80bに配置されたワイヤ片90は、素子中心30cに向けて延びている。よって、第3実施形態に記載した効果を奏しつつ、接続信頼性を高めることができる。なお、複数のワイヤ片90の少なくともひとつを上記した延設方向とすることで、少なからず効果を奏することができる。図16では、外周領域80bに配置されたすべてのワイヤ片90が、素子中心30cに向けて延びている。よって、接続信頼性をより高めることができる。

Although an example in which the relationship described above is applied to the configuration of the first embodiment has been shown, the present invention is not limited to this. For example, the number and arrangement of the

また、延設方向の制御は、はんだ80内のワイヤ片90に限定されない。ワイヤ片90が配置されるはんだであれば適用が可能である。たとえば、はんだ81にワイヤ片90を配置する場合、このワイヤ片90に適用してもよい。はんだ82にワイヤ片90を配置する場合、このワイヤ片90に適用してもよい。また、上記した延設方向を、上アーム6H側および下アーム6L側の一方のみで満たすようにしてもよい。

Also, control of the extension direction is not limited to the

また、はんだ歪を考慮すると、延設長さを以下のように設定するとよい。平面視において、ワイヤ片90の延設長さが所定長さ以下では、はんだ80の端部(外周端)においてはんだ歪が最大となる。一方、延設長さが所定長さを超えると、ワイヤ片90の端部においてはんだ歪が最大となる。延設長さが長くなるとワイヤ片端部のはんだ歪が増加し、所定長さを超えるとワイヤ片端部とはんだ端部とのはんだ歪の大小関係が逆転する。よって、ワイヤ片90の端部のはんだ歪が、はんだ80の端部のはんだ歪を超えない範囲で、延設長さを設定するのが好ましい。たとえばワイヤ片90を形成するアルミニウム系のボンディングワイヤの直径80μmに対し、ワイヤ片90の長さを350μm以下にするとよい。具体的には、200~350μmの範囲内で設定するとよい。

Considering solder distortion, the extension length should be set as follows. In a plan view, when the extension length of the

(第5実施形態)

この実施形態は、先行する実施形態を基礎的形態とする変形例であり、先行実施形態の記載を援用できる。

(Fifth embodiment)

This embodiment is a modification based on the preceding embodiment, and the description of the preceding embodiment can be used.

図17~図19に示すように、ワイヤ片90を、表面電極と表側配線部材とを接合するはんだ81に配置してもよい。その際、図17~図19に示す位置にワイヤ片90を配置するとよい。図17は、本実施形態の半導体装置10において、はんだ81に配置されたワイヤ片90と半導体素子30との位置関係を示している。図18は、ターミナル55におけるワイヤ片90の配置を示している。図19は、図17のXIX-XIX線に沿う断面図である。図19では、便宜上、ゲート配線34を省略して図示している。本実施形態の半導体装置10の構成は、たとえば第1実施形態と同様である。はんだ81に配置されたワイヤ片90の構成は、上アーム6H側と下アーム6L側とで同じである。

As shown in FIGS. 17-19, a piece of

複数のワイヤ片90は、半導体素子30のエミッタ電極31とターミナル55の第1端面55aとの間のはんだ接合部に設けられている。複数のワイヤ片90は、そのすべてがターミナル55の第1端面55aに固定(接合)されており、半導体素子30のエミッタ電極31上、すなわち表面には固定されていない。ターミナル55の第1端面55aが第1対向面に相当し、半導体素子30の表面が第2対向面に相当する。第1端面55aには、複数のワイヤ片90が固定されている。第1端面55aに固定されたすべてのワイヤ片90が、はんだ81内に配置されている。

A plurality of

半導体素子30は、上記したようにゲートパッド33gを有している。半導体素子30は、表面側に形成され、ゲートパッド33gに連なるゲート配線34と、表面に形成された保護膜の一部分であり、ゲート配線34を保護するゲート配線保護部35を有している。エミッタ電極31はX方向において二分割され、隣り合うエミッタ電極31の間に、アルミニウム等を材料としてゲート配線34が形成されている。

The

半導体素子30の表面には、ポリイミドなどを材料とする保護膜が形成されており、エミッタ電極31およびパッド33は保護膜から露出している。ゲート配線保護部35は、この保護膜の一部分であり、ゲート配線34を覆う部分である。図17では、ゲート配線保護部35のうち、平面視においてターミナル55と重なる部分を、破線の領域として示している。図18では、位置関係を示すため、ターミナル55の第1端面55aに、ゲート配線保護部35を一点鎖線の領域として示している。

A protective film made of polyimide or the like is formed on the surface of the

ワイヤ片90は、平面視においてゲート配線保護部35と重ならない位置に配置されている。図17および図18に示すように、第1端面55aの中心付近であって、ゲート配線保護部35と重ならない位置に、ひとつのワイヤ片90が固定されている。また、平面略矩形状をなす第1端面55aの四隅のそれぞれに、ワイヤ片90が固定されている。このように、5つのワイヤ片90が第1端面55aに固定されている。

The

<第5実施形態のまとめ>

本実施形態では、はんだ81内に複数のワイヤ片90を配置している。これにより、はんだ81の最低膜厚を確保することができる。

<Summary of the fifth embodiment>

In this embodiment, a plurality of

また、はんだ81内のワイヤ片90のすべてを、平面視においてゲート配線保護部35と重ならない位置に設けている。これにより、半導体装置10を形成する際に、ワイヤ片90がゲート配線保護部35に接触して保護膜を傷つけるのを抑制することができる。よって、保護膜の傷ついた部分からはんだ81がゲート配線34側に侵入し、ゲート電極とエミッタ電極31とのショート、すなわちゲートリーク不良が生じるのを抑制することができる。

Moreover, all of the

エミッタ電極31はコレクタ電極32よりも面積が小さい。換言すれば、はんだ81の接合部は、平面視においてはんだ80の接合部よりも小さい。よって、半導体素子30に上に凸の反りが生じても、第1端面55aの中心付近に設けたひとつのワイヤ片90により、半導体素子30を支持することができる。これにより、はんだ81の最低膜厚を確保することができる。また、半導体素子30に下に凸の反りが生じても、四隅に配置されたワイヤ片90により半導体素子30を支持することができる。これにより、はんだ81の最低膜厚を確保することができる。以上より、信頼性の高い半導体装置10を提供することができる。

The

ワイヤ片90を、ターミナル55の第1端面55aに固定する例を示したがこれに限定されない。ワイヤ片90を、半導体素子30のエミッタ電極31に固定してもよい。すなわち、半導体素子30の表面を第1対向面としてもよい。しかしながら、ワイヤ片90をターミナル55(表側配線部材)に固定する構造のほうが、ワイヤ片90を接合する際の影響が小さいため、好ましい。

Although an example in which the

はんだ81におけるワイヤ片90の個数および配置は、上記した例に限定されない。平面視においてゲート配線保護部35と重ならない条件を満たす範囲で配置できる。たとえば第1端面55aの中心付近に複数のワイヤ片90を配置してもよい。また、第1端面55aの外周端近傍において、四隅とともに、四隅以外の部分にもワイヤ片90を配置してもよい。また、上記した配置を、上アーム6H側および下アーム6L側の一方のみで満たすようにしてもよい。

The number and arrangement of

上記した関係を、第1実施形態の構成に適用する例を示したが、これに限定されない。はんだ81に配置されるワイヤ片90に、第2実施形態の構成、第3実施形態の構成、および第4実施形態の構成の少なくともひとつを組み合わせてもよい。たとえば、はんだ80に配置されるワイヤ片90の個数が、第1実施形態とは異なる個数の構成にも適用することができる。たとえば、はんだ80、81に配置されるワイヤ片90の数を同数としてもよい。

Although an example in which the relationship described above is applied to the configuration of the first embodiment has been shown, the present invention is not limited to this. At least one of the configuration of the second embodiment, the configuration of the third embodiment, and the configuration of the fourth embodiment may be combined with the

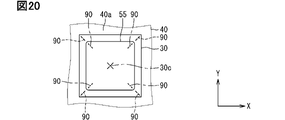

図20に示す変形例では、はんだ80における外周領域80bの四隅にワイヤ片90が配置され、はんだ81における四隅にワイヤ片90が配置されている。つまり、はんだ80、81にそれぞれ4つのワイヤ片90が配置されている。半導体素子30に下に凸の反りが生じても、はんだ81に配置されたワイヤ片90により半導体素子30を支持することができる。これにより、はんだ81の最低膜厚を確保することができる。はんだ81におけるワイヤ片90は、ゲート配線保護部35と重ならない位置に配置されている。はんだ80、81に配置された各ワイヤ片90は、図16に示した構成同様、素子中心30cに向けて延びている。図20は、ターミナル55を第2端面側から見た平面図である。図20では、はんだ80に配置されるワイヤ片90を破線、はんだ81に配置されるワイヤ片90を一点鎖線で示している。

In the modification shown in FIG. 20 ,

また、はんだ80にワイヤ片90を配置せず、上記したようにはんだ81にワイヤ片90を配置してもよい。本実施形態の構成は、裏側配線部材、すなわちヒートシンク40を備えない構成にも適用が可能である。

Further, the

半導体装置10がターミナル55を備える例を示したが、これに限定されない。ターミナル55を備えない構成においても適用が可能である。たとえば、エミッタ電極31とヒートシンク50の実装面50aとのはんだ接合部において、ヒートシンク50の実装面50aにワイヤ片90を固定してもよい。

Although an example in which the

(第6実施形態)

この実施形態は、先行する実施形態を基礎的形態とする変形例であり、先行実施形態の記載を援用できる。

(Sixth embodiment)

This embodiment is a modification based on the preceding embodiment, and the description of the preceding embodiment can be used.

はんだ80、81の両方にワイヤ片90を配置する場合、ワイヤ片90の配置は特に制限されない。図21に示すようにワイヤ片90を配置してもよい。図21は、本実施形態の半導体装置10において、ターミナルを第2端面側から見た平面図である。図21は、図7に対応している。半導体装置10の構成は、たとえば第1実施形態と同様である。図21に示す構成は、上アーム6H側と下アーム6L側とで同じである。

When the

半導体装置10は、はんだ80に配置された複数のワイヤ片90と、はんだ81に配置された複数のワイヤ片90を備えている。以下では、はんだ80に配置されたワイヤ片90をワイヤ片900、はんだ81に配置されたワイヤ片90をワイヤ片901と示すことがある。図21では、ワイヤ片900を破線、ワイヤ片901を一点鎖線で示している。

The

ワイヤ片900は、第1実施形態に記載のワイヤ片90(図7参照)と同様の配置となっている。ワイヤ片900は、たとえばヒートシンク40の実装面40aに固定されている。はんだ80の中央領域80aには、素子中心30cを取り囲むように3つのワイヤ片900が配置されている。外周領域80bには、半導体素子30の四隅のそれぞれに対応して4つのワイヤ片900が配置されている。

The

ワイヤ片901は、第5実施形態に記載のワイヤ片90(図17参照)と同様の配置となっている。ワイヤ片901は、たとえばターミナル55の第1端面55aに固定されている。第1端面55aの中心付近にひとつのワイヤ片901が配置されている。第1端面55aの四隅にワイヤ片901が配置されている。図21に示すように、ワイヤ片900とワイヤ片901とは、平面視において互いに重ならない位置に配置されている。

The

<第6実施形態のまとめ>

図22は、比較例と本例(本実施形態)との違いを示す模式的な図である。比較例において、本実施形態(本例)の要素と同一又は関連する要素について、本実施形態の符号の末尾にrを付け加えて示している。図22では、便宜上、半導体素子の主電極を省略して図示している。

<Summary of the sixth embodiment>

FIG. 22 is a schematic diagram showing the difference between the comparative example and this example (this embodiment). In the comparative example, elements that are the same as or related to elements of this embodiment (this example) are indicated by adding r to the end of the reference numerals of this embodiment. For the sake of convenience, FIG. 22 omits the main electrodes of the semiconductor elements.

ワイヤ片900r、901rは、上記したようにアルミニウム系の材料を用いて形成されており、はんだ80r、81rに対する濡れ性が、半導体素子30rの図示しない主電極、ヒートシンク40r、およびターミナル55rよりも低い。このため、ワイヤ片900r、901rとはんだ80r、81rとの間に、空隙86rが形成される。空隙86rは熱伝導を妨げる。比較例のように、平面視においてワイヤ片900r、901rが重なると、空隙86rも重なる。半導体素子30rに対してZ方向の両側に空隙86rが存在するため、空隙86r(ワイヤ片900r、901r)と重なる半導体素子30rの部分からZ方向へ熱を逃がしにくい。よって、熱抵抗が増加する。

The

本実施形態(本例)でも、比較例同様、ワイヤ片900とはんだ80との間、ワイヤ片901とはんだ81との間に、空隙86がそれぞれ形成される。しかしながら、ワイヤ片900、901が、平面視において互いに重ならない位置に配置されているため、はんだ80、81中の空隙86が、平面視において互いに重ならない、若しくは、重なってもごく一部である。よって、半導体素子30の熱をZ方向における少なくとも一方へ逃がすことができる。これにより、比較例に較べて熱抵抗を小さくし、放熱性を高めることができる。なお、他の実施形態では、空隙86を省略して図示している。

In this embodiment (this example) as well,

本実施形態では、ワイヤ片900が、第1実施形態と同様の構成となっている。このため、本実施形態に記載の効果に加え、第1実施形態に記載の効果も奏することができる。また、ワイヤ片901が、第5実施形態と同様の構成配置となっている。このため、本実施形態に記載の効果に加え、第5実施形態に記載の効果も奏することができる。しかしながら、ワイヤ片900、901の個数、配置は、平面視においてワイヤ片900、901が互いに重ならない条件を満たす範囲内で選択が可能である。すなわち、個数および配置は、上記した例に限定されない。

In this embodiment, the

たとえば、ワイヤ片900のみ第1実施形態同様の構成とし、ワイヤ片901は第5実施形態とは異なる構成としてもよい。ワイヤ片901のみ第4実施形態同様の構成とし、ワイヤ片900は第1実施形態とは異なる構成としてもよい。また、ワイヤ片900、901を同数としてもよい。図20に示した構成では、はんだ80、81のワイヤ片90が同数である。ワイヤ片900に相当するはんだ80側のワイヤ片90と、ワイヤ片901に相当するはんだ81側のワイヤ片90とが、平面視において互いに重ならない位置に配置されている。

For example, only the

ワイヤ片900をヒートシンク40に固定する例を示したが、半導体素子30の裏面(コレクタ電極32)に固定してもよい。ワイヤ片901をターミナル55に固定する例を示したが、半導体素子30の表面(エミッタ電極31)に固定してもよい。ワイヤ片900をヒートシンク40に固定し、ワイヤ片901を半導体素子30に固定してもよい。また、ワイヤ片900を半導体素子30に固定し、ワイヤ片901をターミナル55に固定してもよい。また、ターミナル55を備えない構成としてもよい。この場合、ワイヤ片901は、ヒートシンク50と半導体素子30(エミッタ電極31)とのはんだ接合部に設けられる。

Although an example in which the

本実施形態の構成と、第2実施形態の構成、第3実施形態の構成、および第4実施形態の構成の少なくともひとつを組み合わせてもよい。ワイヤ片900、901の少なくとも一方に、第2実施形態の構成を組み合わせてもよい。ワイヤ片900、901の少なくとも一方に、第3実施形態の構成を組み合わせてもよい。ワイヤ片900、901の少なくとも一方に、第4実施形態の構成を組み合わせてもよい。また、本実施形態の構成を、上アーム6H側および下アーム6L側の一方のみで満たすようにしてもよい。

At least one of the configuration of this embodiment, the configuration of the second embodiment, the configuration of the third embodiment, and the configuration of the fourth embodiment may be combined. At least one of the

(第7実施形態)

この実施形態は、先行する実施形態を基礎的形態とする変形例であり、先行実施形態の記載を援用できる。

(Seventh embodiment)

This embodiment is a modification based on the preceding embodiment, and the description of the preceding embodiment can be used.

図23に示すように、ワイヤ片90を、はんだ82に配置してもよい。その際、各はんだ80、81、82のワイヤ片90を、図24に示すように配置するとよい。図23は、本実施形態の半導体装置10において、ヒートシンク40、50間の積層体を示す模式的な断面図である。図24は、各はんだ80、81、82におけるワイヤ片90の好ましい配置の一例を示す平面図である。図24は、図21に対応している。図24では、ワイヤ片900を破線、ワイヤ片901を一点鎖線で示している。本実施形態の半導体装置10の構成は、たとえば第1実施形態と同様である。図23および図24に示す構成は、上アーム6H側と下アーム6L側とでほぼ同じである。

A piece of

図23に示すように、はんだ80、81、82のそれぞれに複数のワイヤ片90が配置されている。以下では、はんだ80に配置されたワイヤ片90をワイヤ片900、はんだ81に配置されたワイヤ片90をワイヤ片901、はんだ82に配置されたワイヤ片90をワイヤ片902と示すことがある。ワイヤ片90の個数は、はんだ80、81、82において互いに異なっている。ワイヤ片900が最も多く、ワイヤ片902が最も少ない。ワイヤ片901は、ワイヤ片900よりも少なく、ワイヤ片902よりも多い。

As shown in FIG. 23, a plurality of

図23では、ワイヤ片900がヒートシンク40に固定されている。また、ワイヤ片901がターミナル55の第1端面55aに固定され、ワイヤ片902が第2端面55bに固定されている。

In FIG. 23, a piece of

図24に示すように、ワイヤ片900は、第1実施形態に記載のワイヤ片90(図7参照)と同様の配置となっている。ワイヤ片900は、ヒートシンク40の実装面40aに固定されている。はんだ80の中央領域80aには、素子中心30cを取り囲むように3つのワイヤ片900が配置されている。外周領域80bには、半導体素子30の四隅のそれぞれに対応して4つのワイヤ片900が配置されている。

As shown in FIG. 24, the

ワイヤ片901は、第5実施形態に記載のワイヤ片90(図17参照)と同様の配置となっている。ワイヤ片901は、ターミナル55の第1端面55aに固定されている。第1端面55aの中心付近にひとつのワイヤ片901が配置されている。第1端面55aの四隅にワイヤ片901が配置されている。

The

ワイヤ片902は、ターミナル55の第2端面55bに固定されている。第2端面55bには、3つのワイヤ片902が固定されている。複数のワイヤ片902は、素子中心30cを取り囲むように配置されている。図24に示すように、ワイヤ片900、901、902は、平面視において互いに重ならない位置に配置されている。なお、ターミナル55が第1配線部材に相当し、ヒートシンク50が第2配線部材に相当する。はんだ81が、表側接合部材である第1接合部材に相当し、はんだ82が第2接合部材に相当する。

<第7実施形態のまとめ>

本実施形態では、はんだ82に複数のワイヤ片90が配置されている。これにより、はんだ82の最低膜厚を確保することができる。また、はんだ80、81、82のそれぞれに、複数のワイヤ片90が配置されている。これにより、半導体素子30からZ方向両側のヒートシンク40、50までの電気伝導経路、熱伝導経路を構成するはんだ80、81、82のすべてについて、最低膜厚を確保することができる。

<Summary of the seventh embodiment>

In this embodiment, a plurality of

本実施形態では、はんだ80、81、82ごとにワイヤ片90の配置数が異なっている。電極面積の大きいコレクタ電極32側のはんだ80に、最も多いワイヤ片90(ワイヤ片900)が配置されている。また、コレクタ電極32よりも電極面積が小さいエミッタ電極31側において、半導体素子30に近い側のはんだ81に、ワイヤ片900よりも少ない数のワイヤ片90(ワイヤ片901)が配置されている。また、半導体素子30に対して遠い側のはんだ82には、最も少ないワイヤ片90(ワイヤ片902)が配置されている。具体的には、半導体装置10が、ワイヤ片90として、7つのワイヤ片900と、5つのワイヤ片901と、3つのワイヤ片902を備えている。

In this embodiment, the number of

はんだ80、81は、半導体素子30の反りの影響がある。コレクタ電極32に接続されることで平面視の面積が最も大きいはんだ80に、最も多いワイヤ片90を配置するため、はんだ80の最低膜厚を確保することができる。ワイヤ片900の配置を第1実施形態と同様とすることで、半導体素子30の反りに対しても最低膜厚を確保することができる。はんだ81は、コレクタ電極32よりも面積の小さいエミッタ電極31と、金属ブロック体であるターミナル55とを接続している。中心付近にひとつのワイヤ片90を設けることで、半導体素子30の上に凸の反りに対応することができる。はんだ80よりも少ないワイヤ片90の配置にて、はんだ81の最低膜厚を確保することができる。ワイヤ片901の配置を第5実施形態と同様とすることで、半導体素子30の反りに対しても最低膜厚を確保することができる。

はんだ82は、ターミナル55とヒートシンク50とを接続している。ターミナル55およびヒートシンク50には、半導体素子30のような反りは生じない。また、半導体素子30との間にターミナル55が存在するため、半導体素子30の反りの影響を受けない。よって、最も少ないワイヤ片90にて、はんだ82の最低膜厚を確保することができる。ワイヤ片901、902の数をワイヤ片900よりも少なくすることで、ワイヤ片900と同数の構成に較べて、はんだ81、82中の空隙86を低減することができる。よって、最低膜厚を確保しつつ、放熱性を高めることができる。さらに、ワイヤ片902の数をワイヤ片901よりも少なくするため、ワイヤ片901と同数の構成に較べて、放熱性を高めることができる。また、半導体装置10全体のワイヤ片90の個数を低減することもできる。

また、ワイヤ片900、901、902は、平面視において互いに重ならない位置に配置されている。Z方向において空隙86が互いに重ならない、若しくは、重なってもごく一部であるため、放熱性を高めることができる。

Also, the

はんだ80、81、82においてワイヤ片90の数を互いに異ならせる場合、その個数は上記した例に限定されない。ワイヤ片900の数>ワイヤ片901の数>ワイヤ片902の数、の関係を満たせばよい。なお、ワイヤ片900の数>ワイヤ片901の数=ワイヤ片902の数としてもよい。ワイヤ片900の数=ワイヤ片901の数>ワイヤ片902の数としてもよい。はんだ80、81、82の一部のワイヤ片90を、残りのワイヤ片90と異ならせることにより、効果は弱まるが、放熱性の向上およびワイヤ片90の低減を図ることができる。

When the

各はんだ80、81、82において最低膜厚を確保するのであれば、ワイヤ片90の数はより自由に設定できる。はんだ80、81、82においてワイヤ片90を同数としてもよい。それぞれに複数、好ましくは3つ以上のワイヤ片90を配置することで、はんだ厚を確保しやすくなる。

The number of

また、本実施形態の構成を、上アーム6H側および下アーム6L側の一方のみで満たすようにしてもよい。ワイヤ片90を、はんだ80、81、82に配置する例を示したが、さらにはんだ83、84の少なくとも一方に配置してもよい。

Also, the configuration of this embodiment may be satisfied with only one of the

(第8実施形態)

この実施形態は、先行する実施形態を基礎的形態とする変形例であり、先行実施形態の記載を援用できる。

(Eighth embodiment)

This embodiment is a modification based on the preceding embodiment, and the description of the preceding embodiment can be used.

ターミナル55の形状は特に限定されない。好ましくは、ワイヤ片90を、図25に本例として示す形状にするとよい。図25は、ターミナルについて比較例と本例(本実施形態)との違いを示す模式的な図である。比較例において、本実施形態(本例)の要素と同一又は関連する要素について、本実施形態の符号の末尾にrを付け加えて示している。比較例、本例ともに紙面上方が側面図、A面視の平面図である。本実施形態の半導体装置10は、たとえば第1実施形態と同様である。図25に示す構成は、上アーム6H側と下アーム6L側とでほぼ同じである。

The shape of the terminal 55 is not particularly limited. Preferably, the

ターミナルは、プレス加工により金属板から打ち抜いて形成される。ワイヤ片は、ターミナルの端面をカメラで撮像して端面の角部を認識し、角部を位置基準として所定位置にボンディングワイヤを超音波接合することで形成される。比較例のターミナル55rは、Z方向における一方の端面の角に、打ち抜きによるR部550rを有する。このため、R部550r側の端面にワイヤ片90rを形成する際、R部550rがない側の端面に較べて、ワイヤ片90rの形成位置の精度が低くなる虞がある。

The terminal is formed by punching out from a metal plate by press working. The wire piece is formed by imaging the end face of the terminal with a camera, recognizing the corner of the end face, and ultrasonically bonding the bonding wire to a predetermined position using the corner as a position reference. A terminal 55r of the comparative example has a punched

本実施形態(本例)でも、打ち抜いた状態のターミナル55は、比較例同様、一方の端面の角に図示しないR部を有する。しかしながら、打ち抜き後に、R部の面取り、たとえばC面取りを行う。C面取りとは、面取り角度が略45度の面取りである。ターミナル55は、面取り部550を有する。

In this embodiment (this example) as well, the punched

<第8実施形態のまとめ>

上記したように、本実施形態のターミナル55は、面取り部550を有している。このため、打ち抜き時にR部が形成される側の端面にワイヤ片90を形成する際、撮像により角部を精度よく認識することができる。よって、ワイヤ片90を位置精度よく形成することができる。

<Summary of the eighth embodiment>

As described above, the

本実施形態の構成は、ターミナル55を備える構成において適用が可能である。先行実施形態のそれぞれとの組み合わせが可能である。また、ワイヤ片90の接続対象は、ターミナル55に限定されない。金属板を打ち抜いて形成され、打ち抜き時にR部が形成される部材について適用が可能である。打ち抜き後にR部を面取りすることで、打ち抜き時にR部が形成される側の面に、ワイヤ片90を位置精度よく形成することができる。

The configuration of this embodiment can be applied to a

(第9実施形態)

この実施形態は、先行する実施形態を基礎的形態とする変形例であり、先行実施形態の記載を援用できる。この実施形態では、ワイヤ片90の構造および製造方法に特徴がある。

(Ninth embodiment)

This embodiment is a modification based on the preceding embodiment, and the description of the preceding embodiment can be used. This embodiment is characterized by the structure and manufacturing method of the

ワイヤ片90は、上記したように、アルミニウム系のボンディングワイヤを超音波接合し、1stボンドを行った時点でワイヤカットすることで形成される。このようなワイヤ片90として、好ましい形態のひとつを、図26~図29に示す。

As described above, the

図26は、本実施形態の半導体装置10において、半導体素子30とヒートシンク40との接続構造を示している。図27は、図26のXXVII-XXVII線に沿う断面図である。図28は、図26および図27に適用しているワイヤ片90を示す斜視図である。図29は、ワイヤ片90の別例を示している。図26および図27では、ワイヤ片90の数を3つにしている。図26、図27、および図28では、便宜上、主電極の図示を省略している。本実施形態の半導体装置10は、たとえば第1実施形態と同様である。図26~図28に示す構成は、上アーム6H側と下アーム6L側とでほぼ同じである。

FIG. 26 shows a connection structure between the

半導体素子30は、図示しないエミッタ電極31が形成された表面30aと、図示しないコレクタ電極32が形成された裏面30bを有している。コレクタ電極32が裏面30bをなしている。図21および図22に示すように、はんだ80に複数のワイヤ片90が配置されている。ワイヤ片90は、ヒートシンク40の実装面40aに接合(固定)されている。実装面40aが、配線部材における固定面に相当する。ワイヤ片90は、実装面40aから裏面30bに向けて突起している。ワイヤ片90は、ヒートシンク40に保持されている。このため、ヒートシンク40は、保持体と称されることがある。ワイヤ片90は、固定部91と、平坦部92と、非固定部93を有している。固定部91は、ワイヤ片90のヒートシンク40と対向する側において、ヒートシンク40との固定部分(接合箇所)である。

The

平坦部92は、ワイヤ片90において、半導体素子30の裏面30bと対向する側に形成され、ヒートシンクの実装面40aと略平行な部分である。非固定部93は、ワイヤ片90のヒートシンク40と対向する側において、固定部91に連なり、ヒートシンク40に固定されていない部分である。非固定部93は、Z方向において実装面40aから離れている。非固定部93は、固定部91を基準として浮いている。ワイヤ片90は、Z方向に弾性変形可能に設けられている。非固定部93と実装面40aとの隙間には、はんだ80が入り込んでいる。ワイヤ片90は、Z方向においてヒートシンク40側に固定部91および非固定部93を有し、固定部91および非固定部93とは反対側に平坦部92を有している。

The

ワイヤ片90は、X方向に延設されている。図27および図28に示すワイヤ片90は、延設方向の両端に、平坦部92および非固定部93を有している。平坦部92は、平面視において非固定部93と重なる位置に設けられている。実装面40aから両端の平坦部92までの高さは、互いに略等しい。ワイヤ片90は、ZX平面において略U字状、若しくは、略C字状をなしている。両端の平坦部92は、半導体素子30の裏面30bにそれぞれ接触している。

The

図29は、ワイヤ片90の別例を示している。このワイヤ片90は、両端ではなく、延設方向の一端にのみ平坦部92を有している。非固定部93は、延設方向の両端に設けられている。ワイヤ片90において、実装面40aから両端の上部までの高さが異なっている。平坦部92は、実装面40aからの突起高さが高い側の端部に形成されている。ワイヤ片90は、ZX平面において略J字状をなしている。平坦部92、図示しない素子中心30cに対して遠い側の端部に形成されている。

FIG. 29 shows another example of

<製造方法>

次に、半導体装置10の製造方法、特に半導体素子30とヒートシンク40との接続体の製造方法について説明する。ここでは、図29に示したワイヤ片90の例を示す。

<Manufacturing method>

Next, a method for manufacturing the

先ず、図30に示すように、ヒートシンク40の実装面40aにワイヤ片90を形成する。図示しないツールからの超音波により、ボンディングワイヤをヒートシンク40に接合し、固定部91を形成する。この固定部91は、1stボンド部である。そして、超音波の印加完了後に、固定部91に対して延設方向前後に非固定部93が残るようにボンディングワイヤを切断する。このように、2ndボンド部を形成せずに、ボンディングワイヤを切断する。1stボンド側のみを用いてワイヤ片90を形成するため、2点の接合体、すなわち1stボンド部と2ndボンド部を有する構造に較べて、形成時間を短縮することができる。また、ワイヤ片90の体格を小型化、たとえば延設長さを短くすることができる。よって、上記したはんだ歪の観点でも有利である。

First, as shown in FIG. 30, a

なお、ボンディングワイヤは、上記したようにアルミニウム、アルミニウム合金を材料とするワイヤであり、半導体素子30のサイズやはんだ80の厚みに応じて選択することができる。ここでは、直径80μmのボンディングワイヤを用い、実装面40aからの突起高さが110μm、延設長さが350μmのワイヤ片90を形成した。

The bonding wires are wires made of aluminum or aluminum alloy as described above, and can be selected according to the size of the

次に、図31および図32に示すように、ワイヤ片90に平坦部92を形成する。つまり、レベリング加工を行う。具体的には、実装面40aと平行な面(以下、接触面と示す)を有する治具98を用いて、図31の白抜き矢印で示すようにワイヤ片90に荷重をかける。たとえばプレス機に治具98を取り付け、ワイヤ片90に荷重をかける。接触面と実装面40aとの平行状態を維持して治具98をワイヤ片90に押し付ける。治具98は、略J字状をなすワイヤ片90の一端に接触する。また、ワイヤ片90が弾性変形し、非固定部93の少なくとも一部が実装面40aに接触する。さらに治具98を押し込むと、ワイヤ片90が塑性変形し、平坦部92が形成される。ワイヤ片90は、押し込み量に応じて塑性変形する。平坦部92は、治具98と最初に接触する一端側に平坦部92が形成される。

Next, as shown in FIGS. 31 and 32, a

平坦部92の形成後、荷重の開放によりワイヤ片90が弾性変形状態から復元し、接触していた非固定部93の部分が実装面40aから離れる。これにより、図32に示すように、平面視において非固定部93と重なる位置に平坦部92を備えたワイヤ片90が得られる。平坦化により、ワイヤ片90の高さは図30の状態に対して低くなる。ここでは、75μm程度とした。上記した工程により、複数のワイヤ片90を実装面40a上に形成する。半導体素子30の傾きを抑制するためには、複数、より好ましくは3つ以上のワイヤ片90を形成するとよい。さらに好ましくは、先行実施形態に記載の構成とするとよい。

After the

次に、図33に示すように、溶融はんだ80Sを塗布する。ヒートシンク40の実装面40a上に、溶融はんだ80Sを塗布する。ワイヤ片90は、塗布された溶融はんだ80Sにより覆われる。溶融はんだ80Sに対して半導体素子30を配置する必要があるため、必要に応じてヒートシンク40を加熱(加温)する。ここでは、転写法により、溶融はんだ80Sを塗布した。

Next, as shown in FIG. 33,

次に、図34に示すように、半導体素子30を搭載する。半導体素子30を図示しない治具にて保持し、実装面40aの上方から溶融はんだ80Sに向けて下降させる。下降により、半導体素子30の裏面30bが溶融はんだ80Sに接触し、溶融はんだ80Sを押し拡げる。所定位置まで下降すると、治具による保持状態が解除される。溶融はんだ80Sは、裏面30bおよび実装面40aを濡れ拡がる。ヒートシンク40の厚み、半導体素子30の厚みおよび反り、搭載精度のばらつきなどにより、半導体素子30はワイヤ片90に押し当てられることがある。

Next, as shown in FIG. 34, the

そして、図示しない冷却を経て、図29に示す接続構造体を得ることができる。なお、図27および図28に示したワイヤ片90についても同様の方法にて形成することができる。具体的には、固定部91の形成後、両端の高さがほぼ等しくなるようにボンディングワイヤを切断してワイヤ片90を形成し、治具98にて両端に平坦部92を形成すればよい。

After cooling (not shown), the connection structure shown in FIG. 29 can be obtained. The

<第9実施形態のまとめ>

平坦部を有さないワイヤ片90、すなわち図30に示した状態のワイヤ片90を用いると、半導体素子30がワイヤ片90に接触した際に、半導体素子30に応力が集中する。特に、ワイヤ片90の高さばらつきが大きいと、半導体素子30がワイヤ片90に接触する可能性が高まる。これに対し、本実施形態のワイヤ片90によれば、半導体素子30が平坦部92に接触するため、応力集中を抑制することができる。また、平坦部92を形成することで、ワイヤ片90の高さばらつきが小さくなる。これにより、はんだ80の厚みが安定し、接続信頼性を高めることができる。たとえば、温度サイクル環境下でのはんだクラック寿命を確保することができる。平坦部92を有するワイヤ片90は、ワイヤボンディング技術と簡単な押し込みで形成することができるため、コストを低減することもできる。

<Summary of the ninth embodiment>

If the

さらに、ワイヤ片90は、非固定部93を有している。これにより、ワイヤ片90は、弾性変形が可能である。よって、半導体素子30がワイヤ片90に接触しても、ワイヤ片90が弾性変化することにより、半導体素子30の応力集中を抑制することができる。特に本実施形態では、平面視において非固定部93と重なる位置に平坦部92が形成されている。これにより、半導体素子30と接触する平坦部92が、応力を逃がす方向に変形しやすい。したがって、応力集中の抑制により効果的である。

Furthermore, the

ワイヤ片90の配置は、上記した例に限定されない。他の例を、図35~図38に示す。図35~図38に示す例は、いずれも、Z方向を含む一断面に、2つのワイヤ片90を配置している。また、ワイヤ片90が半導体素子30に接触する。

The arrangement of the

図35~図37に示す例では、2つのワイヤ片90が、図29に示したワイヤ片90同様、平坦部92をそれぞれひとつのみ有している。平坦部92は、2つのワイヤ片90の並び方向(X方向)において、外側の端部にそれぞれ形成されている。図35に示すように、半導体素子30の反りが生じていない場合、いずれのワイヤ片90も、平坦部92が半導体素子30に接触する。よって、半導体素子の応力集中を抑制することができる。

In the example shown in FIGS. 35-37, two

図36に示すように、半導体素子30に上に凸の反りが生じている場合も、ワイヤ片90の平坦部92が半導体素子30にそれぞれ接触する。よって、半導体素子の応力集中を抑制することができる。一方、図37に示すように、半導体素子30に下に凸の反りが生じている場合、図中に実線矢印で示すように、ワイヤ片90の内側の端部が半導体素子30に接触してしまう。このように、反り量によっては、平坦部92が形成されていない側の端部に半導体素子30が当たる虞がある。

As shown in FIG. 36 , even when the

なお、平坦部92をワイヤ片90の端部に形成してもよい。これによれば、図37に示す反りが生じていても、内側端部に設けた平坦部92が半導体素子30に接触するため、応力集中を抑制することができる。しかしながら、同一の組み付けロット内に、上に凸の半導体素子30と下に凸の半導体素子30が混在する場合、たとえば上に凸の半導体素子30に平坦部92の位置を合わせると、下に凸の半導体素子30において応力が集中する虞がある。

Note that the

これに対し、図38に示す例では、2つのワイヤ片90が、図27および図28に示したワイヤ片90同様、両端に平坦部92を有している。よって、半導体素子30に下に凸の反りが生じている場合、内側の平坦部92が半導体素子30に接触する。図示しないが、半導体素子30に上に凸の反りが生じている場合、外側の平坦部92が半導体素子30に接触する。したがって、半導体素子30の反りがいずれの方向であっても、応力集中を抑制することができる。

On the other hand, in the example shown in FIG. 38, two

本実施形態のワイヤ片90の構成は、はんだ80に配置されたワイヤ片90に限定されない。主電極と配線部材とのはんだ接合部に設けられるワイヤ片90であれば適用が可能である。たとえば図39に示す例では、図示しないエミッタ電極31とターミナル55との間のはんだ81にワイヤ片90が配置されており、このワイヤ片90にも平坦部92が形成されている。なお、図39では、ワイヤ片90の一端のみに平坦部92を形成しているが、両端に平坦部92を形成してもよいのは言うまでもない。

The configuration of the

ターミナル55を備えず、ヒートシンク50とエミッタ電極31との間にはんだ接合部が形成される構成にも適用することができる。この場合、実装面50aに接合されたワイヤ片90が平坦部92を有せばよい。また、表側配線部材および裏側配線部材のうち、一方のみを備える構成にも適用することができる。

A configuration in which the terminal 55 is not provided and a solder joint is formed between the

本実施形態に記載のワイヤ片90の構造は、先行実施形態のワイヤ片90との組み合わせが可能である。また、本実施形態に記載のワイヤ片90の製造方法を、先行実施形態に記載のワイヤ片90の形成に適用することができる。ワイヤ片90が、非固定部93を有する例を示したが、これに限定されない。少なくとも平坦部92を有せばよい。また、平坦部92を、平面視において非固定部93と重ならない位置に設けてもよい。本実施形態は、半導体素子の主電極と配線部材との接合部に配置されるワイヤ片に適用が可能である。ワイヤ片の配置は、先行実施形態に示した配置に限定されない。

The structure of the

(第10実施形態)

この実施形態は、先行する実施形態を基礎的形態とする変形例であり、先行実施形態の記載を援用できる。本実施形態でも、ワイヤ片90の好ましい形態について示す。

(Tenth embodiment)

This embodiment is a modification based on the preceding embodiment, and the description of the preceding embodiment can be used. This embodiment also shows a preferred form of the

<ワイヤ片の大きさ>

先ず、図40~図43に基づき、ワイヤ片90の好ましい大きさについて説明する。ワイヤ片90は、半導体素子30の主電極と配線部材とを接続するはんだに配置されている。ここでのはんだとは、たとえばはんだ80、81である。

<Size of wire piece>

First, the preferred size of the

図40は、ワイヤ片90の体積と、はんだ歪との関係を示すシミュレーション結果である。横軸は、ワイヤ片90の体積(×107μm3)を示し、縦軸は、はんだ歪(任意単位)を示している。横軸は、対数軸である。図41は、本実施形態のワイヤ片90を示す図である。図41において、紙面上方が側面図、紙面下方が上面視平面図である。図42は、はんだ80に配置されるワイヤ片90の最大高さを説明するための断面図である。図43は、はんだ81に配置されるワイヤ片90の最大高さを説明するための断面図である。

FIG. 40 shows simulation results showing the relationship between the volume of the

図40に示すシミュレーション結果より、ワイヤ片90の体積が大きいと、ワイヤ片90とはんだとの線膨張係数差に基づく熱応力、つまりはんだ歪が増大し、所定の体積を超えると、クラックなどの素子ダメージが生じることが明らかとなった。はんだ歪が図40に示す破線以上の値になると、素子ダメージが生じる。よって、素子ダメージを抑制するには、ワイヤ片90の体積を、1.0×107μm3以下にすることが好ましい。本実施形態の半導体装置10において、各ワイヤ片90の体積は、1.0×107μm3以下に設定されている。

According to the simulation results shown in FIG. 40, when the

次に、上記した体積の関係を満たしつつ、レベリング加工をせずにワイヤ片90の高さばらつきを抑制できる構成について説明する。以下では、ヒートシンク40に接続されるワイヤ片90について例示する。

Next, a description will be given of a configuration capable of suppressing variations in the height of the

図41に示すように、ワイヤ片90は、延設方向において3つの部分に分けられる。ワイヤ片90は、ボンド部94と、フィード部95と、テール部96を有している。ボンド部94は、ワイヤ片90の延設方向において、フィード部95とテール部96の間に位置する。ボンド部94は、ヒートシンク40に接合された部分である。ボンド部94は、ヒートシンク40と対向する側に固定部91を有している。ボンド部94は、固定部91を含み、平面視において固定部91と重なる部分である。つまり、ボンド部94は、固定部91、および、固定部91の直上部分である。ボンド部94が、接合部に相当する。ボンド部94は、超音波接合時にツールからの荷重を受けて潰れている。このため、ボンド部94は、フィード部95およびテール部96よりも幅が広い。

As shown in FIG. 41, the

フィード部95は、ワイヤ片90の先端側において、ボンド部94に連なっている。フィード部95は、ヒートシンク40に接合されていない部分である。フィード部95は、ヒートシンク40と対向する側に、非固定部93を有している。フィード部95は、先端側において、非固定部93を含み、平面視において非固定部93と重なる部分である。つまり、フィード部95は、先端側の非固定部93、および、該非固定部93の直上部分である。フィード部95は、図示しない半導体素子30と対向する側に、平坦部92を有していない。

The

テール部96は、ワイヤ片90の後端側において、ボンド部94に連なっている。テール部96も、フィード部95同様、ヒートシンク40に接合されていない部分である。テール部96は、ヒートシンク40と対向する側に、非固定部93を有している。テール部96は、後端側において、非固定部93を含み、平面視において非固定部93と重なる部分である。つまり、テール部96は、後端側の非固定部93、および、該非固定部93の直上部分である。テール部96は、図示しない半導体素子30と対向する側に、平坦部92を有していない。

The

フィード部95およびテール部96が、非接合部に相当する。先端側とは、超音波接合する前に端部(カット端)を有している側である。後端側とは、超音波接合後にボンディングワイヤの切断で形成される端部側である。図示を省略するが、ヒートシンク40は、ボンディングワイヤを切断する際に生じるカッター痕を、ワイヤ片90の後端の直下に有している。

The

以下では、ボンド部94の延設方向の長さをLB、フィード部95の延設方向の長さをLF、テール部96の延設方向の長さをLTと示すことがある。ワイヤ片90の延設方向の長さ(全長)をLW、ボンド部94の幅をWBと示すことがある。幅WBは、ボンド部94において延設方向に直交する方向の長さである。また、ボンド部94の高さをHB、フィード部95の高さをHF、テール部96の高さをHTと示すことがある。なお、フィード部95の長さLFとテール部96の長さLTは、図41に示すように、ヒートシンク40との対向側(下面側)ではなく、半導体素子30との対向側(上面側)の長さである。高さとは、接合面である第1対向面からZ方向にもっとも離れた部分の高さである。

Hereinafter, the length in the extending direction of the

直径80μmのボンディングワイヤを用いてワイヤ片90を形成する場合、ボンド部94の長さLBは、平坦部92を備える構成と本実施形態とで互いにほぼ同じである。たとえば、長さLBは、260μm±100μmである。ワイヤ片90の体積を1.0×107μm3以下にするには、ワイヤ片90の全長LWを400μm以上、450μm以下、フィード部95およびテール部96の長さLF、LTを100μm以下にするとよい。

When the

平坦部92を設ける構成では、延設方向において平坦部92を確保するための長さが必要である。両端側に平坦部92を設けるとワイヤ片90の全長は450μmを超え、たとえば500μm程度となる。本実施形態では、平坦部92を設けないため、非接合部であるフィード部95とテール部96の長さLF、LTのそれぞれを、100μm以下と短くすることができる。このため、長さLBがばらついても、ワイヤ片90の全長LWを450μm以下にすることができる。つまり、ワイヤ片90を小型化することができる。したがって、ワイヤ片90の体積を1.0×107μm3以下にしやすい。また、長さLF、LTが短いため、高さHF、HTのばらつきを抑制することができる。

In the configuration in which the

さらに、フィード部95の高さHFおよびテール部96の高さHTを、80μm以上、100μm以下とするとよい。高さ80μmはワイヤ径と等しい。この場合、フィード部95およびテール部96は、ヒートシンク40の実装面40aに接触するものの、接合していない。

Further, it is preferable that the height HF of the

半導体素子30が下に凸の反りを生じ得る場合、図42に示すように反りが生じていない半導体素子30とヒートシンク40との対向空間の体積が最大となる。対向空間の体積が最大のとき、コレクタ電極32のほぼ全面にはんだが濡れ拡がる接合面積を確保するためのはんだ80として、もっとも多くのはんだを必要とする。この必要はんだの体積は、半導体素子30がワイヤ片90に支持された状態で最小となる。必要はんだ体積の最小値は、はんだ80の厚みが高さHF、HTに等しいときの、平面視において半導体素子30(コレクタ電極32)と重なる部分の体積から、はんだ80のひけ分を除外した値である。

When the

高さHF、HTを110μm以上にすると、はんだ80の所定供給量が、必要はんだ体積の最小値を下回る虞がある。このことは、シミュレーション結果より明らかである。この場合、コレクタ電極32の一部にしか、はんだ80が濡れ拡がらない虞がある。はんだ高さHF、HTを100μm以下にすると、はんだ80の所定供給量が、必要はんだ体積の最小値を上回る。これにより、コレクタ電極32のほぼ全面をはんだ80が濡れ拡がり、接続信頼性を確保することができる。

If the heights HF and HT are set to 110 μm or more, there is a risk that the predetermined supply amount of the

エミッタ電極31側のはんだ81についても同様である。半導体素子30が下に凸の反りを生じ得る場合、図43に示すように反りが最大(たとえば0.1μm)のときに半導体素子30とターミナル55との対向空間の体積が最大となる。対向空間の体積が最大のとき、エミッタ電極31のほぼ全面にはんだが濡れ拡がる接合面積を確保するためのはんだ81として、もっとも多くのはんだを必要とする。この必要はんだの体積は、半導体素子30がワイヤ片90に支持された状態で最小となる。

The same applies to the

高さHF、HTを110μm以上にすると、はんだ80の所定供給量が、必要はんだ体積の最小値を下回る虞がある。このことは、シミュレーション結果より明らかである。この場合、エミッタ電極31の一部にしか、はんだ81が濡れ拡がらない虞がある。はんだ高さHF、HTを100μm以下にすると、はんだ81の所定供給量が、必要はんだ体積の最小値を上回る。これにより、エミッタ電極31のほぼ全面をはんだ81を濡れ拡がり、接続信頼性を確保することができる。

If the heights HF and HT are set to 110 μm or more, there is a risk that the predetermined supply amount of the

なお、先行実施形態(図14参照)に示したように、下に凸の半導体素子30が傾いて配置された場合でも、高さHF、HTが70μm以上であれば、少なくとも四隅に配置したワイヤ片90(図12および図20参照)によって、はんだ80、81の最低膜厚を保証することができる。接続信頼性を確保できる最低膜厚は、たとえば43μmである。本実施形態では、ワイヤ直径が80μmであり、高さHF、HTの最小値が80μmである。よって、下に凸の半導体素子30が傾いて配置された場合でも、接続信頼性を確保することができる。

As shown in the preceding embodiment (see FIG. 14), even when the downwardly

上記したように長さLF、LTを短くすると、ボンド部94の長さLBに対するフィード部95またはテール部96の長さLF、LTの比(LF/LB、LT/LB)は、平坦部92を設ける構成よりも小さくなる。ワイヤ片90の体積を1.0×107μm3以下にするには、LF/LB、LT/LBを0.1以上、0.65以下にするとよい。この関係を満たすことで、ボンド部94に対してフィード部95、テール部96の長さをおさえ、ワイヤ片90を小型化することができる。また、高さHF、HTのばらつきを抑制することができる。

When the lengths LF and LT are shortened as described above, the ratios (LF/LB, LT/LB) of the lengths LF and LT of the

また、ボンド部94の長さLBに対するボンド部94の幅WBの比(WB/LB)を、0.2以上、0,7以下にするとよい。つまり、幅WBを狭くするとよい。これにより、ワイヤ片90の体積を小さくすることができる。また、高さHF,HTのばらつきを抑制することができる。

Also, the ratio of the width WB of the

より具体的には、下記寸法を満たすように、ワイヤ片90を形成するとよい。ワイヤ片90の全長LWを420μm±20μm、フィード部95の長さLFを85μm±15μm、テール部96の長さLTを70±30μmにするとよい。ボンド部94の長さLBを、260μm±100μm、ボンド部の高さHBを70μm±5μm、ボンド部94の幅WBを90μm+15μm-5μmにするとよい。フィード部95の高さHFを85μm+15μm-5μm、テール部96の高さHTを85μm±5μmにするとよい。

More specifically, it is preferable to form the

<ワイヤ片の製造方法>

次に、図44~図48に基づき、上記した体積、寸法を満たすワイヤ片90の製造方法について説明する。以下では、ワイヤ片90をヒートシンク40上に設ける例を示すが、ターミナル55上についても同様である。

<Method for manufacturing wire piece>

Next, a method of manufacturing the

図44に示すように、超音波接合装置は、ワイヤガイド100、ツール101、およびカッター102を有している。先ず、ワイヤガイド100から引き出したボンディングワイヤ99を、ヒートシンク40の実装面40aの所定位置に配置する。このとき、ツール101による接合箇所を基準として、上記した所定長さのフィード部95を確保できるように、ボンディングワイヤ99を配置する。

As shown in FIG. 44, the ultrasonic bonding apparatus has a

次いで図45に示すように、ツール101により超音波接合を行う。超音波接合により、ボンド部94を形成する。ボンディングワイヤ99は、超音波接合のパワー、ツール101による荷重によって、少なからず潰れる。これにより、ボンド部94の幅が広がる。本実施形態では、ボンド部94の幅WBが広がりすぎず、90μm+15μm-5μm、つまり85μm~105μmの範囲内に入るように、パワーおよび荷重を調整する。

Next, as shown in FIG. 45, ultrasonic bonding is performed using a

超音波接合によって、図45に矢印で示すように、フィード部95の上面側には圧縮応力が作用する。一方、フィード部95の下面側、つまりヒートシンク40側には、引張応力が作用する。これにより、フィード部95は、ヒートシンク40の実装面40aに対してはね上がる。接触していた非固定部93の部分が実装面40aから離れる。

Due to the ultrasonic bonding, a compressive stress acts on the upper surface side of the

超音波接合の終了後、図46に示すように、ツール101(超音波接合装置)を後退させる。図46に白抜き矢印で示すツール101の後退量は、カッター102の切断位置、すなわちテール部96の長さに応じて決定される。具体的には、テール部96の長さLTおよびワイヤ片90の全長がそれぞれ所定長さとなるように、後退量を決定する。

After completing the ultrasonic bonding, as shown in FIG. 46, the tool 101 (ultrasonic bonding apparatus) is retracted. 46 is determined according to the cutting position of the

次いで、図47に示すように、ワイヤカットを行う。上記した後退位置でツール101がボンディングワイヤ99を押さえた状態で、カッター102により、ボンディングワイヤ99を切断する。ワイヤカットにより、ワイヤ片90が形成される。ワイヤカット後、図48に示すように、ツール101を含む超音波接合装置を退避させる。カットにより荷重が解放され、ワイヤ片90のテール部96が弾性変形状態から復元し、ヒートシンク40の実装面40aに対してはね上がる。接触していた非固定部93の部分が実装面40aから離れる。

Then, as shown in FIG. 47, wire cutting is performed. The

ワイヤカットにより、ヒートシンク40には、図48に示すようにカッター痕41が形成される。カッター痕41は、ワイヤ片90の延設方向の両端のうち、テール部96の直下に形成される。

By wire cutting, a

<第10実施形態のまとめ>

本実施形態では、ワイヤ片90の体積を、1.0×107μm3以下に設定している。これにより、熱応力を低減し、ひいては素子ダメージを抑制することができる。つまり、半導体装置10の信頼性を向上することができる。

<Summary of the tenth embodiment>

In this embodiment, the volume of the

なお、先行実施形態(図28参照)において、上記した体積の関係を満たすようにしてもよい。ただし、両端側に平坦部92を設けると、ワイヤ片90の全長LWが長くなる。また、レベリング加工しないと、ワイヤ高さ、つまり高さHF、HTのばらつきが大きい。レベリング加工が必要な分、工程数、ひいては製造工ストが増加する。

Note that in the preceding embodiment (see FIG. 28), the above-described volume relationship may be satisfied. However, if the

本実施形態では、上記した体積の関係を満たすために、ワイヤ片90の全長LWを400μm以上、450μm以下にし、フィード部95およびテール部96の長さLF、LTを100μm以下にする。平坦部92を設けないため、フィード部95およびテール部96の長さLF、LTおよびワイヤ片90の全長LWを短くすることができる。また、レベリング加工が不要であり、たとえば製造コストを低減することができる。

In this embodiment, in order to satisfy the above volume relationship, the total length LW of the

特に、ボンド部94の長さLBに対してフィード部95およびテール部96の長さLF、LTを短くする。具体的には、LF/LB、LT/LBを0.1以上、0.65以下にする。これにより、高さHF、HTのばらつきを抑制することができる。

In particular, the lengths LF and LT of the

本実施形態では、フィード部95の高さHFおよびテール部96の高さHTを、80μm以上、100μm以下にする。これにより、接続信頼性を確保することができる。

In this embodiment, the height HF of the

本実施形態では、ボンド部94の長さLBに対するボンド部94の幅WBの比(WB/LB)を、0.2以上、0,7以下にする。幅WBを狭くするため、ワイヤ片90の体積を小さくすることができる。また、幅WBを狭くするために、超音波接合時のパワーや荷重を、接合強度が確保できる範囲で抑える。これにより、潰し量を低減し、ひいては高さHF、HTのばらつきを抑制することができる。

In the present embodiment, the ratio of the width WB of the

本実施形態に示した平坦部92を有さないワイヤ片90については、第1実施形態~第8実施形態との組み合わせが可能である。たとえば、図12や図20に示した四隅にのみワイヤ片90を配置する構成に好適である。本実施形態は、半導体素子の主電極と配線部材との接合部に配置されるワイヤ片に適用が可能である。ワイヤ片の配置は、先行実施形態に示した配置に限定されない。

The

(他の実施形態)

この明細書及び図面等における開示は、例示された実施形態に制限されない。開示は、例示された実施形態と、それらに基づく当業者による変形態様を包含する。たとえば、開示は、実施形態において示された部品及び/又は要素の組み合わせに限定されない。開示は、多様な組み合わせによって実施可能である。開示は、実施形態に追加可能な追加的な部分をもつことができる。開示は、実施形態の部品及び/又は要素が省略されたものを包含する。開示は、ひとつの実施形態と他の実施形態との間における部品及び/又は要素の置き換え、又は組み合わせを包含する。開示される技術的範囲は、実施形態の記載に限定されない。開示されるいくつかの技術的範囲は、請求の範囲の記載によって示され、さらに請求の範囲の記載と均等の意味及び範囲内でのすべての変更を含むものと解されるべきである。

(Other embodiments)

The disclosure in this specification, drawings, etc. is not limited to the illustrated embodiments. The disclosure encompasses the illustrated embodiments and variations thereon by those skilled in the art. For example, the disclosure is not limited to the combinations of parts and/or elements shown in the embodiments. The disclosure can be implemented in various combinations. The disclosure can have additional parts that can be added to the embodiments. The disclosure encompasses omitting parts and/or elements of the embodiments. The disclosure encompasses permutations or combinations of parts and/or elements between one embodiment and another. The disclosed technical scope is not limited to the description of the embodiments. The disclosed technical scope is indicated by the description of the claims, and should be understood to include all modifications within the meaning and range of equivalents to the description of the claims.

明細書及び図面等における開示は、請求の範囲の記載によって限定されない。明細書及び図面等における開示は、請求の範囲に記載された技術的思想を包含し、さらに請求の範囲に記載された技術的思想より多様で広範な技術的思想に及んでいる。よって、請求の範囲の記載に拘束されることなく、明細書及び図面等の開示から、多様な技術的思想を抽出することができる。 The disclosure in the specification, drawings, etc. is not limited by the description in the claims. The disclosure in the specification, drawings, etc. encompasses the technical ideas described in the claims, and further extends to technical ideas that are more diverse and broader than the technical ideas described in the claims. Therefore, various technical ideas can be extracted from the disclosure of the specification, drawings, etc., without being bound by the scope of claims.

半導体装置10をインバータ5に適用する例を示したが、これに限定されない。たとえばコンバータに適用することもできる。また、インバータ5およびコンバータの両方に適用することもできる。

Although an example in which the

半導体素子30が、ひとつのアームを構成するIGBT6iおよびFWD6dを有する例を示したが、これに限定されない。IGBT6iおよびFWD6dを別チップ(別の素子)としてもよい。スイッチング素子としてIGBT6iの例を示したが、これに限定されない。たとえばMOSFETを採用することもできる。また、両面に主電極を有する縦型構造の素子としてダイオードを採用することもできる。

Although an example in which the

半導体素子30Hを複数備え、複数の半導体素子30Hが並列接続されて上アーム6Hのひとつを構成してもよい。半導体素子30Lを複数備え、複数の半導体素子30Lが並列接続されて下アーム6Lのひとつを構成してもよい。

A plurality of

ヒートシンク40、50の裏面40b、50bが、封止樹脂体20から露出する例を示したが、これに限定されない。裏面40b、50bの少なくとも一方が、封止樹脂体20によって覆われた構成としてもよい。裏面40b、50bの少なくとも一方が、封止樹脂体20とは別の図示しない絶縁部材によって覆われた構成としてもよい。半導体装置10が封止樹脂体20を備える例を示したが、これに限定されない。封止樹脂体20を備えない構成としてもよい。

Although an example in which the back surfaces 40b, 50b of the heat sinks 40, 50 are exposed from the sealing

半導体装置10が、一相分の上下アーム回路6を構成する複数の半導体素子30を備える例を示したが、これに限定されない。ひとつのアームを構成する半導体素子のみを備えてもよい。半導体装置10は、たとえば、ひとつのアームを構成する半導体素子30と、半導体素子30を挟むように配置された一対のヒートシンク40、50を備えればよい。また、三相分の上下アーム回路6を構成する半導体素子をひとつのパッケージとして備えてもよい。

Although an example in which the

信号端子75がボンディングワイヤ87を介してパッド33に接続される例を示したが、これに限定されない。たとえば信号端子75を、はんだを介してパッド33に接続してもよい。ボンディングワイヤ87のスペースが不要となるため、ターミナル55を備えない構成とすることが可能である。

Although an example in which the

ヒートシンク50に溝51を設け、継手部61、62に溝63を設ける例を示したが、これに限定されない。溝51、63の少なくとも一方を排除した構成としてもよい。上アーム6Hと下アーム6Lとをつなぐ連結部分を、2つの継手部60、61の接続構造により実現する例を示したが、これに限定されない。ヒートシンク40L、50Hの一方に連なる継手部が、他方に接続される構成としてもよい。また、継手部62を備える例を示したが、これに限定されない。主端子71が、継手部62を介さず、ヒートシンク50Lに連なる構成としてもよい。

Although an example in which the

1…電力変換装置、2…直流電源、3…モータジェネレータ、4…平滑コンデンサ、5…インバータ、6…上下アーム回路、6H…上アーム、6L…下アーム、6i…IGBT、6d…FWD、7…高電位電源ライン、8…低電位電源ライン、9…出力ライン、10…半導体装置、20…封止樹脂体、20a…表面、20b…裏面、20c、20d…側面、30、30H、30L…半導体素子、30a…表面、30b…裏面、30c…素子中心、31…エミッタ電極、32…コレクタ電極、33…パッド、33g…ゲートパッド、34…ゲート配線、35…ゲート配線保護部、40、40H、40L…ヒートシンク、40a…実装面、40b…裏面、41…カッター痕、50、50H、50L…ヒートシンク、50a…実装面、50b…裏面、51…溝、55、55H、55L…ターミナル、55a…第1端面、55b…第2端面、550…面取り部、60、61、62…継手部、63…溝、64…凸部、70、71、72…主端子、71a…接続部、75…信号端子、80、81、82、83、84…はんだ、80a…中央領域、80b…外周領域、80S…溶融はんだ、86…空隙、87…ボンディングワイヤ、88…吊りリード、90、90a、90b、900、901、902…ワイヤ片、91…固定部、92…平坦部、93…非固定部、94…ボンド部、95…フィード部、96…テール部、98…治具、99…ボンディングワイヤ、100…ワイヤガイド、101…ツール、102…カッター

DESCRIPTION OF

Claims (16)

第1対向面と第2対向面との間に介在して接合部を形成する接合部材と、

前記接合部材を介して前記主電極と電気的に接続された配線部材と、

前記接合部材内に配置され、前記第1対向面に固定されて前記第1対向面から突起する複数のワイヤ片(90)と、を備え、

前記配線部材は、前記裏面側に配置され、前記裏面電極と接続された裏側配線部材(40)を含み、

前記接合部材は、前記裏面電極と前記裏側配線部材との接合部を形成し、複数の前記ワイヤ片が配置された裏側接合部材(80)を含み、

前記裏側接合部材は、前記板厚方向の平面視において、素子中心を含む前記半導体素子の中央部分と重なる中央領域(80a)と、前記中央部分を取り囲む前記半導体素子の外周部分と重なる部分を含み、前記中央領域を取り囲む外周領域(80b)と、を有し、

前記外周領域には、4つ以上の前記ワイヤ片が少なくとも前記半導体素子の四隅のそれぞれに対応して配置され、

前記ワイヤ片の少なくともひとつが、前記平面視において前記素子中心に向けて延びており、

前記ワイヤ片は、

前記主電極と前記配線部材との接合部において前記配線部材に固定されており、

前記板厚方向において前記主電極と対向する側に、前記配線部材における固定面と平行な平坦部(92)を有し、

前記板厚方向において前記配線部材と対向する側に、前記配線部材との固定部(91)と、前記固定部に連なり、前記配線部材に固定されていない部分である非固定部(93)と、を有している半導体装置。 A semiconductor element having, as main electrodes, a front electrode (31) formed on the front surface and a rear electrode (32) formed on the rear surface opposite to the front surface in the plate thickness direction and having a larger area than the front electrode. (30) and

a joining member interposed between the first opposing surface and the second opposing surface to form a joint;

a wiring member electrically connected to the main electrode via the bonding member;

a plurality of wire pieces (90) arranged in the joining member, fixed to the first opposing surface and protruding from the first opposing surface;

The wiring member includes a back side wiring member (40) arranged on the back side and connected to the back electrode,

The bonding member includes a back side bonding member (80) forming a bonding portion between the back electrode and the back side wiring member and having a plurality of wire pieces arranged thereon,

The back side bonding member includes a central region (80a) that overlaps the central portion of the semiconductor element including the element center and a portion that overlaps the outer peripheral portion of the semiconductor element surrounding the central portion in a plan view in the plate thickness direction. , and a peripheral region (80b) surrounding the central region,

Four or more wire pieces are arranged in the outer peripheral region corresponding to at least four corners of the semiconductor element,

at least one of the wire pieces extends toward the center of the element in the plan view ;

The piece of wire is

fixed to the wiring member at a junction between the main electrode and the wiring member,

A flat portion (92) parallel to the fixing surface of the wiring member is provided on the side facing the main electrode in the plate thickness direction,

A fixed portion (91) to the wiring member and a non-fixed portion (93) connected to the fixed portion and not fixed to the wiring member are provided on the side facing the wiring member in the plate thickness direction. A semiconductor device comprising:

第1対向面と第2対向面との間に介在して接合部を形成する接合部材と、

前記接合部材を介して前記主電極と電気的に接続された配線部材と、

前記接合部材内に配置され、前記第1対向面に固定されて前記第1対向面から突起する複数のワイヤ片(90)と、を備え、

前記配線部材は、前記裏面側に配置され、前記裏面電極と接続された裏側配線部材(40)を含み、

前記接合部材は、前記裏面電極と前記裏側配線部材との接合部を形成し、複数の前記ワイヤ片が配置された裏側接合部材(80)を含み、

前記裏側接合部材は、前記板厚方向の平面視において、素子中心を含む前記半導体素子の中央部分と重なる中央領域(80a)と、前記中央部分を取り囲む前記半導体素子の外周部分と重なる部分を含み、前記中央領域を取り囲む外周領域(80b)と、を有し、

前記外周領域には、4つ以上の前記ワイヤ片が少なくとも前記半導体素子の四隅のそれぞれに対応して配置され、

前記ワイヤ片の少なくともひとつが、前記平面視において前記素子中心に向けて延びており、

前記ワイヤ片は、前記主電極と前記配線部材との接合部において前記配線部材に固定されており、

前記ワイヤ片それぞれの体積が、1.0×10 7 μm 3 以下であり、

前記ワイヤ片は、前記配線部材に接合された部分である接合部(94)と、前記接合部に連なるとともに前記ワイヤ片の延設方向の両端にそれぞれ設けられ、前記配線部材に接合されていない部分である非接合部(95、96)と、を有する半導体装置。 A semiconductor element having, as main electrodes, a front electrode (31) formed on the front surface and a rear electrode (32) formed on the rear surface opposite to the front surface in the plate thickness direction and having a larger area than the front electrode. (30) and

a joining member interposed between the first opposing surface and the second opposing surface to form a joint;

a wiring member electrically connected to the main electrode via the bonding member;

a plurality of wire pieces (90) arranged in the joining member, fixed to the first opposing surface and protruding from the first opposing surface;