JP7091406B2 - Sn-Bi-In系低融点接合部材、微小部材および半導体電子回路、バンプの製造方法ならびに半導体電子回路の実装方法 - Google Patents

Sn-Bi-In系低融点接合部材、微小部材および半導体電子回路、バンプの製造方法ならびに半導体電子回路の実装方法 Download PDFInfo

- Publication number

- JP7091406B2 JP7091406B2 JP2020149165A JP2020149165A JP7091406B2 JP 7091406 B2 JP7091406 B2 JP 7091406B2 JP 2020149165 A JP2020149165 A JP 2020149165A JP 2020149165 A JP2020149165 A JP 2020149165A JP 7091406 B2 JP7091406 B2 JP 7091406B2

- Authority

- JP

- Japan

- Prior art keywords

- melting point

- plating

- mass

- low melting

- plated

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/8119—Arrangement of the bump connectors prior to mounting

- H01L2224/81191—Arrangement of the bump connectors prior to mounting wherein the bump connectors are disposed only on the semiconductor or solid-state body

Description

点1(1、69、30)、点2(26、52、22)、点3(40、10、50)、点4(1、57、42)の4点を頂点とする四角形の範囲内であり、融点が60~110℃であるSn-Bi-In合金を含むSn-Bi-In系低融点接合部材。

<2> 前記Sn-Bi-In合金が、Ag、Cu、Ni、Zn、およびSbからなる群から選択される1以上の混合成分を含み、前記合金における前記混合成分の合計質量が0.001~3.0質量%である前記<1>記載のSn-Bi-In系低融点接合部材。

<3> アンダーメタルとしてTi、Ni、Cu、Au、Sn、Ag、Cr、Pd、Pt、W、Co、TiW、NiP、NiB、NiCo、およびNiVからなる群から選択される1以上のアンダーメタルを成膜したものの上に前記Sn-Bi-In合金が配置される前記<1>または<2>に記載のSn-Bi-In系低融点接合部材。

<4> 前記Sn-Bi-In合金が、SnとBiとInとの合計を100質量%としたとき、Snを15~19質量%、Biを43~51質量%、Inを30~42質量%含む組成である前記<1>~<3>のいずれかに記載のSn-Bi-In系低融点接合部材。

<5> 前記Sn-Bi-In合金が、Sn、Bi、およびInの濃度が異なる複数の層を有する積層めっき層を有する前記<1>~<4>のいずれかに記載のSn-Bi-In系低融点接合部材。

<6> 前記Sn-Bi-In合金が、Sn、Bi、およびInの濃度が異なる複数の層を有する積層めっき層を、加熱リフローされてなるバンプを有する前記<1>~<4>記載のいずれかSn-Bi-In系低融点接合部材。

<7> 大きさが1mm以下である、微小金属ボール、導電性の金属の被覆層を有する微小樹脂ボール、はんだ合金の被覆層を有する微小樹脂ボール、および微小ピン部材からなる群から選択されるいずれかのコア材の表層に前記Sn-Bi-In合金を有する微小部材を有する前記<1>~<6>のいずれかに記載のSn-Bi-In系低融点接合部材。

<8> 導電性接合部上に前記微小部材が実装された前記<7>に記載の低融点接合部材。

<9> 前記<1>~<8>のいずれかに記載のSn-Bi-In系低融点接合部材を有することを特徴とする半導体電子回路。

本発明のSn-Bi-In系低融点接合部材は、Sn-Bi-In三元状態図で、Snがx質量%、Biがy質量%、Inがz質量%である点を(x、y、z)とするとき、点1(1、69、30)、点2(26、52、22)、点3(40、10、50)、点4(1、57、42)の4点を頂点とする四角形の範囲内であり、融点が60~110℃であるSn-Bi-In合金を含む。以下、「本発明のSn-Bi-In系低融点接合部材」を、単に「本発明の接合部材」と記載する場合がある。

なお、本発明の接合部材の融点は、Sn-Bi-In合金部分の融点である。またその測定方法は、後述する実施例に記載のように、DSCで測定したときの吸熱ピークのトップ温度をその成分の融点として扱うものである。また、ピークが複数ある場合は、最も低い温度の吸熱ピークを最低融点(固相線温度)とし、最も高い温度の吸熱ピークを最高融点(液相線温度)として扱う。

(a)単独の吸熱ピークを示すもの

(b)吸熱ピークを複数示す場合であっても、最も大きな吸熱ピーク高さに対して、他の吸熱ピークの高さが1/10以下であるもの

(c)大きな吸熱ピーク高さをもつ吸熱ピークを複数示す場合であっても、大きな吸熱ピーク高さをもつ吸熱ピークのトップ温度の差が5℃以内であるもの

また、実施例8に示す、Snが19質量%、Biが48質量%、Inが33質量%の組成では、吸熱ピーク高さの小さな吸熱ピークが70℃と108℃に観察されるが、吸熱ピーク高さの大きな吸熱ピークは、82℃に観察される吸熱ピークのみである。

実施例10に示す、Snが17質量%、Biが45質量%、Inが38質量%の組成では、83℃に単独の吸熱ピークが観察されている。

本発明のSn-Bi-In系低融点接合部材等の形成については、Snめっき、Biめっき、Inめっきをそれぞれ行うことで得られる低融点めっき積層物を利用する方法であるめっき積層法を主体に説明する。めっき方法は、電解めっきまたは無電解めっきのいずれの方法でも可能であるが、めっき所要時間や生産性などを考慮すると電解めっきが好ましい。

本発明にかかるSn-Bi-In系低融点はんだ合金やそのはんだ合金バンプを形成させる対象となる部材は、LSIなどの半導体電子部品またはこれを複数搭載して回路構成されたパッケージやモジュールとするためのプリント配線板などの配線基板などである。これらの部材は、必要に応じてその表面をフォトリソグラフィー等により所要の導電性接合部(パッド)がパターン形成されたものを使用する。

被めっき物の表面洗浄は、被めっき物の表面の付着物を除去して清浄化することが目的であり、付着物除去が可能な溶媒を選定して用いる。例えば、有機溶媒としてはメタノール、エタノール、イソプロピルアルコール等の低級アルコール類、アセトン、メチルエチルケトン(MEK)、イソブチルケトン(MIBK)等のケトン類などが挙げられる。水系溶媒としては、アンモニア、有機アミン化合物等と過酸化水素水の併用、アニオン系、カチオン系、ノニオン系の界面活性剤などが添加された水溶液が挙げられる。これらの溶媒のうち、被めっき物の材質を侵さないことを考慮して適時選択して用いる。

導電性接合部がパターン形成された被めっき物の表面に、必要に応じてTi(チタン)、Ni(ニッケル)、Cu(銅)、Au(金、Sn(スズ)、Ag(銀)、Cr(クロム)、Pd(パラジウム)、Pt(白金)、W(タングステン)、Co(コバルト)、TiW(チタン-タングステン)、NiP(ニッケル-リン)、NiB(ニッケル-ホウ素)、NiCo(ニッケル-コバルト)、およびNiV(ニッケル-バナジウム)からなる群から選択される1以上のアンダーメタルを成膜したものを用いることも可能である。これらのアンダーメタルは、単独または複数を積層して用いても構わない。成膜方法は、蒸着、PVD、めっき法などから適応可能な方法を適時選択して用いれば良い。成膜の膜厚は、各々で0.01~10μmの範囲で適時設定すれば良い。

また、集積回路の微細化に伴って導電性接合材料のはんだ合金を狭い間隔(狭ピッチ)で並べることによる実装時(加熱リフロー時)のショート防止などの目的で設けられる円柱状の導電性ポストをアンダーメタル上に形成したものを用いることも可能である。円柱状のポスト材としては、Cu、Ag、Niなどの導電性金属から適時選択すれば良い。円柱状ポストの形成は、PVD、めっき法などから適応可能な方法を適時選択して用いれば良い。円柱状ポストの高さは、1~200μmの範囲が通常であり、その必要に応じて適時設定すれば良い。

前記した導電性接合部がパターン形成されたこれらの被めっき物上に、本発明のSn-Bi-In系低融点接合部材にかかるめっき積層物を形成する方法について以下に説明する。まず、Sn、Bi、In各々のめっき処理の方法を以下に例示する。

Snめっきは、被めっき物をめっきする主たる成分としてSnを含むめっき液等を用いて行うめっき処理である。Snめっき液は、市販のものを使用すれば良く、例えば石原ケミカル社のSnめっき液などが挙げられる。めっき条件としては、例えば撹拌翼、揺動、スキージ撹拌などを用いた撹拌下で、温度5~50℃、めっき液中のSnイオン濃度1~70g/L、電流密度0.1~20.0A/dm2の範囲内で任意に設定すれば良い。Snめっき量は、設定条件下でのめっき処理時間(めっき液浸漬時間)で制御可能である。

Biめっきは、被めっき物をめっきする主たる成分としてBiを含むめっき液等を用いて行うめっき処理である。Biめっき液は、市販のものを使用すれば良く、例えば石原ケミカル社のBiめっき液などが挙げられる。めっき条件としては、例えば撹拌翼、揺動、スキージ撹拌などを用いた撹拌下で、温度5~50℃、めっき液中のBiイオン濃度1~70g/L、電流密度0.1~20.0A/dm2の範囲内で任意に設定すれば良い。Biめっき量は、設定条件下でのめっき処理時間(めっき液浸漬時間)で制御可能である。

Inめっきは、被めっき物をめっきする主たる成分としてInを含むめっき液等を用いて行うめっき処理である。Inめっき液は、市販のものを使用すれば良く、例えば石原ケミカル社やEEJA社のInめっき液などが挙げられる。めっき条件としては、例えば撹拌翼、揺動、スキージ撹拌などを用いた撹拌下で、温度5~50℃、めっき液中のInイオン濃度1~70g/L、電流密度0.1~20.0A/dm2の範囲内で任意に設定すれば良い。Inめっき量は、設定条件下でのめっき処理時間(めっき液浸漬時間)で制御可能である。

めっき積層順番は、SnめっきとBiめっきとInめっきを、いずれも行うものとすることができ、その順序は任意でよい。具体的には、被めっき物の表面から順に、Sn→Bi→In、Sn→In→Bi、Bi→Sn→In、Bi→In→Sn、In→Sn→Bi、In→Bi→Snの順のいずれの順番でも可能である。電解めっきでSn-Bi-Inを所定の組成で安定的に積層するには、標準電極電位が高くイオン化傾向の小さいものからめっきした方が好ましく「Bi→Sn→In」または「Sn→Bi→In」の順番で積層めっきすることがより好ましい。なお、25℃、105パスカル(Pa)で標準水素電極を基準した場合の標準電極電位は、Bi=0.317V、Sn=-0.138V、In=-0.338Vであり、3成分のなかで最も電位の低いInめっきを1つ目や2つ目のめっきとすると、Inは次成分のめっき操作中に電解めっき浴中でイオン化して溶出し易いため、めっき積層物中における濃度が設定条件よりも低下し易い。よって、Inめっきは、SnめっきおよびBiめっきを行った後に行う、最後のめっきとすることが好ましい。

めっき積層物は、Sn、Bi、In各成分を単独で逐次にめっき処理して積層したものである。本発明のめっき積層物は、Sn、Bi、Inの濃度差が異なる複数の層を有している。この層は、例えば、Snめっきによる層にInが拡散したSnIn層や、Biめっきによる層にInが拡散したBiIn層を有するものとすることができる。めっき後に、これらの合金層を形成することで、Sn、Bi、In各々単独の融点よりも大幅に低い60~110℃の低融点めっき積層物にできる。

Snめっきにより得られるSnの層は、Sn(スズ)を含む層である。Snの層は、Inを除いてSnを主たる成分として含んでおり、この層におけるInを除く元素におけるSn濃度は、70質量%以上が好ましく、80質量%以上がより好ましく、90質量%以上であることがさらに好ましい。このSnの層は、Snめっきにより得ることができる。

Biめっきにより得られるBiの層は、Bi(ビスマス)を含む層である。Biの層は、Inを除いてBiを主たる成分として含んでおり、この層におけるInを除く元素におけるBi濃度は、70質量%以上が好ましく、80質量%以上がより好ましく、90質量%以上であることがさらに好ましい。このBiの層は、Biめっきにより得ることができる。

Inめっきにより積層めっき層に含まれるInは、めっき処理中にSnの層やBiの層中に拡散し易いため、In単独を主成分とした単独層は形成し難く、SnIn合金またはBiIn合金の形態で形成される場合がある。

積層めっき層のめっき積層数は、特に限定されず、Sn、Bi、Inの濃度が異なる2層以上の複数の層を有するものであれば良い。なお、被めっき物とめっき成分の相互作用による双方成分の合金化や拡散防止などの目的により、前記の3成分の濃度が異なる層を形成させて、3層や、4層、5層などの積層も可能である。

各めっき工程後の水洗の目的は、めっき浴から引上げた時に被めっき物の表面に付着しためっき液の除去であり、水中に浸漬または水シャワーにより水洗して清浄化する。その後の乾燥は、めっき積層物の融点未満の温度で乾燥すれば良い。めっき積層物の融点を考慮したうえで、通常は室温~100℃の範囲で適時設定して加温乾燥または通風乾燥すれば良い。なお、次工程で残存水分があっても問題なければ、乾燥工程を省略して次工程に進めることも可能である。

レジストパターン除去は、Sn-Bi-In系低融点めっき積層物を侵さずにレジスト除去できる薬液に浸漬またはシャワー洗浄などの公知の湿式法、または酸素プラズマによるアッシング処理などの方法を用いて除去することが可能である。

本発明のSn-Bi-In系低融点接合部材は、皮膜の平滑性や、密着性などの物性向上の目的で、融点が110℃を超えない範囲で、適宜、Sn-Bi-In合金に、Ag、Cu、Ni、Zn、およびSbからなる群から選択される1以上の混合成分を含み、Sn-Bi-In合金における前記混合成分の合計質量が占める割合(混合成分の合計質量/Sn-Bi-In合金の質量)が、0.001~3.0質量%の範囲で混合することも可能である。

本発明の接合部材は、はんだ合金の形態とすることもできる。このはんだ合金バンプを製造するにあたっては、Sn-Bi-In系低融点接合部材に係るめっき積層物を80~135℃の低温領域で加熱リフロー処理してバンプ形成したものを用いてもよい。一般的に加熱リフローによるはんだ合金バンプの形成では、合金組成が均一で表面凹凸が無く、均一な球状または半球状の形状物性が求められる。また、実装物性としては、被めっき物などの接合部材の接着対象物との接合強度が3.3mg/μm2以上、ヒートサイクル耐久性などが必要である。これらの要求物性に悪影響する因子は、はんだ合金そのものの基本物性や、加熱リフロー前の合金成分の自然酸化膜や不純物付着や混入などがあげられる。

・ぎ酸ガス還元法 MeO + HCOOH → Me + CO2 +H2O

・水素ガス還元法 MeO + H2 → Me + H2O

次に、被めっき物等としてBGA等の微小ボール搭載型の導電性接合材料のコアボールとして用いられる微小金属ボールおよび微小樹脂ボール、微小ピンなどのコア材の表層が、Sn-Bi-In系低融点めっき積層物で被覆された接合部材を形成する方法について説明する。

微小金属ボールなどのコア材のめっき方法としては、円周方向に回転する円柱状めっき槽で、めっき槽内中央部に陽極、槽内円周部に陰極が配設され、回転軸が水平軸による垂直方向回転あるいは傾斜軸による傾斜回転ができる装置を用いて、5~200rpm程度の回転数でめっき処理を行う。具体的には、槽内にめっき液と被めっき物のボール等を入れて、所定のめっき厚みになる様に電流密度および通電時間を設定してめっき処理を行い、終了すれば回転円周部よりめっき処理されたボール等およびめっき液が排出される回転型めっき装置(バレルめっき法)を用いることができる。また、これを微小金属ボールのめっき用に改良された特開平10-18096号公報や、特開平10-270836号公報に記載の回転型めっき装置や、更には特開平11-92994号公報に記載の回転型めっき装置を用いることができる。

なお、コア材として微小金属ピンなどを用いる場合も前記した微小金属ボールを用いる場合と同様に、本発明のSn-Bi-In系低融点めっき積層物を形成することが可能である。

微小金属ボールなどの表面にSn-Bi-In系低融点めっき積層物を被覆する方法は、前記したバレルめっき法(回転型めっき装置)等の公知の装置を用いることができる。Sn、Bi、In各々のめっき方法は前述のSn-Bi-In系低融点めっき積層物の形成方法と同様の条件でめっきすれば良く、めっき積層の順番は特に限定されないが、最初(最下層)にSnまたはBiめっき、最後(最上層)にInめっきすることが好ましい。また、めっき膜の平滑性、密着性向上、またはめっき処理中のボール相互の凝集防止などの物性向上の目的で前述した(特定の微量金属添加)と同様の微量金属を添加することができる。

前記のコア材の表面をSn-Bi-In系低融点めっき積層物で被覆された微小金属ボールや微小樹脂ボールなどのバンプ形成について例示する。BGA用プリント配線板などの導電性接合部のパット上にフラックスを塗布し、その上に前記したSn-Bi-In系低融点めっき積層物で被覆された微小金属ボールや微小樹脂ボールなどを実装した後、前述のSn-Bi-In系低融点はんだ合金バンプの形成と同様の方法で加熱リフローすることで、導電性接合部のパッド上にバンプ形成が可能である。

本発明にかかるめっき積層物や、本発明にかかるめっき積層物を加熱リフローして形成されるSn-Bi-In系低融点はんだ合金バンプのような接合部材を、配線基板と、半導体チップ表面との間に配置して、80~135℃の範囲内で加熱リフローして前記配線基板と前記半導体チップとを接合する半導体電子回路の実装を行うことができる。

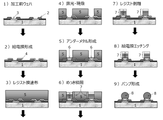

まず、1)加工前ウエハに示すように、基板1(シリコン、化合物半導体、圧電素子、樹脂基板等)上に、パッド3(Au、Al-Cu等)が配置され、保護膜2(SiN、ポリイミド等)を有している。

次に、2)給電膜形成に示すように、保護膜2やパッド3上に、給電膜4(Ti/Cu等)を形成する。

次に、3)レジスト膜塗布に示すように、給電膜4の上に、レジスト膜5を塗布する。

次に、4)露光・現像に示すように、レジスト膜5に所定のパターンで露光・現像を行い、レジスト膜5の一部を除去する。この時、通常、パッド3に対応する位置に露光を行う。

次に、5)アンダーメタル形成に示すように、レジスト膜5を露光・現像して孔が形成された部分にアンダーメタル6(Ni、Cu等)を形成する。

次に、6)めっき積層に示すように、本発明の接合部材に関する製造方法により、積層めっき層7(Sn、Bi、In)を形成する。

次に、7)レジスト剥離に示すように、残存していたレジスト膜5も除去する。これにより、パッド3上に積層めっき層7が形成された状態となる。

次に、8)給電膜エッチングに示すように、給電膜4をエッチングにより除去する。

そして、9)バンプ形成に示すように、加熱リフローすることで、積層めっき層7から、はんだ合金バンプ8(Sn/Bi/In)が形成され、接合部材として用いることができる。なお、8)給電膜エッチング後の積層めっき層7をそのまま接合部材として用いることもできる。

実施例1~21、比較例1~5で得られたSn-Bi-In系めっき積層物をSUS基板から剥離して、酸溶解後、ICP-OES(高周波誘導結合プラズマ-発光分光分析装置)にて、定量分析を行った。また、実施例27、比較例6~9、参考例1~2については、めっき積層物を加熱リフローしたはんだ合金バンプを前記同様に測定した。使用機器及び測定条件は以下の通りである。

・測定機 Thermo Fisher Scientific社ICP発光分光分析装置 形式:iCAP6300Duo

・測定条件 検量線法による定量分析

測定波長:Sn188.9nm、Bi306.7nm、In325.6nm

実施例1~21、比較例1~5で得られたSn-Bi-In系めっき積層物をSUS基板から剥離、粉砕したサンプルを測定サンプルとして、DSC(示差走査熱量計)を用いて昇温過程における吸熱プロファイルを測定した。昇温過程のDSC測定においては、各成分の融解熱が吸熱ピークとして表れ、測定サンプルの組成によって単独または複数の吸熱ピークとなる。本発明では、便宜的に各吸熱ピークのトップ温度をその成分の融点として扱う。また、ピークが複数ある場合は、最も低い温度の吸熱ピークを最低融点(固相線温度)、最も高い温度の吸熱ピークを最高融点(液相線温度)とした。使用機器及び測定条件は以下の通りである。

・測定機器 セイコーインスツル株式会社DSC装置 形式:DSC6220型

・測定条件 サンプル量:10~36mg

測定パン:アルミニウム

雰囲気:窒素ガス

測定温度範囲:室温~300℃,昇温速度:10℃/分

実施例27、比較例6~9、参考例1~2で得られたはんだ合金バンプのバンプ直径を画像計測にて測定した。使用機器及び測定条件は以下の通りである。

・測定機器 キーエンス社レーザー顕微鏡 形式:VK-X150

・測定条件 画像計測:200倍画像からの測長

実施例27、比較例6~9、参考例1~2で得られたはんだ合金バンプのシェア強度をシェア強度試験機にて測定した。使用機器及び測定条件は以下の通りである。

・測定機器 DAGE社ボンドテスター 形式:4000

・測定条件 シェアスピード:150μm/s、シェア位置:はんだ部

脱脂洗浄したSUS304板(100mm×40mm×厚み0.3mm)の裏面の全面にテフロン(登録商標)テープを張り付け、一方の表面にテフロン(登録商標)テープを張り付けてSUS板開口部が40mm×40mmとして被めっき物とした。めっき浴としては、ガラス製1Lビーカーを用い、各々のめっき液を500mlほど入れて、陽極には白金を使用した。

Sn-Bi-In各々のめっき液は以下のものを使用した。

・Snめっき液 石原ケミカル社製(Sn濃度 5g/L)

・Biめっき液 石原ケミカル社製(Bi濃度 40g/L)

・Inめっき液 EEJA社製(In濃度 25g/L)

第1層目はBiめっきを行った。条件は、前記の被めっき物をBiめっき液に浸漬して揺動しながら、温度20℃、電流密度2A/dm2一定で、8分間めっき処理した後、引上げて、直ぐに水槽に浸漬し、これを引上げて水シャワー洗浄した。これを通風乾燥器を用いて、50℃で5分間乾燥してBiめっき物を得た。

引き続いて、第3層目のSnめっきを行った。Bi-Inめっき処理された被めっき物をSnめっき液に浸漬して揺動しながら、温度20℃、電流密度1A/dm2一定で、30秒間めっき処理した後、引上げて、直ぐに水槽に浸漬し、引上げて水シャワー洗浄した。これを通風乾燥器を用いて、50℃で5分間乾燥してBi-In-Sn系のめっき積層物を得た。

得られたBi-In-Snめっき積層物をSUS板から剥ぎ取り粉砕したサンプルの組成をThermo Fisher Scientific社ICP発光分光分析装置、融点をセイコーインスツル株式会社DSC装置を用いて測定した。

実施例1と同様の方法で、めっき積層の順番と各めっき成分のめっき時間を変えて、種々のSn-Bi-In組成を振っためっき積層物サンプルを作製した。

表1に、実施例1~21および比較例1~5で得られたSn-Bi-In系めっき積層物の組成分析結果および融点測定結果を示す。

また、融点測定時のDSC測定プロファイルの代表例として、実施例2、4、8、12、14、15、18、21、比較例2、4、5を図4~14に示す。

また、実施例7、10を図26、27に示す。

Snめっき液にCuを添加した、Sn=60g/L、Cu=1g/Lの複合めっき液を用いて、SnCu→Bi→Inの順番でめっき積層した以外は実施例1と同様の操作を行い、微量のCu添加系めっき積層物を得た。このめっき積層物をSUS板から剥ぎ取り粉砕したサンプルの組成をThermo Fisher Scientific社ICP発光分光分析装置を用いて測定し、融点をセイコーインスツル株式会社DSC装置を用いて測定した。結果を表2(Cu、Ag微量添加系めっき積層物の組成分析と融点測定結果)に示す。

Snめっき液にAgを添加した、Sn=40g/L、Ag=2.5g/Lの複合めっき液を用いて、SnAg→Bi→Inの順番でめっき積層した以外は実施例1と同様の操作を行い、微量のAg添加系めっき積層物を得た。このめっき積層物をSUS板から剥ぎ取り粉砕したサンプルの組成をThermo Fisher Scientific社ICP発光分光分析装置、融点をセイコーインスツル株式会社DSC装置を用いて測定した。結果を表2(Cu、Ag微量添加系めっき積層物の組成分析と融点測定結果)に示す。

自然酸化膜付きのシリコンウェハ表面に、スパッタで厚み0.1μmのTi膜と0.3μmのCu膜を成膜し、フォトリソグラフィーにて配線接続用の開口部(60μmφ×高さ40μm:1000000個、ピッチ間隔:150μm)が設けられたレジストパターンが形成されたシリコンウェハを作製し、続いて、ポストとして電解めっきでCuを10μm厚みで、更にその上に、電解めっきでNiを3μm厚みで成膜して、パターン形成被めっき物を作製した。

・還元剤 :ギ酸

・圧力 :200mbar

・昇温速度 :20℃/min

・トップ温度:110℃(キープ時間180sec)

比較例6~9は、バンプ組成が所定の組成になる様に、めっき積層時の各めっき液でのめっき処理時間(浸漬時間)を変えた以外は実施例27に準じて操作を行い、本発明のSn-Bi-In系組成範囲外のSn-Bi-In系低融点はんだ合金バンプを作製した。

はんだ合金バンプのシェア強度測定用のレファレンスとして、実施例27と同様のレジストパターンが形成されたシリコンウェハを用いて、同様の操作で表3に示すアンダーメタルを成膜(但し、参考例1は10μmのCuポスト形成は省略した)した上に、既存Pbフリーはんだ合金のバンプを作製した。参考例1は、Sn3.2Ag(Sn:96.8質量%、Ag:3.2質量%)はんだ合金バンプである。また、参考例2は、Sn58Bi(Sn:42質量%、Bi:58質量%)はんだ合金バンプである。いずれも公知のSnAgめっき液を用いてSnAgめっき処理したものをそれぞれ乾燥して、実施例27と同様のレジスト除去操作を行った後、同様のリフロー装置を用いて表3記載のリフロー温度以外は同様の操作条件ではんだ合金バンプを作製した。

また、実施例27、比較例6~9の結果から得られた「In濃度とバンプシェア強度の関係」を図21に示す。

微小金属ボール表面にSn-Bi-In系の低融点めっき積層物を形成した。まず、微小金属ボールの表面に、バリア層として電解Niめっきを成膜した。脱脂洗浄したφ450μmのCuボールの表面に、回転型めっき装置を用いて電解Niめっきを厚み約2μm成膜した物を作製した。続いて、回転型めっき装置を用いてSnAg-Bi-Inのめっき積層を行った。SnAg-Bi-In各々のめっき液は以下のものを使用した。

・SnAgめっき液 石原ケミカル社製(Sn濃度 5g/L、Ag濃度 0.5g/L)

・Biめっき液 石原ケミカル社製(Bi濃度 40g/L)

・Inめっき液 EEJA社製(In濃度 25g/L)

微小樹脂ボール表面にSn-Bi-In系の低融点めっき積層物を形成した。まず、微小樹脂ボールの表面に導電性金属を成膜した。脱脂洗浄したφ210μmの樹脂ボールに導電層として、まず撹拌下で無電解Niめっきを厚み約1μm、続いて回転型めっき槽を用いて電解Cuめっきを厚み約10μm、更にバリア層として電解Niめっきを厚み約1μm成膜した物を作製した。Sn-Bi-In各々のめっき液は、実施例28と同じものを使用した。

微金属円柱表面にSn-Bi-In系の低融点めっき積層物を形成した。まず、脱脂洗浄したφ300μm、L500μmのCu円柱の表面に、バリア層として回転型めっき装置を用いて電解Niめっきを厚み約2μm成膜した物を作製した。続いて、回転型めっき装置を用いてSnAg-Bi-Inのめっき積層を行った。SnAg-Bi-In各々のめっき液は以下のものを使用した。

・SnAgめっき液 石原ケミカル社製(Sn濃度 5g/L、Ag濃度 0.5g/L)

・Biめっき液 石原ケミカル社製(Bi濃度 40g/L)

・Inめっき液 EEJA社製(In濃度 25g/L)

2 保護膜

3 パッド

4 給電膜

5 レジスト膜

6 アンダーメタル

7 積層めっき層

8 はんだ合金バンプ

9 はんだ合金バンプ

10 接合用の金属膜

Claims (10)

- Sn、Bi、およびInの濃度が異なる複数の層を有する積層めっき層からなるSn-Bi-In系低融点接合部材であり、

前記積層めっき層は、示差走査型熱量計(DSC)を用いて、窒素雰囲気下、10℃/分の昇温速度で、室温から300℃まで昇温したときに観測される全ての吸熱ピークのピークトップの温度が60~110℃であり、

前記積層めっき層が、少なくとも、SnとInを含むSnIn層と、BiとInを含むBiIn層を有し、

前記積層めっき層におけるSnとBiとInとの合計量が占める割合が95質量%以上であり、

前記積層めっき層の総量において、SnとBiとInとの合計を100質量%として換算したときのそれぞれの濃度が、Sn-Bi-In三元状態図で、Snがx質量%、Biがy質量%、Inがz質量%である点を(x、y、z)とするとき、点1(1、69、30)、点2(26、52、22)、点3(40、10、50)、点4(1、57、42)の4点を頂点とする四角形の範囲内であるSn-Bi-In系低融点接合部材。 - 前記積層めっき層の総量において、SnとBiとInとの合計を100質量%としたとき、Snを15~19質量%、Biを43~51質量%、Inを30~42質量%含む組成である請求項1に記載のSn-Bi-In系低融点接合部材。

- SnとBiとInとの合計を100質量%としたとき、Snを17~19質量%、Biを43~51質量%、Inを32~38質量%含む組成であり、

SnとBiとInとの合計量が占める割合が95質量%以上であり、

示差走査型熱量計(DSC)を用いて、窒素雰囲気下、10℃/分の昇温速度で、室温から300℃まで昇温したときに観測される全ての吸熱ピークのピークトップの温度が60~110℃であるSn-Bi-In系低融点接合部材。 - Ag、Cu、Ni、Zn、およびSbからなる群から選択される1以上の混合成分を含み、

前記Sn-Bi-In系低融点接合部材における前記混合成分の合計質量が0.001~3.0質量%である請求項1~3のいずれかに記載のSn-Bi-In系低融点接合部材。 - アンダーメタルとしてTi、Ni、Cu、Au、Sn、Ag、Cr、Pd、Pt、W、Co、TiW、NiP、NiB、NiCo、およびNiVからなる群から選択される1以上のアンダーメタルを成膜したものの上に配置された請求項1~4のいずれかに記載のSn-Bi-In系低融点接合部材。

- 大きさが1mm以下である、微小金属ボール、導電性の金属の被覆層を有する微小樹脂ボール、はんだ合金の被覆層を有する微小樹脂ボール、および微小ピン部材からなる群から選択されるいずれかのコア材の表層に、請求項1~5のいずれかに記載のSn-Bi-In系低融点接合部材を有する微小部材。

- 導電性接合部のパッド上に配置された、請求項1~5に記載のSn-Bi-In系低融点接合部材および請求項6に記載の微小部材からなる群から選択されるいずれかを、80~135℃の範囲内で加熱リフローして、バンプを形成する工程を有するバンプの製造方法。

- 半導体チップの導電性接合部のパッド上に配置された、請求項1~5に記載のSn-Bi-In系低融点接合部材および請求項6に記載の微小部材からなる群から選択されるいずれかを、80~135℃の範囲内で加熱リフローしてバンプを形成した後、前記バンプと配線基板の電極部を重ねて、80~135℃の範囲内で加熱リフローして前記配線基板と前記半導体チップとを接合する半導体電子回路の実装方法。

- 配線基板の導電性接合部のパッド上に配置された、請求項1~5に記載のSn-Bi-In系低融点接合部材および請求項6に記載の微小部材からなる群から選択されるいずれかを、80~135℃の範囲内で加熱リフローしてバンプを形成した後、前記バンプと半導体チップの電極部を重ねて、80~135℃の範囲内で加熱リフローして前記配線基板と前記半導体チップとを接合する半導体電子回路の実装方法。

- 配線基板と半導体チップ表面との間に配置された、請求項1~5に記載のSn-Bi-In系低融点接合部材および請求項6に記載の微小部材からなる群から選択されるいずれかを、80~135℃の範囲内で加熱リフローして前記配線基板と前記半導体チップとを接合する半導体電子回路の実装方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019165700 | 2019-09-11 | ||

| JP2019165700 | 2019-09-11 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2021048392A JP2021048392A (ja) | 2021-03-25 |

| JP2021048392A5 JP2021048392A5 (ja) | 2022-01-20 |

| JP7091406B2 true JP7091406B2 (ja) | 2022-06-27 |

Family

ID=74876660

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020149165A Active JP7091406B2 (ja) | 2019-09-11 | 2020-09-04 | Sn-Bi-In系低融点接合部材、微小部材および半導体電子回路、バンプの製造方法ならびに半導体電子回路の実装方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7091406B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7091405B2 (ja) * | 2019-09-11 | 2022-06-27 | 株式会社新菱 | Sn-Bi-In系低融点接合部材および、その製造方法、ならびに半導体電子回路およびその実装方法 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000511466A (ja) | 1996-05-10 | 2000-09-05 | フォード、モーター、カンパニー | ロウ組成 |

| JP2001219267A (ja) | 2000-02-09 | 2001-08-14 | Nippon Macdermid Kk | 錫−インジウム−ビスマスはんだ合金めっき層の形成方法 |

| WO2008016140A1 (en) | 2006-08-04 | 2008-02-07 | Panasonic Corporation | Bonding material, bonded portion and circuit board |

| JP2013521207A (ja) | 2010-03-02 | 2013-06-10 | サン−ゴバン グラス フランス | 電気接続素子を備えた窓ガラス |

| JP5534122B1 (ja) | 2014-02-04 | 2014-06-25 | 千住金属工業株式会社 | 核ボール、はんだペースト、フォームはんだ、フラックスコート核ボールおよびはんだ継手 |

| WO2016056656A1 (ja) | 2014-10-10 | 2016-04-14 | 石原ケミカル株式会社 | 合金バンプの製造方法 |

| JP2018079480A (ja) | 2016-11-14 | 2018-05-24 | 住友金属鉱山株式会社 | 低温用のBi−In−Sn系はんだ合金、それを用いた電子部品実装基板及びその実装基板を搭載した装置 |

| JP2021048391A (ja) | 2019-09-11 | 2021-03-25 | 株式会社新菱 | Sn−Bi−In系低融点接合部材および、その製造方法、ならびに半導体電子回路およびその実装方法 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5344607A (en) * | 1993-06-16 | 1994-09-06 | International Business Machines Corporation | Lead-free, high tin, ternary solder alloy of tin, bismuth, and indium |

-

2020

- 2020-09-04 JP JP2020149165A patent/JP7091406B2/ja active Active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000511466A (ja) | 1996-05-10 | 2000-09-05 | フォード、モーター、カンパニー | ロウ組成 |

| JP2001219267A (ja) | 2000-02-09 | 2001-08-14 | Nippon Macdermid Kk | 錫−インジウム−ビスマスはんだ合金めっき層の形成方法 |

| WO2008016140A1 (en) | 2006-08-04 | 2008-02-07 | Panasonic Corporation | Bonding material, bonded portion and circuit board |

| JP2013521207A (ja) | 2010-03-02 | 2013-06-10 | サン−ゴバン グラス フランス | 電気接続素子を備えた窓ガラス |

| JP5534122B1 (ja) | 2014-02-04 | 2014-06-25 | 千住金属工業株式会社 | 核ボール、はんだペースト、フォームはんだ、フラックスコート核ボールおよびはんだ継手 |

| WO2016056656A1 (ja) | 2014-10-10 | 2016-04-14 | 石原ケミカル株式会社 | 合金バンプの製造方法 |

| JP2018079480A (ja) | 2016-11-14 | 2018-05-24 | 住友金属鉱山株式会社 | 低温用のBi−In−Sn系はんだ合金、それを用いた電子部品実装基板及びその実装基板を搭載した装置 |

| JP2021048391A (ja) | 2019-09-11 | 2021-03-25 | 株式会社新菱 | Sn−Bi−In系低融点接合部材および、その製造方法、ならびに半導体電子回路およびその実装方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2021048392A (ja) | 2021-03-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4753090B2 (ja) | はんだペースト、及び電子装置 | |

| US7780801B2 (en) | Flux composition and process for use thereof | |

| WO2012133598A1 (ja) | 鉛フリーはんだボール | |

| JP7091405B2 (ja) | Sn-Bi-In系低融点接合部材および、その製造方法、ならびに半導体電子回路およびその実装方法 | |

| JP2000260801A (ja) | 半導体素子およびその製造方法 | |

| KR20140119693A (ko) | 배선 기판 및 배선 기판의 제조 방법 | |

| Zheng et al. | Intermetallic growth on PWBs soldered with Sn3. 8Ag0. 7Cu | |

| JP7091406B2 (ja) | Sn-Bi-In系低融点接合部材、微小部材および半導体電子回路、バンプの製造方法ならびに半導体電子回路の実装方法 | |

| JPH08164496A (ja) | Sn−Zn系、Sn−Zn−Bi系はんだ及びその表面処理方法並びにそれを用いた実装品 | |

| WO2006017327A2 (en) | Electrocodeposition of lead free tin alloys | |

| WO2021049437A1 (ja) | Sn-Bi-In系低融点接合部材およびその製造方法、ならびに半導体電子回路およびその実装方法 | |

| WO2004105053A1 (ja) | 導電性ボール、電子部品の電極の形成方法および電子部品ならびに電子機器 | |

| JP2010040691A (ja) | 鉛フリーバンプ形成方法 | |

| EP3807930A1 (en) | Zinc-cobalt barrier for interface in solder bond applications | |

| JP7080867B2 (ja) | Sn-Bi-In系低融点接合部材、微小部材および半導体電子回路、バンプの製造方法ならびに半導体電子回路の実装方法 | |

| Gupte et al. | Effect of solder paste volume and reflow parameters on solder paste wicking and joint shear strength of Ni–Au-coated Cu spheres | |

| JP7080939B2 (ja) | 低融点接合部材およびその製造方法ならびに半導体電子回路およびその実装方法 | |

| WO2022050186A1 (ja) | Sn-In系低融点接合部材およびその製造方法ならびに半導体電子回路およびその実装方法 | |

| JP2007046087A (ja) | 金属ボール | |

| Karim et al. | Lead-free bump interconnections for flip-chip applications | |

| Azlina et al. | Comparison between SAC405 lead-free solders and EN (P) EPIG and EN (B) EPIG surface finishes | |

| TWI313923B (en) | Surface structure of semiconductor package substrate | |

| Adawiyah et al. | Solder volume effect on interfacial reaction between Sn-Ag-Cu/ENImAg substrate | |

| Alam et al. | Effect of 0.5 wt% Cu in Sn-3.5% Ag solder to retard interfacial reactions with the electroless Ni-P metallization for BGA solder joints application | |

| Azman et al. | The Effect of Isothermal Aging on the Intermetallic Growth between SN100C Lead-Free Solders and ENIG Surface Finish |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220112 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220112 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20220112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220208 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220310 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220405 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220422 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220510 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20220614 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20220615 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7091406 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |