JP6968172B2 - 可変利得信号増幅器、フロントエンドアーキテクチャ及び無線デバイス - Google Patents

可変利得信号増幅器、フロントエンドアーキテクチャ及び無線デバイス Download PDFInfo

- Publication number

- JP6968172B2 JP6968172B2 JP2019531591A JP2019531591A JP6968172B2 JP 6968172 B2 JP6968172 B2 JP 6968172B2 JP 2019531591 A JP2019531591 A JP 2019531591A JP 2019531591 A JP2019531591 A JP 2019531591A JP 6968172 B2 JP6968172 B2 JP 6968172B2

- Authority

- JP

- Japan

- Prior art keywords

- gain

- variable gain

- signal

- stage

- variable

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000007850 degeneration Effects 0.000 claims description 87

- 230000003321 amplification Effects 0.000 claims description 33

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 33

- 238000000034 method Methods 0.000 description 19

- 230000008569 process Effects 0.000 description 17

- 230000001413 cellular effect Effects 0.000 description 12

- 239000003990 capacitor Substances 0.000 description 11

- 230000008901 benefit Effects 0.000 description 5

- 238000004891 communication Methods 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 4

- 230000003213 activating effect Effects 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 230000008713 feedback mechanism Effects 0.000 description 2

- 238000001914 filtration Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 230000006399 behavior Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000007717 exclusion Effects 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 230000010363 phase shift Effects 0.000 description 1

- -1 resistors Substances 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000005236 sound signal Effects 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/38—Transceivers, i.e. devices in which transmitter and receiver form a structural unit and in which at least one part is used for functions of transmitting and receiving

- H04B1/40—Circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G3/00—Gain control in amplifiers or frequency changers

- H03G3/20—Automatic control

- H03G3/30—Automatic control in amplifiers having semiconductor devices

- H03G3/3052—Automatic control in amplifiers having semiconductor devices in bandpass amplifiers (H.F. or I.F.) or in frequency-changers used in a (super)heterodyne receiver

- H03G3/3068—Circuits generating control signals for both R.F. and I.F. stages

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G1/00—Details of arrangements for controlling amplification

- H03G1/0005—Circuits characterised by the type of controlling devices operated by a controlling current or voltage signal

- H03G1/0035—Circuits characterised by the type of controlling devices operated by a controlling current or voltage signal using continuously variable impedance elements

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G3/00—Gain control in amplifiers or frequency changers

- H03G3/20—Automatic control

- H03G3/30—Automatic control in amplifiers having semiconductor devices

- H03G3/3036—Automatic control in amplifiers having semiconductor devices in high-frequency amplifiers or in frequency-changers

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B7/00—Radio transmission systems, i.e. using radiation field

- H04B7/02—Diversity systems; Multi-antenna system, i.e. transmission or reception using multiple antennas

- H04B7/04—Diversity systems; Multi-antenna system, i.e. transmission or reception using multiple antennas using two or more spaced independent antennas

- H04B7/08—Diversity systems; Multi-antenna system, i.e. transmission or reception using multiple antennas using two or more spaced independent antennas at the receiving station

- H04B7/0882—Diversity systems; Multi-antenna system, i.e. transmission or reception using multiple antennas using two or more spaced independent antennas at the receiving station using post-detection diversity

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Amplifiers (AREA)

- Control Of Amplification And Gain Control (AREA)

- Moving Of The Head To Find And Align With The Track (AREA)

- Transmitters (AREA)

Description

本願は、2016年8月31日に出願された「デジェネレーションスイッチングブロック及び低損失バイパス機能を有するマルチ入力増幅器」との名称の米国仮出願第62/381,851号の優先権を主張する。その全体がすべての目的のために、参照として明示的に組み入れられる。

Claims (18)

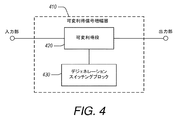

- 可変利得信号増幅器であって、

複数の入力部において複数の入力信号を受信して増幅された出力信号を生成するべく構成された可変利得段であって、個々の受信した信号が、異なる信号周波数帯域内の周波数を有する、可変利得段と、

前記可変利得段に結合されて前記可変利得段の複数の利得レベルを与えるべく構成されたデジェネレーションスイッチングブロックと、

前記可変利得段の前記複数の入力部に結合された中間利得モードフィードバックブロックと

を含み、

前記中間利得モードフィードバックブロックは、前記複数の利得レベルの部分集合のためにフィードバックを前記可変利得段に与えるように構成され、

前記可変利得信号増幅器は、少なくとも部分的に利得モードに基づいて、

前記可変利得段をバイパスして前記複数の入力部から前記可変利得信号増幅器の一つの出力部へと向かうバイパス経路と、

前記可変利得段を通過する増幅経路と

を選択的に与えるように構成される可変利得信号増幅器。 - 前記デジェネレーションスイッチングブロックはさらに、あつらえられたインピーダンスを前記可変利得段に与えるように構成される請求項1の可変利得信号増幅器。

- 前記あつらえられたインピーダンスは、前記あつらえられたインピーダンスを有するデジェネレーションスイッチングブロックに結合されない可変利得段と比べ、前記増幅された出力信号において改善された線形性を与えるように構成される請求項2の可変利得信号増幅器。

- 前記デジェネレーションスイッチングブロックは、前記複数の利得レベルの第1の利得レベルに対して第1のあつらえられたインピーダンスを与え、前記複数の利得レベルの第2の利得レベルに対して第2のあつらえられたインピーダンスを与えるように構成される請求項2の可変利得信号増幅器。

- 前記第1のあつらえられたインピーダンスは前記第2のあつらえられたインピーダンスよりも大きく、

前記第1の利得レベルは前記第2の利得レベルよりも低い請求項4の可変利得信号増幅器。 - 前記中間利得モードフィードバックブロック、及び前記デジェネレーションスイッチングブロックは、前記中間利得モードフィードバックブロック、及び前記デジェネレーションスイッチングブロックが存在しない増幅器と比べ、改善された線形性を前記増幅された出力信号に与える請求項1の可変利得信号増幅器。

- 前記可変利得段の前記複数の入力部に結合されたバイパスブロックをさらに含み、

前記バイパスブロックは、前記可変利得段を含まないバイパス経路を与えるべく、前記複数の利得レベルの低利得レベルにおいてアクティブにされるように構成される請求項1の可変利得信号増幅器。 - 前記バイパス経路は前記デジェネレーションスイッチングブロックを含まない請求項7の可変利得信号増幅器。

- 前記可変利得信号増幅器は、個々の入力ポートにおいて受信した信号を、他の受信した信号の増幅から独立して増幅するように構成される請求項1の可変利得信号増幅器。

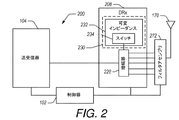

- フロントエンドアーキテクチャであって、

可変利得段、デジェネレーションスイッチングブロック、及び中間利得モードフィードバックブロックを含む可変利得信号増幅器と、

フィルタアセンブリと、

制御器と

を含み、

前記可変利得段は、複数の入力部において複数の入力信号を受信して増幅された出力信号を生成するべく構成され、個々の受信した信号が、異なる信号周波数帯域内の周波数を有し、

前記デジェネレーションスイッチングブロックは前記可変利得段に結合されて前記可変利得段の複数の利得レベルを与えるべく構成され、

前記中間利得モードフィードバックブロックは前記可変利得段の前記複数の入力部に結合され、

前記中間利得モードフィードバックブロックは、前記複数の利得レベルの部分集合のためにフィードバックを前記可変利得段に与えるように構成され、

前記フィルタアセンブリは、前記可変利得信号増幅器の選択入力部に周波数帯域を向けるように前記可変利得信号増幅器に結合され、

前記制御器は、複数の利得モードを与えるべく前記可変利得信号増幅器を制御するように実装され、

低利得モードにおいて、前記可変利得信号増幅器は信号を、前記可変利得段をバイパスする経路に沿って前記複数の入力部から前記可変利得信号増幅器の一つの出力部へと向けるフロントエンドアーキテクチャ。 - 前記デジェネレーションスイッチングブロックはさらに、あつらえられたインピーダンスを前記可変利得段に与えるように構成される請求項10のフロントエンドアーキテクチャ。

- 前記あつらえられたインピーダンスは、前記あつらえられたインピーダンスにより、前記デジェネレーションスイッチングブロックに結合されない可変利得段と比べ、前記増幅された出力信号において改善された線形性を与えるように構成される請求項11のフロントエンドアーキテクチャ。

- 前記デジェネレーションスイッチングブロックは、前記複数の利得レベルの第1の利得レベルに対して第1のあつらえられたインピーダンスを与え、前記複数の利得レベルの第2の利得レベルに対して第2のあつらえられたインピーダンスを与えるように構成される請求項11のフロントエンドアーキテクチャ。

- 無線デバイスであって、

ダイバーシティアンテナと、

フィルタアセンブリと、

可変利得信号増幅器と、

制御器と

を含み、

前記フィルタアセンブリは、前記ダイバーシティアンテナに結合されて信号を受信して周波数帯域を選択経路に沿うように向け、

前記可変利得信号増幅器は、

複数の入力部において複数の入力信号を受信して増幅された出力信号を生成するべく構成された可変利得段であって、個々の受信した信号が、異なる信号周波数帯域内の周波数を有する、可変利得段と、

前記可変利得段に結合されて前記可変利得段の複数の利得レベルを与えるべく構成されたデジェネレーションスイッチングブロックと、

前記可変利得段の前記複数の入力部に結合された中間利得モードフィードバックブロックと

を含み、

前記中間利得モードフィードバックブロックは、前記複数の利得レベルの部分集合のためにフィードバックを前記可変利得段に与えるように構成され、

前記制御器は、複数の利得モードを与えるべく前記可変利得信号増幅器を制御するように実装され、

低利得モードにおいて、前記可変利得信号増幅器は信号を、前記可変利得段をバイパスする経路に沿って前記複数の入力部から前記可変利得信号増幅器の一つの出力部へと向ける無線デバイス。 - 前記デジェネレーションスイッチングブロックはさらに、あつらえられたインピーダンスを前記可変利得段に与えるように構成される請求項14の無線デバイス。

- 前記デジェネレーションスイッチングブロックは、前記複数の利得レベルの第1の利得レベルに対して第1のあつらえられたインピーダンスを与え、前記複数の利得レベルの第2の利得レベルに対して第2のあつらえられたインピーダンスを与えるように構成される請求項15の無線デバイス。

- 前記複数の入力部それぞれからの信号が前記中間利得モードフィードバックブロックに入り一つのポイントから出るように構成される請求項1の可変利得信号増幅器。

- 前記一つのポイントは、出力整合ネットワークを介して前記出力部に結合される請求項17の可変利得信号増幅器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021174427A JP2022020699A (ja) | 2016-08-31 | 2021-10-26 | 増幅器のアーキテクチャ、フロントエンドモジュール及び無線デバイス |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201662381851P | 2016-08-31 | 2016-08-31 | |

| US62/381,851 | 2016-08-31 | ||

| PCT/US2017/049363 WO2018045024A1 (en) | 2016-08-31 | 2017-08-30 | Multi-input amplifier with degeneration switching block and low loss bypass function |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021174427A Division JP2022020699A (ja) | 2016-08-31 | 2021-10-26 | 増幅器のアーキテクチャ、フロントエンドモジュール及び無線デバイス |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019528657A JP2019528657A (ja) | 2019-10-10 |

| JP2019528657A5 JP2019528657A5 (ja) | 2020-10-08 |

| JP6968172B2 true JP6968172B2 (ja) | 2021-11-17 |

Family

ID=61243748

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019531591A Active JP6968172B2 (ja) | 2016-08-31 | 2017-08-30 | 可変利得信号増幅器、フロントエンドアーキテクチャ及び無線デバイス |

| JP2021174427A Pending JP2022020699A (ja) | 2016-08-31 | 2021-10-26 | 増幅器のアーキテクチャ、フロントエンドモジュール及び無線デバイス |

| JP2023075552A Pending JP2023100806A (ja) | 2016-08-31 | 2023-05-01 | 増幅器のアーキテクチャ、フロントエンドモジュール及び無線デバイス |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021174427A Pending JP2022020699A (ja) | 2016-08-31 | 2021-10-26 | 増幅器のアーキテクチャ、フロントエンドモジュール及び無線デバイス |

| JP2023075552A Pending JP2023100806A (ja) | 2016-08-31 | 2023-05-01 | 増幅器のアーキテクチャ、フロントエンドモジュール及び無線デバイス |

Country Status (9)

| Country | Link |

|---|---|

| US (4) | US10230417B2 (ja) |

| JP (3) | JP6968172B2 (ja) |

| KR (1) | KR102551718B1 (ja) |

| CN (1) | CN109845098B (ja) |

| DE (1) | DE112017004352T5 (ja) |

| GB (3) | GB2598209B (ja) |

| SG (1) | SG11201901799UA (ja) |

| TW (4) | TWI811981B (ja) |

| WO (1) | WO2018045024A1 (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106160673B (zh) * | 2016-06-30 | 2021-03-30 | 唯捷创芯(天津)电子技术股份有限公司 | 谐波抑制方法及相应的低噪声放大器、通信终端 |

| GB2598209B (en) * | 2016-08-31 | 2022-09-21 | Skyworks Solutions Inc | Multi-input amplifier with degeneration switching block and low loss bypass function |

| KR101912288B1 (ko) * | 2017-06-12 | 2018-10-29 | 삼성전기 주식회사 | 파워 증폭 시스템의 밴드 선택 스위치 장치 |

| US20200007098A1 (en) * | 2018-06-29 | 2020-01-02 | Qualcomm Incorporated | Dual-Mode Amplification by Varying a Load Impedance |

| US10700650B1 (en) * | 2019-01-08 | 2020-06-30 | Psemi Corporation | Configurable wideband split LNA |

| CN113366759A (zh) | 2019-01-08 | 2021-09-07 | 派赛公司 | 可配置的宽带分裂lna |

| US10951252B2 (en) | 2019-01-08 | 2021-03-16 | Psemi Corporation | 5G NR configurable wideband RF front-end LNA |

| WO2020204885A1 (en) * | 2019-03-29 | 2020-10-08 | Huawei Technologies Co. Ltd. | Programmable millimeter wave radar integrated circuit |

| JP2021016106A (ja) * | 2019-07-12 | 2021-02-12 | 株式会社東芝 | 高周波増幅回路 |

| US11245372B2 (en) | 2019-08-30 | 2022-02-08 | Skyworks Solutions, Inc. | Variable-gain amplifier with degeneration circuit |

| TWI733244B (zh) * | 2019-11-07 | 2021-07-11 | 瑞昱半導體股份有限公司 | 收發器裝置 |

| TWI756702B (zh) | 2020-06-02 | 2022-03-01 | 立積電子股份有限公司 | 切換電路 |

| US12212351B2 (en) * | 2020-12-23 | 2025-01-28 | Intel Corporation | Communication device |

| CN116897510A (zh) * | 2020-12-31 | 2023-10-17 | 天工方案公司 | 不使用开关的增益级退化电感器切换 |

| US20230082415A1 (en) * | 2021-09-16 | 2023-03-16 | Qorvo Us, Inc. | Phase and amplitude error correction in a transmission circuit |

| TWI799094B (zh) * | 2022-01-20 | 2023-04-11 | 瑞昱半導體股份有限公司 | 具有線性度補償機制的可變增益放大電路及方法 |

| CN115441839A (zh) * | 2022-09-16 | 2022-12-06 | 深圳飞骧科技股份有限公司 | 多频段低噪声放大器、集成电路芯片及电子设备 |

| CN115208338A (zh) * | 2022-09-16 | 2022-10-18 | 深圳飞骧科技股份有限公司 | 多频段低噪声放大器及通信设备 |

| CN115296620B (zh) * | 2022-09-29 | 2022-12-30 | 深圳飞骧科技股份有限公司 | 多频段可调增益的低噪声放大器 |

| CN115567013B (zh) * | 2022-10-20 | 2023-08-29 | 臻智微芯(广州)技术有限公司 | 一种基于旁路模式的低噪声放大器电路 |

| CN116015331B (zh) * | 2022-12-26 | 2023-08-08 | 成都爱科特科技发展有限公司 | 一种复杂电磁环境弱信号接收方法、装置及系统 |

| CN118508885A (zh) * | 2024-07-22 | 2024-08-16 | 荣耀终端有限公司 | 一种低噪声放大器、射频芯片以及通信设备 |

Family Cites Families (43)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB9928355D0 (en) * | 1999-12-01 | 2000-01-26 | Koninkl Philips Electronics Nv | Amplifier |

| US6586993B2 (en) * | 2000-11-08 | 2003-07-01 | Research In Motion Limited | Impedance matching low noise amplifier having a bypass switch |

| US6801089B2 (en) * | 2001-05-04 | 2004-10-05 | Sequoia Communications | Continuous variable-gain low-noise amplifier |

| US7113033B2 (en) * | 2002-01-31 | 2006-09-26 | Qualcomm Incorporated | Variable impedance load for a variable gain radio frequency amplifier |

| US7259629B2 (en) * | 2002-08-12 | 2007-08-21 | Nxp, B.V. | Variable gain amplifier with improved control characteristics linearity |

| US6930546B2 (en) * | 2003-09-26 | 2005-08-16 | International Business Machines Corporation | Bypass switch topology for low-noise amplifiers |

| GB2434494B (en) * | 2006-01-24 | 2008-02-06 | Toumaz Technology Ltd | Low noise amplifier |

| KR100732070B1 (ko) * | 2007-03-07 | 2007-06-27 | (주)에프씨아이 | 이득을 가변시킬 수 있는 저 잡음 증폭기 |

| US7486135B2 (en) | 2007-05-29 | 2009-02-03 | Telefonaktiebolaget Lm Ericsson (Publ) | Configurable, variable gain LNA for multi-band RF receiver |

| US7532070B2 (en) * | 2007-09-24 | 2009-05-12 | Intel Corporation | Analog variable gain amplifier with improved dynamic range characteristics |

| US7705682B2 (en) | 2007-09-27 | 2010-04-27 | Nanoamp Mobile, Inc. | Inductor sharing in radio frequency communications |

| JP5206689B2 (ja) * | 2007-12-17 | 2013-06-12 | パナソニック株式会社 | バイパス回路付増幅回路とこれを用いた電子機器 |

| JP2009290411A (ja) * | 2008-05-28 | 2009-12-10 | Nec Electronics Corp | 低雑音受信装置 |

| JP5296809B2 (ja) * | 2009-01-13 | 2013-09-25 | パナソニック株式会社 | 可変利得増幅器およびそれを備えた高周波信号受信装置 |

| CN101505140B (zh) * | 2009-03-04 | 2012-01-18 | 中国电力科学研究院 | 一种低噪声高增益-带宽乘积跨阻抗放大器 |

| US8022772B2 (en) | 2009-03-19 | 2011-09-20 | Qualcomm Incorporated | Cascode amplifier with protection circuitry |

| US7898325B2 (en) * | 2009-05-28 | 2011-03-01 | Avago Technologies Wireless Ip (Singapore) Pte. Ltd. | Amplifier with bypass switch |

| US20120206150A1 (en) * | 2009-08-27 | 2012-08-16 | Kyle David Holzer | Adjustable gain amplifier, automated test equipment and method for adjusting a gain of an amplifier |

| US20120013401A1 (en) * | 2010-07-14 | 2012-01-19 | Avago Technologies Wireless Ip (Singapore) Pte. Ltd. | Power amplifier with selectable load impedance and method of amplifying a signal with selectable load impedance |

| US8620242B2 (en) * | 2010-08-19 | 2013-12-31 | Broadcom Corporation | High performance transmitter preamplification chain with calibration feedback |

| US8310314B2 (en) * | 2010-09-06 | 2012-11-13 | Mediatek Inc. | Signal amplification circuits for receiving/transmitting signals according to input signal |

| PT2456068E (pt) * | 2010-11-22 | 2013-08-22 | Ericsson Telefon Ab L M | Amplificador de baixo ruído com circuito de reforço de impedância |

| US8649302B2 (en) * | 2011-02-15 | 2014-02-11 | Intel Mobile Communications GmbH | Receiver for receiving RF-signals in a plurality of different communication bands and transceiver |

| EP2557687B1 (en) | 2011-08-11 | 2018-06-13 | Telefonaktiebolaget LM Ericsson (publ) | Low-noise amplifier, receiver, method and computer program |

| CN102361435B (zh) * | 2011-10-28 | 2013-02-06 | 电子科技大学 | 一种可变增益宽带低噪声放大器 |

| US8737545B2 (en) * | 2011-12-14 | 2014-05-27 | Posedge Inc. | Receiver chain gain selection |

| US9154356B2 (en) * | 2012-05-25 | 2015-10-06 | Qualcomm Incorporated | Low noise amplifiers for carrier aggregation |

| US8913976B2 (en) * | 2012-10-23 | 2014-12-16 | Qualcomm Incorporated | Amplifiers with shunt switches |

| US9603187B2 (en) | 2012-11-14 | 2017-03-21 | Qualcomm Incorporated | Omni-band amplifiers |

| US9059665B2 (en) | 2013-02-22 | 2015-06-16 | Qualcomm Incorporated | Amplifiers with multiple outputs and configurable degeneration inductor |

| US9106185B2 (en) * | 2013-03-11 | 2015-08-11 | Qualcomm Incorporated | Amplifiers with inductive degeneration and configurable gain and input matching |

| US9035697B2 (en) * | 2013-03-15 | 2015-05-19 | Qualcomm Incorporated | Split amplifiers with improved linearity |

| US9124228B2 (en) | 2013-04-04 | 2015-09-01 | Qualcomm Incorporated | Amplifiers with boosted or deboosted source degeneration inductance |

| US9154087B2 (en) * | 2013-08-01 | 2015-10-06 | Qualcomm Incorporated | Amplifiers with configurable mutually-coupled source degeneration inductors |

| EP2874311B1 (en) * | 2013-11-15 | 2016-07-20 | Nxp B.V. | An amplifier circuit |

| US9271239B2 (en) * | 2014-02-14 | 2016-02-23 | Qualcomm Incorporated | Current-efficient low noise amplifier (LNA) |

| US9467104B2 (en) * | 2014-03-28 | 2016-10-11 | Qualcomm Incorporated | Single-input multiple-output amplifiers with simultaneous multiple gain modes |

| JP6029728B2 (ja) | 2014-10-31 | 2016-11-24 | スカイワークス ソリューションズ,インコーポレイテッドSkyworks Solutions,Inc. | 位相シフト部品を備えたダイバーシティ受信器フロントエンドシステム |

| US10050694B2 (en) * | 2014-10-31 | 2018-08-14 | Skyworks Solution, Inc. | Diversity receiver front end system with post-amplifier filters |

| US9337775B1 (en) * | 2014-12-05 | 2016-05-10 | Infineon Technologies Ag | System and method for a low noise amplifier module |

| US10181829B2 (en) * | 2015-07-02 | 2019-01-15 | Murata Manufacturing Co., Ltd. | Amplification circuit |

| GB2598209B (en) | 2016-08-31 | 2022-09-21 | Skyworks Solutions Inc | Multi-input amplifier with degeneration switching block and low loss bypass function |

| US9929701B1 (en) * | 2016-09-21 | 2018-03-27 | Psemi Corporation | LNA with programmable linearity |

-

2017

- 2017-08-30 GB GB2111131.5A patent/GB2598209B/en active Active

- 2017-08-30 JP JP2019531591A patent/JP6968172B2/ja active Active

- 2017-08-30 SG SG11201901799UA patent/SG11201901799UA/en unknown

- 2017-08-30 US US15/690,947 patent/US10230417B2/en active Active

- 2017-08-30 GB GB2111132.3A patent/GB2598210B/en active Active

- 2017-08-30 WO PCT/US2017/049363 patent/WO2018045024A1/en active Application Filing

- 2017-08-30 DE DE112017004352.2T patent/DE112017004352T5/de active Pending

- 2017-08-30 CN CN201780065096.1A patent/CN109845098B/zh active Active

- 2017-08-30 GB GB1904240.7A patent/GB2570229B/en active Active

- 2017-08-30 KR KR1020197009155A patent/KR102551718B1/ko active IP Right Grant

- 2017-08-31 TW TW111103841A patent/TWI811981B/zh active

- 2017-08-31 TW TW106129711A patent/TWI757329B/zh active

- 2017-08-31 TW TW111103840A patent/TWI814230B/zh active

- 2017-08-31 TW TW111103839A patent/TWI814229B/zh active

-

2019

- 2019-03-12 US US16/351,446 patent/US10530412B2/en active Active

-

2020

- 2020-01-07 US US16/736,777 patent/US10804951B2/en active Active

- 2020-10-13 US US17/069,745 patent/US11563460B2/en active Active

-

2021

- 2021-10-26 JP JP2021174427A patent/JP2022020699A/ja active Pending

-

2023

- 2023-05-01 JP JP2023075552A patent/JP2023100806A/ja active Pending

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6968172B2 (ja) | 可変利得信号増幅器、フロントエンドアーキテクチャ及び無線デバイス | |

| JP6853362B2 (ja) | 可変利得信号増幅器、フロントエンドアーキテクチャ及び無線デバイス | |

| JP6170114B2 (ja) | 可変利得増幅器を備えたダイバーシティ受信器フロントエンドシステム | |

| US20190273523A1 (en) | Filtering techniques | |

| US9698757B2 (en) | Analog baseband filtering apparatus of multimode multiband wireless transceiver and control method thereof | |

| JP2018042100A (ja) | 送信モジュール及び送受信モジュール | |

| CN117044102A (zh) | 具有不使用开关的退化切换的多输入放大器 | |

| JP6280905B2 (ja) | 受信システム、無線周波数モジュール及び無線デバイス | |

| TWI611663B (zh) | 具有彈性頻帶路由之分集接收器前端系統 | |

| WO2022147305A1 (en) | Gain stage degeneration inductor switching without the use of switches | |

| KR102035256B1 (ko) | 멀티모드 멀티밴드 무선 송수신기를 위한 아날로그 기저대역 필터 장치 및 그 제어 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200828 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200828 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20200828 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20200930 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20201013 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20210112 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210217 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210511 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210730 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210928 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20211026 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6968172 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |