JP6679317B2 - 信号供給回路及び表示装置 - Google Patents

信号供給回路及び表示装置 Download PDFInfo

- Publication number

- JP6679317B2 JP6679317B2 JP2016004077A JP2016004077A JP6679317B2 JP 6679317 B2 JP6679317 B2 JP 6679317B2 JP 2016004077 A JP2016004077 A JP 2016004077A JP 2016004077 A JP2016004077 A JP 2016004077A JP 6679317 B2 JP6679317 B2 JP 6679317B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- mode

- sub

- video data

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000006243 chemical reaction Methods 0.000 claims description 69

- 238000012546 transfer Methods 0.000 claims description 13

- 238000000034 method Methods 0.000 claims description 9

- 238000012545 processing Methods 0.000 description 36

- 238000010586 diagram Methods 0.000 description 32

- 102100023882 Endoribonuclease ZC3H12A Human genes 0.000 description 22

- 101710112715 Endoribonuclease ZC3H12A Proteins 0.000 description 22

- 238000005070 sampling Methods 0.000 description 18

- 239000013256 coordination polymer Substances 0.000 description 17

- 239000000758 substrate Substances 0.000 description 16

- 101150103187 Reg4 gene Proteins 0.000 description 12

- 239000010409 thin film Substances 0.000 description 12

- 101100412401 Rattus norvegicus Reg3a gene Proteins 0.000 description 9

- 101150044140 Slc7a5 gene Proteins 0.000 description 9

- 230000005540 biological transmission Effects 0.000 description 9

- 239000004973 liquid crystal related substance Substances 0.000 description 9

- 102100036464 Activated RNA polymerase II transcriptional coactivator p15 Human genes 0.000 description 8

- 101000713904 Homo sapiens Activated RNA polymerase II transcriptional coactivator p15 Proteins 0.000 description 8

- 229910004444 SUB1 Inorganic materials 0.000 description 8

- 229910004438 SUB2 Inorganic materials 0.000 description 7

- 101100311330 Schizosaccharomyces pombe (strain 972 / ATCC 24843) uap56 gene Proteins 0.000 description 7

- 101150018444 sub2 gene Proteins 0.000 description 7

- 101100120298 Rattus norvegicus Flot1 gene Proteins 0.000 description 6

- 101100412403 Rattus norvegicus Reg3b gene Proteins 0.000 description 6

- -1 Lat3 Proteins 0.000 description 5

- 101100454355 Rattus norvegicus Slc7a8 gene Proteins 0.000 description 5

- 101150095230 SLC7A8 gene Proteins 0.000 description 5

- 101150085091 lat-2 gene Proteins 0.000 description 5

- 125000004122 cyclic group Chemical group 0.000 description 4

- 238000000926 separation method Methods 0.000 description 4

- 230000006870 function Effects 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 101100191136 Arabidopsis thaliana PCMP-A2 gene Proteins 0.000 description 2

- 101100048260 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) UBX2 gene Proteins 0.000 description 2

- 102100029469 WD repeat and HMG-box DNA-binding protein 1 Human genes 0.000 description 2

- 101710097421 WD repeat and HMG-box DNA-binding protein 1 Proteins 0.000 description 2

- 230000001360 synchronised effect Effects 0.000 description 2

- 238000003491 array Methods 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000003786 synthesis reaction Methods 0.000 description 1

- 230000002194 synthesizing effect Effects 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2074—Display of intermediate tones using sub-pixels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2003—Display of colours

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2092—Details of a display terminals using a flat panel, the details relating to the control arrangement of the display terminal and to the interfaces thereto

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0452—Details of colour pixel setup, e.g. pixel composed of a red, a blue and two green components

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0857—Static memory circuit, e.g. flip-flop

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/0666—Adjustment of display parameters for control of colour parameters, e.g. colour temperature

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3614—Control of polarity reversal in general

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

Description

(1)W映像信号を生成するために新たな変換回路を必要とする。また

(2)変換回路を設けた場合1画素を構成する副画素が、3個(R、G及びB副画素)から4個(R、G、B及びW副画素)に増えるために、駆動に必要なデータ数が増加する。この結果、データの送信時間が長くなるとともに、消費電力も増大する、

(3)勿論、データ処理プロセスも煩雑となる。

前記画素を構成する複数の副画素用のデジタルデータを前記メモリに供給する、第1モードと第2モードとに選択的に切り替えられ、

第1モードは、外部からn個の前記副画素に対応する第1映像データを受け取り、前記第1映像データに基づいてn個の前記副画素のためのデジタルデータを前記メモリに供給するモードであり、

第2モードは、外部から前記n個よりも少ないm個の前記副画素に対応する第2映像データを受け取り、前記第2映像データに基づいてn個の前記副画素のためのデジタルデータを前記メモリに供給するモードである、信号供給回路を提供するものである。

表示エリアDAは、第1基板SUB1と第2基板SUB2との間に液晶層LQが保持された領域に相当し、例えば、四角形状であり、この領域にはマトリクス状に配置された複数の副画素PX(PX11,PX12,・・・・)が配置されている。

各ゲート線G(G1〜Gn)は、表示エリアDAの外側に引き出され、ゲート線駆動回路(第1駆動回路)GDに接続されている。各信号線S(S1〜Sm)は、表示エリアDAの外側に引き出され、ソース線駆動回路(第2駆動回路)SDに接続されている。第1駆動回路GD及び第2駆動回路SDは、例えばその少なくとも一部が第1基板SUB1上に形成され、制御装置(駆動ICチップ或いは液晶ドライバと称される場合もある)CPと接続されている。

制御装置CPは、第1駆動回路GD及び第2駆動回路SDを制御するために、クロック及びタイミングパルス生成回路(コントローラ或いはシーケンサと称してもよい)を内蔵し、表示パネルPNLを駆動するのに必要な信号を供給する信号供給源として機能する。制御装置CPは、信号供給回路110を含む。信号供給回路110は、第2駆動回路SDに映像データを与えるとき、映像データのタイプに応じて、動作モードを切り替えるモード制御回路(後述する)を含む。映像データのタイプとは、後で詳しく説明するが、映像データが例えば、赤(R)、緑(G)、青(B)の映像データである場合、赤(R)、緑(G)、青(B)、白(W)の映像データである場合、赤(R)、緑(G)、青(B)、ダミー(DUM)の映像データである場合、或いは単なる1ビットの映像データである場合などがある。

図示した例では、制御装置CPは、表示パネルPNLの表示エリアDAの外側において、第1基板SUB1上に実装されている。

図2Aは、メモリを有する前記副画素PX(又は画素)の構成を示している。この副画素PXにおいて、信号線SにスイッチSW0の一端が接続され、このスイッチSW0の他端がメモリM0に接続されている。メモリM0は、例えばインバータIN1、IN2を有し、このインバータIN1、IN2は逆方向に並列接続されている。インバータIN1の入力端子(インバータIN2の出力端子)は、スイッチSW1の制御端子に接続されている。またインバータIN1の出力端子(インバータIN2の入力端子)は、スイッチSW2の制御端子に接続されている。スイッチSW1の入力端子は、第1の信号ラインPoaに接続され、出力端子は、液晶層に形成された表示素子の画素電極PEに接続されている。またスイッチSW2の入力端子は、第2の信号ラインPobに接続され、出力端子は、前記画素電極PEに接続されている。第1の信号ラインPoaには、第1の信号(表示用信号)xFRPが供給され、第2の信号ラインPobには、第2の信号(非表示用信号)FRPが入力している。これらの第1の信号xFRPと第2の信号FRPは、互いに逆位相の関係となる交流信号であり、図1で説明した制御装置CPで生成されている。前記画素電極PEに対向する共通電極CEには、制御装置CPから共通信号VCOMが供給されている。共通信号VCOMは、第2の信号FRPと同位相の信号交流信号である。

ここで、メモリM0にデータ“0”が保持されたとする。すると、スイッチSW1がオフし、スイッチSW2がオンする。このため、図4の時間t1〜t2に示すように、画素電極PEに第2の信号FRPが印加され、共通電極CEに共通信号VCOMが印加される。このときは第2の信号FRPと共通信号VCOMとは、同位相の関係にあるから、画素電極PEと共通電極CEの間は、低い電位差となる。この時、表示素子は非表示状態を形成する。

制御装置CP内の表示電位制御回路126は、白、黒反転点灯やネガ、ポジ反転点灯などの特殊表示状態を得る際に、図2A、図2B、図3で説明した第1の信号xFRP又は第2の信号FRPを変化させて画素電極に印加してもよい。

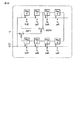

シリアルパラレル変換回路1110は、スイッチSW11、オア回路OR1を有する。初期値入力端子Pからデータ“1”が入力され、スイッチSW11が制御データCont_Sigによりオンされた場合、レジスタReg1にデータ“1”がラッチされる。レジスタReg1にデータ“1”がラッチされた後は、スイッチSW11はオフされる。レジスタReg1の出力は、レジスタReg2に入力可能であり、レジスタReg2の出力は、レジスタReg3に入力可能であり、レジスタReg3の出力は、レジスタReg4に入力可能に構成されている。レジスタReg1に入力されたデータ“1”は、入力端子1102に入力するクロックにより、順次レジスタReg2、レジスタReg3、レジスタReg4に順次転送される。なお複数のレジスタが直列接続された回路は、レジスタ直列回路或いはカウンタ回路と称されてもよい。

ラッチ回路Lat1、Lat2、Lat3、Lat4の出力データD1、データD2、データD3、データD4は、ラインデータ生成回路1120のデータ変換部Dconに入力されて、R、G、B、W信号に変換される。

ラインデータ生成回路1120のデータ変換部Dcon及びレジスタReg11は、入力端子1104からのタイミングパルスTimによりデータの出力タイミング及びデータの転送タイミングが制御される。データ変換部Dconから出力された、R、G、B、W信号は、レジスタReg11からのラッチパルスに基づいて、ラッチ回路Lat11、Lat12、Lat13、Lat14・・・・・にラッチされる。図7では4つのラッチ回路Lat11、Lat12、Lat13、Lat14を示しているが、実際には、1水平ライン分のデータをラッチするラッチ回路が設けられている。

スイッチSW41、スイッチSW42のいずれか一方がオンされるが、そのオンオフ制御は、セレクタ1132からの切り替え信号により実施される。また、各スイッチSW31,SW32,SW33、SW34のオン及びオフに関してもセレクタ1132からの切り替え信号により実施される。

なお、図11Aにおいて、(*1)で示している記述は、次の事を意味する。外部から赤表示のためのデータが入力している1ビットモードにおいては、赤のみの表示が可能である。或いは色フィルタとして白があるときは白のみの表示も可能である。さらにまた表示パネルの色フィルタが、シアン、マゼンタ、黄のフィルタで構成されている場合もある。このような場合、1ビットモードにおいては、マゼンタのみの表示、黄のみの表示を可能とすることができる。このときは、スイッチSW31の出力が、振り分け回路1134において振り分けられ、マゼンタ、或いは黄のフィルタを有する副画素に供給される。

なお、図11Bにおいて、(*2)で示している記述は、次の事を意味する。外部から緑表示のためのデータが入力している1ビットモードにおいては、緑のみの表示が可能である。或いは色フィルタとして白があるときは白のみの表示も可能である。さらにまた表示パネルの色フィルタが、シアン、マゼンタ、黄のフィルタで構成されている場合もある。このような場合、1ビットモードにおいては、シアンのみの表示、黄のみの表示を可能とすることができる。このときは、スイッチSW31の出力が、振り分け回路1134において振り分けられ、シアン、或いは黄のフィルタを有する副画素に供給される。

なお、図11Cにおいて、(*3)に示している記述は、次の事を意味する。外部から青表示のためのデータが入力している1ビットモードにおいては、青のみの表示が可能である。或いは色フィルタとして白があるときは白のみの表示も可能である。さらにまた表示パネルの色フィルタが、シアン、マゼンタ、黄のフィルタで構成されている場合もある。このような場合、1ビットモードにおいては、シアンのみの表示、マゼンタのみの表示を可能とすることができる。このときは、スイッチSW31の出力が、振り分け回路1134において振り分けられ、シアン、或いはマゼンタのフィルタを有する副画素に供給される。

なお、図11Dにおいて、(*4)で示している記述は、次の事を意味する。外部から白表示のためのデータが入力している1ビットモードにおいては、白のみの表示が可能である。色フィルタを有する表示パネルが使用されている場合は、振り分け回路1134が白フィルタの位置にデータを出力する。さらにまた表示パネルの色フィルタが、R、G、Bであったり、或いはシアン、マゼンタ、黄のフィルタで構成されている場合は、振り分け回路1134がそれぞれのフィルタに対して、例えばすべてデータ“1”を出力する。

4ビットモードでは、シリアルデータには映像データR,G,B,Wが含まれる。よって、4ビットモードでは、映像データR,G,B,Wを4サイクル分シフトさせるためには、16個のクロックを必要とする(図12(a))。

上記したように実施形態によると、副画素にメモリ出力が供給される表示装置に用いられる信号供給回路110が特徴的な機能を備えている。この信号供給回路110は、動作モード制御するモード制御回路1103を含む。

図13は、図10に示したセレクタ1132に与えられる制御データCont_Sigと複数のビットモードとの関係を示している。制御データCont_Sigは、例えば2ビットM1,M2を含み、第1の4ビットモード(R、G、B、W)のときは、(M1,M2)=(0,0)である。第2の4ビットモード(R、G、B、DUM)のときは、(M1,M2)=(0,1)である。3ビットモード(R、G、B)のときは、(M1,M2)=(1,0)である。1ビットモード(RorGorBorW)のときは、(M1,M2)=(1,1)である。

)を出力する。振り分け回路1134は、(C1,C2,C3)=(1,1,1)のときは白と判断する。この時は、出力ラインR、G、B、Wに対して(1,1,1,1)

)を出力する。

ところで一般にデジタルデバイスで処理されるデータは、バイト単位(例えば8ビット単位、16ビット単位、32ビット単位等)で取り扱われることが多い。このため、入力端子1103に入力するシリアルデータも8ビット単位で区分することができる。

図16には、伝送ラインなどで各種のシリアルデータを伝送する伝送形態の一例を示している。伝送ラインにおいて、映像データ、制御データ、アドレスデータ、ダミーデータなどが一定のルールで伝送される。SCSは、あるまとまったシリアルデータが伝送される期間を指定する期間指定信号(同期信号と称してもよい)である。SIは、シリアルデータであり、モード制御データ(M0、M1・・・M5)、ゲートラインアドレス指定データ(AG9、AG8、AG7、・・・AG0)、映像データ(D1R、D1G,D1B・・・・DnB)、ダミーデータ(・・・・)、その他などが含まれる。さらにデータの境界を示す同期クロック、エラー訂正コードなどが含まれてもよい。SCLKは、シリアルクロック(或いはシステムクロック)であり、シリアルデータに同期しており、シリアルデータをサンプリングすることができる。上記のシリアルデータを受け取るシリアルデータ処理部では、8ビット単位のシリアルデータを判断し、映像データ、制御データ、アドレス指定データなどを分離する。映像データは、後述するデータ変換部(データ制御部と称してもよい)に伝送される。制御データ、アドレス指定データなどは、制御装置CP内で出力タイミングなどが調整され、信号供給回路110、ゲート線駆動回路GDなどに送られる。

シリアルデータ処理回路2200の内部には、データ分離回路2201が設けられている。データ分離回路2201は、同期信号SCS及びシリアルクロックSCLKを利用して、モード制御データ(M0、M1・・・M5)、ゲートラインアドレス指定データ(AG9、AG8、AG7、・・・AG0)、映像データ(D1R、D1G,D1B・・・・DnB)、ダミーデータ(・・・・)、などを分離する。

モード制御データ(M0、M1・・・M5)は、4ビットモード、3ビットモード、1ビットモードなどを指定するデータであり、シリアルデータ処理回路2200及びデータ変換部2300における映像データの処理形態を決定するために利用される。ゲートラインアドレス指定データ(AG9、AG8、AG7、・・・AG0)は、映像データが副画素に書き込まれる際に、ゲート線駆動回路GD(図1に示した)がゲート線G(G1〜Gn)のいずれかを選択するために利用される。

シリアルデータ処理回路2200においては、シリアルで入力される映像データが、パラレルデータD1〜D8(データには、モードに応じてダミーデータが含まれる場合もある)に変換されて出力される。パラレルデータD1〜D8は、データ変換部2300に入力され一旦ラッチされる。データ変換部2300は、振り分け回路2301を含む。振り分け回路2301は、データ変換部2300内部にラッチされた各データを、適切なカラーの副画素に振り分けて、後段の水平ライン分を保持するラッチ回路に出力する。即ち、図7、図8、図9に示したように、振り分けられた各データは、1水平ライン分の副画素データを保持するラッチ回路群に出力される。

入力端子2103は、ラッチ回路Lat21−Lat28のデータ入力端子に対して、スイッチSW31を介して接続されている。このスイッチSW31は、図16に示した映像データ(D1R、D1G,D1B・・・・DnB)が入力端子2103に入力したときにオンとなる。またスイッチSW32は、レジスタReg21に初期値“1”を入力するためと、8ビット単位のサイクルでレジスタの出力“1”を巡回させるために利用される。レジスタReg21−Reg28は、シリアルクロックSCLKと同相のクロックで駆動されるが、図18では省略している。

一方、セレクタSEL1は、サンプリングパルスSP1を選択するように制御される。したがって、レジスタReg1からのサンプリングパルスSP1が採用され、4つのシリアルクロックSCLK毎に、ラッチ回路Lat41−Lat48にラッチパルスが供給される。また、シリアルデータ処理回路2200から出力されるデータは、データD1、D2、D3、D4、D5、D6、D7、D8、D1、D2、D3、D4、D5、D6、D7、D8、・・・と順次8ビット単位が繰り返しでラッチされ、そのデータ内容もR、G、B、W、R、G、B、W、R、G、B、W、R、G、B、W、・・・・の繰り返しである。よって、4つのリアルクロックSCLK毎に、データがラッチされた場合、各ラッチタイミング毎に、(1回目)R、G、B、W、(2回目)R、G、B、W、・・・・と8ビットシリアル伝送に同期した映像データを得ることができる。

一方、セレクタSEL1は、このときもサンプリングパルスSP1を選択するように制御される。したがって、レジスタReg1からのサンプリングパルスSP1が採用され、この場合は3つのシリアルクロックSCLK毎に、ラッチ回路Lat41−Lat48にラッチパルスが供給される。また、シリアルデータ処理回路2200から出力されるデータは、データD1、D2、D3、D4、D5、D6、D7、D8、D1、D2、D3、D4、D5、D6、D7、D8、・・・と順次8ビット単位が繰り返しでラッチされ、そのデータ内容は、R、G、B、R、G、B、R、G、B、R、G、B、・・・・の繰り返しである。そして、3つのシリアルクロックSCLK毎に、データがラッチされた場合、各ラッチタイミング毎に、(1回目)R、G、B、(2回目)R、G、B、・・・・の映像データを得ることができる。ここで、8ビット単位でシリアル伝送される映像データと、ラッチ回路Lat41−Lat48でラッチされるデータD1、D2、D3、D4、D5、D6、D7、D8との関係は、次のような関係にある。3つの映像データR、G、Bに対して伝送単位が8ビットであると、その最少公倍数24、つまり24ビット(8ビットの3サイクル)が同期サイクルとなる。つまり、例えばデータD1、D2、D3、D4、D5、D6、D7、D8に同じパターンの映像データR、G、B、R、G、B、R、Gが現れるのは、24ビットサイクルとなる。

したがって、3ビットモードのときは、データ振り分け回路2301の動作モードは、24ビットサイクルが考慮されて、データD1、D2、D3、D4、D5、D6、D7、D8をそれぞれR、G、Bの出力端子へ振り分けるモードが採用される。図20Bの例では、例えばR出力端子の場合、D4、D7、D2、D5、D8、D3、D6、D1、・・・の順でR出力端子へデータが選択されて出力される。

1ビットモードの場合は、シリアルデータ処理回路2200から出力されるデータは、データD1、D2、D3、D4、D5、D6、D7、D8の何れかが1でもよいが、例えばデータD1が伝送データ“1”とされ、他は“0”として取り決められる。これにより、振り分け回路2301は、データD1を選択する。振り分け回路2301は、白モード或いは黒モードに応じて、すべての出力端子R、G、Bに“0”又は“1”同時に出力する。或いは、振り分け回路2301は、1ビットモードとカラー指定情報がある場合、カラー指定情報に応じて、出力端子R、又はG,又はBに“1”を出力する。

上記の構成によると、レジスタ直列回路が、データ“1”を転送する場合、8段系路又は6段系路をスイッチ切り替えにより得ることができる。即ち、レジスタReg21−レジスタRge28−レジスタReg21・・・の順でデータ“1”が巡回する8段系路、又は、レジスタReg21−レジスタReg23−レジスタReg26、Reg27、Reg28、Reg21、・・・・の順でデータ“1”が巡回する6段系路である。レジスタの8段は、4の倍数であるから、4ビットモードのときに利用すると便利である。またレジスタの6段は、3の倍数であるから、3ビットモードのときに利用すると便利である。

図24Bは、図23に示した信号供給回路110が基本3ビットモード(6ビットモードと称してもよい)で動作しているとき、ラッチ回路Lat21−Lat26からの出力データD1−D6と、データ変換部2300におけるデータラッチタイミングとラッチデータとの関係を示している。1回のラッチにより3つのデータD1−D3がラッチされ、次のラッチにより3つのデータD4−D6がラッチされる。また次のラッチにより3つのデータD1−D3がラッチされ、この次のラッチにより3つのデータD4−D6がラッチされ、このような動作が繰り替えされる。3ビットモードは、映像データR、G、Bの入力に対して適用される。

シリアルデータ処理回路が1ビットモードで動作するときは、例えば振り分け回路2301は、制御信号(振り分けモード切替信号、カラー指定情報も含む)に応じて、自動的にR、G、B、Wの何れか1つ、又は複数の組み合わせ出力に切り替わる。このとき、レジスタReg21−Reg28、Lat21−Lat28は、電源節約のために停止してもよい。

上記した実施形態によると、振り分け回路2301における振り分け処理の制御が簡単となる。

レジスタReg1−レジスタReg8から出力される各サンプリングクパルス(ラッチパルス)は、ラッチ回路Lat1−ラッチ回路Lat8のラッチパルス入力端子に供給される。ラッチ回路Lat1−ラッチ回路Lat8のデータ入力端子には、それぞれシリアルデータ処理部2200で取り出された映像データD1−D8がそれぞれ入力される。

このときは、ラッチ回路Lat1−Lat8からの出力データD1−D8と、データ変換部2300におけるデータラッチタイミングとラッチデータとの関係は、先の図24Aで示した関係と同じである。1回のラッチにより4つのデータD1−D4がラッチされ、次のラッチにより4つのデータD5−D8がラッチされる。また次のラッチにより4つのデータD1−D4がラッチされ、この次のラッチにより4つのデータD5−D8がラッチされ、このような動作が繰り替えされる。4ビットモードは、映像データR、G、B、W(又はWがダミーデータ)の入力に対して適用される。

このときは、ラッチ回路Lat1−Lat8からの出力データD1−D8と、データ変換部2300におけるデータラッチタイミングとラッチデータとの関係は、先の図24Bで示した関係と同じである。1回のラッチにより3つのデータD1−D3がラッチされ、次のラッチにより3つのデータD4−D6がラッチされる。また次のラッチにより3つのデータD1−D3がラッチされ、この次のラッチにより3つのデータD4−D6がラッチされ、このような動作が繰り替えされる。3ビットモードは、映像データR、G、Bの入力に対して適用される。

信号供給回路110が1ビットモードで動作するときは、例えば振り分け回路2301は、制御信号(振り分けモード切替信号、カラー指定情報も含む)に応じて、自動的にR、G、B、Wの何れか1つ、又は複数の組み合わせ出力状態に切り替わる。このとき、データ変換部2300は、電源節約のために停止してもよい。

上記した実施形態によると、振り分け回路2301における振り分け処理の制御が簡単となる。

副画素がマトリックス状に配列された表示パネル対して、前記副画素にデジタルデータを供給する信号供給回路であって、前記信号供給回路は、

第1モードでは、外部からn個の副画素に対応する第1映像データを受け取り、前記第1映像データに基づいてn個の前記副画素のためのデジタルデータを前記表示パネルに供給するモードの動作状態を形成し、

第2モードは、外部から前記n個よりも少ないm個の前記副画素に対応する第2映像データを受け取り、前記第2映像データに基づいてn個の前記副画素のためのデジタルデータを前記表示パネルに供給するモードの動作状態を形成するものである。

(2)前記第1及び第2の映像データはシリアルデータであり、上記(1)記載の信号供給回路は、前記シリアルデータをパラレルデータに変換するためのラッチパルスを生成するために、複数のレジスタを直列接続したレジスタ直列回路を有する(例えば図7、図8、図9、図18、図19、図22、図23、図25、図26)。

(3)上記(2)記載の前記レジスタ直列回路は、前記第1モードにおけるラッチパルスと、前記第2モードにおけるラッチパルスを選択的に得るために、最終段のレジスタ出力を初段のレジスタのデータ入力端子に帰還する第1の系路と、最終段よりも前の段のレジスタ出力を前記初段のレジスタのデータ入力端子に帰還する第2の系路とを切り替えるスイッチを備える(例えば図7、図8、図9、図19、図22、図23、図25、図26)。

(4)上記(2)記載の前記レジスタ直列回路から出力される複数のラッチパルスは、それぞれ前記シリアルデータをラッチする複数のラッチ回路のラッチパルス入力端子に供給される(図7−図9、図18、図19、図23、図25、図26)。

(5)上記(2)記載のレジスタ直列回路は、8ビット単位で入力するシリアルデータをパラレルデータに変換するためのシリアルデータ処理回路に設けられている(例えば図18、図22、図23)。

(6)上記(2)記載のレジスタ直列回路は、8ビット単位で入力するシリアルデータをパラレルデータに変換した後の任意のデータを、ラッチするためのラッチパルスを生成するラッチパルス生成回路に用いられる(図19、図25、図26)。

(7)上記(5)又は(6)記載の8ビット単位で入力するシリアルデータは、さらに、映像データの他にアドレス指定データ、モード制御データを含む。

(8)上記(7)記載の前記信号供給回路は、前記モード制御データに基づいて前記第1モード、前記第2モードを切り替える。

(9)上記(1)記載のシリアルデータは、R、G、B、Wの映像データ又はR、G、Bの映像データのいずれかを含む。

(10)上記(1)記載の信号供給回路は、さらに、自動的にダミーデータを生成する回路を含む。

Claims (13)

- 複数の副画素からなる画素にメモリを有する表示装置に用いられ、動作モード制御するモード制御回路を含む信号供給回路であって、

前記モード制御回路により、

前記複数の副画素用のデジタルデータを前記メモリに供給する、第1モードと第2モードとに選択的に切り替えられ、

第1モードは、外部からn個の前記副画素に対応する第1映像データを受け取り、前記第1映像データに基づいてn個の前記副画素用のデジタルデータを前記メモリに供給するモードであり、

第2モードは、外部から前記n個よりも少ないm個の前記副画素に対応する第2映像データを受け取り、前記第2映像データに基づいてn個の前記副画素用のデジタルデータを前記メモリに供給するモードであり、

前記第1映像データ及び前記第2映像データはシリアルデータであり、前記シリアルデータを前記複数の副画素に対応するデジタルデータにパラレル変換するパラレル変換部を有し、

前記パラレル変換部は、n個のラッチ回路と、

前記ラッチ回路のラッチタイミングを制御するn個の制御レジスタと、を備え、

前記第1モードのときn個の前記制御レジスタで、前記制御レジスタの転送データの巡回路を構成し、前記第2モードのときm個の制御レジスタで、前記制御レジスタの転送データの巡回路を構成する、信号供給回路。 - 前記モード制御回路が、前記第1映像データと前記第2映像データを受け取ることに先行して、モード制御データを受け取る、請求項1記載の信号供給回路。

- 前記n個のラッチ回路のパラレル出力データを前記n個の前記複数の副画素用のデジタルデータに変換するラインデータ変換回路と、

を備える、請求項1又は2に記載の信号供給回路。 - 前記モード制御回路が、前記第2モードのとき前記nの制御レジスタのうちの一部の制御レジスタの動作を非アクティブに切り替える、請求項1ないし3のいずれか1項に記載の信号供給回路。

- 前記第1モードの前記第1映像データは、赤、緑、青、白用の映像データから成り、

前記第2モードの前記第2映像データは、赤、緑、青用の映像データから成り、

前記第2モードでは前記ラインデータ変換回路が、前記赤、緑、青用の映像データから、白用の映像データを生成する、請求項3と請求項4のいずれか1項に記載の信号供給回路。 - 前記第1モードの前記第1映像データは、赤、緑、青、白用の映像データ又はシアン、マゼンタ、黄、白用の映像データから成る、

請求項1と請求項2のいずれか1項に記載の信号供給回路。 - 前記第1モード又は前記第2モードにおいて、前記パラレル変換部は、前記n個の前記第1映像データ又は前記m個の前記第2映像データを1個の映像データ単位に変換する、請求項1に記載の信号供給回路。

- 画素にメモリを有する表示装置であって、

前記画素を構成する複数の副画素と、

前記複数副画素にデジタルデータを供給する信号供給回路と、

前記デジタルデータが供給される、前記画素に配置されたメモリと、

前記メモリに記憶された前記デジタルデータによって電位が供給される画素電極と、を備え、

前記信号供給回路は、第1モードと第2モードとを有し、

第1モードは、外部からn個の前記副画素の第1映像データを受け取り、前記第1映像データに基づいてn個の前記副画素用のデジタルデータを前記メモリに供給するモードであり、

第2モードは、外部から前記n個よりも少ないm個の前副画素に対応する第2映像データを受け取り、前記第2映像データに基づいてn個の前記複数の副画素用のデジタルデータを前記メモリに供給するモードであり、

前記第1映像データ及び前記第2映像データはシリアルデータであり、前記シリアルデータを前記複数の副画素に対応するデジタルデータにパラレル変換するパラレル変換部を有し、

前記パラレル変換部は、n個のラッチ回路と、

前記ラッチ回路のラッチタイミングを制御するn個の制御レジスタと、を備え、

前記第1モードのときn個の前記制御レジスタで巡回路を構成し、前記第2モードのときm個の制御レジスタで巡回路を構成する、

表示装置。 - 前記複数の副画素としての第1副画素と第2副画素と第3副画素と第4副画素と、を備え、

前記第1モードは、前記第1副画素と前記第2副画素と前記第3副画素と前記第4副画素に対応した前記第1映像データを受け取り、前記第1映像データに基づいて前記第1副画素と前記第2副画素と前記第3副画素と前記第4副画素用のデジタルデータを前記メモリに供給するモードであり、

前記第2モードは、前記第1副画素と前記第2副画素と前記第3副画素に対応した前記第2映像データを受け取り、前記第2映像データに基づいて前記第1副画素と前記第2副画素と前記第3副画素と前記第4副画素用のデジタルデータを前記メモリに供給するモードである、請求項8に記載の表示装置。 - 前記複数の副画素に対応するデジタルデータを前記メモリに供給する第3モードをさらに有し、

前記第3モードは、外部から前記第2映像データを受け取り、前記第2映像データに基づいてm個の前記副画素のデジタルデータを前記メモリに供給するモードである、請求項8と請求項9のいずれかに記載の表示装置。 - 前記複数の副画素に対応するデジタルデータを前記メモリに供給する第3モードをさらに有し、

前記第3モードは、外部から前記第2映像データを受け取り、前記第2映像データに基づいて一部の前記複数の副画素のデジタルデータを供給するモードであり、

前記第3モードは、前記第1副画素と前記第2副画素と前記第3副画素に対応した前記第2映像データを受け取り、前記第2映像データに基づいて前記第1副画素と前記第2副画素と前記第3副画素用のデジタルデータを前記メモリに供給するモードである、請求項8又は9に記載の表示装置。 - 外部からのビット制御信号によって、前記第2モードと前記第3モードとを切り替える、請求項10乃至11のいずれかに記載の表示装置。

- 外部からのラッチ数制御信号によって、前記第1モードと前記第2モードとを切り替える、請求項8乃至12のいずれかに記載の表示装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016004077A JP6679317B2 (ja) | 2016-01-13 | 2016-01-13 | 信号供給回路及び表示装置 |

| US15/405,616 US10311772B2 (en) | 2016-01-13 | 2017-01-13 | Signal supply circuit and display device |

| US16/368,365 US10762827B2 (en) | 2016-01-13 | 2019-03-28 | Signal supply circuit and display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016004077A JP6679317B2 (ja) | 2016-01-13 | 2016-01-13 | 信号供給回路及び表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017125903A JP2017125903A (ja) | 2017-07-20 |

| JP2017125903A5 JP2017125903A5 (ja) | 2018-12-13 |

| JP6679317B2 true JP6679317B2 (ja) | 2020-04-15 |

Family

ID=59274972

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016004077A Expired - Fee Related JP6679317B2 (ja) | 2016-01-13 | 2016-01-13 | 信号供給回路及び表示装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US10311772B2 (ja) |

| JP (1) | JP6679317B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017219586A (ja) * | 2016-06-03 | 2017-12-14 | 株式会社ジャパンディスプレイ | 信号供給回路及び表示装置 |

| JP2019039949A (ja) | 2017-08-22 | 2019-03-14 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP6944334B2 (ja) * | 2017-10-16 | 2021-10-06 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN107833557B (zh) * | 2017-11-20 | 2019-05-31 | 深圳市华星光电半导体显示技术有限公司 | Amoled显示器及其驱动方法 |

| JP6951237B2 (ja) * | 2017-12-25 | 2021-10-20 | 株式会社ジャパンディスプレイ | 表示装置 |

| KR102555211B1 (ko) * | 2017-12-29 | 2023-07-12 | 엘지디스플레이 주식회사 | 발광 표시 장치 |

| JP2022161374A (ja) * | 2021-04-08 | 2022-10-21 | シャープディスプレイテクノロジー株式会社 | タッチパネル付き表示装置 |

| KR20230082162A (ko) * | 2021-12-01 | 2023-06-08 | 엘지디스플레이 주식회사 | 표시장치 및 데이터 구동 회로 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003273749A (ja) * | 2002-03-18 | 2003-09-26 | Seiko Epson Corp | 信号伝送装置及び信号伝送方法、電子装置並びに電子機器 |

| US7307644B2 (en) * | 2002-06-12 | 2007-12-11 | Ati Technologies, Inc. | Method and system for efficient interfacing to frame sequential display devices |

| US20090207325A1 (en) * | 2003-11-01 | 2009-08-20 | Naoya Sugimoto | Algorithm for SLM of single hinge type |

| JP5312779B2 (ja) * | 2007-12-13 | 2013-10-09 | ルネサスエレクトロニクス株式会社 | 液晶表示装置、データ駆動ic、及び液晶表示パネル駆動方法 |

| KR101806407B1 (ko) * | 2010-12-24 | 2017-12-08 | 삼성디스플레이 주식회사 | 감마전압 제어기, 계조 전압 생성기 및 이를 포함하는 표시 장치 |

| JP2013186294A (ja) | 2012-03-08 | 2013-09-19 | Japan Display West Co Ltd | 表示装置及び電子機器 |

| JP5827970B2 (ja) | 2013-03-25 | 2015-12-02 | 株式会社ジャパンディスプレイ | 表示装置及び電子機器 |

| KR102134030B1 (ko) * | 2014-10-23 | 2020-07-15 | 엘지디스플레이 주식회사 | 영상 변환 장치 및 이를 구비하는 디스플레이 장치 |

-

2016

- 2016-01-13 JP JP2016004077A patent/JP6679317B2/ja not_active Expired - Fee Related

-

2017

- 2017-01-13 US US15/405,616 patent/US10311772B2/en active Active

-

2019

- 2019-03-28 US US16/368,365 patent/US10762827B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20190221151A1 (en) | 2019-07-18 |

| US10762827B2 (en) | 2020-09-01 |

| US10311772B2 (en) | 2019-06-04 |

| US20170200407A1 (en) | 2017-07-13 |

| JP2017125903A (ja) | 2017-07-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6679317B2 (ja) | 信号供給回路及び表示装置 | |

| US7239300B2 (en) | Driving apparatus and display module | |

| JP4996222B2 (ja) | 表示装置 | |

| JP4523487B2 (ja) | 液晶表示装置およびその駆動方法 | |

| JP2004177918A (ja) | 駆動表示装置及び装置セット | |

| JP2009020498A (ja) | パーシャルメモリ制御を有するビデオディスプレイドライバ | |

| US10593304B2 (en) | Signal supply circuit and display device | |

| JP2009009122A (ja) | データイネーブルラーニングを具備するビデオディスプレイドライバ | |

| JPH11259046A (ja) | 液晶表示制御装置、それを用いた液晶表示装置および情報処理装置 | |

| CN107644627B (zh) | 显示控制设备和显示面板模块 | |

| JP2009092729A (ja) | 電気光学装置および電子機器 | |

| JP2003015611A (ja) | 液晶駆動装置 | |

| WO2019015073A1 (zh) | 显示面板的驱动方法及驱动装置 | |

| CN104424888B (zh) | 显示面板及其驱动方法、以及电子设备 | |

| JP3637898B2 (ja) | 表示駆動回路及びこれを備えた表示パネル | |

| CN101290750A (zh) | 图像显示系统及其驱动方法 | |

| JP2000122622A (ja) | 電気光学装置の駆動回路、電気光学装置およびこれを用いた電子機器 | |

| US6307531B1 (en) | Liquid crystal display having driving integrated circuits in a single bank | |

| KR101061631B1 (ko) | 액정표시장치의 구동장치 및 방법 | |

| JP2004205901A (ja) | 表示装置およびデータ側駆動回路 | |

| US20020089476A1 (en) | TFT LCD driver capable of reducing current consumption | |

| US7158128B2 (en) | Drive unit and display module including same | |

| US7903102B2 (en) | Display driving integrated circuit and method | |

| JP2007011275A (ja) | 液晶表示パネルモジュールと、そのスキャンドライバ | |

| EP4394750A1 (en) | Display apparatus and driving method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181030 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20181030 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190719 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190910 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190918 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200303 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200318 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6679317 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |