以下、本発明の実施形態について、添付図面を参照して詳細に説明する。

(第1の実施形態)

図1は、本発明の第1の実施形態に係わる撮像装置100の構成を示す全体ブロック図である。図1において、撮像素子101はCMOS撮像素子であり、不図示の撮影レンズで結像された被写体像を光電変換する。AFE(Analog Front End)102は、撮像素子101からの信号の増幅や基準レベルの調整(クランプ処理)などを行う信号処理回路である。また上記処理を行ったアナログ信号をデジタル信号に変換する。

DFE(Digital Front End)103は、AFE102で変換された各画素のデジタル画像信号の各種補正や画素の並び替え等のデジタル処理などを行う。画像処理装置105は、現像処理を行って表示回路8に画像を表示する、あるいは制御回路106を介して画像を記録媒体109に記録する、といった処理を行う。

制御回路106は、操作部107からのユーザーによる指示や、メモリ回路104に記憶されている情報に基づきタイミング発生回路110に命令を送る制御なども行う。メモリ回路104は、画像処理装置105の現像段階での作業用メモリとして、あるいは連続撮像等のバッファメモリとしても使用される。

操作部107には、デジタルカメラを起動させるための電源スイッチが含まれる。また、測光処理、測距処理などの撮影準備動作開始や、ミラー、シャッターを駆動するとともに撮像素子101から読み出した信号を処理して記録媒体109に書き込む一連の撮像動作の開始を指示するシャッタースイッチなども含まれる。また、撮像装置の動作モードの設定・切り換えを行うモードスイッチも含まれ、モードスイッチの設定により、動画撮影を行う動画モード、通常の静止画撮影を行う静止画モードの設定・切り換えが行われる。タイミング発生回路110は、制御回路106からの信号を受け撮像素子101を駆動する各制御信号についてタイミングの生成・出力を行う。

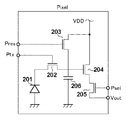

図2は、図1中の撮像素子101における受光素子を含む単位画素部(Pixel)を示す図である。

図2において、光信号電荷を発生するフォトダイオード201は、この例ではアノードが接地されている。フォトダイオード201のカソード側には、転送トランジスタ202を介してフローティングディフュージョン(FD)206が接続されている。また、FD206は、増幅トランジスタ204のゲートに接続されている。また、増幅トランジスタ204のゲートには、これをリセットするためのリセットトランジスタ203のソースが接続されている。リセットトランジスタ203のドレインには電源電圧VDDが供給されている。

さらに増幅トランジスタ204にも電源電圧VDDが供給され、増幅トランジスタ204のソースは選択トランジスタ205のドレインに接続されている。上記の転送トランジスタ202は、そのゲート端子に入力されるPtx信号により駆動され、フォトダイオード201の信号電荷をFD206に転送する。

リセットトランジスタ203のゲート端子はPres信号により駆動され、FD206およびフォトダイオード201をリセットする。このリセット後の出力信号がノイズ信号として読み出されることになる。選択トランジスタ205のゲート端子はPsel信号により駆動され、接続される各増幅トランジスタによって増幅された電気信号をVout端子へ出力する。

上記のVout端子は、後述する図3の第1の垂直信号線Vla、第2の垂直線信号線Vlbの各々に接続されている。また、増幅トランジスタ204は、選択トランジスタ205を介して垂直信号線負荷と接続されることで、ソースフォロワアンプとして機能する。

図3は、撮像素子101の構成例を示すブロック図である。画素領域300は、図2に示した単位画素部を行方向および列方向に複数有するものであるが、ここでは説明を簡略化するため6x8画素のみを図示しており、水平・垂直方向に所定数繰り返し配置されることで画素領域300を構成するものである。なお、画素領域300における各単位画素部には、図5に示すようなR,G,Bのカラーフィルタがベイヤ状に配置され、また、単位画素部が配列される画素列の1列に対して、垂直信号線は一対となる2本ずつ配されている。

そして、各列の単位画素部は行毎に交互に異なる垂直信号線へ接続される。すなわち、ベイヤ状のカラーフィルタの配列と合わせて、同列にある同色の単位画素部が同一の垂直信号線に接続される。なお図中、各制御信号名に続く(n)はn行目、(n+1)ではn+1行目を指し示すものである。また第1および第2の垂直信号線Vla〜Vlbに続く(m)は画素列であるm列、(m+1)ではm+1列目を指し示すものである。

垂直走査回路301は、タイミング発生回路110からの信号を受けて、信号Pres、Ptx、Pselを、各行選択線を介して画素領域300に出力する。上述の各制御信号は、同一行に配列された各単位画素部に共通に接続されており、同一行の画素は同時に駆動される。

各単位画素部のVout端子は、n行目では垂直信号線Vlaを介して負荷である定電流源304aに接続され、第1の読み出し回路315aによりVout端子の出力信号が読み出される。n+1行目では垂直信号線Vlbを介して負荷である定電流源304bに接続され、第2の読み出し回路315bによりVout端子の出力信号が読み出される。なお、第1の読み出し回路315aと第2の読み出し回路315bは、同一構成となっており、接続先がそれぞれ第1の垂直信号線Vla、第2の垂直信号線Vlbと異なるだけである。同様に、次行以降においても各単位画素部のVout端子は、行毎に交互に異なる垂直信号線に接続され、第1の読み出し回路315aまたは第2の読み出し回路315bによりVout端子の出力信号が読み出される。

なお、上記構成によりカラーフィルタのベイヤ状による色配置の関係と、画素部の出力端が行毎に異なる垂直信号線へ接続されることで、同一列上において同色となる画素出力は、同一の垂直信号線上に出力される。

第1および第2の読み出し回路315a,315bは、画素領域300から読み出される画素信号及びノイズ信号を、同回路内の転送容量で保持する。詳細については後述する。また、第1および第2の読み出し回路315a,315bは、それぞれ第1の保持ブロック、第2の保持ブロックとなる。

転送トランジスタ305a,307aおよび306a,308aは、第1の水平走査回路303aからの走査クロック信号PHおよび走査行切り換え信号LSELにより発生する制御信号を受けて、第1の読み出し回路315a内の転送容量に記憶された信号を、水平読み出し線PsaまたはPnaに出力する。この際、転送トランジスタ305a,307aにより水平読み出し線Psaに、転送トランジスタ306a,308aによって水平読み出し線Pnaに出力がなされる。

同様に、転送トランジスタ305b,307bおよび306b,308bは、第2の水平走査回路303bからの走査クロック信号PHおよび走査行切り換え信号LSELにより発生する制御信号を受けて、第2の読み出し回路315b内の転送容量に記憶された信号を、水平読み出し線PsbまたはPnbに順次出力する。この際、転送トランジスタ305b,307bにより水平読み出し線Psbに、転送トランジスタ306b,308bによって水平読み出し線Pnbに出力がなされる。

なお、信号LSELがHi状態では転送トランジスタ305a,306a,305b,306bが、信号LSELがLo状態では転送トランジスタ307a,308a,307b,308bが動作可能となる。これにより行毎に転送容量の使い分けを行い、1水平走査期間中に画素部からの信号読み出しと、水平転送による順次出力の同時動作を行えるようにしている。

第1の水平走査回路303aは、走査クロック信号PHと信号PHSTにより、水平読み出し線Psa,Pnaへの信号出力を順次行わせる。第2の水平走査回路303bは、走査クロック信号PHと信号PHSTにより、水平読み出し線Psb、Pnbへの信号出力を順次行わせる。

差動アンプ302aは、水平読み出し線Psaの信号と水平読み出し線Pnaの信号との差分を撮像素子の外部に出力する。同様に、差動アンプ302bは、水平読み出し線Psbの信号と水平読み出し線Pnbの信号との差分を撮像素子の外部に出力する。また、差動アンプ302a,302bは、最終段読み出し回路に相当する。

図4は、図3に示した第1および第2の読み出し回路315a,315bにおける回路例を示す図である。図4については、例として、第1の読み出し回路315aにおける画素1列分のm列における垂直信号線Vla(m)が接続される1線分の読み出し回路を示しており、画素列数に応じて他列分についても同様に構成されている。

また、第2の読み出し回路315bも接続先が垂直信号線Vlb(m)および水平読み出し線Psb,Pnbに接続される転送トランジスタが異なるだけであり、読み出し回路1と同様の構成となっている。

各画素部の端子Voutからの出力は、信号Pcts1、信号Pctn1、信号Pcts2、信号Pctn2で駆動される各々に接続されている転送トランジスタ403a,404a,407a,408aを介して、各々の転送容量401a,402a,405a,406aに保持される。

なお、後述するタイミングチャートの駆動により、画素回路部で発生するノイズ信号は転送容量402aまたは406aに保持され、その後フォトダイオード201からFD206に転送した電荷に応じた画素信号は転送容量401aまたは405aに保持されることになる。上述した各転送容量に保持された各信号を差動アンプ302a,302bへ順次転送することにより、1行分の画素信号の出力を行う。

図6は、図1〜図5で説明した固体撮像素子を駆動するタイミングチャートであり、動画撮影モードなどの画素出力加算読み出し時における動作タイミングを示している。本実施形態においては、垂直同色の2画素出力を垂直信号線に同時出力し、垂直信号線上で混合する。

ソースフォロアとして機能する増幅トランジスタ204に入力される信号電圧が等しい、または近い場合に、負荷定電流源304aまたは304bの電流が、接続される各増幅トランジスタに均等に分配される。それにより信号電圧が平均化されることを利用するものである。さらに、垂直信号線の1線に対して備えられた、画素信号およびノイズ信号を保持する転送容量の各2対(2系統分)を使い分ける。これにより、1水平走査期間中において、画素部からの信号読み出しと、水平転送動作を異なる行間で同時に動作させるように駆動する。そして、2本の垂直信号線による画素1列分に対する2行同時読み出し動作と併せて、画素混合(平均)時の読み出し動作を、簡易な構成でかつ高速に行うことを可能としている。

なお、図中において、信号レベルの『Hi』状態は駆動トランジスタをON、『Lo』状態は駆動トランジスタをOFFするものとする。また、説明を分かりやすくするため、全画素リセット及び全画素蓄積開始するタイミングは省略し、画素信号の読み出し動作時のタイミングのみを示す。

時刻t1からt8までの1水平走査期間においては、n行目、n+2行目、n+3行目、n+5行目における転送容量への画素信号およびノイズ信号の転送動作が行われる。また、それと同時に並行して、不図示のn−6行目、n−4行目、n−1行目、n−3行目における画素信号およびノイズ信号が、転送容量より順次出力アンプに出力される動作が行われることになる。

次に、上記時間帯におけるn−6行目、n−4行目、n−1行目、n−3行目における動作について説明する。時刻t1にて信号LSELがLoになり、第1および第2の水平走査回路303a,303bに入力される水平走査クロック信号PHに同期して、転送容量405aに記憶された信号が、転送トランジスタ307aを介して水平読み出し線Psaに順次読み出される。同時に転送容量406aに記憶された信号が、転送トランジスタ308aを介して水平読み出し線Pnaに順次読み出される。

同時に転送容量405bに記憶された信号が、転送トランジスタ307bを介して水平読み出し線Psbに順次読み出される。同時に転送容量406bに記憶された信号が、転送トランジスタ308bを介して水平読み出し線Pnbに順次読み出される。出力アンプ302aは、水平読み出し線Psaと水平読み出し線Pnaの差分信号を外部に出力する。このとき出力される信号は、n−6行目、n−4行目の出力が混合された信号となる。同様に、出力アンプ302bは、水平読み出し線Psbと水平読み出し線Pnbの差分信号を外部に出力する。このとき出力される信号は、n−1行目、n−3行目の出力が混合された信号となる。

次に、上述した外部への出力と同時に行われる、n行目、n+2行目、n+3行目、n+5行目における信号電荷の転送容量への転送動作について説明する。

時刻t2にて信号Psel(n)、信号Psel(n+2)がLoからHiになり、n行目およびn+2行目における選択トランジスタ205がONされ、n行目およびn+2行目の各ソースフォロア出力が第1の垂直信号線Vlaに接続される。同時に信号Psel(n+3)、信号Psel(n+5)がLoからHiになり、n+3行目およびn+5行目における選択トランジスタ205がONされ、n+3行目およびn+5行目の各ソースフォロア出力が第2の垂直信号線Vlbに接続される。

また、時刻t2において、信号Pres(n)、信号Pres(n+2)、および信号Pres(n+3)、信号Pres(n+5)がLoからHiになる。そして、n行目、n+1行目、およびn+3行目、n+5行目のリセットトランジスタ203がONされ、同行におけるFD206に蓄積された不要電荷がリセットされる。

時刻t3で、リセットが終了するとともに信号Pctn1がLoからHiになり、転送トランジスタ404aをONし、画素回路で発生するノイズ成分を転送容量402aに記憶する。時刻t4で信号Pctn1がHiからLoになり、ノイズ成分の転送容量402aへの記憶を終了する。

時刻t5にて、信号Ptx(n)、信号Ptx(n+2)がLoからHiになり、n行目およびn+2行目における転送トランジスタ202がONする。そして、n行目のPD201に蓄積された信号電荷と、n+2行目のPD201に蓄積された信号電荷がFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、n行目の電圧信号とn+2行目の電圧信号が同時に第1の垂直信号線Vla上に出力されて混合される。

同時に信号Ptx(n+3)、信号Ptx(n+5)がLoからHiになり、n+3行目およびn+5行目における転送トランジスタ202がONする。そして、n+3行目のPD201に蓄積された信号電荷と、n+5行目のPD201に蓄積された信号電荷がFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、n+3行目の電圧信号とn+5行目の電圧信号が同時に第2の垂直信号線Vlb上に出力されて混合される。

時刻t6にて、Ptcs1信号がLoからHiになり、転送トランジスタ403aをONし、第1および第2の垂直信号線VlaおよびVlbで混合された画素信号を、読み出し回路1および2内の転送容量401aに記憶する。時刻t7でPtcs1信号がHiからLoになり、転送トランジスタ403aをOFFし、転送容量401aへの記憶を終了する。その後、時刻t8から時刻t15までの1水平走査期間で、混合されたn行目とn+2行目の信号が、出力アンプ302aより出力され、同時に混合されたn+3行目とn+5行目の信号が、出力アンプ302bより出力される。

時刻t8で、信号Psel(n)、信号Psel(n+2)および信号Psel(n+3)、信号Psel(n+5)がHiからLoになり、選択トランジスタ205がOFFされ、n行目、n+2行目、およびn+3行目、n+5行目について、第1および第2の垂直信号線VlaおよびVlbへの接続を解除する。

時刻t9からは、前述の説明と同様に、次行として読み出すn+6行目、n+8行目を第1の垂直信号線Vlaに、n+9行目、n+11行目を第2の垂直信号線Vlbに接続し、混合された画素信号を読み出す。この際、異なる点として、行そのものを選択する信号Psel以外に、第1および第2の読み出し回路315a,315b内のノイズ信号および画素信号を保持する転送容量および転送トランジスタ、また水平読み出し線へ信号を転送する転送トランジスタ、およびそれらの制御信号は別のものとなる。

なお、1水平走査期間毎に、前術した前行の転送容量を合わせて切り替えて使用することで、前行での画素出力の水平転送と、今行における画素信号の読み出しの同時動作が可能となり、画素1列に対する垂直信号線の複線化と併せて、高速に読み出すことが可能となる。

時刻t9にて信号Psel(n+6)、信号Psel(n+8)がLoからHiになり、n+6行目およびn+8行目における選択トランジスタ205がONされ、n+6行目およびn+8行目の各ソースフォロア出力が第1の垂直信号線Vlaに接続される。同時に信号Psel(n+9)、信号Psel(n+11)がLoからHiになり、n+9行目およびn+11行目における選択トランジスタ205がONされ、n+9行目およびn+11行目の各ソースフォロア出力が第2の垂直信号線Vlbに接続される。

また、時刻t9において、信号Pres(n+6)、信号Pres(n+8)および信号Pres(n+9)、信号Pres(n+11)がLoからHiになる。そして、n+6行目、n+8行目、およびn+9行目、n+11行目のリセットトランジスタ203がONされ、同行におけるFD206に蓄積された不要電荷がリセットされる。

時刻t10で、リセットが終了するとともに信号Pctn2がLoからHiになり、転送トランジスタ408aをONし、画素回路で発生するノイズ成分を転送容量406aに記憶する。時刻t11で信号Pctn2がHiからLoになり、ノイズ成分の転送容量406aへの記憶を終了する。

時刻t12にて、信号Ptx(n+6)、信号Ptx(n+8)がLoからHiになり、n+6行目およびn+8行目における転送トランジスタ202がONする。そして、n+6行目のPD201に蓄積された信号電荷と、n+8行目のPD201に蓄積された信号電荷がFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、同時に第1の垂直信号線Vla上に出力されて混合される。

同時に信号Ptx(n+9)、信号Ptx(n+11)がLoからHiになり、n+9行目およびn+11行目における転送トランジスタ202がONする。そして、n+9行目のPD201に蓄積された信号電荷と、n+11行目のPD201に蓄積された信号電荷がFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、同時に第2の垂直信号線Vlb上に出力されて混合される。

時刻t13にて、信号Ptcs2がLoからHiになり、転送トランジスタ407aをONし、第1および第2の垂直信号線VlaおよびVlbで混合された画素信号を、読み出し回路1および2内の転送容量405aに記憶する。時刻t14で信号Ptcs2がHiからLoになり、転送トランジスタ407aをOFFし転送容量405aへの記憶を終了する。

その後の1水平走査期間で、混合されたn+6行目とn+8行目の信号が、出力アンプ302aより出力され、同時に混合されたn+9行目とn+11行目の信号が、出力アンプ302bより出力される。なお、行走査切り換え信号LSELは、1水平走査毎に、Lo状態とHi状態が切り換えられ、交互にLo、Hi状態となる。

行走査切り換え信号LSELの状態により、転送容量からの信号を転送する転送トランジスタが有効となるが、1水平走査毎に切り替えることにより、前の1水平走査中に画素信号を保持した転送容量にあわせて転送トランジスタの動作を有効として、予め転送容量に保持されていた信号を順次出力させることで、同時に次行の読み出しも別転送容量および転送トランジスタにて動作を可能とさせている。

このような動作を、固体撮像素子が持つ行数分を順次繰り返すことで、画素出力混合時においても、高速に読み出すことが可能となる。

図7は本実施形態における読み出しを、ベイヤ配列のカラー撮像素子に適用した場合の模式図であり、混合読み出し動作を示す模式図である。

本実施形態においては、同一列の画素列に対して、2本の垂直信号線を有しているため、ベイヤ配列の各色成分ごとに異なる垂直信号線に読み出すことになる。同一列のRの信号については第1の垂直信号線Vla(m)に読み出され、Gbの信号が第2の垂直信号線Vlb(m)に読みだされ、Grの信号が第1の垂直信号線Vla(m+1)に読み出され、Bの信号が第2の垂直信号線Vlb(m+1)に読みだされる。

図7において、ハッチングが掛っている画素は、読み出しを行わない画素である。また前述したような画素出力混合動作を行わせた場合、同色の信号の2画素分の混合が垂直信号線上で行われる。また、混合した後の画像はベイヤ配列であり、従来同様の信号処理が可能である。なお、混合により、各色の重心は、混合される同色2画素分の領域の中心となり、混合前では異なる色が配された画素上に位置することになるが、混合後の信号の重心が等間隔であることから、モアレ等の偽信号の発生を抑圧できる。

(第2の実施形態)

図8は、本発明の第2の実施形態における固体撮像素子を駆動するタイミングチャートであり、画素出力混合読み出し時における動作タイミングを示している。なお、撮像装置の構成は第1の実施形態と同様である。

本実施形態においては、垂直の同色3画素出力の混合が行われるものであり、同一垂直信号線への同時出力を同色となる3行分行うことで垂直信号線上にて混合するものである。

時刻t1からt8までの1水平走査期間においては、n行目、n+2行目、n+4行目、およびn+3行目、n+5行目、n+7行目における転送容量への画素信号およびノイズ信号の転送動作が行われる。また、不図示のn−6行目、n−4行目、n−2行目、n−3行目、n−1行目およびn+1行目における画素信号およびノイズ信号が、転送容量より順次出力アンプへ出力される動作が行われることになる。なお、前述した第1の実施形態と異なる点として、画素出力の混合数が2画素から3画素に変わり、それに応じて同色行となる行の同時選択も3行分に変わるものである。

次に上記時刻帯におけるn−6行目、n−4行目、n−2行目、n−3行目、n−1行目、およびn+1行目における動作を説明する。

時刻t1にて信号LSELがLoになり、第1および第2の水平走査回路303a,303bに入力される水平走査クロック信号PHに同期して、転送容量405aに記憶された信号が、転送トランジスタ307aを介して水平読み出し線Psaに順次読み出される。同時に転送容量406aに記憶された信号が、転送トランジスタ308aを介して水平読み出し線Pnaに順次読み出される。

同時に転送容量405bに記憶された信号が、転送トランジスタ307bを介して水平読み出し線Psbに順次読み出される。同時に転送容量406bに記憶された信号が、転送トランジスタ308bを介して水平読み出し線Pnbに順次読み出される。

出力アンプ302aは、水平読み出し線Psaと水平読み出し線Pnaの差分信号を外部に出力する。このとき出力される信号は、n−6行目、n−4行目、n−2行目の出力が混合された信号となる。

同様に、出力アンプ302bは、水平読み出し線Psbと水平読み出し線Pnbの差分信号を外部に出力する。このとき出力される信号は、n−3行目、n−1行目、n+1行目の出力が混合された信号となる。

次に、上述した外部への出力と同時に行われる、n行目、n+2行目、n+4行目、およびn+3行目、n+5行目、n+7行目における信号の転送容量への転送動作について説明する。

時刻t2にて信号Psel(n)、信号Psel(n+2)、信号Psel(n+4)がLoからHiになり、n行目、n+2行目、n+4行目における選択トランジスタ205がONされる。そして、n行目、n+2行目、n+4行目の各ソースフォロア出力が第1の垂直信号線Vlaに接続される。

同時に信号Psel(n+3)、信号Psel(n+5)、信号Psel(n+7)がLoからHiになり、n+3行目、n+5行目、n+7行目における選択トランジスタ205がONされる。そして、n+3行目、n+5行目、n+7行目の各ソースフォロア出力が第2の垂直信号線Vlbに接続される。

また、時刻t2において、信号Pres(n)、信号Pres(n+2)、信号Pres(n+4)および信号Pres(n+3)、信号Pres(n+5)、信号Pres(n+7)がLoからHiになり、n行目、n+2行目、n+4行目、およびn+3行目、n+5行目、n+7行目のリセットトランジスタ203がONされ、同行におけるFD206に蓄積された不要電荷がリセットされる。

時刻t3で、リセットが終了するとともに信号Pctn1がLoからHiになり、転送トランジスタ404aをONし、画素回路で発生するノイズ成分を転送容量402aに記憶する。時刻t4で信号Pctn1がHiからLoになり、ノイズ成分の転送容量402aへの記憶を終了する。

時刻t5にて、信号Ptx(n)、信号Ptx(n+2)、信号Ptx(n+4)がLoからHiになり、n行目、n+2行目、n+4行目における転送トランジスタ202がONする。そして、n行目のPD201に蓄積された信号電荷と、n+2行目のPD201に蓄積された信号電荷とn+4行目のPD201に蓄積された信号電荷とがFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、同時に第1の垂直信号線Vla上に出力されて混合される。

同時に信号Ptx(n+3)、信号Ptx(n+5)、信号Ptx(n+7)がLoからHiになり、n+3行目、n+5行目、n+7行目における転送トランジスタ202がONする。そして、n+3行目のPD201に蓄積された信号電荷と、n+5行目のPD201に蓄積された信号電荷と、n+7行目のPD201に蓄積された信号電荷とがFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、同時に第2の垂直信号線Vlb上に出力されて混合される。

時刻t6にて、信号Ptcs1がLoからHiになり、転送トランジスタ403aをONし、第1および第2の垂直信号線VlaおよびVlbで混合された画素信号を、第1および第2の読み出し回路315a,315b内の転送容量401aに記憶する。時刻t7で信号Ptcs1がHiからLoになり、転送トランジスタ403aをOFFし転送容量401aへの記憶を終了する。

その後、時刻t8から時刻t15までの1水平走査期間で、混合されたn行目とn+2行目とn+4行目による信号が、出力アンプ302aより出力される。同時に混合されたn+3行目とn+5行目とn+7行目による信号が、出力アンプ302bより出力される。

時刻t8で、信号Psel(n)、信号Psel(n+2)、信号Psel(n+4)および信号Psel(n+3)、信号Psel(n+5)、信号Psel(n+7)がHiからLoになり、選択トランジスタ205がOFFされる。そして、n行目、n+2行目、n+4行目、およびn+3行目、n+5行目、n+7行目について、第1および第2の垂直信号線VlaおよびVlbへの接続を解除する。

時刻t9からは、前述の説明と同様に、次行として読み出すn+6行目、n+8行目、n+10行目を第1の垂直信号線Vlaに、n+9行目、n+11行目、n+13行目を第2の垂直信号線Vlbに接続し、混合された画素信号を読み出す。

時刻t9にて信号Psel(n+6)、信号Psel(n+8)、信号Psel(n+10)がLoからHiになり、n+6行目、n+8行目、n+10行目における選択トランジスタ205がONされる。そして、n+6行目、n+8行目、n+10行目の各ソースフォロア出力が第1の垂直信号線Vlaに接続される。

同時に信号Psel(n+9)、信号Psel(n+11)、信号Psel(n+13)がLoからHiになり、n+9行目、n+11行目、n+13行目における選択トランジスタ205がONされる。そして、n+9行目、n+11行目、n+13行目の各ソースフォロア出力が第2の垂直信号線Vlbに接続される。

また、時刻t9において、信号Pres(n+6)、信号Pres(n+8)、信号Pres(n+10)および信号Pres(n+9)、信号Pres(n+11)、信号Pres(n+13)がLoからHiになる。そして、n+6行目、n+8行目、n+10行目、およびn+9行目、n+11行目、n+13行目のリセットトランジスタ203がONされ、同行におけるFD206に蓄積された不要電荷がリセットされる。

時刻t10で、リセットが終了するとともに信号Pctn2がLoからHiになり、転送トランジスタ408aをONし、画素回路で発生するノイズ成分を転送容量406aに記憶する。時刻t11で信号Pctn2がHiからLoになり、ノイズ成分の転送容量406aへの記憶を終了する。

時刻t12にて、信号Ptx(n+6)、信号Ptx(n+8)、信号Ptx(n+10)がLoからHiになり、n+6行目、n+8行目、n+10行目における転送トランジスタ202がONする。そして、n+6行目のPD201に蓄積された信号電荷と、n+8行目のPD201に蓄積された信号電荷と、n+10行目のPD201に蓄積された信号電荷がFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、同時に第1の垂直信号線Vla上に出力されて混合される。

同時に信号Ptx(n+9)、信号Ptx(n+11)、信号Ptx(n+13)がLoからHiになり、n+9行目、n+11行目、n+13行目における転送トランジスタ202がONする。そして、n+9行目のPD201に蓄積された信号電荷と、n+11行目のPD201に蓄積された信号電荷と、n+13行目のPD201に蓄積された信号電荷がFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、同時に第2の垂直信号線Vlb上に出力されて混合される。

時刻t13にて、信号Ptcs2がLoからHiになり、転送トランジスタ407aをONし、第1および第2の垂直信号線VlaおよびVlbで混合された画素信号を、第1および第2の読み出し回路315a,315b内の転送容量405aに記憶する。時刻t14で信号Ptcs2がHiからLoになり、転送トランジスタ407aをOFFし転送容量405aへの記憶を終了する。

その後の1水平走査期間で、混合されたn+6行目とn+8行目とn+10行目による信号が、出力アンプ302aより出力され、同時に混合されたn+9行目とn+11行目とn+13行目による信号が、出力アンプ302bより出力される。

このような動作を、固体撮像素子が持つ行数分を順次繰り返すことで、画素混合時においても、高速に読み出すことが可能となる。

図9は本実施形態における読み出しを、ベイヤ配列のカラー撮像素子に適用した場合の模式図であり、混合読み出し動作を示す図である。

本実施形態においては、同一列の画素列に対して、2本の垂直信号線を有しているため、ベイヤ配列の各色成分ごとに異なる垂直信号線に読み出すようになっている。同一列のRの信号が第1の垂直信号線Vla(m)に読み出され、Gbの信号が第2の垂直信号線Vlb(m)に読みだされ、Grの信号が垂直信号線Vla(m+1)に読み出され、Bの信号が第2の垂直信号線Vlb(m+1)に読みだされる。

図9において、前述したような画素出力混合動作を行わせた場合、同色の信号の3画素出力の混合が垂直信号線上で行われる。なお、各垂直信号線上に記載される太線部およびI,IIの番号は、太線部については同時に読み出されて混合される画素部を示すものであり、I,IIの番号については、共通の番号により1水平走査期間にて同時に読み出される画素部を示すものである。なお混合後の画像はベイヤ配列であり、従来同様の信号処理が可能である。また重心が等間隔であることから、モアレ等の偽信号の発生を抑圧できるものとなる。

なお、上記の第1及び第2の実施形態においては、画素混合を同色2画素および3画素により行っていたが、この画素数に限られるものではない。混合する画素数に応じ、かつ混合後の信号がベイヤ配列を保つように垂直信号線への同時出力を行うことで、複画素数による画素混合を可能とすることができる。

図10は図1〜図5で説明した固体撮像素子を駆動するタイミングチャートであり、上記の第1及び第2の実施形態における静止画モード時における全画素読み出し時の動作タイミングを示している。

本実施形態においては、画素1列に対して垂直信号線が2本備えられ、且つ行毎に交互に異なる垂直信号線に接続されているため、2行同時読み出しが可能であり、全画素読み出し時においては、2行同時読みにより高速に読み出しが行われる。

なお、撮像装置の設定として、操作部7の動作モードスイッチにより、通常の静止画撮影を行うための静止画モードに設定されているものとする。また、図中において、信号レベルの『Hi』状態は駆動トランジスタをON、『Lo』状態は駆動トランジスタをOFFするものとする。また、説明を分かりやすくするため、全画素リセット及び全画素蓄積開始するタイミングは省略し、画素信号の読み出し動作時のタイミングのみを示す。

図10を用いて全画素読み出し動作について説明する。時刻t1からt8までの1水平走査期間においては、n行目、n+1行目における転送容量への画素信号およびノイズ信号の転送動作が行われる。また、同時に不図示のn−2行目、n−1行目における画素信号およびノイズ信号が、転送容量から順次出力アンプへ出力され、撮像素子外部へと出力される。

次に上記の時刻帯におけるn−2行目、n−1行目における動作を説明する。時刻t1にて信号LSELがLoになり、第1および第2の水平走査回路315a,315bに入力される水平走査クロック信号PHに同期して、転送容量405aに記憶された信号が、転送トランジスタ307aを介して水平読み出し線Psaに順次読み出される。同時に転送容量406aに記憶された信号が、転送トランジスタ308aを介して水平読み出し線Pnaに順次読み出される。

同時に転送容量405bに記憶された信号が、転送トランジスタ307bを介して水平読み出し線Psbに順次読み出される。同時に転送容量406bに記憶された信号が、転送トランジスタ308bを介して水平読み出し線Pnbに順次読み出される。

出力アンプ302aは、水平読み出し線Psaと水平読み出し線Pnaの差分信号を外部に出力する。このとき出力される信号は、n−2行目の出力信号となる。同様に、出力アンプ302bは、水平読み出し線Psbと水平読み出し線Pnbの差分信号を外部に出力する。このとき出力される信号は、n−1行目の出力信号となる。

次に、上述した外部への出力と同時に行われる、n行目、n+1行目における信号の転送容量への転送動作について説明する。時刻t2において信号Psel(n)がLoからHiになり、n行目における選択トランジスタ205がONされ、n行目の各ソースフォロワ出力が第1の垂直信号線Vlaに接続される。同様に時刻t2にて、信号Psel(n+1)がLoからHiになり、n+1行目における選択トランジスタ205がONされ、n+1行目の各ソースフォロワ出力が第2の垂直信号線Vlbに接続される。

同時に時刻t2において、信号Pres(n)、信号Pres(n+1)がLoからHiになり、n行目、n+1行目のリセットトランジスタ203がONされ、同行におけるFD206に蓄積された不要電荷がリセットされる。

時刻t3で、リセットが終了するとともに信号Pctn1がLoからHiになり、転送トランジスタ404aをONし、画素回路で発生するノイズ成分を転送容量402aに記憶する。時刻t4で信号Pctn1がHiからLoになり、ノイズ成分の転送容量402aへの記憶を終了する。

時刻t5にて、信号Ptx(n)がLoからHiになり、n行目おける転送トランジスタ202がONし、n行目のPD201に蓄積された信号電荷がFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、第1の垂直信号線Vla上に出力される。

同時に信号Ptx(n+1)がLoからHiになり、n+1行目における転送トランジスタ202がONし、n+1行目のPD201に蓄積された信号電荷がFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、第2の垂直信号線Vlb上に出力される。

時刻t6にて、信号Ptcs1がLoからHiになり、転送トランジスタ403aをONし、第1および第2の垂直信号線VlaおよびVlbに出力された画素信号を、第1および第2の読み出し回路315a,315b内の転送容量401aに記憶する。時刻t7で信号Ptcs1がHiからLoになり、転送トランジスタ403aをOFFし転送容量401aへの記憶を終了する。

その後、時刻t8から時刻t15までの1水平走査期間で、n行目の信号が出力アンプ302aより出力され、同時にn+1行目の信号が出力アンプ302bより出力される。

時刻t8で、信号Psel(n)、信号Psel(n+1)がHiからLoになり、選択トランジスタ205がOFFされ、n行目およびn+1行目について、第1および第2の垂直信号線VlaおよびVlbへの接続を解除する。

時刻t9からは、前述の説明と同様に、次行として読み出すn+2行目を第1の垂直信号線Vlaに、n+3行目を第2の垂直信号線Vlbに接続し、画素信号を読み出す。この際、異なる点として、行そのものを選択する信号Psel以外に、読み出し回路1,2内のノイズ信号および画素信号を保持する転送容量および転送トランジスタ、また、水平読み出し線へ信号を転送する転送トランジスタ、およびそれらの制御信号も別のものとなる。

なお、1水平走査期間毎に、前術した前行の転送容量を合わせて切り替えて使用することで、前行での画素出力の水平転送と、今行における画素信号の読み出しの同時動作が可能となる。これにより、画素1列に対する垂直信号線の複線化と併せて、高速に読み出すことが可能となる。

時刻t9にて信号Psel(n+2)がLoからHiになり、n+2行目における選択トランジスタ205がONされ、ソースフォロア出力が第1の垂直信号線Vlaに接続される。同時に信号Psel(n+3)がLoからHiになり、n+3行目における選択トランジスタ205がONされ、n+3行目の各ソースフォロア出力が第2の垂直信号線Vlbに接続される。

また、時刻t9において、信号Pres(n+2)および信号Pres(n+3)がLoからHiになり、n+2行目およびn+3行目のリセットトランジスタ203がONされ、同行におけるFD206に蓄積された不要電荷がリセットされる。

時刻t10で、リセットが終了するとともに信号Pctn2がLoからHiになり、転送トランジスタ408aをONし、画素回路で発生するノイズ成分を転送容量406aに記憶する。時刻t11で信号Pctn2がHiからLoになり、ノイズ成分の転送容量406aへの記憶を終了する。

時刻t12にて、信号Ptx(n+2)がLoからHiになり、n+2行目における転送トランジスタ202がONし、n+2行目のPD201に蓄積された信号電荷がFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、第1の垂直信号線Vla上に出力される。

同時に信号Ptx(n+3)がLoからHiになり、n+3行目における転送トランジスタ202がONし、n+3行目のPD201に蓄積された信号電荷が同時にFD206に転送され、増幅トランジスタ204により増幅され電圧に変換される。そして、第2の垂直信号線Vlb上に出力される。

時刻t13にて、信号Ptcs2がLoからHiになり、転送トランジスタ407aをONし、第1および第2の垂直信号線VlaおよびVlbに出力された画素信号を、第1および第2の読み出し回路315a,315b内の転送容量405aに記憶する。時刻t14で信号Ptcs2がHiからLoになり、転送トランジスタ407aをOFFし転送容量405aへの記憶を終了する。

その後の1水平走査期間で、n+2行目の信号が出力アンプ302aより出力され、同時にn+3行目の信号が出力アンプ302bより出力される。

このような動作を、固体撮像素子が備える行数分を順次繰り返すことで、全画素読み出し時においても、高速に読み出すことが可能となる。

(その他の実施形態)

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。