JP6585612B2 - アーキテクチャ・モードの構成 - Google Patents

アーキテクチャ・モードの構成 Download PDFInfo

- Publication number

- JP6585612B2 JP6585612B2 JP2016557130A JP2016557130A JP6585612B2 JP 6585612 B2 JP6585612 B2 JP 6585612B2 JP 2016557130 A JP2016557130 A JP 2016557130A JP 2016557130 A JP2016557130 A JP 2016557130A JP 6585612 B2 JP6585612 B2 JP 6585612B2

- Authority

- JP

- Japan

- Prior art keywords

- mode

- architecture

- computer

- architectural

- processor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 claims description 82

- 238000012545 processing Methods 0.000 claims description 67

- 238000004590 computer program Methods 0.000 claims description 22

- 238000004891 communication Methods 0.000 claims description 18

- 230000000977 initiatory effect Effects 0.000 claims description 4

- 230000006870 function Effects 0.000 description 73

- 230000008569 process Effects 0.000 description 32

- 238000013519 translation Methods 0.000 description 30

- 230000014616 translation Effects 0.000 description 30

- 238000005192 partition Methods 0.000 description 25

- 238000007667 floating Methods 0.000 description 14

- 238000010586 diagram Methods 0.000 description 13

- 238000009434 installation Methods 0.000 description 13

- 230000003213 activating effect Effects 0.000 description 12

- 230000008859 change Effects 0.000 description 12

- 230000009471 action Effects 0.000 description 9

- 230000006399 behavior Effects 0.000 description 9

- 230000000875 corresponding effect Effects 0.000 description 8

- 230000007246 mechanism Effects 0.000 description 7

- 238000006243 chemical reaction Methods 0.000 description 6

- 238000006073 displacement reaction Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 230000003993 interaction Effects 0.000 description 5

- 238000007726 management method Methods 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 5

- 230000002093 peripheral effect Effects 0.000 description 5

- 230000001960 triggered effect Effects 0.000 description 5

- 230000008901 benefit Effects 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 4

- 230000000295 complement effect Effects 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 230000008520 organization Effects 0.000 description 4

- 238000012360 testing method Methods 0.000 description 4

- 230000006378 damage Effects 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000007774 longterm Effects 0.000 description 3

- 238000012546 transfer Methods 0.000 description 3

- 238000010200 validation analysis Methods 0.000 description 3

- 230000003139 buffering effect Effects 0.000 description 2

- 230000001934 delay Effects 0.000 description 2

- 230000001419 dependent effect Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 239000000835 fiber Substances 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 230000005055 memory storage Effects 0.000 description 2

- 230000001902 propagating effect Effects 0.000 description 2

- 230000011664 signaling Effects 0.000 description 2

- 238000012384 transportation and delivery Methods 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 102000004137 Lysophosphatidic Acid Receptors Human genes 0.000 description 1

- 108090000642 Lysophosphatidic Acid Receptors Proteins 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 238000012884 algebraic function Methods 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 230000001276 controlling effect Effects 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 238000007405 data analysis Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000001976 improved effect Effects 0.000 description 1

- 238000007562 laser obscuration time method Methods 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000005012 migration Effects 0.000 description 1

- 238000013508 migration Methods 0.000 description 1

- 230000006855 networking Effects 0.000 description 1

- 238000013439 planning Methods 0.000 description 1

- 229920001690 polydopamine Polymers 0.000 description 1

- 238000011176 pooling Methods 0.000 description 1

- 238000007781 pre-processing Methods 0.000 description 1

- 230000000644 propagated effect Effects 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 230000009131 signaling function Effects 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

- 238000012358 sourcing Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 229920000638 styrene acrylonitrile Polymers 0.000 description 1

- 210000003813 thumb Anatomy 0.000 description 1

- 238000012795 verification Methods 0.000 description 1

- 238000005303 weighing Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/445—Program loading or initiating

- G06F9/44505—Configuring for program initiating, e.g. using registry, configuration files

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/4401—Bootstrapping

- G06F9/4403—Processor initialisation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/78—Architectures of general purpose stored program computers comprising a single central processing unit

- G06F15/7867—Architectures of general purpose stored program computers comprising a single central processing unit with reconfigurable architecture

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30076—Arrangements for executing specific machine instructions to perform miscellaneous control operations, e.g. NOP

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30181—Instruction operation extension or modification

- G06F9/30189—Instruction operation extension or modification according to execution mode, e.g. mode flag

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/4401—Bootstrapping

- G06F9/4405—Initialisation of multiprocessor systems

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Computer Security & Cryptography (AREA)

- Stored Programmes (AREA)

- Executing Machine-Instructions (AREA)

- Multi Processors (AREA)

- Supply And Distribution Of Alternating Current (AREA)

Description

マスク毎(Per Mask)(R)502:ビット1は、CPUがプログラム・イベント記録(PER)と関連した割り込みに関してイネーブルにされるかどうかを制御する。ビットが0である場合、PERイベントが割り込みを引き起こすことはない。ビットが1である場合、割り込みは許容され、制御レジスタ9内のPERイベント・マスク・ビットに左右される。

DATモード(T)504:ビット5は、ストレージにアクセスするのに用いられる論理及び命令アドレスの暗黙的な動的アドレス変換(DAT)が行われるかどうかを制御する。ビットが0である場合、DATはオフであり、論理及び命令アドレスは実アドレスとして扱われる。ビットが1である場合、DATはオンであり、動的アドレス変換機構が呼び出される。

外部マスク(EX)508:ビット7は、CPUが、外部クラス内に含まれる条件による割り込みに関してイネーブルにされるかどうかを制御する。ビットが0である場合、外部割り込みが発生することはない。ビットが1である場合、外部割り込みは、制御レジスタ0内の対応する外部サブクラス・マスク・ビットに左右される。サブクラス・マスク・ビットが0である場合、サブクラスと関連した条件が割り込みを発生させることはない。サブクラス・マスク・ビットが1である場合、そのサブクラス内の割り込みが発生し得る。

(1)エラーを発生することなく(又はエラーを無視することなく)、モードから自身への(z/Architectureモードからz/Architectureモードへの)切り替えをイネーブルにすること。つまり、プロセッサは、SIGP命令を発行して、z/Architectureモードに切り替えることができ、プロセッサが既にそのモードにある場合、エラーは発生しない。これまで、現在のモードに対応するモードに切り替えようとする試みにより、エラーが発生した。

(2)ESA/390モードへの切り替えをディスエーブルにすること。CZMをインストールし、アクティブにすることに基づいて、ESA/390への切り替えがディスエーブルにされ、今やエラーが発生する。ESA/390への再切り替えは、PSWのビット12をチェックすることにより防止され、ビット12がz/Architectureモードを示すように設定されない場合(ストレージ内の「1」のビット12により表され、このビットは、ESA/390 PSWが有効なz/Architecture PSWに変換されたとき、PSWにおけるz/Architectureを表すように、ビット「0」に反転される)、例外が発生する。

(3)ビット12の処理を制限するために、Load PSW(PSWロード)操作を変更すること。構成z/Architectureアーキテクチャ・モード・ファシリティがインストールされている場合、PSWロードは、その第2のオペランドが1でない場合には、指定例外を認識する。PSWロードは、ビット12が反転されることを除いて、その第2のオペランドのビット0−32を、そして、オペランドのビット33−63を、現PSWのそれぞれ、ビット0−32及び97−127としてロードし、現PSWのビット33−96を0に設定する。

*ビット0、2−4、12、又は24−30のいずれかが1である。

*ビット31及び32の両方とも0であり、ビット97−103は全て0ではない。

*ビット31及び32は、それぞれ、1及び0である。

これらの場合、操作は完了し、結果として得られる命令長コードは0である。

結果の条件コード:コードは、ロードされた新しいPSWにおいて指定されるように設定される。

プログラム例外:

*アクセス(フェッチ、オペランド2)

*特権操作

*指定

(4)(例えば、リセット、クリア・リセット、及びリセットのための他のアクションに関する)リセット・モードを変更すること。CZAMファシリティがインストールされているとき、CPUリセットは、例えばロード・ノーマル・キーなどをアクティブにすることにより引き起こされる場合、アーキテクチャ・モードをz/Architectureモードに設定する。

CPUリセットは、機器チェック表示をクリアする手段と、破壊される情報の破壊を最小量に抑えた、CPU状態における結果の予測不能性とをもたらす。特に、CPUリセットは、CPU状態が分析又は操作の再開のために予約されるとき、チェック条件をクリアするために使用される。構成z/Architectureアーキテクチャ・モード(CZAM)ファシリティがインストールされていない場合、CPUリセットは、これがロード・ノーマル・キー(オペレータ・ファシリティ)をアクティブにすることによって引き起こされるのであれば、アーキテクチャ・モードをESA/390モードに設定する。CZAMファシリティがインストールされている場合、CPUリセットは、これがロード・ノーマル・キーをアクティブにすることによって引き起こされるのであれば、アーキテクチャ・モードをz/Architectureモードに設定する。CPUリセットによりESA/390モードが設定される場合、これは現PSWを保存するので、アーキテクチャ・モードを元のz/Architectureに変更するSignal Processor Set Architecture指令により、PSWを復元することができる。

本発明の1つの好ましい実施形態において、CPUリセットにより、次のアクションが引き起こされる。

1.現在の命令又は割り込みなどの他の処理シーケンスの実行が終了し、全てのプログラム割り込み及びスーパーバイザ呼び出し・割り込み条件がクリアされる。

2.CPUにローカルなあらゆる保留中の外部割り込み条件がクリアされる。浮動外部割り込み条件はクリアされない。

3.CPUにローカルなあらゆる保留中のマシン・チェック・割り込み条件及びエラー表示、並びにあらゆるチェック停止状態がクリアされる。浮動マシン・チェック割り込み条件はクリアされない。構成内の全てのCPUに報告され、CPUに対して保留状態にされたあらゆるマシン・チェック条件は、CPUにローカルであると言われる。

4.プリフェッチされた命令又はオペランドの全てのコピーがクリアされる。付加的に、現在のチェックポイント間隔での命令の実行が理由で格納されるあらゆる結果がクリアされる。

5.ART(Access Register Translation)ルックアサイド・バッファ及び変換ルックアサイド・バッファは、エントリをクリアする。

6.構成内のいずれかのCPU上のロード・ノーマル・キーをアクティブすることにより、リセットが引き起こされた場合、次のアクションが行われる。

a.CZAMファシリティがインストールされていないとき、CPU(及び、CPUリセット又はそれらにより実行されるCPUリセットのため、構成内の他の全てのCPU)のアーキテクチャ・モードが、z/ArchitectureモードからESA/390モードに設定される。

b.CZAMファシリティがインストールされていないとき、現PSWは、z/Architectureモードを復元するSignal Processor Set Architecture命令による後の使用のために保存される。

c.CZAMファシリティがインストールされていないとき、現PSWは、16バイトから8バイトに変更される。8バイトのPSWのビットは、次のように設定される。:即ち、ビット0−11及び13−32は、16バイトのPSWの同じビットと等しくなるように設定され、ビット12は1に設定され、ビット33−63は、16バイトのPSWのビット97−127と等しくなるように設定される。

システム・リセット・ノーマル・キーをアクティブにすることにより又はSignal Processor CPU−Reset命令により引き起こされるCPUリセット、並びにESA/390モードにおけるあらゆるCPUリセットは、キャプチャされたz/Architecture−PSWレジスタ(即ち、コード0でのSet Architecture命令、又はロード・ノーマル・キーをアクティブにすることに起因するCPUリセットのために、CPUが、z/ArchitectureモードからESA/390モードに最後に変わったときに保存されるPSW)に影響を与えない。

7.アクション1−6が完了した後、CPUは停止状態になる。CCWタイプのIPLシーケンスがそのCPUにおけるリセット機能に従うとき、CPUは、リセット機能の完了時にロード状態になり、リセット動作の実行中、必ずしも停止状態にはならない。リスト指示のIPLシーケンスがそのCPUにおけるリセット機能に従うとき、CPUは動作状態になり、リセット操作の実行中、必ずしも停止状態にはならない。

1.CPUが停止状態にあるとき、状態、条件、又はフィールドの内容を変更する大部分の操作が行われないことがある。しかしながら、一部のプロセッサ信号機能及び一部のオペレータ機能により、これらのフィールドが変更されることがある。CPUリセットが生じたときにフィールドを失う可能性を排除するために、CPUを停止すべきであり、オペレータ機能が進行中であってはならない。

2.アーキテクチャ・モードがESA/390モードに変更され、現PSWのビット31が1である場合、PSWは無効である。

初期CPUリセットは、現PSWの初期化、キャプチャされたz/ArchitecturePSW、CPUタイマ、クロック・コンパレータ、プリフィックス、ブレーキング・イベント・アドレス制御、浮動小数点制御、及び時刻(Time of Day、TOD)プログラム可能レジスタと共に、CPUリセットの機能を提供する。CZAMファシリティがインストールされていない場合、初期CPUリセットは、ロード・ノーマル・キーをアクティブにすることによりリセットが引き起こされるならば、アーキテクチャ・モードがESA/390モードに設定される。CZAMファシリティがインストールされている場合、初期CPUリセットは、これがロード・ノーマル・キーをアクティブにすることにより引き起こされるならば、アーキテクチャ・モードがz/Architectureモードに設定される。

初期CPUリセットは、CPUリセット機能を以下のクリア及び初期化機能と結合させる。

1.CZAMファシリティがインストールされていない場合、ロード・ノーマル・キーをアクティブにすることによりリセットが引き起こされるならば、CPU(及び構成内の他の全てのCPUの)アーキテクチャ・モードが、ESA/390モードに設定される。そうでない場合、CZAMファシリティがインストールされているならば、CPU(及び構成内の他の全てのCPU)のアーキテクチャ・モードは、z/Architectureモードに設定される。

2.現PSW、キャプチャされたz/Architecture−PSW、プリフィックス、CPUタイマ、クロック・コンパレータ、及びTODプログラム可能レジスタの内容が、0に設定される。IPLシーケンスがそのCPUにおけるリセット機能に従うとき、PSWの内容は、必ずしも0に設定されない。

3.制御レジスタの内容は、その初期z/Architecture値に設定される。CPUがESA/390モードにあるか又はz/Architectureモードにあるかに関係なく、制御レジスタの全ての64ビットが設定される。

4.浮動小数点制御レジスタの内容は、0に設定される。

5.ブレーキング・イベント・アドレス・レジスタの内容は、0000000000000001hexに初期化される。

これらのクリア及び初期化機能は、妥当性検査を含む。

サブシステム・リセットは、浮動割り込み条件のクリア及びI/Oシステム・リセットの呼び出しのための手段を提供する。

クリア・リセットにより、初期CPUリセット及びサブシステム・リセットが実行され、付加的に、TODクロックを除く、構成内の全てのCPUにおける全てのストレージ位置及びレジスタがクリア又は初期化される。こうしたクリアは、プログラムをデバッグする際及びユーザのプライバシーを保証する際に有用である。また、クリア・リセットにより、PERFORM LOCKED OPERATION命令によって使用される全てのロックが解放される。CZAMファシリティがインストールされていない場合、クリア・リセットにより、アーキテクチャ・モードがESA/390モードに設定される。CZAMファシリティがインストールされている場合、クリア・リセットにより、アーキテクチャ・モードがz/Architectureモードに設定される。クリアは、アドレス指定可能でないページの内容を保持するために制御プログラムが使用するダイレクト・アクセス・ストレージ・デバイスなどの外部ストレージに影響を与えない。

クリア・リセットは、初期CPU上のリセット機能を初期化機能と結合し、それにより以下のアクションが引き起こされる。

1.CZAMファシリティがインストールされていない場合、構成内の全てのCPUのアーキテクチャ・モードは、ESA/390モードに設定される。CZAMファシリティがインストールされている場合、構成内の全てのCPUのアーキテクチャ・モードは、z/Architectureモードに設定される。

2.構成内の全てのCPUのアクセス、汎用、及び浮動小数点レジスタは、0に設定される。クリア・リセットが開始されると、CPUがESA/390モードにあったか又はz/Architectureアーキテクチャ・モードにあったかに関係なく、汎用レジスタの全ての64ビットが0に設定される。

3.構成内の主ストレージの内容及び関連したストレージ・キーは、有効なチェック・ブロック・コードにより0に設定される。

4.PERFORM LOCKED OPERATION命令を実行する際に構成内のあらゆるCPUにより使用されるロックが、解放される。

5.サブシステム・リセットが実施される。

妥当性検査は、レジスタの設定、並びにストレージ及びストレージ・キーのクリアに含まれる。

1.アーキテクチャ・モードは、システム・リセット・ノーマル・キーのアクティブ化により、又はSignal Processor CPU−Reset若しくはInitial−CPU−reset指令の実行により、変更されない。構成内の全てのCPUは、同じアーキテクチャ・モードにある。

2.CPUリセット動作が変更されないままにされるフィールドの内容に影響を与えない場合、CPUは命令を実行しておらず、リセット時に全ての割り込みに関してディスエーブルにされる。CPUタイマの動作及びマシン・チェック割り込みの発生の可能性を除き、CPUを待機状態にすること、及び、I/O及び外部割り込みに対してこれをディスエーブルにすることにより、全てのCPU活動を停止させることができる。CPUタイマが更新されるとき又はマシン・チェック割り込みが発生するときにリセットを引き起こす可能性を回避するために、CPUは停止状態になる。

3.CPUリセット、初期CPUリセット、サブシステム・リセット、及びクリア・リセットは、TODクロックの値及び状態に影響を与えない。

4.CPUがチェック停止状態になる条件はモデル依存であり、現在の動作の完了を妨げる機能不良を含む。従って、CPUがチェック停止状態にある間にCPUリセット又は初期CPUリセットが実行された場合、PSW、レジスタ、及びエラー時にアクセスされるストレージ・キー及びストレージ位置を含むストレージ位置の内容は、予測不能な値を有することがあり、場合によっては、内容は、チェック停止状態がこれらのリセットによってクリアされた後、依然としてエラーになり得る。この状況において、クリア・リセットは、エラーのクリアを必要とする。

マシンのコンポーネントのためのパワーオン・リセット機能は、そのコンポーネントのためのパワーオン・シーケンスの一部として実行される。TODクロック、主ストレージ、拡張ストレージ及びチャネル・サブシステムのパワーオン・シーケンスは、CPUパワーオン・シーケンスの一部として含ませることができ、又は、これらのユニットのパワーオン・シーケンスを別個に開始することができる。

CPUパワーオン・リセット:パワーオン・リセットにより、初期CPUリセットが実行され、チャネル・サブシステムにおいてI/Oシステム・リセットが実行されることも又はされないこともある。汎用レジスタ、アクセス・レジスタ、及び浮動小数点レジスタの内容は、チェック・ブロッサム・コードにより、0にクリアされる。PERFORM LOCKED OPERATIONにより使用され、CPUと関連付けられたロックは、それらが既にパワーオンしているCPUにより保持されない限り、解放される。CZAMファシリティがインストールされておらず、リセットが構成の確立と関連付けられている場合、CPUは、ESA/390モードになり、そうでない場合、CPUは、既に構成内にあるCPUのアーキテクチャ・モードになる。CZAMファシリティがインストールされている場合、CPUは、z/Architectureモードになる。

CPUリセット、初期CPUリセット、サブシステム・リセット、及びクリア・リセットは、オペレータ・ファシリティを用いて手動で開始することができる。初期CPUリセットは、初期プログラム・ロード機能の部分である。パワーオン・リセットは、パワーオンに変わる部分として実行される。

(5)リセットが実行されると、ESA/390モードとz/Architectureモードとの間の変更を容易にするためにとられる他のリセット関連アクションを抑止する。CZAMファシリティがインストールされていない場合、現PSWは、z/Architectureモードを復元するSignal Processor Set Architecture指令による後の使用のために保存される。CZAMファシリティがインストールされていない場合、現PSWは、16バイトから8バイトに変更される。8バイトのPSWのビットは、一例では、次のように設定される。:即ち、ビット0−11及び13−32は、16バイトのPSWの同じビットに等しくなるように設定され、ビット12は1に設定され、ビット33−63は、16バイトのPSWのビット97−127に等しくなるように設定される。CZAMファシリティがインストールされている場合、PSWは、z/Architectureモードを復元するSignal Processor Set Architecture指令による後の使用のために保存されず、現PSWは、16バイトから8バイトに変更されない。

(6)CPU SCLP構成(configure Service Call Logical Processor)コマンド、及びロード・キー操作により、CPUを構成するためのプロセスを変更する。ESA/390における構成ではなく、リセットにより定められるモードで構成する。CPU SCLP構成コマンドは、対象CPUを、既に構成された状態にあるCPUのアーキテクチャ・モードにする。構成内に入れられた少なくとも第1のCPUは、CPUのパワーオン・リセットと共にそこに入れられ、そのリセットの一部分として、CPUパワーオン・リセットで定められたアーキテクチャ・モードにされる。モデルは、これが構成されるCPUのモードを設定するとき、待機状態にあるCPUのモードを代替的に設定することができる。

R1により指定される汎用レジスタ:ビット0−31は使用されない;ビット32−63は状況を含む。

どちらであっても奇数番号のレジスタであるR1又はR1+1により指定される汎用レジスタ:ビット0−31は使用されない;ビット32−63はパラメータを含む。

R3により指定される汎用レジスタ:ビット0−48は未使用;ビット49−63はCPUアドレスを含む。

第2オペランド・アドレス:ビット0−55は使用されない;ビット56−63は指令コードを含む。

0 指令コードが受け入れられる

1 状況が格納される

2 ビジー

3 非動作状態

プログラム例外

*特権操作

*トランザクション制約

・パラメータ・レジスタ内のコードが0、1、又は2でない場合、又はCPUが既にコードにより指定されるアーキテクチャ・モードにあるとき、指令は受け入れられない。代わりに、Signal Processor命令のR1フィールドに指定されている汎用レジスタのビット55(無効パラメータ)が1に設定され、条件コード1が設定される。

・構成内の他の全てのCPUが停止又はチェック停止状態にある場合、指令は受け入れられない。代わりに、Signal Processor命令のR1フィールドに指定されている汎用レジスタのビット54(誤り状態)が1に設定され、条件コード1が設定される。

・構成内の全てのCPUのアーキテクチャ・モードがコードで指定されているものに設定される(例えば、操作を制御するためのPSWのビット12は、指定されたアーキテクチャ・モードに設定され、及び/又は、コンピューティング環境内の別の表示は、指定されたアーキテクチャ・モードを示すように設定される)。

・指令によりアーキテクチャ・モードがESA/390からz/Architectureに変更され、コードが1である場合は、構成内の各CPUについて、8バイトの現PSWは16バイトのPSWに変更され、16バイトPSWのビットは、以下のように設定される。:即ち、ビット0−11及び13−32は8バイトPSWの同じビットと等しくなるように設定され、ビット12及びビット33−96は0に設定され、ビット97−127は8バイトPSWのビット33−63と等しくなるように設定される。また、ESA/390プリフィックスのビット19(これは、z/Architectureプリフィックスのビット51になる)は、0に設定される。

・指令により、アーキテクチャ・モードがz/ArchitectureからESA/390に変更された場合、構成内の各CPUについて、(1)Signal Processorを実行しているCPUの場合に更新されたPSWである現PSWが、キャプチャされたz/Architecture・PSWレジスタ内に保存され、(2)8バイトPSWのビットを以下のように設定すること:即ち、ビット0−11及び13−32は16バイトPSWの同じビットと等しくなるように設定され、ビット12は1に設定し、ビット33−63は16バイトPSWのビット97−127と等しくなるように設定することにより、16バイトPSWが8バイトPSWに変更される。z/Architectureプリフィックスのビット51(これは、ESA/390プリフィックスのビット19になる)は、変更されないままである。

・構成内の全てのCPUのALB及びTLBの内容がクリアされる。

・構成内の全てのCPUで、シリアル化及びチェックポイント同期化機能が実行される。

(8)ファシリティ・ビットへの変更:例えばビット138などの新しいビットが、構成z/Architectureアーキテクチャ・モード・ファシリティを示すようにファシリティ・ビットに加えられ、z/Architectureアーキテクチャ・モードがアクティブかどうかを示すビット2が1(アクティブを示す)に設定される。

オンデマンド・セルフサービス:クラウド・コンシューマは、必要に応じて、サーバ時間及びネットワーク・ストレージ等のコンピューティング機能を、人間がサービスのプロバイダと対話する必要なく自動的に、一方的にプロビジョニングすることができる。

広範なネットワーク・アクセス:機能は、ネットワーク上で利用可能であり、異種のシン又はシック・クライアント・プラットフォーム(例えば、携帯電話、ラップトップ、及びPDA)による使用を促進する標準的な機構を通じてアクセスされる。

リソースのプール化:プロバイダのコンピューティング・リソースは、マルチ・テナント・モデルを用いて、異なる物理及び仮想リソースを要求に応じて動的に割り当て及び再割り当てすることにより、複数のコンシューマにサービスを提供するためにプールされる。コンシューマは、一般に、提供されるリソースの正確な位置についての制御又は知識を持たないが、より高レベルの抽象化では位置(例えば、国、州、又はデータセンタ)を特定できる場合があるという点で、位置とは独立しているといえる。

迅速な弾力性:機能は、迅速かつ弾力的に、幾つかの場合自動的に、プロビジョニングして素早くスケール・アウトし、迅速にリリースして素早くスケール・インさせることができる。コンシューマにとって、プロビジョニングに利用可能なこれらの機能は、多くの場合、無制限であり、いつでもどんな量でも購入できるように見える。

サービスの測定:クラウド・システムは、サービスのタイプ(例えば、ストレージ、処理、帯域幅、及びアクティブなユーザ・アカウント)に適した何らかの抽象化レベルでの計量機能を用いることによって、リソースの使用を自動的に制御及び最適化する。リソース使用を監視し、制御し、報告し、利用されるサービスのプロバイダとコンシューマの両方に対して透明性をもたらすことができる。

Software as a Service(SaaS):クラウド・インフラストラクチャ上で動作しているプロバイダのアプリケーションを使用するために、コンシューマに提供される機能である。これらのアプリケーションは、ウェブ・ブラウザ(例えば、ウェブ・ベースの電子メール)などのシン・クライアント・インターフェースを通じて、種々のクライアント・デバイスからアクセス可能である。コンシューマは、限定されたユーザ固有のアプリケーション構成設定の考え得る例外として、ネットワーク、サーバ、オペレーティング・システム、ストレージ、又は個々のアプリケーション機能をも含めて、基礎をなすクラウド・インフラストラクチャを管理又は制御しない。

Platform as a Service(PaaS):プロバイダによってサポートされるプログラミング言語及びツールを用いて生成された、コンシューマが生成した又は取得したアプリケーションを、クラウド・インフラストラクチャ上に配備するために、コンシューマに提供される機能である。コンシューマは、ネットワーク、サーバ、オペレーティング・システム、又はストレージなどの基礎をなすクラウド・インフラストラクチャを管理又は制御しないが、配備されたアプリケーション、及び場合によってはアプリケーション・ホスティング環境構成に対して制御を有する。

Infrastructure as a Service(IaaS):コンシューマが、オペレーティング・システム及びアプリケーションを含み得る任意のソフトウェアを配備及び動作させることができる、処理、ストレージ、ネットワーク、及び他の基本的なコンピューティング・リソースをプロビジョニンングするために、コンシューマに提供される機能である。コンシューマは、基礎をなすクラウド・インフラストラクチャを管理又は制御しないが、オペレーティング・システム、ストレージ、配備されたアプリケーションに対する制御、及び場合によってはネットワーク・コンポーネント(例えば、ホストのファイアウォール)選択の限定された制御を有する。

プライベート・クラウド:クラウド・インフラストラクチャは、ある組織のためだけに運営される。このクラウド・インフラストラクチャは、その組織又は第三者によって管理することができ、構内又は構外に存在することができる。

コミュニティ・クラウド:クラウド・インフラストラクチャは、幾つかの組織によって共有され、共通の関心事項(例えば、任務、セキュリティ要件、ポリシー、及びコンプライアンス上の考慮事項)を有する特定のコミュニティをサポートする。クラウド・インフラストラクチャは、その組織又は第三者によって管理することができ、構内又は構外に存在することができる。

パブリック・クラウド:クラウド・インフラストラクチャは、一般公衆又は大規模な業界グループに利用可能であり、クラウド・サービスを販売する組織によって所有される。

ハイブリッド・クラウド:クラウド・インフラストラクチャは、固有のエンティティのままであるが、データ及びアプリケーションの移行性を可能にする標準化された又は専用の技術(例えば、クラウド間の負荷分散のためのクラウド・バースティング)によって結び付けられる2つ又はそれより多いクラウド(プライベート、コミュニティ、又はパブリック)の混成物である。

ハードウェア及びソフトウェア層6060は、ハードウェア及びソフトウェア・コンポーネントを含む。ハードウェア・コンポーネントの例として、IBM(登録商標)zSeriesシステムを一例とするメインフレームと、IBM(登録商標) pSeriesシステムを一例とするRISC(Reduced Instruction Set Computer(縮小命令セット・コンピュータ))アーキテクチャ・ベースのサーバと、IBM(登録商標) xSeries(登録商標)システムと、IBM(登録商標) BladeCenter(登録商標)システムと、ストレージ・デバイスと、ネットワーク及びネットワーク・コンポーネントと、が含まれる。ソフトウェア・コンポーネントの例として、IBM(登録商標) WebSphere(登録商標)アプリケーション・サーバ・ソフトウェアを一例とするネットワーク・アプリケーション・サーバ・ソフトウェアと、IBM(登録商標) DB2(登録商標)データベース・ソフトウェアを一例とするデータベース・ソフトウェアとが含まれる。IBM、zSeries、xSeries、BladeCenter、WebSphere、及びDB2、z/OS、z/VM、z/Architecture、及びProcessor Resource/Systems Managerは、世界中の多数の管轄区域において登録されているインターナショナル・ビジネス・マシーンズ・コーポレーションの商標である。本明細書において用いられる他の名称は、インターナショナル・ビジネス・マシーンズ・コーポレーション又は他の会社の登録商標、商標、又は製品名とすることができる。

仮想化層6062は、抽象化層を提供し、この層により、仮想エンティティの以下の例、すなわち、仮想サーバ、仮想ストレージ、仮想プライベート・ネットワークを含む仮想ネットワーク、仮想アプリケーション及びオペレーティング・システム、並びに仮想クライアントを提供することができる。

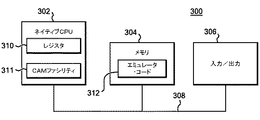

102、152:中央プロセッサ・コンプレックス

104、154:プロセッサ・メモリ

108:制御ユニット

110:中央プロセッサ

111、212:入力/出力サブシステム

112:論理パーティション

113、165:プロセッサ・ファームウェア

114:論理パーティション・ハイパーバイザ

162:仮想メモリ

164:ホスト・ハイパーバイザ

202:プロセッサ

210:キャッシュ

304:メモリ

311:構成アーキテクチャ・モード・ファシリティ

312:エミュレータ・コード

350:ゲスト命令

356:ネイティブ命令

1300:コンピュータ・プログラム製品

Claims (18)

- プロセッサを備えるコンピュータを再構成するための方法であって、前記方法は、

前記プロセッサにより、複数のアーキテクチャ・モード用に構成され、かつ、前記複数のアーキテクチャ・モードのうちの1つのアーキテクチャ・モードで前記コンピュータをパワーオンするために定められたパワーオン・シーケンスを有する前記コンピュータにおいて、構成アーキテクチャ・モード・ファシリティがインストールされていることを判断することであって、前記1つのアーキテクチャ・モードは、第1の命令セット・アーキテクチャ・モードを含み、第1セットのサポートされたフィーチャを有する、判断することと、

前記構成アーキテクチャ・モード・ファシリティがインストールされていると判断することに基づいて、前記プロセッサにより、前記1つのアーキテクチャ・モードの使用を制限するように前記コンピュータを再構成することと、

を含み、前記再構成することは、

前記複数のアーキテクチャ・モードの別のアーキテクチャ・モードで前記コンピュータをパワーオンするための異なるパワーオン・シーケンスを選択することであって、前記別のアーキテクチャ・モードは前記1つのアーキテクチャ・モードとは異なり、前記別のアーキテクチャ・モードは、第2の命令セット・アーキテクチャを含み、第2セットのサポートされたフィーチャを有する、選択することと、

前記1つのアーキテクチャ・モードの代わりに、前記1つのアーキテクチャ・モードの使用を制限する前記別のアーキテクチャ・モードで前記コンピュータをパワーオンするための前記異なるパワーオン・シーケンスを実行することと、

を含む、方法。 - 前記異なるパワーオン・シーケンスは、前記別のアーキテクチャ・モードで前記コンピュータの操作を制御するための新しいプログラム状況ワードを作成することを含み、前記新しいプログラム状況ワードを作成することは、前記別のアーキテクチャ・モードを示すように、前記新しいプログラム状況ワード内のアーキテクチャ・モード・インジケータを反転させることを含む、請求項1に記載の方法。

- 前記新しいプログラム状況ワードを作成することは、前記別のアーキテクチャ・モードにより示される形式を有するように前記新しいプログラム状況ワードを形成することであって、前記形式は、アドレス・フィールドを第1のサイズから第2のサイズへ拡張させることを含む、形成することと、前記アーキテクチャ・モード・インジケータの前記反転を実行することとを含む、請求項2に記載の方法。

- 前記構成アーキテクチャ・モード・ファシリティがインストールされていることを判断することは、ファシリティ・インジケータをチェックすることを含み、前記ファシリティ・インジケータは、無条件に又は構成インジケータの制御下で設定される、前記請求項1ないし3のいずれかに記載の方法。

- 前記再構成することは、前記コンピュータ内で、前記1つのアーキテクチャ・モードをサポートするために1又は複数の操作をディスエーブルにすることをさらに含み、前記1又は複数の操作は、前記別のアーキテクチャ・モードから元の前記1つのアーキテクチャ・モードへ切り替えるための切り替え操作を含み、元の前記1つのアーキテクチャ・モードへの切り替えがディスエーブルにされる、前記請求項1ないし4のいずれかに記載の方法。

- 前記ディスエーブルにすることは、元の前記1つのアーキテクチャ・モードへ切り替える要求に基づいてエラーを与えるように、Signal Processor命令の処理を変更することを含む、請求項5に記載の方法。

- 前記方法は、

前記コンピュータの少なくとも1つのプロセッサのリセットを実行することをさらに含み、前記リセットを実行することは、

前記別のアーキテクチャ・モードで前記コンピュータをリセットすることであって、前記リセットすることは、前記コンピュータの1つのアーキテクチャ・モードを前記別のアーキテクチャ・モードに設定することを含む、リセットすることと、

前記別のアーキテクチャ・モードを示すようにプログラム状況ワード内のアーキテクチャ・モード・インジケータを反転させることであって、前記プログラム状況ワードは前記コンピュータの操作を制御するために用いられる、反転させることと、

を含む、前記請求項1ないし6のいずれかに記載の方法。 - 前記再構成することは、プロセッサ信号操作の処理を変更することを含み、前記コンピュータのアーキテクチャ・モードを、これが現在ある前記アーキテクチャ・モードに設定するための前記プロセッサ信号操作は、前記コンピュータが現在前記アーキテクチャ・モードにあることを示す状況の格納をもたらし、この状況は、前記プロセッサ信号操作の発行者により受け入れ可能なものとして扱われる、前記請求項1ないし7のいずれかに記載の方法。

- 前記1つのアーキテクチャ・モードはレガシー・モードであり、前記別のアーキテクチャ・モードは強化されたモードであり、前記第1セットのサポートされたフィーチャは、31ビット・アドレッシング及び32ビット汎用レジスタの使用を含み、前記第2セットのサポートされたフィーチャは、64ビット・アドレッシング及び64ビット汎用レジスタの使用を含む、前記請求項1ないし8のいずれかに記載の方法。

- 前記コンピュータは、ホスト・プロセッサ、第1レベルの仮想化における第1のゲスト仮想マシン、及び第2レベルの仮想化における第2のゲスト仮想マシンを有する仮想ゲストコンピュータであり、前記再構成することは、前記ホスト・プロセッサ及び前記第1のゲスト仮想マシンに関して実行されるが、前記第2のゲスト仮想マシンに関しては実行されず、前記第2のゲスト仮想マシンは前記1つのアーキテクチャ・モードで開始され、処理する、前記請求項1ないし9のいずれかに記載の方法。

- プロセッサを備えるコンピュータを構成するための方法であって、前記方法は、

前記プロセッサにより、選択されたアーキテクチャ・モードで操作を実行するためにコンピューティング環境を構成することであって、前記構成することは、

格納されたプログラム状況ワードを用いた前記コンピュータの初期化を開始することであって、前記格納されたプログラム状況ワードは前記選択されたアーキテクチャ・モードとは異なるアーキテクチャ・モードの形式を有する、開始することと、

前記格納されたプログラム状況ワードは前記選択されたアーキテクチャ・モードとは異なるアーキテクチャ・モードの形式を有することを判断することと、

前記格納されたプログラム状況ワードが前記選択されたアーキテクチャ・モードとは異なるアーキテクチャ・モードの形式を有すると判断することに基づいて、前記選択されたアーキテクチャ・モードの形式を有するように前記格納されたプログラム状況ワードを自動的に修正することであって、前記自動的に修正することは、前記選択されたアーキテクチャ・モードへ切り替える明示的な要求なしに実行される、自動的に修正することと、

前記修正されたプログラム状況ワードを用いた前記コンピュータの初期化を完了し、前記選択されたアーキテクチャ・モードで前記コンピュータを構成することと、

を含む、方法。 - 自身を再構成するコンピュータ・システムであって、前記コンピュータ・システムは、

メモリと、

前記メモリと通信するプロセッサと、

を含み、前記コンピュータ・システムは、方法を実行するように構成され、前記方法は、

前記プロセッサにより、複数のアーキテクチャ・モード用に構成され、かつ、前記複数のアーキテクチャ・モードのうちの1つのアーキテクチャ・モードで前記コンピュータ・システムをパワーオンするために定められたパワーオン・シーケンスを有する前記コンピュータ・システムにおいて、構成アーキテクチャ・モード・ファシリティがインストールされていることを判断することであって、前記1つのアーキテクチャ・モードは、第1の命令セット・アーキテクチャ・モードを含み、第1セットのサポートされたフィーチャを有する、判断することと、

前記構成アーキテクチャ・モード・ファシリティがインストールされていると判断することに基づいて、前記プロセッサにより、前記1つのアーキテクチャ・モードの使用を制限するように前記コンピュータ・システムを再構成することと、

を含み、前記再構成することは、

前記複数のアーキテクチャ・モードの別のアーキテクチャ・モードで前記コンピュータ・システムをパワーオンするための異なるパワーオン・シーケンスを選択することであって、前記別のアーキテクチャ・モードは前記1つのアーキテクチャ・モードとは異なり、前記別のアーキテクチャ・モードは、第2の命令セット・アーキテクチャを含み、第2セットのサポートされたフィーチャを有する、選択することと、

前記1つのアーキテクチャ・モードの代わりに、前記1つのアーキテクチャ・モードの使用を制限する前記別のアーキテクチャ・モードで前記コンピュータ・システムをパワーオンするための前記異なるパワーオン・シーケンスを実行することと、

を含む、コンピュータ・システム。 - 前記異なるパワーオン・シーケンスは、前記別のアーキテクチャ・モードで前記コンピュータ・システムの操作を制御するための新しいプログラム状況ワードを作成することを含み、前記新しいプログラム状況ワードを作成することは、前記別のアーキテクチャ・モードを示すように、前記新しいプログラム状況ワード内のアーキテクチャ・モード・インジケータを反転させることを含む、請求項12に記載のコンピュータ・システム。

- 前記新しいプログラム状況ワードを作成することは、前記別のアーキテクチャ・モードにより示される形式を有するように前記新しいプログラム状況ワードを形成することであって、前記形式は、アドレス・フィールドを第1のサイズから第2のサイズへ拡張させることを含む、形成することと、前記アーキテクチャ・モード・インジケータの前記反転を実行することとを含む、請求項13に記載のコンピュータ・システム。

- 前記再構成することは、前記コンピュータ・システム内で、前記1つのアーキテクチャ・モードをサポートするために1又は複数の操作をディスエーブルにすることをさらに含み、前記1又は複数の操作は、前記別のアーキテクチャ・モードから元の前記1つのアーキテクチャ・モードへ切り替えるための切り替え操作を含み、元の前記1つのアーキテクチャ・モードへの切り替えがディスエーブルにされる、請求項12から請求項14までのいずれかに記載のコンピュータ・システム。

- 前記ディスエーブルにすることは、元の前記1つのアーキテクチャ・モードへ切り替える要求に基づいてエラーを与えるように、Signal Processor命令の処理を変更することを含む、請求項15に記載のコンピュータ・システム。

- 前記再構成することは、プロセッサ信号操作の処理を変更することを含み、前記コンピュータ・システムのアーキテクチャ・モードを、これが現在ある前記アーキテクチャ・モードに設定するための前記プロセッサ信号操作は、前記コンピュータが現在前記アーキテクチャ・モードにあることを示す状況の格納をもたらし、この状況は、前記プロセッサ信号操作の発行者により受け入れ可能なものとして扱われる、請求項12から請求項16までのいずれかに記載のコンピュータ・システム。

- コンピュータに実行されることで、前記コンピュータに請求項1ないし11のいずれかに記載の方法を実行させるコンピュータ・プログラム。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/217,840 US9582295B2 (en) | 2014-03-18 | 2014-03-18 | Architectural mode configuration |

| US14/217,840 | 2014-03-18 | ||

| US14/554,806 | 2014-11-26 | ||

| US14/554,806 US9594576B2 (en) | 2014-03-18 | 2014-11-26 | Architectural mode configuration |

| PCT/EP2015/054850 WO2015139992A1 (en) | 2014-03-18 | 2015-03-09 | Architectural mode configuration in a computing system |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017513114A JP2017513114A (ja) | 2017-05-25 |

| JP6585612B2 true JP6585612B2 (ja) | 2019-10-02 |

Family

ID=54142196

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016557130A Active JP6585612B2 (ja) | 2014-03-18 | 2015-03-09 | アーキテクチャ・モードの構成 |

Country Status (22)

| Country | Link |

|---|---|

| US (6) | US9582295B2 (ja) |

| EP (1) | EP3114561B1 (ja) |

| JP (1) | JP6585612B2 (ja) |

| KR (1) | KR101884544B1 (ja) |

| CN (1) | CN106133683B (ja) |

| AU (1) | AU2015230885B2 (ja) |

| BR (1) | BR112016021602B1 (ja) |

| CA (1) | CA2940911C (ja) |

| DK (1) | DK3114561T3 (ja) |

| ES (1) | ES2717525T3 (ja) |

| HU (1) | HUE043750T2 (ja) |

| IL (1) | IL247856B (ja) |

| LT (1) | LT3114561T (ja) |

| MX (1) | MX2016011921A (ja) |

| PL (1) | PL3114561T3 (ja) |

| PT (1) | PT3114561T (ja) |

| RU (1) | RU2664413C2 (ja) |

| SG (1) | SG11201606095SA (ja) |

| SI (1) | SI3114561T1 (ja) |

| TW (1) | TWI608363B (ja) |

| WO (1) | WO2015139992A1 (ja) |

| ZA (1) | ZA201605470B (ja) |

Families Citing this family (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9582295B2 (en) | 2014-03-18 | 2017-02-28 | International Business Machines Corporation | Architectural mode configuration |

| US9916185B2 (en) | 2014-03-18 | 2018-03-13 | International Business Machines Corporation | Managing processing associated with selected architectural facilities |

| US9588774B2 (en) | 2014-03-18 | 2017-03-07 | International Business Machines Corporation | Common boot sequence for control utility able to be initialized in multiple architectures |

| US9853863B1 (en) * | 2014-10-08 | 2017-12-26 | Servicenow, Inc. | Collision detection using state management of configuration items |

| US10073707B2 (en) * | 2015-03-23 | 2018-09-11 | n.io Innovations, LLC | System and method for configuring a platform instance at runtime |

| US10642706B2 (en) * | 2016-07-20 | 2020-05-05 | International Business Machines Corporation | Detection and recovery of lost host enabled facilities |

| US10514932B2 (en) * | 2016-09-26 | 2019-12-24 | Amazon Technologies, Inc. | Resource configuration based on dynamic group membership |

| US10452288B2 (en) | 2017-01-19 | 2019-10-22 | International Business Machines Corporation | Identifying processor attributes based on detecting a guarded storage event |

| US10579377B2 (en) | 2017-01-19 | 2020-03-03 | International Business Machines Corporation | Guarded storage event handling during transactional execution |

| US10725685B2 (en) | 2017-01-19 | 2020-07-28 | International Business Machines Corporation | Load logical and shift guarded instruction |

| US10732858B2 (en) | 2017-01-19 | 2020-08-04 | International Business Machines Corporation | Loading and storing controls regulating the operation of a guarded storage facility |

| US10496292B2 (en) | 2017-01-19 | 2019-12-03 | International Business Machines Corporation | Saving/restoring guarded storage controls in a virtualized environment |

| US10496311B2 (en) | 2017-01-19 | 2019-12-03 | International Business Machines Corporation | Run-time instrumentation of guarded storage event processing |

| US10282327B2 (en) | 2017-01-19 | 2019-05-07 | International Business Machines Corporation | Test pending external interruption instruction |

| US11126474B1 (en) * | 2017-06-14 | 2021-09-21 | Amazon Technologies, Inc. | Reducing resource lock time for a virtual processing unit |

| US10684852B2 (en) | 2017-06-23 | 2020-06-16 | International Business Machines Corporation | Employing prefixes to control floating point operations |

| US10514913B2 (en) | 2017-06-23 | 2019-12-24 | International Business Machines Corporation | Compiler controls for program regions |

| US10740067B2 (en) | 2017-06-23 | 2020-08-11 | International Business Machines Corporation | Selective updating of floating point controls |

| US10481908B2 (en) | 2017-06-23 | 2019-11-19 | International Business Machines Corporation | Predicted null updated |

| US10725739B2 (en) | 2017-06-23 | 2020-07-28 | International Business Machines Corporation | Compiler controls for program language constructs |

| US10379851B2 (en) | 2017-06-23 | 2019-08-13 | International Business Machines Corporation | Fine-grained management of exception enablement of floating point controls |

| US10908998B2 (en) | 2017-08-08 | 2021-02-02 | Toshiba Memory Corporation | Managing function level reset in an IO virtualization-enabled storage device |

| US10592281B1 (en) | 2017-09-28 | 2020-03-17 | Amazon Technologies, Inc. | Wait optimizer for recording an order of first entry into a wait mode by a virtual central processing unit |

| CN108900086B (zh) * | 2018-08-01 | 2020-01-17 | 环鸿电子(昆山)有限公司 | 可程序隔离式电源电路结构及系统 |

| US11086715B2 (en) * | 2019-01-18 | 2021-08-10 | Arm Limited | Touch instruction |

| US11574060B2 (en) * | 2019-04-24 | 2023-02-07 | International Business Machines Corporation | Secure initial program load |

| TWI719720B (zh) * | 2019-11-18 | 2021-02-21 | 瑞昱半導體股份有限公司 | 資料寫入系統與方法 |

| CN112860174B (zh) * | 2019-11-27 | 2024-07-12 | 瑞昱半导体股份有限公司 | 数据写入系统与方法 |

| CN214851908U (zh) * | 2021-06-16 | 2021-11-23 | 深圳市不插电光电科技有限公司 | 一种能够独立集成化控制的机顶盒彩灯条 |

| US12020059B2 (en) | 2021-08-30 | 2024-06-25 | International Business Machines Corporation | Inaccessible prefix pages during virtual machine execution |

Family Cites Families (79)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS59123943A (ja) | 1982-12-29 | 1984-07-17 | Fujitsu Ltd | Vmアシスト制御方式 |

| JPS60254358A (ja) * | 1984-05-31 | 1985-12-16 | Toshiba Corp | マルチア−キテクチヤマイクロプロセツサシステム |

| JPH02135528A (ja) | 1988-11-16 | 1990-05-24 | Oki Electric Ind Co Ltd | マルチosにおける起動os選択方法 |

| US5212777A (en) | 1989-11-17 | 1993-05-18 | Texas Instruments Incorporated | Multi-processor reconfigurable in single instruction multiple data (SIMD) and multiple instruction multiple data (MIMD) modes and method of operation |

| AU6629894A (en) | 1993-05-07 | 1994-12-12 | Apple Computer, Inc. | Method for decoding guest instructions for a host computer |

| JPH06332803A (ja) | 1993-05-25 | 1994-12-02 | Hitachi Ltd | 仮想計算機システムにおけるtlb制御方法 |

| GB2289353B (en) * | 1994-05-03 | 1997-08-27 | Advanced Risc Mach Ltd | Data processing with multiple instruction sets |

| US5551013A (en) | 1994-06-03 | 1996-08-27 | International Business Machines Corporation | Multiprocessor for hardware emulation |

| US5638525A (en) * | 1995-02-10 | 1997-06-10 | Intel Corporation | Processor capable of executing programs that contain RISC and CISC instructions |

| US5790825A (en) | 1995-11-08 | 1998-08-04 | Apple Computer, Inc. | Method for emulating guest instructions on a host computer through dynamic recompilation of host instructions |

| US6009261A (en) | 1997-12-16 | 1999-12-28 | International Business Machines Corporation | Preprocessing of stored target routines for emulating incompatible instructions on a target processor |

| US6199202B1 (en) | 1998-01-06 | 2001-03-06 | Hewlett-Packard Company | Method and apparatus for the inter-operation of differing architectural and run time conventions |

| US6308255B1 (en) | 1998-05-26 | 2001-10-23 | Advanced Micro Devices, Inc. | Symmetrical multiprocessing bus and chipset used for coprocessor support allowing non-native code to run in a system |

| US20020147969A1 (en) | 1998-10-21 | 2002-10-10 | Richard A. Lethin | Dynamic optimizing object code translator for architecture emulation and dynamic optimizing object code translation method |

| US6772325B1 (en) | 1999-10-01 | 2004-08-03 | Hitachi, Ltd. | Processor architecture and operation for exploiting improved branch control instruction |

| US6496971B1 (en) * | 2000-02-07 | 2002-12-17 | Xilinx, Inc. | Supporting multiple FPGA configuration modes using dedicated on-chip processor |

| US7058791B1 (en) | 2000-08-09 | 2006-06-06 | Advanced Micro Devices, Inc. | Establishing a mode indication responsive to two or more indications |

| US7406682B2 (en) | 2001-03-26 | 2008-07-29 | Emc Corporation | Translator-compiler for converting legacy management software |

| US7496498B2 (en) | 2003-03-24 | 2009-02-24 | Microsoft Corporation | Front-end architecture for a multi-lingual text-to-speech system |

| US7496915B2 (en) | 2003-04-24 | 2009-02-24 | International Business Machines Corporation | Dynamic switching of multithreaded processor between single threaded and simultaneous multithreaded modes |

| US7552426B2 (en) | 2003-10-14 | 2009-06-23 | Microsoft Corporation | Systems and methods for using synthetic instructions in a virtual machine |

| US7234037B2 (en) | 2003-11-25 | 2007-06-19 | International Business Machines Corporation | Memory mapped Input/Output operations |

| US8024730B2 (en) * | 2004-03-31 | 2011-09-20 | Intel Corporation | Switching between protected mode environments utilizing virtual machine functionality |

| US7562209B2 (en) | 2004-04-07 | 2009-07-14 | Marvell International, Ltd. | Supporting different instruction set architectures during run time |

| US7339837B2 (en) * | 2004-05-18 | 2008-03-04 | Infineon Technologies Ag | Configurable embedded processor |

| US7260702B2 (en) | 2004-06-30 | 2007-08-21 | Microsoft Corporation | Systems and methods for running a legacy 32-bit x86 virtual machine on a 64-bit x86 processor |

| US7308571B2 (en) | 2004-10-06 | 2007-12-11 | Intel Corporation | Overriding processor configuration settings |

| US7647589B1 (en) | 2005-02-07 | 2010-01-12 | Parallels Software International, Inc. | Methods and systems for safe execution of guest code in virtual machine context |

| US7562349B2 (en) | 2005-04-25 | 2009-07-14 | Sap Ag | Version adaptation interface for integration of different virtual machines |

| US7496495B2 (en) | 2005-05-12 | 2009-02-24 | Microsoft Corporation | Virtual operating system device communication relying on memory access violations |

| KR100663864B1 (ko) * | 2005-06-16 | 2007-01-03 | 엘지전자 주식회사 | 멀티-코어 프로세서의 프로세서 모드 제어장치 및 방법 |

| JP2007007074A (ja) | 2005-06-29 | 2007-01-18 | Nagaoka Univ Of Technology | 温熱治療装置 |

| US7523291B2 (en) | 2005-07-26 | 2009-04-21 | International Business Machines Corporation | System and method for testing for memory address aliasing errors |

| RU2294010C1 (ru) | 2005-09-05 | 2007-02-20 | Павел Михайлович Шестаков | Способ обработки цифровых данных |

| US7409537B2 (en) | 2005-10-06 | 2008-08-05 | Microsoft Corporation | Fast booting an operating system from an off state |

| JP2007207074A (ja) | 2006-02-03 | 2007-08-16 | Ricoh Co Ltd | オペレーションシステム、スレッド制御機構、及び情報処理装置 |

| EP2087424A4 (en) | 2006-04-26 | 2009-12-23 | Tata Consultancy Services | SYSTEM AND METHOD FOR AUTOMATED RE-ARCHITECTURE OF FORMER SYSTEMS MODELS USING OBJECT-ORIENTED LANGUAGE |

| US8001549B2 (en) | 2006-04-27 | 2011-08-16 | Panasonic Corporation | Multithreaded computer system and multithread execution control method |

| US8117614B2 (en) | 2006-05-19 | 2012-02-14 | International Business Machines Corporation | Extract CPU time facility |

| CN100470476C (zh) * | 2006-05-25 | 2009-03-18 | 杭州晟元芯片技术有限公司 | 一种芯片上电后的程序引导方法 |

| US20080093277A1 (en) | 2006-06-13 | 2008-04-24 | John Armour | Cadence detection in a sequence of video fields |

| US8028290B2 (en) | 2006-08-30 | 2011-09-27 | International Business Machines Corporation | Multiple-core processor supporting multiple instruction set architectures |

| US8479264B2 (en) | 2006-09-29 | 2013-07-02 | Micron Technology, Inc. | Architecture for virtual security module |

| WO2008083277A1 (en) | 2006-12-31 | 2008-07-10 | San Disk Corporation | Portable multi-platform booting systems and architectures |

| US7783867B2 (en) * | 2007-02-01 | 2010-08-24 | International Business Machines Corporation | Controlling instruction execution in a processing environment |

| US7734900B2 (en) | 2008-01-11 | 2010-06-08 | International Business Machines Corporation | Computer configuration virtual topology discovery and instruction therefore |

| US8117417B2 (en) | 2008-01-11 | 2012-02-14 | International Business Machines Corporation | Dynamic address translation with change record override |

| US8677098B2 (en) | 2008-01-11 | 2014-03-18 | International Business Machines Corporation | Dynamic address translation with fetch protection |

| US7739434B2 (en) | 2008-01-11 | 2010-06-15 | International Business Machines Corporation | Performing a configuration virtual topology change and instruction therefore |

| US8321861B2 (en) | 2008-02-20 | 2012-11-27 | Arm Limited | Non-native program execution across multiple execution environments |

| US8176280B2 (en) | 2008-02-25 | 2012-05-08 | International Business Machines Corporation | Use of test protection instruction in computing environments that support pageable guests |

| US8086811B2 (en) | 2008-02-25 | 2011-12-27 | International Business Machines Corporation | Optimizations of a perform frame management function issued by pageable guests |

| US8095773B2 (en) | 2008-02-26 | 2012-01-10 | International Business Machines Corporation | Dynamic address translation with translation exception qualifier |

| US8301865B2 (en) | 2009-06-29 | 2012-10-30 | Oracle America, Inc. | System and method to manage address translation requests |

| US20110179254A1 (en) | 2010-01-15 | 2011-07-21 | Sun Microsystems, Inc. | Limiting speculative instruction fetching in a processor |

| GB2478726B (en) | 2010-03-15 | 2013-12-25 | Advanced Risc Mach Ltd | Mapping between registers used by multiple instruction sets |

| US9851969B2 (en) | 2010-06-24 | 2017-12-26 | International Business Machines Corporation | Function virtualization facility for function query of a processor |

| US10521231B2 (en) | 2010-06-24 | 2019-12-31 | International Business Machines Corporation | Function virtualization facility for blocking instruction function of a multi-function instruction of a virtual processor |

| US8479172B2 (en) | 2010-11-23 | 2013-07-02 | International Business Machines Corporation | Virtual machine testing |

| US9141389B2 (en) | 2011-04-07 | 2015-09-22 | Via Technologies, Inc. | Heterogeneous ISA microprocessor with shared hardware ISA registers |

| US9645822B2 (en) * | 2011-04-07 | 2017-05-09 | Via Technologies, Inc | Conditional store instructions in an out-of-order execution microprocessor |

| US8924695B2 (en) * | 2011-04-07 | 2014-12-30 | Via Technologies, Inc. | Conditional ALU instruction condition satisfaction propagation between microinstructions in read-port limited register file microprocessor |

| DE102011017596A1 (de) | 2011-04-27 | 2012-10-31 | Robert Bosch Gmbh | Mikrofluidisches System und Verfahren für eine Polymerase Kettenreaktion |

| US9063747B2 (en) | 2011-04-28 | 2015-06-23 | Freescale Semiconductor, Inc. | Microprocessor systems and methods for a combined register file and checkpoint repair register |

| TW201248499A (en) | 2011-05-18 | 2012-12-01 | Asustek Comp Inc | Method of swapping between operating systems applied to computer system |

| KR101780052B1 (ko) | 2011-08-24 | 2017-09-19 | 한국전자통신연구원 | 정보처리 시스템에서 운영체제 전환방법 |

| CN102955713B (zh) * | 2011-08-31 | 2015-11-25 | 北京中电华大电子设计有限责任公司 | 一种802.11n无线网卡芯片仿真固件优化的处理方法 |

| EP2791789A2 (en) | 2011-12-16 | 2014-10-22 | Hyperion Core, Inc. | Advanced processor architecture |

| US8930950B2 (en) | 2012-01-19 | 2015-01-06 | International Business Machines Corporation | Management of migrating threads within a computing environment to transform multiple threading mode processors to single thread mode processors |

| US9251027B2 (en) | 2012-03-05 | 2016-02-02 | Dell Productes L.P. | Information handling system performance optimization system |

| US9298469B2 (en) | 2012-06-15 | 2016-03-29 | International Business Machines Corporation | Management of multiple nested transactions |

| EP2891379B1 (en) | 2012-08-30 | 2019-07-31 | University of Virginia Patent Foundation, D/B/A University of Virginia | Ultra low power sensing platform with multimodal radios |

| US9348757B2 (en) | 2012-10-08 | 2016-05-24 | International Business Machines Corporation | System supporting multiple partitions with differing translation formats |

| JP6075013B2 (ja) | 2012-10-31 | 2017-02-08 | 富士通株式会社 | ログ取得プログラム、ログ取得装置及びログ取得方法 |

| US9582295B2 (en) | 2014-03-18 | 2017-02-28 | International Business Machines Corporation | Architectural mode configuration |

| US9916185B2 (en) | 2014-03-18 | 2018-03-13 | International Business Machines Corporation | Managing processing associated with selected architectural facilities |

| US9588774B2 (en) | 2014-03-18 | 2017-03-07 | International Business Machines Corporation | Common boot sequence for control utility able to be initialized in multiple architectures |

| US9594660B2 (en) | 2014-03-27 | 2017-03-14 | International Business Machines Corporation | Multithreading computer system and program product for executing a query instruction for idle time accumulation among cores |

| US9921848B2 (en) | 2014-03-27 | 2018-03-20 | International Business Machines Corporation | Address expansion and contraction in a multithreading computer system |

-

2014

- 2014-03-18 US US14/217,840 patent/US9582295B2/en active Active

- 2014-11-26 US US14/554,806 patent/US9594576B2/en active Active

-

2015

- 2015-03-09 HU HUE15711073A patent/HUE043750T2/hu unknown

- 2015-03-09 WO PCT/EP2015/054850 patent/WO2015139992A1/en active Application Filing

- 2015-03-09 ES ES15711073T patent/ES2717525T3/es active Active

- 2015-03-09 CA CA2940911A patent/CA2940911C/en active Active

- 2015-03-09 PL PL15711073T patent/PL3114561T3/pl unknown

- 2015-03-09 PT PT15711073T patent/PT3114561T/pt unknown

- 2015-03-09 RU RU2016127224A patent/RU2664413C2/ru active

- 2015-03-09 EP EP15711073.5A patent/EP3114561B1/en active Active

- 2015-03-09 SI SI201530669T patent/SI3114561T1/sl unknown

- 2015-03-09 JP JP2016557130A patent/JP6585612B2/ja active Active

- 2015-03-09 SG SG11201606095SA patent/SG11201606095SA/en unknown

- 2015-03-09 BR BR112016021602-4A patent/BR112016021602B1/pt active IP Right Grant

- 2015-03-09 KR KR1020167028754A patent/KR101884544B1/ko active IP Right Grant

- 2015-03-09 MX MX2016011921A patent/MX2016011921A/es active IP Right Grant

- 2015-03-09 LT LTEP15711073.5T patent/LT3114561T/lt unknown

- 2015-03-09 AU AU2015230885A patent/AU2015230885B2/en active Active

- 2015-03-09 DK DK15711073.5T patent/DK3114561T3/en active

- 2015-03-09 CN CN201580014479.7A patent/CN106133683B/zh active Active

- 2015-03-17 TW TW104108513A patent/TWI608363B/zh active

-

2016

- 2016-08-05 ZA ZA2016/05470A patent/ZA201605470B/en unknown

- 2016-09-15 IL IL247856A patent/IL247856B/en active IP Right Grant

-

2017

- 2017-01-09 US US15/401,693 patent/US10545772B2/en active Active

- 2017-03-10 US US15/455,198 patent/US10552175B2/en active Active

-

2019

- 2019-07-16 US US16/512,987 patent/US11029974B2/en active Active

- 2019-07-16 US US16/513,034 patent/US11023256B2/en active Active

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6585612B2 (ja) | アーキテクチャ・モードの構成 | |

| JP6437008B2 (ja) | 複数のアーキテクチャにおいて初期化することができる制御ユーティリティのための共通ブート・シーケンス | |

| JP6407299B2 (ja) | 選択されたアーキテクチャ・ファシリティと関連した処理の管理 | |

| US10027675B2 (en) | Determining virtual adapter access controls in a computing environment | |

| JP6521997B2 (ja) | 比較及び遅延(compare and delay)命令 | |

| US10061600B2 (en) | Ascertaining configuration of a virtual adapter in a computing environment |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161227 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20171116 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20181126 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20181211 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190308 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190813 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190905 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6585612 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |