JP6355459B2 - 撮像装置及びその制御方法 - Google Patents

撮像装置及びその制御方法 Download PDFInfo

- Publication number

- JP6355459B2 JP6355459B2 JP2014138019A JP2014138019A JP6355459B2 JP 6355459 B2 JP6355459 B2 JP 6355459B2 JP 2014138019 A JP2014138019 A JP 2014138019A JP 2014138019 A JP2014138019 A JP 2014138019A JP 6355459 B2 JP6355459 B2 JP 6355459B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- imaging

- image

- level

- period

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

図1は、本発明の実施形態に係る撮像装置100の全体構成を示すブロック図である。図1において、撮影レンズ101及び絞り102を通過した光は、撮影レンズ101の焦点位置近傍に結像する。撮像素子103はCMOSセンサであり、撮影レンズ101により結像された被写体像を光量に応じて電気信号に変換する。信号処理回路104は、撮像素子103から出力される画像信号に対して信号増幅、基準レベル調整等の各種の補正や、データの並べ替えなどを行う。タイミング発生回路105は撮像素子103や信号処理回路104等に駆動タイミング信号を出力する。

L2=T2/T1×L1×α …(1)

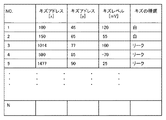

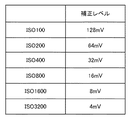

となる(αはT2/T1×α>1を満たす任意の係数)。このように、式(1)で算出されたキズレベルL2が、高ビット分解能モードでのリークキズのキズレベルとなる。キズレベルL2の算出後、S16において、図6のテーブルに従って、算出されたキズレベルL2が、S12で取得した感度における補正レベル以上であるかどうかを判断する。以降、上述したS17及びS18の処理を行う。

画像のキズ、及びノイズ補正としては、撮影された画像からキズ画素を検出して補正を行う、リアルタイムキズ補正方法がある。リアルタイムキズ補正も公知の技術であり、様々な手法が開示されているが、基本的には得られた画素の出力が周辺画素の信号に対して予め設定した閾値以上のレベル差があれば欠陥画素と判定し、キズ補正を実施するものである。

次に、本発明の第2の実施形態について説明する。撮像装置100の全体的な構成は、図1を参照して説明したものと同様であるが、撮像素子103の構成が第1の実施形態において説明したものと異なる。以下、図9を参照して、本発明の第2の実施形態における撮像素子103の構成について説明する。

L4=T4/T3×L3×α …(2)

により求める(αはT4/T3×α>1を満たす任意の係数)。

次に、本発明の第3の実施形態について説明する。第2の実施形態において、図11に示す撮像素子103の駆動方法について2つのモードを説明した。撮像面位相差AFモードにおいては、AF用の情報と撮像用の情報の両方を取得可能であるが、A像信号を読み出してから、A+B像信号を読み出すため、通常撮影モードに比べて1枚の画像取得に必要な読み出し時間が長くなりフレームレートが下がってしまう。

Claims (11)

- 撮像素子と、該撮像素子から読み出された信号を処理して画像を生成する画像処理手段とを有する撮像装置であって、

前記撮像素子が、

複数のマイクロレンズと、

前記複数のマイクロレンズそれぞれに、少なくとも1つの光電変換部が対応するように構成された複数の光電変換部と、

前記複数の光電変換部から撮像信号を読み出す読み出し手段と、

読み出された撮像信号を保持するメモリとを有し、

前記撮像素子は、前記読み出し手段が前記複数の光電変換部に蓄積された撮像信号を読み出して前記メモリに保持するまでの信号読み出し期間が異なる、少なくとも2つ以上の駆動方法により駆動され、

前記画像処理手段は、前記読み出された撮像信号のノイズを低減するノイズ低減処理を行うノイズ低減手段を備え、該ノイズ低減手段は、前記読み出された撮像信号のうち、前記ノイズ低減処理を行う撮像信号を判定して前記ノイズ低減処理を行い、該判定を行う際に、前記信号読み出し期間の異なる2つ以上の駆動方法において該判定のレベルを調整することを特徴とする撮像装置。 - 前記ノイズ低減手段は、前記信号読み出し期間が第1の期間の場合に、前記第1の期間よりも短い第2の期間の場合よりも前記ノイズ低減処理を行う撮像信号と判定されやすくなるように前記判定のレベルを調整することを特徴とする請求項1に記載の撮像装置。

- 予め決められた条件で撮影を行った場合に、欠陥が現れる撮像信号に対応した光電変換部のアドレスと、欠陥の種類と、欠陥のレベルとを含む欠陥情報を予め記憶した記憶手段を更に有し、

前記ノイズ低減手段は、前記信号読み出し期間に応じて前記欠陥のレベルが変わる種類の欠陥に対して、前記予め決められた条件における信号読み出し期間と、前記撮像信号の読み出しにかかった信号読み出し期間との比に応じて、前記欠陥のレベルを調整することを特徴とする請求項1または2に記載の撮像装置。 - 前記ノイズ低減手段は前記撮像素子の感度を取得し、該感度が第1の感度の場合、前記第1の感度よりも低い第2の感度の場合よりもより低い欠陥のレベルで前記ノイズ低減処理を行うと判定することを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。

- 前記ノイズ低減手段は、撮影ごとに前記撮像信号のレベルに応じて欠陥画素を検出して補正する処理を行い、前記欠陥画素を検出するための閾値は、前記信号読み出し期間が第3の期間の場合に、前記第3の期間よりも短い第4の期間の場合よりも低いことを特徴とする請求項1または2に記載の撮像装置。

- 前記メモリに保持された信号をアナログデジタル変換する変換手段を更に有し、

前記読み出し手段は、前記撮像信号に先立って前記撮像素子からリセットレベルの信号を読み出して前記メモリに保持し、前記変換手段により前記保持されたリセットレベルの信号の変換が終了してから、前記撮像信号の読み出しを開始することを特徴とする請求項1乃至5のいずれか1項に記載の撮像装置。 - 前記駆動方法は、前記変換手段に異なるビット数のデジタル信号に変換させる駆動方法を含み、ビット数が多いほど、前記信号読み出し期間が長くなることを特徴とする請求項6に記載の撮像装置。

- 前記読み出し手段は、前記複数の光電変換部の撮像信号を予め決められた数ずつ加算して読み出し、

前記ノイズ低減手段は、前記加算数が同じで、かつ前記信号読み出し期間の長さが異なる場合に、前記判定のレベルを調整することを特徴とする請求項1乃至7のいずれか1項に記載の撮像装置。 - 前記撮像素子は、前記複数のマイクロレンズの少なくとも一部のマイクロレンズそれぞれに、複数の光電変換部が対応するように構成され、

前記駆動方法は、前記各マイクロレンズに対応する前記複数の光電変換部からの前記撮像信号を加算して読み出す第1の駆動方法と、前記複数の光電変換部それぞれの前記撮像信号を取得可能に読み出す第2の駆動方法とを含み、

前記第1の駆動方法よりも、前記第2の駆動方法による前記信号読み出し期間が長いことを特徴とする請求項1乃至7のいずれか1項に記載の撮像装置。 - 前記読み出し手段は、各フレームにおいて、前記第1の駆動方法と前記第2の駆動方法による読み出しを、予め決められた割合で行単位で行うことを特徴とする請求項9に記載の撮像装置。

- 複数のマイクロレンズと、前記複数のマイクロレンズそれぞれに、少なくとも1つの光電変換部が対応するように構成された複数の光電変換部と、前記複数の光電変換部から撮像信号を読み出す読み出し手段と、読み出された撮像信号を保持するメモリとを有する撮像素子と、該撮像素子から読み出された信号を処理して画像を生成する画像処理手段とを有する撮像装置の制御方法であって、

前記撮像素子は、前記読み出し手段が前記複数の光電変換部に蓄積された撮像信号を読み出して前記メモリに保持するまでの信号読み出し期間が異なる、少なくとも2つ以上の駆動方法により駆動され、前記画像処理手段は、前記読み出された撮像信号のノイズを低減するノイズ低減処理を行うノイズ低減手段を備え、

前記ノイズ低減手段が、前記撮像信号の読み出しに用いられた駆動方法による信号読み出し期間を取得する取得工程と、

前記ノイズ低減手段が、前記信号読み出し期間の異なる2つ以上の駆動方法において、前記読み出された撮像信号のうち、前記ノイズ低減処理を行う撮像信号を判定するレベルを調整する調整工程と、

前記調整されたレベルに応じて前記ノイズ低減処理を行う撮像信号を判定する判定工程と

を有することを特徴とする撮像装置の制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014138019A JP6355459B2 (ja) | 2014-07-03 | 2014-07-03 | 撮像装置及びその制御方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014138019A JP6355459B2 (ja) | 2014-07-03 | 2014-07-03 | 撮像装置及びその制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016015695A JP2016015695A (ja) | 2016-01-28 |

| JP2016015695A5 JP2016015695A5 (ja) | 2017-08-10 |

| JP6355459B2 true JP6355459B2 (ja) | 2018-07-11 |

Family

ID=55231561

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014138019A Active JP6355459B2 (ja) | 2014-07-03 | 2014-07-03 | 撮像装置及びその制御方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6355459B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6736329B2 (ja) * | 2016-03-31 | 2020-08-05 | キヤノン株式会社 | 撮像素子 |

| JP6765859B2 (ja) | 2016-05-31 | 2020-10-07 | キヤノン株式会社 | 撮像装置、およびその制御方法 |

| JP6701001B2 (ja) * | 2016-06-22 | 2020-05-27 | キヤノン株式会社 | 撮像装置及びその制御方法、プログラム、記憶媒体 |

| JP2018148263A (ja) * | 2017-03-01 | 2018-09-20 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像装置、及び、電子機器 |

| JP7250428B2 (ja) * | 2018-03-22 | 2023-04-03 | キヤノン株式会社 | 撮像装置およびその制御方法 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3927702B2 (ja) * | 1998-09-24 | 2007-06-13 | キヤノン株式会社 | 画像処理装置、自動焦点検出装置、補正装置、補正方法及び記憶媒体 |

| JP4977541B2 (ja) * | 2007-07-18 | 2012-07-18 | 富士フイルム株式会社 | ディジタル・カメラおよびその動作制御方法 |

| JP5153563B2 (ja) * | 2008-10-21 | 2013-02-27 | キヤノン株式会社 | 固体撮像装置及びその駆動方法 |

| JP5742313B2 (ja) * | 2011-03-10 | 2015-07-01 | 株式会社ニコン | 撮像装置 |

| JP5893572B2 (ja) * | 2012-03-01 | 2016-03-23 | キヤノン株式会社 | 撮像装置、撮像システム、撮像装置の駆動方法 |

| JP5968146B2 (ja) * | 2012-07-31 | 2016-08-10 | キヤノン株式会社 | 固体撮像装置およびカメラ |

-

2014

- 2014-07-03 JP JP2014138019A patent/JP6355459B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016015695A (ja) | 2016-01-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9894295B2 (en) | Imaging device and imaging system | |

| US10038868B2 (en) | Solid-state image sensing device and electronic device | |

| US9531972B2 (en) | Solid-state imaging device, method for driving the same, and imaging device | |

| JP5852324B2 (ja) | 撮像装置及びその制御方法、プログラム | |

| WO2017047010A1 (en) | Image sensor and image capturing apparatus | |

| JP5312246B2 (ja) | 撮像装置及び制御方法 | |

| US20140192249A1 (en) | Image capturing apparatus and method for controlling the same | |

| US20130070129A1 (en) | Image capturing apparatus and defective pixel detection method | |

| JP6602109B2 (ja) | 制御装置、撮像装置、制御方法、プログラム、および、記憶媒体 | |

| US10630912B2 (en) | Image sensor, image capturing apparatus, and method for controlling image sensor | |

| JP6355459B2 (ja) | 撮像装置及びその制御方法 | |

| JP2010245891A (ja) | 撮像装置および撮像方法 | |

| US8169524B2 (en) | Image sensing apparatus with pixel readout correction | |

| US10277855B2 (en) | Image sensing device and control method thereof with switchable analog-to-digital conversion modes based on the amount of dark current generated in pixels | |

| US20180295307A1 (en) | Image sensing apparatus and control method therefor | |

| JP2008017100A (ja) | 固体撮像装置 | |

| JP2008148082A (ja) | 固体撮像装置 | |

| JP2016167773A (ja) | 撮像装置及び撮像装置の処理方法 | |

| JP2008118571A (ja) | 撮像装置及びその制御方法 | |

| JP2020057892A (ja) | 撮像装置 | |

| US10368020B2 (en) | Image capturing apparatus and control method therefor | |

| JP2018133685A (ja) | 撮像素子、その制御方法、および制御プログラム、並びに撮像装置 | |

| JP2021072529A (ja) | 撮像装置及びその制御方法 | |

| JP2019186817A (ja) | 固体撮像素子、撮像装置および固体撮像素子の制御方法 | |

| JP2010141392A (ja) | 固体撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170630 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170630 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180427 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180514 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180612 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6355459 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |