JP6340517B2 - Gaming machine - Google Patents

Gaming machine Download PDFInfo

- Publication number

- JP6340517B2 JP6340517B2 JP2016082209A JP2016082209A JP6340517B2 JP 6340517 B2 JP6340517 B2 JP 6340517B2 JP 2016082209 A JP2016082209 A JP 2016082209A JP 2016082209 A JP2016082209 A JP 2016082209A JP 6340517 B2 JP6340517 B2 JP 6340517B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- master

- control device

- expander

- address

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000000694 effects Effects 0.000 claims description 158

- 230000005540 biological transmission Effects 0.000 claims description 116

- 238000012545 processing Methods 0.000 claims description 107

- 238000003860 storage Methods 0.000 claims description 86

- 238000005034 decoration Methods 0.000 description 332

- 238000000034 method Methods 0.000 description 192

- 230000008569 process Effects 0.000 description 183

- 230000005856 abnormality Effects 0.000 description 110

- 230000004044 response Effects 0.000 description 84

- 102100036409 Activated CDC42 kinase 1 Human genes 0.000 description 71

- 239000000758 substrate Substances 0.000 description 48

- 238000012544 monitoring process Methods 0.000 description 45

- 239000000872 buffer Substances 0.000 description 40

- 238000010586 diagram Methods 0.000 description 27

- 238000011144 upstream manufacturing Methods 0.000 description 27

- 230000008859 change Effects 0.000 description 25

- 101000741965 Homo sapiens Inactive tyrosine-protein kinase PRAG1 Proteins 0.000 description 23

- 102100038659 Inactive tyrosine-protein kinase PRAG1 Human genes 0.000 description 23

- 238000009877 rendering Methods 0.000 description 22

- 239000003990 capacitor Substances 0.000 description 19

- 238000001514 detection method Methods 0.000 description 16

- 230000002829 reductive effect Effects 0.000 description 11

- 230000006870 function Effects 0.000 description 10

- 239000011521 glass Substances 0.000 description 10

- 238000009499 grossing Methods 0.000 description 9

- 230000006854 communication Effects 0.000 description 7

- 238000004891 communication Methods 0.000 description 7

- 230000004397 blinking Effects 0.000 description 6

- 238000012790 confirmation Methods 0.000 description 6

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 5

- 238000005286 illumination Methods 0.000 description 5

- 230000000670 limiting effect Effects 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 238000012546 transfer Methods 0.000 description 5

- 230000002159 abnormal effect Effects 0.000 description 4

- 230000001360 synchronised effect Effects 0.000 description 4

- 239000006059 cover glass Substances 0.000 description 3

- 230000005669 field effect Effects 0.000 description 3

- 208000025174 PANDAS Diseases 0.000 description 2

- 208000021155 Paediatric autoimmune neuropsychiatric disorders associated with streptococcal infection Diseases 0.000 description 2

- 240000004718 Panda Species 0.000 description 2

- 235000016496 Panda oleosa Nutrition 0.000 description 2

- 230000002457 bidirectional effect Effects 0.000 description 2

- 238000010924 continuous production Methods 0.000 description 2

- 230000001419 dependent effect Effects 0.000 description 2

- 230000001678 irradiating effect Effects 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 238000007726 management method Methods 0.000 description 2

- 230000008054 signal transmission Effects 0.000 description 2

- 101100365021 Arabidopsis thaliana SCL9 gene Proteins 0.000 description 1

- 240000001973 Ficus microcarpa Species 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000007175 bidirectional communication Effects 0.000 description 1

- OMFRMAHOUUJSGP-IRHGGOMRSA-N bifenthrin Chemical compound C1=CC=C(C=2C=CC=CC=2)C(C)=C1COC(=O)[C@@H]1[C@H](\C=C(/Cl)C(F)(F)F)C1(C)C OMFRMAHOUUJSGP-IRHGGOMRSA-N 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000013256 coordination polymer Substances 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 238000010304 firing Methods 0.000 description 1

- 230000002401 inhibitory effect Effects 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 239000002023 wood Substances 0.000 description 1

Images

Landscapes

- Pinball Game Machines (AREA)

Description

グループに分割された演出装置を制御する複数のグループ単位制御手段と、複数のグループ単位制御手段を制御するグループ統括制御手段とを備える遊技機に関する。 About the gaming machine comprising a plurality of group units control means for controlling the effect device which is divided into groups, and the group supervisory controlling means for controlling a plurality of group units control means.

サブ中継基板と電飾基板との間の配線を簡素化することができる遊技機として、トップ

電飾領域の中央部に配置されたトップLED中央基板をサブ中継基板とシリアル接続し、

トップ電飾領域の右側部に配置されたトップLED右基板及びトップ電飾領域の左側部に

配置されたトップLED左基板をトップLED中央基板から分離して配線により接続した

構成の遊技機が知られている。これにより、サブ中継基板からトップ電飾領域への配線数

を減らして配線を簡素化することができる(例えば、特許文献1参照)。

As a gaming machine capable of simplifying the wiring between the sub relay board and the electric decoration board, the top LED central board disposed in the center of the top electric decoration area is serially connected to the sub relay board,

A gaming machine is known in which the top LED right substrate disposed on the right side of the top illumination area and the top LED left substrate disposed on the left side of the top illumination area are separated from the top LED central substrate and connected by wiring It is done. As a result, the number of wires from the sub relay board to the top illumination area can be reduced to simplify the wires (see, for example, Patent Document 1).

また、信号線の数を削減することができると共に不正行為の発見を容易に行うことがで

きる遊技機として、主基板と副基板との間での信号送信をI2Cバス方式により行い、主

基板及び副基板にそれぞれ双方向バスバッファを設けたものがある。この双方向バスバッ

ファは、I2Cバスを構成する二つの双方向シリアルライン(SDA、SCL)をそれぞ

れ二つの片方向シリアルラインに分岐させるためのものであり、主基板に設けられた双方

向バスバッファと副基板に設けられた双方向バスバッファとの間を、それらによって分岐

された片方向シリアルラインの信号伝送方向が互いに一致するようにして、四つのシリア

ル線で接続した構成としている(例えば、特許文献2参照)。

In addition, as a gaming machine that can reduce the number of signal lines and easily detect fraudulent activity, it performs signal transmission between the main substrate and the sub substrate by the I 2 C bus system, and Some substrates and sub substrates are provided with bidirectional bus buffers, respectively. This bi-directional bus buffer is for branching the two bi-directional serial lines (SDA, SCL) constituting the I 2 C bus into two unidirectional serial lines, respectively. Between the bus buffer and the bidirectional bus buffer provided on the sub board, the signal transmission directions of the unidirectional serial lines branched by them are made to coincide with each other, and they are connected by four serial lines (see FIG. See, for example, Patent Document 2).

従来の遊技機では、配線を十分に削減することができなかった。 In conventional gaming machines, it was not possible to sufficiently reduce wiring.

本発明は、グループ統括制御手段とグループ単位制御手段との間の配線を削減することのできる遊技機を提供することを目的とする。 The present invention aims to provide a game machine that can of reducing the wiring between the group supervisory controlling means and the group-unit control unit.

本発明は、複数の演出装置を複数グループに分割し、該分割されたグループに属する演出装置を制御するためのグループ単位制御手段をグループ毎に備えるとともに、前記グループ単位制御手段の各々を統括的に制御するグループ統括制御手段と、前記グループ統括制御手段を制御する演算処理手段と、を備え、前記演算処理手段と前記グループ統括制御手段の間に、初期化信号を伝達可能な初期化信号線を備えることによって、前記演算処理手段によって前記グループ統括制御手段の初期化を可能にするとともに、前記グループ統括制御手段と前記グループ単位制御手段との間を、タイミング信号を伝達するタイミング信号線と、データ信号を伝達するデータ線と、前記グループ単位制御手段に電源電圧を供給する電源線と、を含むハーネスによりコネクタを介して接続することで前記グループ統括制御手段から前記グループ単位制御手段に複数の制御データを含むデータを送信可能とし、前記グループ統括制御手段が送信するデータには、前記グループ単位制御手段に設けられた記憶領域のうちの所定のアドレスを示すアドレス情報と、前記複数の制御データと、前記記憶領域の範囲内においてアドレスを更新する際の上限アドレスと戻りアドレスを特定可能なアドレス更新情報と、が含まれ、前記グループ単位制御手段は、当該グループ単位制御手段に電源供給が開始されると、当該グループ単位制御手段自身を電源供給による電圧上昇に基づいて初期化する初期化手段を備え、前記アドレス情報が示すアドレスを開始アドレスとして、前記グループ統括制御手段より送信された制御データを記憶するとともに、制御データを記憶する毎に記憶先のアドレスを順次更新する機能を有し、前記上限アドレスが示す記憶領域に制御データを記憶した場合は、前記戻りアドレスに戻るように記憶先のアドレスを更新し、前記グループ統括制御手段は、前記アドレス更新情報として、前記上限アドレス又は前記戻りアドレスの異なる複数のアドレス更新情報のうちのいずれかを指定可能である。 The present invention divides a plurality of rendering devices into a plurality of groups, and comprises group unit control means for controlling the rendering devices belonging to the divided groups for each group, and supervising each of the group unit control means And an arithmetic processing means for controlling the group general control means, and an initialization signal line capable of transmitting an initialization signal between the arithmetic processing means and the group general control means. And a timing signal line for transmitting a timing signal between the group general control means and the group unit control means while enabling initialization of the group general control means by the arithmetic processing means. A harness including a data line transmitting a data signal, and a power supply line supplying a power supply voltage to the group unit control means. And capable of sending data including a plurality of control data from said group supervisory controlling means by connecting via the connector to the group-unit control unit allows the data to which the group supervisory controlling means sends, the group-unit control unit Address update information that can specify an upper limit address and a return address when updating an address within the range of the storage area, address information indicating a predetermined address among storage areas provided in the storage area, the plurality of control data, And the group unit control means includes initialization means for initializing the group unit control means itself based on the voltage rise due to the power supply when the power supply to the group unit control means is started. , as the starting address the address where the address information indicating the transmission than the group supervisory controlling means Stores the control data has a function to sequentially update the storage destination address for each for storing control data, when storing the control data in the storage area in which the upper address indicates, like back to the return address The address of the storage destination is updated, and the group general control means can designate, as the address update information, any one of a plurality of address update information different in the upper limit address or the return address .

本発明によれば、グループ統括制御手段とグループ単位制御手段との間の配線を削減することができる。 It is possible to reduce wiring between the I lever, the group supervisory controlling means and the group-unit control unit to the present invention.

(第1実施形態)

以下、本発明の第1実施形態について、図1〜図32を参照して説明する。

First Embodiment

Hereinafter, a first embodiment of the present invention will be described with reference to FIGS.

図1は、本発明の第1実施形態の遊技機1の説明図である。

FIG. 1 is an explanatory view of a

遊技機1の前面枠(遊技枠)3は本体枠(外枠)2にヒンジ4を介して、遊技機1の前

面に開閉回動可能に組み付けられる。前面枠3の表側には、遊技盤10(図2参照)が収

装される。また、前面枠3には、遊技盤10の前面を覆うカバーガラス(透明部材)を備

えたガラス枠18が取り付けられている。

The front frame (game frame) 3 of the

ガラス枠18のカバーガラスの周囲には、装飾光が発光される装飾部材9が備えられて

いる。この装飾部材9の内部にはランプやLED等からなる装飾装置620(図3参照)

が備えられている。この装飾装置620を所定の発光態様によって発光することによって

、装飾部材9が所定の発光態様によって発光する。

A

Is equipped. When the

ガラス枠18の左右には、音響(例えば、効果音)を発するスピーカ30が備えられて

いる。また、ガラス枠18の上方には照明ユニット11が備えられている。照明ユニット

11の内部には、前述した装飾装置620が備えられている。

At the left and right of the

照明ユニット11の右側には、遊技機1において異常が発生したことを報知するための

異常報知LED29が備えられている。

An

前面枠3の下部の開閉パネル20には図示しない打球発射装置に遊技球を供給する上皿

21が、固定パネル22には灰皿15、下皿23及び打球発射装置の操作部24等が備え

られる。下皿23には、下皿23に貯まった遊技球を排出するための下皿球抜き機構16

が備えられる。前面枠3下部右側には、ガラス枠18を施錠するための鍵25が備えられ

ている。

An

Is provided. A key 25 for locking the

また、遊技者が操作部24を回動操作することによって、打球発射装置は、上皿21か

ら供給される遊技球を発射する。

In addition, when the player rotates the

また、上皿21の上縁部には、遊技者からの操作入力を受け付けるための演出ボタン1

7が備えられている。

In addition, at the upper edge of the

7 are provided.

遊技者が演出ボタン17を操作することによって、遊技盤10に設けられた表示装置5

3(図2参照)における特図変動表示ゲームの演出内容を選択して、表示装置53におけ

る特図変動表示ゲームに、遊技者の操作を介入させた演出を行うことができる。

The

The effect contents of the special view variation display game in 3 (refer to FIG. 2) can be selected, and the special view variation display game in the

なお、特図変動表示ゲームは、発射された遊技球が遊技盤10に備わる第1始動入賞口

45(図2参照)又は普通変動入賞装置36(図2参照)の第2始動入賞口に入賞した場

合に開始される。特図変動表示ゲームでは、表示装置53において複数の識別情報が変動

表示する。そして、変動表示していた識別情報が停止し、停止した識別情報の結果態様が

特定の結果態様である場合に、遊技機1の状態が遊技者に有利な状態(特典が付与される

状態)である特別遊技状態に遷移する。

In the special view variation display game, the first starting winning opening 45 (see FIG. 2) or the second starting winning opening of the normal variation winning device 36 (see FIG. 2) provided on the

上皿21の右上部には、遊技者が遊技球を借りる場合に操作する球貸ボタン26、及び

、図示しないカードユニットからプリペイドカードを排出させるために操作される排出ボ

タン27が設けられている。これらのボタン26、27の間には、プリペイドカードの残

高を表示する残高表示部28が設けられる。

In the upper right portion of the

図2は、本発明の第1実施形態の遊技盤10の正面図である。

FIG. 2 is a front view of the

図1に示す遊技機1は、内部の遊技領域10a内に遊技球を発射して(弾球して)遊技

を行うもので、ガラス枠18のカバーガラスの奥側には、遊技領域10aを構成する遊技

盤10が設置されている。

The

遊技盤10は、各種部材の取付ベースとなる平板状の遊技盤本体10b(木製又は合成

樹脂製)を備え、該遊技盤本体10bの前面にガイドレール32で囲まれた遊技領域10

aを有している。また、遊技盤本体10bの前面であってガイドレール32の外側には、

前面構成部材33、33、…が取り付けられている。そして、このガイドレール32で囲

まれた遊技領域10a内に発射装置から遊技球(打球;遊技媒体)を発射して遊技を行う

ようになっている。

The

have a. In addition, on the front of the game board

The

遊技領域10aの略中央には、特図変動表示ゲームの表示領域となる窓部52を形成す

るセンターケース51が取り付けられている。このセンターケース51に形成された窓部

52の後方には、複数の識別情報を変動表示する特図変動表示ゲームの演出を実行可能な

演出表示装置としての表示装置53が配されるようになっている。この表示装置53は、

例えば、液晶ディスプレイを備え、表示内容が変化可能な表示部53aがセンターケース

51の窓部52を介して遊技盤10の前面側から視認可能となるように配されている。な

お、表示装置53は、液晶ディスプレイを備えるものに限らず、EL、CRT等のディス

プレイを備えるものであってもよい。

At the approximate center of the

For example, a liquid crystal display is provided, and a

センターケース51の窓部52の上端付近には、遊技状態に基づいて動作可能な可動役

物60が取り付けられる。

In the vicinity of the upper end of the

また、遊技盤10には、普図始動ゲート34と、普図変動表示ゲームの未処理回数を表

示する普図記憶表示器47、普図変動表示ゲームを表示する普図表示器35が設けられて

いる。また、遊技領域10a内には、第1の始動入賞領域をなす第1始動入賞口45と、

第2の始動入賞領域をなす第2始動入賞口を有する普通変動入賞装置36と、が設けられ

ている。そして、遊技球が第1始動入賞口45に入賞した場合は、補助遊技として第1特

図変動表示ゲームが実行され、遊技球が普通変動入賞装置36に入賞した場合は、補助遊

技として第2特図変動表示ゲームが実行されるようになっている。

Further, the

A normal

また、遊技盤10には、第1特図変動表示ゲームを表示する第1特図表示器38と、第

2特図変動表示ゲームを表示する第2特図表示器39と、が設けられている。また、第1

特図変動表示ゲームの未処理回数(第1特図始動記憶)を表示する第1特図記憶表示器4

8と、第2特図変動表示ゲームの未処理回数(第2特図始動記憶)を表示する第2特図記

憶表示器49が設けられている。なお、普図記憶表示器47、普図表示器35、第1特図

表示器38、第2特図表示器39、第1特図記憶表示器48、第2特図記憶表示器49は

、遊技状態を表す遊技状態表示LED(図示略)と併せて、セグメントLEDとして一体

に設けられている。

In addition, the

First special

A second special

さらに遊技領域10aには、上端側が手前側に倒れる方向に回動して開放可能になって

いるアタッカ形式の開閉扉42aを有し、第1特図変動表示ゲーム、第2特図変動表示ゲ

ームの結果如何によって大入賞口を閉じた状態(遊技者にとって不利な状態)から開放状

態(遊技者にとって有利な状態)に変換する特別変動入賞装置42、入賞口などに入賞し

なかった遊技球を回収するアウト穴43が設けられている。この他、遊技領域10aには

、一般入賞口44、44、…、打球方向変換部材としての風車46、多数の障害釘(図示

略)などが配設されている。

Furthermore, in the

普図始動ゲート34内には、該普図始動ゲート34を通過した遊技球を検出するための

ゲートSW34a(図3参照)が設けられている。そして、遊技領域10a内に打ち込ま

れた遊技球が普図始動ゲート34内を通過すると、普図変動表示ゲームが行われる。

In the drawing

また、普図変動表示ゲームを開始できない状態中に、普図始動ゲート34を遊技球が通

過すると、普図始動記憶数が上限数未満であるならば、普図始動記憶数が1加算されて、

当該普図変動表示ゲームが当りとなるか否かを示す乱数が普図始動記憶として一つ記憶さ

れる。

In addition, when the game ball passes the common drawing start

A random number indicating whether or not the common drawing variation display game is hit is stored as one common drawing start memory.

普図変動表示ゲームが開始できない状態とは、例えば、普図変動表示ゲームが既に行わ

れ、その普図変動表示ゲームが終了していない状態や、普図変動表示ゲームが当って普通

変動入賞装置36が開状態に変換されている状態のことをいう。

The state in which the common drawing fluctuation display game can not be started means, for example, a state in which the common drawing fluctuation display game has already been played and the common drawing fluctuation display game has not ended, or the common drawing fluctuation display game hits 36 refers to a state in which it is converted to the open state.

なお、普図変動表示ゲームの始動記憶数は、LEDを備える普図記憶表示器47にて表

示される。

In addition, the starting memory number of the common drawing variation display game is displayed on the common

普図変動表示ゲームは、遊技盤10に設けられた普図表示器35で実行されるようにな

っている。なお、表示装置53の表示領域の一部で普図変動表示ゲームを表示するように

してもよく、この場合は識別図柄として、例えば、数字、記号、キャラクタ図柄などを用

い、この識別図柄を所定時間変動表示させた後、停止表示させることにより行うようにす

る。

The common drawing variation display game is to be executed by the

この普図変動表示ゲームの停止表示が特別の結果態様となれば、普図変動表示ゲームが

当りとなって、普通変動入賞装置36の開閉部材36a、36aが所定時間(例えば、0

.5秒間)開放される。これにより、普通変動入賞装置36に遊技球が入賞しやすくなり

、第2特図変動表示ゲームの始動が容易となる。

If the stop display of the common drawing fluctuation display game is a special result mode, the common drawing fluctuation display game becomes a hit, and the opening /

Open for .5 seconds) Thereby, the game ball easily wins the normal

普通変動入賞装置36は左右一対の開閉部材36a、36aを具備し、第1始動入賞口

45の下部に配設される。この開閉部材36a、36aは、常時は遊技球の直径程度の間

隔をおいて閉じた状態(遊技者にとって不利な状態)を保持しているが、普図変動表示ゲ

ームの結果が所定の停止表示態様となった場合(普図変動表示ゲームが当りとなった場合

)には、駆動装置としてのソレノイド(普電SOL36b、図3参照)によって、逆「ハ

」の字状に開いて普通変動入賞装置36に遊技球が流入し易い状態(遊技者にとって有利

な状態)に変化させられるようになっている。

The normal

また、本実施形態の遊技機1は、特図変動表示ゲームの結果態様に基づき、遊技状態と

して、表示装置53における特図変動表示ゲームの変動表示時間を短縮する時短動作状態

(第2動作状態)を発生可能となっている。この時短動作状態(第2動作状態)は、普通

変動入賞装置36の動作状態が、通常動作状態(第1動作状態)に比べて開放状態となり

やすい状態である。

In addition, the

この時短動作状態においては、上述の普図変動表示ゲームの実行時間が、通常動作状態

における長い実行時間よりも短くなるように制御され(例えば、10秒が1秒)、これに

より、単位時間当りの普通変動入賞装置36の開放回数が実質的に多くなるように制御さ

れる。また、時短動作状態においては、普図変動表示ゲームが当り結果となって普通変動

入賞装置36が開放される場合に、開放時間が通常動作状態の短い開放時間より長くされ

るように制御される(例えば、0.3秒が1.8秒)。また、時短動作状態においては、

普図変動表示ゲームの1回の当り結果に対して、普通変動入賞装置36が1回ではなく、

複数回(例えば、2回)開放される。さらに、時短動作状態においては普図変動表示ゲー

ムの当り結果となる確率が通常動作状態より高くなるように制御される。すなわち、通常

動作状態よりも普通変動入賞装置36の開放回数が増加され、普通変動入賞装置36に遊

技球が入賞しやすくなり、第2特図変動表示ゲームの始動が容易となる。

At this time, in the short operation state, the execution time of the above-mentioned common view variation display game is controlled to be shorter than the long execution time in the normal operation state (for example, 10 seconds is one second), whereby The number of opening of the normal

The normal

It is opened multiple times (for example, twice). Furthermore, in the short-time operation state, the probability of being a hit result of the common view variation display game is controlled to be higher than that in the normal operation state. That is, the number of times the normal

第1始動入賞口45の内部には第1始動口SW45a(図3参照)が備えられ、この第

1始動口SW45aによって遊技球を検出することに基づき、補助遊技としての第1特図

変動表示ゲームを開始する始動権利が発生するようになっている。また、普通変動入賞装

置36の内部には第2始動口SW36d(図3参照)が備えられ、この第2始動口SW3

6dによって遊技球を検出することに基づき、補助遊技としての第2特図変動表示ゲーム

を開始する始動権利が発生するようになっている。

A first

Based on the detection of the game ball by 6d, a start right to start a second special view variation display game as an auxiliary game is generated.

この第1特図変動表示ゲームを開始する始動権利は、所定の上限数(例えば4)の範囲

内で第1始動記憶(特図1始動記憶)として記憶される。そして、この第1始動記憶数は

、第1特図記憶表示器48に表示される。また、第2特図変動表示ゲームを開始する始動

権利は、所定の上限数(例えば4)の範囲内で第2始動記憶(特図2始動記憶)として記

憶される。そして、この第2始動記憶数は、第2特図記憶表示器49にて表示される。

The right to start the first special view variable display game is stored as a first start storage (

そして、第1特図変動表示ゲームが開始可能な状態(第1始動記憶数及び第2始動記憶

数が0の状態)で、第1始動入賞口45に遊技球が入賞すると、始動権利の発生に伴って

抽出された乱数が第1始動記憶として記憶されて、第1始動記憶数が1加算されるととと

もに、直ちに第1始動記憶に基づいて、第1特図変動表示ゲームが開始され、この際に第

1始動記憶数が1減算される。

Then, when the gaming ball is won in the first

また、第2特図変動表示ゲームは第1特図変動表示ゲームよりも優先して実行されるた

め、第1始動記憶数が0でなくても、第2始動記憶数が0であれば、第2始動入賞口をな

す普通変動入賞装置36に遊技球が入賞すると、始動権利の発生に伴って抽出された乱数

が第2始動記憶として記憶されて、第2始動記憶数が1加算されるととともに、実行中の

第1特図変動表示ゲームが終了後直ちに第2始動記憶に基づいて、第2特図変動表示ゲー

ムが開始され、この際に第2始動記憶数が1減算される。

Further, since the second special view variation display game is executed prior to the first special view variation display game, even if the first start storage number is not zero, if the second start storage number is zero, When the game ball wins in the normal

一方、第1特図変動表示ゲーム又は第2特図変動表示ゲームが直ちに開始できない状態

、例えば、既に第1特図変動表示ゲーム又は第2特図変動表示ゲームが行われ、その特図

変動表示ゲームが終了していない状態や、特別遊技状態となっている場合に、第1始動入

賞口45に遊技球が入賞すると、第1始動記憶数が上限数未満(例えば、4個未満)なら

ば、第1始動記憶数が1加算されて、第1始動入賞口45に遊技球が入賞したタイミング

で抽出された乱数が第1始動記憶として一つ記憶される。

On the other hand, the first special view variation display game or the second special view variation display game can not be started immediately, for example, the first special view variation display game or the second special view variation display game is already played, and the special view variation display game is performed. If the game ball does not end the game or is in the special game state, and the game ball is won in the first

同様に、この場合に第2始動入賞口をなす普通変動入賞装置36に遊技球が入賞すると

、第2始動記憶数が上限数未満(例えば、4個未満)ならば、第2始動記憶数が1加算さ

れて、第2始動入賞口に遊技球が入賞したタイミングで抽出された乱数が第2始動記憶と

して一つ記憶される。

Similarly, in this case, if the game ball wins in the normal

そして、第1特図変動表示ゲーム又は第2特図変動表示ゲームが開始可能な状態となる

と、第1始動記憶又は第2始動記憶に基づき第1特図変動表示ゲーム又は第2特図変動表

示ゲームが開始される。このとき、第1特図変動表示ゲームと第2特図変動表示ゲームは

同時に実行されることはなく、第2特図変動表示ゲームが第1特図変動表示ゲームよりも

優先して実行されるようになっている。

Then, when the first special view variation display game or the second special view variation display game can be started, the first special view variation display game or the second special view variation display is based on the first start storage or the second start storage. The game is started. At this time, the first special view change display game and the second special view change display game are not simultaneously executed, and the second special view change display game is executed with priority over the first special view change display game. It is supposed to be.

すなわち、第1始動記憶と第2始動記憶がある場合には、第2特図変動表示ゲームが実

行される。

That is, when there is the first start storage and the second start storage, the second special view variation display game is executed.

補助遊技としての第1特図変動表示ゲーム、第2特図変動表示ゲームは、遊技盤10に

設けられた第1特図表示器38、第2特図表示器39で実行されるようになっており、複

数の識別情報を変動表示したのち、所定の結果態様を停止表示することで行われる。また

、表示装置53にて各特図変動表示ゲームに対応して複数種類の識別情報(例えば、数字

、記号、キャラクタ図柄など)を変動表示させる特図変動表示ゲームが実行される。そし

て、この特図変動表示ゲームの結果として、第1特図表示器38又は第2特図表示器39

の表示態様が特別結果態様となった場合には、大当たりとなって特別遊技状態(いわゆる

、大当たり状態)となる。また、これに対応して表示装置53の表示態様も特別結果態様

(例えば、「7,7,7」等のゾロ目数字の何れか)となる。なお、遊技機に第1特図表

示器38、第2特図表示器39を備えずに、表示装置53のみで特図変動表示ゲームを実

行するようにしてもよい。

The first special view variation display game and the second special view variation display game as auxiliary games are to be executed by the first

When the display mode of is a special result mode, it becomes a jackpot and becomes a special gaming state (a so-called jackpot state). In addition, in response to this, the display mode of the

また、本実施形態の遊技機1は、特図変動表示ゲームの結果態様に基づき、遊技状態と

して確変状態(第2確率状態)を発生可能となっている。この確変状態(第2確率状態)

は、特図変動表示ゲームでの当り結果となる確率が、通常確率状態(第1確率状態)に比

べて高い状態である。なお、第1特図変動表示ゲームと第2特図変動表示ゲームのどちら

の特図変動表示ゲームの結果態様に基づき確変状態となっても、第1特図変動表示ゲーム

及び第2特図変動表示ゲームの両方が確変状態となる。また、確変状態と上述した時短動

作状態はそれぞれ独立して発生可能であり、両方を同時に発生することも可能であるし、

一方のみを発生させることも可能である。

In addition, the

Is a state in which the probability of being a hit result in the special figure variation display game is higher than that in the normal probability state (first probability state). Note that the first special view fluctuation display game and the second special view fluctuation even if it becomes a definite change state based on the result form of the special view fluctuation display game of the first special view fluctuation display game and the second special view fluctuation display game Both display games are in a state of probability variation. Also, the probability variation state and the above-mentioned short time operation state can be generated independently of each other, and both can be generated simultaneously,

It is also possible to generate only one.

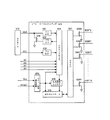

図3は、本発明の第1実施形態の遊技機1の構成を示すブロック図である。

FIG. 3 is a block diagram showing the configuration of the

遊技機1は、遊技を統括的に制御する遊技制御装置500、各種演出を行うために表示

装置53及びスピーカ30等を制御する演出制御装置550、遊技球を払い出すために図

示しない払出モータを制御する払出制御装置580を備える。

The

まず、遊技制御装置500について説明する。図4では、演出制御装置550について

説明する。

First, the

遊技制御装置500は、遊技用マイコン501、入力I/F(Interface)5

05、出力I/F(Interface)506、及び外部通信端子507を備える。

The

05, an output I / F (Interface) 506, and an

遊技用マイコン501は、CPU502、ROM(Read Only Memory

)503及びRAM(Random Access Memory)504を備える。

The

And a random access memory (RAM) 504.

CPU502は、遊技を統括的に制御する主制御装置であって、遊技制御を司る。RO

M503は、遊技制御のための不変の情報(プログラム、データ等)を記憶している。R

AM504は、遊技制御時にワークエリアとして利用される。

The CPU 502 is a main control device that controls the game in an integrated manner, and controls the game control. RO

外部通信端子507は、遊技制御装置500の設定情報等を検査する検査装置等の外部

機器に遊技制御装置500を接続する。

The

CPU502は、入力I/F505を介して各種入力装置(第1始動口SW45a、第

2始動口SW36d、一般入賞口SW44a、ゲートSW34a、カウントSW42d、

ガラス枠開放SW18a、前面枠開放SW3a、球切れSW54、振動センサ55、及び

磁気センサ56)からの検出信号を受けて、大当り抽選等、種々の処理を行う。

The CPU 502 can input various input devices (a first

In response to detection signals from the glass

第1始動口SW45aは、第1始動入賞口45に遊技球が入賞したことを検出するスイ

ッチである。第2始動口SW36dは、普通変動入賞装置36の第2始動入賞口に遊技球

が入賞したことを検出するスイッチである。

The first

一般入賞口SWa44a〜44nは、一般入賞口44に遊技球が入賞したことを検出す

るスイッチである。ゲートSW34aは、普図始動ゲート34を遊技球が通過したことを

検出するスイッチである。

The general winning

カウントSW42dは、特別変動入賞装置42の大入賞口に遊技球が入賞したことを検

出するスイッチである。

The

ガラス枠開放SW18aは、ガラス枠18が開放されたことを検出するスイッチである

。前面枠開放SW3aは、前面枠3が開放されたことを検出するスイッチである。

The glass

球切れSW54は、遊技機1の内部に貯留され、払い出しに用いられる遊技球の数が所

定数以下になったことを検出するスイッチである。

The out-of-

振動センサ55は、遊技機1に与えられた振動を検出するセンサであり、遊技機1に振

動を与えて、不当に遊技球を獲得する不正を検出する。磁気センサ56は、第1始動入賞

口45、普通変動入賞装置36の第2始動入賞口、一般入賞口44、特別変動入賞装置4

2の大入賞口、及び普図始動ゲート34付近に設けられ、磁力を検出するセンサである。

磁気センサ93は、各入賞口付近に磁石を近づけて、遊技領域10aに発射された遊技球

を各入賞口に導く不正を検出する。

The

A sensor for detecting the magnetic force is provided near the winning

The magnetic sensor 93 brings a magnet close to each winning opening, and detects an injustice leading the gaming balls fired to the

また、CPU502は、出力I/F506を介して、第1特図表示器38、第1特図記

憶表示器48、第2特図表示器39、第2特図記憶表示器49、普図表示器35、普電S

OL36b、大入賞口SOL42b、払出制御装置580、及び演出制御装置550に指

令信号を送信して、遊技を統括的に制御する。

In addition, the CPU 502, through the output I /

A command signal is transmitted to the

第1特図表示器38には、第1始動入賞口45に遊技球が入賞した場合に補助遊技とし

て実行される第1特図変動表示ゲームが表示される。第1特図記憶表示器48には、所定

の上限数の範囲内で記憶される第1特図変動表示ゲームを開始する始動権利である第1始

動記憶数が表示される。

On the first

第2特図表示器39には、普通変動入賞装置36の大入賞口に遊技球が入賞した場合に

補助遊技として実行される第2特図変動表示ゲームが表示される。第2特図記憶表示器4

9には、所定の上限数の範囲内で記憶される第2特図変動表示ゲームを開始する始動権利

である第2始動記憶数が表示される。

On the second

A second start memory number, which is a start right to start a second special view variation display game stored within a predetermined upper limit number, is displayed on the 9.

普図表示器35には、遊技球が普図始動ゲート34を通過した場合に行われる普図変動

表示ゲームが表示される。

The

普電SOL36bは、普図表示器35で実行される普図変動表示ゲームの停止表示が特

別の結果態様となった場合に、開閉部材36a、36aを開放し、普通変動入賞装置36

の第2始動入賞口を遊技球が入賞しやすい状態にする。

When the stop display of the common drawing fluctuation display game executed by the

The game ball makes it easy to win the second start winning opening of the game.

大入賞口SOL42bは、第1特図変動表示ゲーム又は第2特図変動表示ゲームの結果

が特別の結果態様となり、特別遊技状態となった場合に、特別変動入賞装置42の開閉扉

42aを開放して、大入賞口を遊技球が入賞しやすい状態に変換する。

In the special winning opening SOL42b, when the result of the first special view variation display game or the second special view variation display game becomes a special result mode, and the special game state is obtained, the open /

また、遊技制御装置500は、遊技機データを、外部情報端子508を介して、図示し

ない情報収集端末装置を介して、図示しない遊技場管理装置に出力する。遊技場管理装置

は、遊技場に設置された遊技機1の遊技データを収集管理する計算機である。

Further, the

また、払出制御装置580は、遊技球が一般入賞口44又は大入賞口に入賞した場合に

、入賞した入賞口に対応する数の遊技球の払い出し、又は球貸ボタン26が操作された場

合に、所定数の遊技球の払い出しを行う払出指令を遊技制御装置500から受信した場合

に、受信した払出指令に基づいて、図示しない払出モータを制御する。なお、払出指令に

は、払い出す遊技球の数が含まれる。

Further, the

遊技制御装置500は、変動開始コマンド、客待ちデモコマンド、ファンファーレコマ

ンド、確率情報コマンド、及びエラー指定コマンド等を、遊技の状況を示す遊技データと

して、出力I/F506を介して、演出制御装置550へ送信する。

The

図4は、本発明の第1の実施形態の演出制御装置550の構成を示すブロック図である

。

FIG. 4 is a block diagram showing the configuration of the

演出制御装置550は、遊技制御装置500から入力される遊技データ(表示制御指令

)に基づいて、演出内容を決定して、表示装置53、及びスピーカ30を制御するととも

に、装飾制御装置610を介して装飾装置620、役物駆動SOL560(ソレノイド)

、及び役物駆動MOT(モータ)561を制御する。詳細は後述するが、これら装飾装置

620、役物駆動SOL560、及び役物駆動MOT561(総称して演出装置という)

によって、遊技の演出が行われる。また、演出制御装置550は、演出ボタン17から当

該演出ボタン17が操作されたことを示す信号が入力される。

The

, And controls the accessory drive MOT (motor) 561. Although the details will be described later, the

An effect of the game is performed. Further, the

演出制御装置550は、CPU551、制御ROM552、RAM553、画像ROM

554、音ROM555、VDP556、音LSI557、入出力I/F558、電源投

入検出回路559、マスタIC570、及びNORゲート回路590を備える。

The

A

CPU551は、遊技制御装置500に接続され、遊技制御装置500から指令信号が

割込信号(INT)として入力され、入力された指令信号に基づいて、各種演出を制御す

る主制御装置である。また、CPU551には、マスタIC570の後述するコントロー

ラから割込信号が入力されるとともに、VDP556から割込信号が入力される。

The

なお、CPU551に割込信号が入力されると、CPU551は、現在実行中の処理を

中断して、入力された割込信号に対応する処理を実行する。

When an interrupt signal is input to the

制御ROM552には、演出制御のための不変の情報(プログラム、データ等)が格納

されている。RAM553は、演出制御時にワークエリアとして利用される。

The

画像ROM554には、表示装置53に表示される画像データが格納され、画像ROM

554はVDP556に接続されている。音ROM555には、スピーカ30から出力さ

れる音データが格納され、音ROM555は音LSI557に接続されている。

The image ROM 554 stores image data to be displayed on the

554 is connected to the

VDP556は、表示装置53への画像出力を制御するプロセッサである。音LSI5

57は、スピーカ30からの音声出力を制御する回路である。

The

Reference numeral 57 denotes a circuit for controlling an audio output from the

なお、VDP556は、表示装置53に表示される画像を更新する周期(33ms周期

)と同期する同期信号を発生させる同期信号発生手段を備える。同期信号発生手段は、同

期信号を発生させるごとに、発生させた同期信号をCPU551に割込信号として入力す

る。

The

入出力I/F558は、演出ボタン17、モータ位置検出センサ510、及びNORゲ

ート回路590に接続されるインタフェースであり、演出ボタン17からの操作信号、及

びモータ位置検出センサ510からのモータ位置検出信号をCPU551へ伝達するとと

もに、CPU551からのリセット信号をNORゲート回路590へ伝達する。

The input / output I /

なお、演出ボタン17は、上皿21の上縁部に設けられ、表示装置53で実行される第

1特図変動表示ゲーム又は第2特図変動表示ゲームにおける演出で、遊技者によって操作

される。

The

また、モータ位置検出センサ510は、役物駆動MOT561の回転軸が初期位置まで

回転したことを検出した場合に、モータ位置検出信号を出力するセンサである。

The motor

なお、NORゲート回路590は、マスタIC570のコントローラに備わるRESE

T端子、及び初期化を必要とする他の回路に接続される。初期化を必要とする他の回路と

は、例えば、VDP556や音LSI557などである。これらは、演出制御装置550

に電源が投入されて起動したときに、CPU551により初期化されるものである。

NOR

It is connected to the T terminal and other circuits that require initialization. The other circuits requiring initialization are, for example, the

When the power is turned on to start up, the

CPU551、VDP556、RAM553、制御ROM552、音LSI557、及

び入出力I/F558はバス563を介してそれぞれ接続されている。

The

電源投入検出回路559は、演出制御装置550に電源が投入された場合に、マスタI

C570の図示しないレジスタをデフォルト状態(すべて0)に初期化するリセット信号

を発生させ、発生させたリセット信号をNORゲート回路590へ出力する。

The power on

A reset signal for initializing a register (not shown) of

また、CPU551は、所定の条件が成立した場合に、リセット信号をバス563を介

して入出力I/F558に出力し、入出力I/F558は入力されたリセット信号をNO

Rゲート回路590へ出力する。

Further, when a predetermined condition is satisfied, the

なお、電源投入検出回路559からNORゲート回路590へ入力されるリセット信号

、及びCPU551から入出力I/F558を介してNORゲート回路590へ入力され

るリセット信号は、いずれの場合にもロウレベルの状態である場合にリセットを指令する

信号として機能する。そのため、電源投入検出回路559及びCPU551の少なくとも

一方からNORゲート回路590にリセット信号が出力されていれば、NORゲート回路

590を介してリセット信号がマスタIC570に入力される。

The reset signal input from the power on

上述したように、NORゲート回路590は、マスタIC570及び初期化を必要とす

る他の回路に接続されるため、NORゲート回路590にリセットが入力されると、マス

タIC570及び当該NORゲート回路590に接続される初期化を必要とする他の回路

が初期化される。

As described above, since the NOR

なお、初期化を必要とする他の回路がない場合には、NORゲート回路590は、マス

タIC570にのみ接続される。

If there is no other circuit requiring initialization, NOR

次に、マスタIC570について説明する。

Next,

マスタIC570は、制御対象となる演出装置の装飾制御装置610のアドレスを指定

して、指定したアドレスの装飾制御装置610に演出装置の制御内容を出力する。

The

マスタIC570は、接続線Vcc、接続線Vact、接続線SDA、接続線SCL、

及び接続線GND(図5参照)の5本の接続線を介して、中継基板(装飾制御装置)60

0に接続される。

And the relay substrate (decorative control device) 60 via five connection lines of the connection line GND (see FIG. 5).

Connected to 0.

接続線Vccは、中継基板600及び装飾制御装置610に、ロジック用の電源を供給

するための接続線である。接続線Vactは、演出装置を駆動させるための電源(例えば

、LEDを発光させるための電源)を供給するための接続線である。接続線SDAは、演

出制御装置550と装飾制御装置610との間でデータを通信するための接続線であり、

本実施形態におけるデータ線として機能する。接続線SCLは、接続線SDAでのデータ

通信に用いられるクロック信号を入出力するための接続線であり、本実施形態におけるタ

イミング信号線として機能する。図5に示す接続線GNDは、接続線Vcc及び接続線V

actで供給される電源のグランドである。

The connection line Vcc is a connection line for supplying a power supply for logic to the

It functions as a data line in the present embodiment. The connection line SCL is a connection line for inputting and outputting a clock signal used for data communication in the connection line SDA, and functions as a timing signal line in the present embodiment. Connection line GND shown in FIG. 5 is formed of connection line Vcc and connection line V.

It is the ground of the power supplied by act.

中継基板600と装飾制御装置610との間は、マスタIC570と中継基板600と

の間と同じく、接続線Vcc、接続線Vact、接続線SDA、接続線SCL、及び接続

線GNDを介して接続される。

Similar to the connection between the

マスタIC570と装飾制御装置610とは、接続線SDA及び接続SCLによって2

ライン双方向通信を行う。

Perform line bi-directional communication.

マスタIC570は、中継基板600及び装飾制御装置610にデータを送信する場合

には、まず、接続線SCLの信号レベルをHIGHに維持したまま、接続線SDAの信号

レベルをHIGHからLOWに変化させることにより、装飾制御装置610へのデータ出

力を開始するためのスタート条件を成立させる(装飾制御装置610に対してスタートコ

ンディションを発行する)。

When transmitting data to relay

この後、マスタIC570は、接続線SCLの信号レベルをLOWに変更し、接続線S

CLの信号レベルがLOWである間に接続線SDAの信号レベルを送信データの最初のビ

ットのレベルに設定し、所定時間後に接続線SCLの信号レベルをLOWからHIGHに

変化させる。接続線SCLの信号レベルがHIGHに変化すると、装飾制御装置610は

接続線SDAの信号レベルを取り込んで、送信データの最初のビットとして認識する。次

いで、マスタIC570は、接続線SCLの信号レベルをHIGHからLOWに戻す。

After this,

While the signal level of CL is LOW, the signal level of the connection line SDA is set to the level of the first bit of the transmission data, and after a predetermined time, the signal level of the connection line SCL changes from LOW to HIGH. When the signal level of the connection line SCL changes to HIGH, the

この手順を1回実行すると、マスタIC570から装飾制御装置610へ1ビットのデ

ータが送信され、最終的にはこの手順が8回繰り返されることで、送信データの単位ビッ

トである8ビット全てがマスタIC570から装飾制御装置610へ送信される(1バイ

ト分のデータが送信される)。

When this procedure is executed once, one bit of data is transmitted from the

そして、マスタIC570は、最後の8ビット目のデータを送信し終えて、接続線SC

Lの信号レベルをHIGHからLOWに戻した際に、接続線SDAを解放して装飾制御装

置610からの返答信号を受信することを待機する受信待機状態にする。

Then,

When the signal level of L is returned from HIGH to LOW, the connection line SDA is released to be in a reception standby state to wait to receive a response signal from the

受信待機状態になると、装飾制御装置610は、接続線SDAを介して1ビットの返答

信号(後述するACK又はNACK)をマスタIC570に返す。次いで、マスタIC5

70は、接続線SCLの信号レベルをLOWからHIGHに変化させて返答信号のレベル

を取り込み、所定時間後に接続線SCLの信号レベルをHIGHからLOWに変化させる

と、装飾制御装置610は接続線SDAを解放する。

When in the reception standby state, the

70 changes the signal level of the connection line SCL from LOW to HIGH to capture the level of the response signal, and changes the signal level of the connection line SCL from HIGH to LOW after a predetermined time, the

マスタIC570は、このような1バイト分のデータ送信と1ビット分の返答信号の受

信とを交互に繰り返し、装飾制御装置610へ出力すべきデータがすべて出力されるまで

継続する。マスタIC570は、出力すべきデータの出力が終了した場合には、接続線S

CLの信号レベルをHIGHに維持したまま、接続線SDAの信号レベルをLOWからH

IGHに変更させることにより、装飾制御装置610へのデータ出力を終了するためのス

トップ条件を成立させる(装飾制御装置610に対してストップコンディションを発行す

る)。

The signal level of the connection line SDA is changed from LOW to H while keeping the signal level of CL HIGH.

By changing to IGH, a stop condition for ending data output to the

入力用BUF571は、装飾制御装置610から接続線SDAを介して入力されたデー

タが一時的に記憶される記憶装置である。

The

具体的には、マスタIC570が入力モードに設定された場合において、装飾制御装置

610からマスタIC570に送信されたデータが、フィルタ575Aによりノイズが除

去されて入力用BUF571に一時的に記憶される。

Specifically, when the

出力用BUF572は、装飾制御装置610に接続線SDAを介して出力するデータが

一時的に記憶される。

The

リセットREG573は、本実施形態の初期化指示データ記憶領域として機能するもの

で、バス563に接続され、CPU551からの指令を受けてリセット信号をコントロー

ラに出力する。コントローラは、マスタIC570を統括的に制御し、各種処理を実行す

る。

The

送信モードREG574は、I2CI/Oエクスパンダ615へデータを送信するモー

ドを、バイトモード又はバッファモードにするかを選択するためのレジスタである。

The

バイトモードは、マスタIC570が、I2CI/Oエクスパンダ615へデータを1

バイト送信する毎に、I2CI/Oエクスパンダ615からACK又はNACKを受信し

、ACK及びNACKの何れを受信した場合でも、マスタIC570からCPU551に

割込信号を出力するモードである。

In byte mode, the

In this mode, an ACK or NACK is received from the I 2 CI /

バッファモードは、マスタIC570が、出力用BUF572に格納された複数バイト

のデータを、I2CI/Oエクスパンダ615へ1バイト毎送信し、その送信の都度、I2

CI/Oエクスパンダ615からACK又はNACKを受信するととともに、NACKを

受信した場合には、その時点で、割込信号をCPU551に出力するモードである。

In the buffer mode, the

In addition to receiving an ACK or NACK from the CI /

但し、バッファモードでは、ACKを受信した場合には、出力用BUF572に格納さ

れたすべてのデータが送信完了となった場合にのみ、割込信号をCPU551に出力し、

マスタIC570は、出力用BUF572に未送信のデータが残っている状態でI2CI

/Oエクスパンダ615からACKを受信したときには、割込信号をCPU551に出力

せずに、出力用BUF572から次の送信すべきデータを取り出して、I2CI/Oエク

スパンダ615へ出力する制御が繰り返される。

However, in the buffer mode, when ACK is received, an interrupt signal is output to the

When an ACK is received from the /

なお、バイトモードは、マスタIC570が、後述する初期化指示データ及び可動制御

データをI2CI/Oエクスパンダ615へ出力する場合に用いられる。バッファモード

は、マスタIC570が、後述する発光制御データをI2CI/Oエクスパンダ615へ

出力する場合に用いられる。

The byte mode is used when the

ステータスREG579は、マスタIC570がI2CI/Oエクスパンダ615から

受信した返答信号が、ACKであったのかNACKであったのかを識別するレジスタであ

る。マスタIC570は、CPU551に割込信号を出力する際に、I2CI/Oエクス

パンダ615から受信した返答信号に対応して、ステータスREG579の値を設定する

。

The

フィルタ575Aは、接続線SDAから入力されたデータのノイズを除去する。ドライ

バ576Aは、接続線SDAからデータを出力する場合に、トランジスタ578Aが動作

可能な電圧をトランジスタ578Aに印加する。

The

図9に示すように接続線SDAには、プルアップ抵抗Rによって所定の電圧が印加され

て、接続線SDAはフィルタ575A及びトランジスタ578Aに接続されている。

As shown in FIG. 9, a predetermined voltage is applied to the connection line SDA by the pull-up resistor R, and the connection line SDA is connected to the

トランジスタ578Aは、電力消費を抑えるために電界効果トランジスタ(FET)が

用いられており、トランジスタ578Aのゲートはドライバ576Aに接続され、ドレイ

ンはプルアップ抵抗Rにより所定の電圧が印加された接続線SDAに接続され、ソースは

接地されている。

トランジスタ578Aのゲートに印加される電圧がトランジスタ578Aを動作させる

所定値よりも小さければ、ドレインとソースとの間に電流が流れないので、接続線SDA

に印加された電圧は降下せず、その結果、接続線SDAはHIGHレベルとなる。一方、

トランジスタ578Aのゲートに印加される電圧がトランジスタ578Aを動作させる所

定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流

が流れることによって、接続線SDAの電圧が低下し、その結果、接続線SDAはLOW

レベルとなる。

If the voltage applied to the gate of

The applied voltage does not drop, and as a result, the connection line SDA goes high. on the other hand,

If the voltage applied to the gate of the

It becomes a level.

なお、トランジスタ578Aは、10ミリアンペア程度の電流をドレインからソースへ

流しても破損しない仕様のものを用いている。このため、接続線SDAには、通常のI2

Cバス使用で用いられる電流値よりもはるかに大きい10ミリアンペア程度の電流を流す

ことが可能であり、演出制御装置550と装飾制御装置610との間のデータ送信が、ノ

イズによる障害に耐えうる構成となっている。

Note that the

A current of about 10 milliamperes which is much larger than the current value used in the C bus use can be supplied, and data transmission between the

ドライバ576Aは、データを接続線SDAから出力する場合に、トランジスタ578

Aにドレインとソースとの間に電流を流すためにトランジスタ578Aのゲートにトラン

ジスタ578Aが動作可能な値の電圧を印加する。そして、ドライバ576Aは、接続線

SDAの電圧を、HIGHレベル又はLOWレベルに設定することによって、データを接

続線SDAから出力する。

When

In order to cause current to flow between the drain and the source in A, a voltage with an operable value of the

また、フィルタ575Bは、接続線SCLから入力されたデータのノイズを除去する。

ドライバ576Bは、接続線SCLからデータを出力する場合に、トランジスタ578B

が動作可能な電圧をトランジスタ578Bに印加する。

In addition, the

When

Apply an operable voltage to the

図9に示すように接続線SCLは、プルアップ抵抗Rによって所定の電圧が印加されて

、接続線SDAはフィルタ575B及びトランジスタ578Bに接続されている。

As shown in FIG. 9, a predetermined voltage is applied to the connection line SCL by the pull-up resistor R, and the connection line SDA is connected to the

トランジスタ578Bは、電力消費を抑えるために電界効果トランジスタ(FET)が

用いられており、トランジスタ578Bのゲートはドライバ576Bに接続され、ドレイ

ンはプルアップ抵抗Rにより所定の電圧が印加された接続線SCLに接続され、ソースは

接地されている。

The

トランジスタ578Bのゲートに印加される電圧がトランジスタ578Bを動作させる

所定値よりも小さければ、ドレインとソースとの間に電流が流れないので、接続線SCL

に印加された電圧は降下せず、その結果、接続線SCLはHIGHレベルとなる。一方、

トランジスタ578Bのゲートに印加される電圧がトランジスタ578Bを動作させる所

定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流

が流れることによって、接続線SCLの電圧が低下し、その結果、接続線SCLはLOW

レベルとなる。

If the voltage applied to the gate of

The applied voltage does not drop, as a result, the connection line SCL goes high. on the other hand,

If the voltage applied to the gate of the

It becomes a level.

なお、トランジスタ578Bは、10ミリアンペア程度の電流をドレインからソースへ

流しても破損しない仕様のものを用いている。そのため、接続線SCLには、通常のI2

Cバス使用で用いられる電流値よりもはるかに大きい10ミリアンペア程度の電流を流す

ことが可能であり、演出制御装置550と装飾制御装置610との間のデータ送信が、ノ

イズによる障害に耐えうる構成となっている。

Note that the

A current of about 10 milliamperes which is much larger than the current value used in the C bus use can be supplied, and data transmission between the

ドライバ576Bは、クロック信号を接続線SCLから出力する場合に、トランジスタ

578Bにドレインとソースとの間に電流を流すためにトランジスタ578Bのゲートに

トランジスタ578Bが動作可能な値の電圧を印加する。そして、ドライバ576Bは、

接続線SCLの電圧を、HIGHレベルとLOWレベルとに繰り返し変化させることによ

って、クロック信号を接続線SCLから出力する。

When the

A clock signal is output from the connection line SCL by repeatedly changing the voltage of the connection line SCL between the high level and the low level.

電源投入リセット回路577は、マスタIC570に電源が投入されて、電源投入リセ

ット回路577内の電圧が所定値に達した場合に、入力用BUF571及び出力用BUF

572などの記憶領域をデフォルト状態にするためのリセット信号をコントローラに出力

する。

When the

A reset signal for setting a storage area such as 572 to a default state is output to the controller.

次に、中継基板600及び装飾制御装置610について説明する。

Next, the

なお、中継基板600は、装飾制御装置610のうちマスタIC570に直接接続され

る、つまり最も上流側に位置するものである。

The

装飾装置620は、装飾制御装置610に設けたI2CI/Oエクスパンダ615(図

6で後述)によって制御され、電流を流すことによって光が点滅して演出を行う発光装置

であり、例えばLEDなどで構成される。役物駆動ソレノイド(SOL)560は、電流

が流れると往復動作する装置であり、遊技盤10に配置される図示しない装飾のための役

物を可動させて演出を行う。役物駆動モータ(MOT)561は、電流が流れると回転動

作する装置であり、可動役物60を可動させて演出を行う。役物駆動ソレノイド(SOL

)560及び役物駆動モータ(MOT)561も、装飾制御装置610に設けたI2CI

/Oエクスパンダ615によって制御される。

The

) 560 and the character drive motor (MOT) 561 are also provided in the

/

なお、役物駆動SOL560が可動役物60を可動させてもよいし、役物駆動MOT5

61が図示しない役物を可動させてもよい。

In addition, the

61 may move an unillustrated accessory.

演出制御装置550と中継基板600との接続方法、及び中継基板600と中継基板6

00以外の装飾制御装置610との接続方法は、図5で詳細を説明する。装飾制御装置6

10は、図6〜図10で詳細を説明する。

A method of connecting the

The connection method with the

10 will be described in detail with reference to FIGS.

図5は、本発明の第1の実施形態の装飾制御装置610A〜610Fの接続の説明図で

ある。なお、説明の都合上、装飾制御装置610として、1個の中継基板600と、6個

の装飾制御装置610A〜610Fを図示しているが、実際には、遊技機の仕様に対応し

て必要な数の装飾制御装置610が接続されている。

FIG. 5 is an explanatory diagram of connection of the

演出制御装置550は、接続線Vcc、接続線Vact、接続線SDA、接続線SCL

、及び接続線GND(以下、この5本の接続線を一つのハーネスという)を介して演出制

御装置550と接続される。

The

And the connection line GND (hereinafter, these five connection lines are referred to as one harness) and are connected to the

中継基板600には、二つの装飾制御装置610A及び610Dがそれぞれハーネスに

よって並列に接続される。

Two

装飾制御装置610Aにはハーネスを介して装飾制御装置610Bが接続され、装飾制

御装置610Bにはハーネスを介して装飾制御装置610Cが接続される。

A

一方、装飾制御装置610Dにはハーネスを介して装飾制御装置610Eが接続され、

装飾制御装置610Eにはハーネスを介して装飾制御装置610Fが接続される。

On the other hand, the

A

各装飾制御装置610は、ハーネスを自身に接続するための取付口となるコネクタを備

える。このコネクタは各装飾制御装置610で共通であるので、接続線を接続順の誤配線

を防止できる。

Each

ここで、装飾制御装置610に設けたI2CI/Oエクスパンダ615(図6で後述)

が装飾装置620を制御する方法について説明する。

Here, the I 2 CI / O expander 615 (described later in FIG. 6) provided in the

The method of controlling the

演出制御装置550は、遊技制御装置500から入力された遊技データに基づいて、演

出装置の出力態様を決定する。そして、演出制御装置550は、決定された出力態様とな

るように、制御対象となる装飾制御装置610の個別アドレス(I2CI/Oエクスパン

ダ615の個別アドレス)を含む演出制御データ(演出制御情報)を中継基板600に出

力する。このとき、演出制御データは、中継基板600を介して演出制御装置550に接

続されるすべての装飾制御装置610に対して接続線SDAから出力される。このため、

マスタIC570は、マスタIC570に接続されるすべての装飾制御装置610を制御

可能である。

Based on the game data input from

The

なお、本実施形態では演出装置としてLED等の発光装置を例示しているので、LED

の発光態様が演出装置の出力態様に相当する。この場合、演出制御データによって、LE

Dの点灯/点滅/消灯が指示され、同時に、LEDの点滅周期や点灯輝度も指示される。

In the present embodiment, a light emitting device such as an LED is illustrated as a rendering device, so the LED

The light emission aspect of corresponds to the output aspect of the effect device. In this case, the effect control data causes LE to

The lighting / blinking / lighting out of D is instructed, and at the same time, the blinking cycle of the LED and the lighting luminance are also instructed.

各装飾制御装置610には、一意な個別アドレスが予め設定されているので、演出制御

データが入力されると、入力された演出制御データに含まれるアドレスと設定されている

個別アドレスとが一致するか否かを判定する。そして、入力された演出制御データに含ま

れるアドレスと設定されている個別アドレスとが一致すると判定された場合には、装飾制

御装置610のI2CI/Oエクスパンダ615は、演出制御データを取り込んで、対応

する装飾装置620の出力態様を制御するとともに、8ビット目のデータが入力された直

後に返答信号をマスタIC570に出力する。

Since unique individual addresses are set in advance in each

なお、各装飾制御装置610には、個別アドレス以外にも、装飾制御装置610のI2

CI/Oエクスパンダ615を初期化するためのリセット用アドレスが設定されている。

このリセットアドレスは、すべてのI2CI/Oエクスパンダ615に対して共通に設け

られたアドレスであり、個別アドレスとして使用することは不可能となっている。また、

このリセットアドレスの値を変更することもできないようになっている(詳細は後述する

)。

In addition, in each

A reset address for initializing the CI /

This reset address is an address commonly provided to all the I 2 CI /

The value of this reset address can not be changed (the details will be described later).

演出制御装置550は、装飾制御装置610(正確には、装飾制御装置610のI2C

I/Oエクスパンダ615)を初期化する場合に、このリセット用の共通アドレスを含ん

だ初期化指示データを、中継基板600に出力する。このとき、初期化指示データ演出制

御データは、中継基板600を介して、演出制御装置550に接続されるすべての装飾制

御装置610に対して接続線SDAから出力される。

The

When the I / O expander 615) is initialized, initialization instruction data including the common address for this reset is output to the

各装飾制御装置610には、リセット用の共通アドレスが予め設定されているので、入

力されたデータに含まれるアドレスと、予め設定されているリセット用の共通アドレスと

が一致するか否かを判定する。入力されたデータに含まれるアドレスと、予め設定されて

いるリセット用の共通アドレスとが一致すると判定された場合には、装飾制御装置610

のI2CI/Oエクスパンダ615は、返答信号をマスタIC570に出力するとともに

、入力されたデータを初期化指示データとして取り込み、I2CI/Oエクスパンダ61

5自身を初期化する。

Since a reset common address is preset in each

The I 2 CI /

5 Initialize itself.

なお、I2CI/Oエクスパンダ615が初期化されると、当該初期化されたI2CI/

Oエクスパンダ615によって制御される演出装置はオフ状態となる。

Incidentally, the I 2 CI /

The rendering device controlled by the

このように、装飾制御装置610は、演出制御装置550からの指令に基づく制御を行

うので、演出制御装置550と装飾制御装置610との関係は、演出制御装置550のマ

スタIC570がマスタであり、装飾制御装置610のI2CI/Oエクスパンダ615

がスレーブである。

Thus, since the

Is the slave.

図5では、装飾制御装置610の制御対象が装飾装置620である場合について説明し

たが、装飾制御装置610の制御対象が役物駆動SOL560や役物駆動MOT561で

あってもよい。この場合、演出装置がモータやソレノイドなどの駆動源となることから、

これらの駆動源の動作態様が、演出装置の出力態様に相当することになる。この場合、演

出制御データによって、駆動源の作動/停止が指示され、同時に動作速度も指示される。

Although FIG. 5 describes the case where the control target of the

The operation mode of these drive sources corresponds to the output mode of the rendering device. In this case, the effect control data instructs the operation / stop of the drive source and at the same time the operation speed.

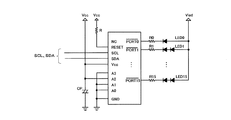

図6は、本発明の第1の実施形態の装飾制御装置610のブロック図である。

FIG. 6 is a block diagram of the

図6では、装飾制御装置610の内部に装飾装置620であるLEDを備える装飾制御

装置610(図6の下側の装飾制御装置610)と、外部の装飾装置620に接続される

装飾制御装置610(図6の中央の装飾制御装置610)と、について説明する。

In FIG. 6, the decoration control device 610 (the

まず、装飾制御装置610の内部にLEDを備える装飾制御装置610について説明す

る。

First, the

図6の下側の装飾制御装置610は、I2CI/Oエクスパンダ615及びLED(装

飾装置20)を備える。接続線SDA及び接続線SCLは、装飾制御装置610内で二つ

に分岐し、一方は、そのまま次の装飾制御装置610に出力される。他方は、I2CI/

Oエクスパンダ615に接続される。

The

また、I2CI/Oエクスパンダ615の出力側には、制御対象となる装飾装置620

が接続される。I2CI/Oエクスパンダ615の出力側は、図7で説明するポート0〜

15によって構成される。さらに、装飾制御装置610のすべてのポートが、図8Aで後

述する電流制限抵抗R0〜R15を介して、内部のLEDに接続されている。なお、この

電流制限抵抗R0〜R15も、装飾制御装置610に備えられている。

In addition, on the output side of the I 2 CI /

Is connected. The output side of the I 2 CI /

It is comprised by 15. Furthermore, all ports of the

前述したように、I2CI/Oエクスパンダ615は、演出制御装置550から入力さ

れた演出制御データに含まれるアドレスと、当該I2CI/Oエクスパンダ615に設定

されている個別アドレスとが一致する場合にのみ、演出制御データに含まれる装飾データ

に基づいて、I2CI/Oエクスパンダ615に接続されている装飾装置620を制御す

る。

As described above, the I 2 CI /

なお、図中の電源Vledは、図5で前述した接続線Vactにより供給される電源(

LEDを発光させるための電源)に相当するものである。

Note that the power supply Vled in the figure is a power supply supplied by the connection line Vact described above with reference to FIG.

It corresponds to the power supply for making LED light-emit).

次に、外部の装飾装置620に接続される装飾制御装置610について説明する。

Next, the

図6の中央の装飾制御装置610は、I2CI/Oエクスパンダ615及びLED(装

飾装置20)を備え、装飾制御装置610の外部に接続される装飾装置基板625に備わ

るLEDに電流を流すための接続線、装飾装置基板625のLEDに電源電圧Vledを

供給する接続線、及び、グランドに接地する接続線を介して、装飾制御装置610と装飾

装置基板625とが接続される。

The

装飾装置基板625は、I2CI/Oエクスパンダ615を備えておらず、LEDのみ

を備えた基板である。この場合、装飾装置基板625に備えたLEDに接続される電流制

限抵抗(図8A)を、装飾装置基板625に設けることになるが、I2CI/Oエクスパ

ンダ615が備えられた装飾制御装置610に設けてもよい。

The

なお、装飾装置基板625に設けたLEDの数に対応して、装飾制御装置610から装

飾装置基板625へ渡されることになる、これらのLEDに電流を流すための接続線の数

が決定される。例えば、装飾装置基板625に二つのLEDを備えた場合には、I2CI

/Oエクスパンダ615のポートと対応するLEDとを接続するための2本の制御線と、

Vledを供給する電源線が1本とが、少なくとも必要となる。

It should be noted that the number of connection lines for causing current to flow to the

Two control lines for connecting the port of the /

At least one power supply line for supplying Vled is required.

そして、中央の装飾制御装置610に設けられたI2CI/Oエクスパンダ615も、

演出制御装置550から入力された演出制御データに含まれるアドレスと、当該I2CI

/Oエクスパンダ615に設定されている個別アドレスとが一致する場合にのみ、演出制

御データに含まれる装飾データに基づいて、I2CI/Oエクスパンダ615に接続され

ている装飾装置620を制御する。この場合、中央の装飾制御装置610に設けられた装

飾装置620と、装飾装置基板625に設けられた装飾装置620の両方が、I2CI/

Oエクスパンダ615によって制御される。

And, the I 2 CI /

An address included in the effect control data input from the

Controls the

It is controlled by

このように、装飾装置基板625を設けて、装飾制御装置610から一部の装飾装置(

LED)を分離させることで、離れた箇所に配置されたLEDであっても、共通のI2C

I/Oエクスパンダ615により制御することができる。

Thus, the

Even if the LEDs are placed at a distant place by separating the LEDs), the common I 2 C

It can be controlled by the I /

なお、装飾制御装置610は、装飾装置620の代わりに、役物駆動SOL560や役

物駆動MOT561を接続し、これらを制御してもよいが、詳細は、図8Bで後述する。

Note that the

図7は、本発明の第1の実施形態のI2CI/Oエクスパンダ615のブロック図であ

る。

FIG. 7 is a block diagram of the I 2 CI /

I2CI/Oエクスパンダ615は、接続線SDAに接続されるトランジスタ630、

接続線SDAに接続されるフィルタ631、接続線SDAに接続されるドライバ632、

接続線SCLに接続されるフィルタ633、バスコントローラ634、出力設定レジスタ

635、出力コントローラ636、I2CI/Oエクスパンダ615の出力側の各ポート

0〜15に接続されるドライバ637、各ポート0〜15に接続されるトランジスタ63

8A〜638P、及びリセット信号発生回路639を備える。

The I 2 CI /

A

8A to 638P and a reset

フィルタ631は、接続線SDAに接続され、接続線SDAから入力されたデータのノ

イズを除去し、ノイズが除去されたデータをバスコントローラ634に出力する。ドライ

バ632は、返答信号を接続線SDAから出力する場合に、トランジスタ630が動作可

能な電圧をトランジスタ630に印加する。

The

ドライバ632は、接続線SDAからデータ(返答信号)を出力する場合に、トランジ

スタ630が動作可能な電圧をトランジスタ630に印加する。

When the

トランジスタ630は、電力消費を抑えるために電界効果トランジスタ(FET)が用

いられており、トランジスタ630のゲートはドライバ632に接続され、ドレインはプ

ルアップ抵抗R(図4参照)により所定の電圧が印加された接続線SDAに接続され、ソ

ースは接地されている。

The

トランジスタ630のゲートに印加される電圧がトランジスタ630を動作させる所定

値よりも小さければ、ドレインとソースとの間に電流が流れない。一方、トランジスタ6

30のゲートに印加される電圧がトランジスタ630を動作させる所定値以上であれば、

所定値の電圧が印加されたドレインから接地されているソースへ電流が流れることによっ

て、接続線SDAの電圧が低下する。なお、トランジスタ630は、10ミリアンペア程

度の電流をドレインからソースへ流しても破損しない仕様のものを用いている。

If the voltage applied to the gate of the

If the voltage applied to the gate of 30 is equal to or greater than the predetermined value for operating the

When a current flows from the drain to which the voltage of a predetermined value is applied to the source grounded, the voltage of the connection line SDA decreases. Note that the

ドライバ632は、データ(返答信号)を接続線SDAから出力する場合に、トランジ

スタ630にドレインとソースとの間に電流を流すためにトランジスタ630のゲートに

トランジスタ630が動作可能な値の電圧を印加する。そして、ドライバ632は、接続

線SDAの電圧をHIGHからLOWへ繰り返し変化させることによって、データを接続

線SDAから出力する。

The

フィルタ633は、接続線SCLに接続され、接続線SCLから入力されたデータのノ

イズを除去し、ノイズが除去されたデータをバスコントローラ634に出力する。

The

また、I2CI/Oエクスパンダ615には、当該I2CI/Oエクスパンダ615に備

わるアドレス設定用端子A0〜A3によって固有のアドレスが設定されており、バスコン

トローラ634に入力されている。さらに、I2CI/Oエクスパンダ615をリセット

するためのアドレスも、予め設定されている。

In addition, the I 2 CI /

バスコントローラ634は、接続線SDAから入力されたデータのアドレスがI2CI

/Oエクスパンダ615に設定された固有のアドレスと一致するか否かを判定し、一致し

ている場合に当該データを演出制御データとして取り込む。

The

It is determined whether or not the address matches the unique address set in the /

また、バスコントローラ634は、接続線SDAから入力されたデータのアドレスがI

2CI/Oエクスパンダ615に予め設定されたリセット用のアドレスと一致するか否か

を判定し、入力されたデータのアドレスとI2CI/Oエクスパンダ615に予め設定さ

れたリセット用のアドレスとが一致している場合に当該データを初期化指示データとして

取り込み、当該I2CI/Oエクスパンダ615を初期化する。

Also, the

2 It is determined whether or not the address matches with the address for resetting preset in the CI /

また、バスコントローラ634は、SCL接続線の信号レベルのLOWからHIGHへ

の変化回数が8回に達し8ビット目のデータを取り込んだ後、SCL接続線の信号レベル

がHIGHからLOWへ変化すると、返答信号を接続線SDAからマスタIC570に出

力する。さらに、SCL接続線の信号レベルがLOWからHIGHへ変化することが確認

され、再度SCL接続線の信号レベルがHIGHからLOWへ変化すると、接続線SDA

を開放する。つまり、SCL接続線の信号レベルのLOWからHIGHへの変化回数が9

回になるタイミングで返答信号を出力する。

In addition, when the signal level of the SCL connection line changes from HIGH to LOW after the

Open In other words, the number of times the signal level of the SCL connection line changes from LOW to HIGH is 9

Outputs a response signal at the same timing.

出力設定レジスタ635には、当該I2CI/Oエクスパンダ615の動作モードやポ

ート0〜15の出力状態が設定される。バスコントローラ634が接続線SDAから初期

化指示データを取り込んで、当該I2CI/Oエクスパンダ615が初期化された場合に

は、出力設定レジスタ635は、すべてのポート0〜15に電流が流れないように初期状

態に設定される。

In the

出力コントローラ636は、出力設定レジスタ635に設定されたデータに基づいて、

ポートドライバ637を介して、各ポート0〜15に接続された演出装置に電流を流すこ

とによって、演出装置の出力状態を実際に制御する。この出力状態は、バスコントローラ

634が接続線SDAから演出制御データを取り込むと、取り込んだ演出制御データに指

定されている内容に更新される。

By supplying current to the rendering devices connected to the

ドライバ637は、ポートに電流を流す場合に、電流を流すポートに接続されるトラン

ジスタ638A〜638Pが動作可能な電圧を当該トランジスタに印加する。

The

トランジスタ638A〜638Pのゲートはドライバ637に接続され、ドレインは図

8A及び図8Bに示すように演出装置を動作させるための電圧が印加された接続線に接続

するポート端子に接続され、ソースは接地されている。

The gates of the

トランジスタ638A〜638Pのゲートに印加される電圧がトランジスタ638A〜

638Pを動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れな

い。一方、638A〜638Pのゲートに印加される電圧がトランジスタ638を動作さ

せる所定値以上であれば、図8Aに示す電源Vled、又は図8Bに示す電源Vmotや

電源Vsolからゲートに印加されている所定の電圧が、トランジスタ638のドレイン

を介して接地されているソースへ電流が流れることによって、ポート端子に接続された演

出装置の出力状態を制御できる。

The voltage applied to the gates of the

If it is smaller than the predetermined value for operating 638P, no current flows between the drain and the source. On the other hand, if the voltage applied to the gates of 638A to 638P is equal to or higher than the predetermined value for operating the transistor 638, the predetermined voltage applied to the gate from the power supply Vled shown in FIG. 8A or the power supply Vmot shown in FIG. When the voltage of the current flows through the drain of the transistor 638 to the grounded source, the output state of the rendering device connected to the port terminal can be controlled.

また、装飾制御装置610のI2CI/Oエクスパンダ615は、I2CI/Oエクスパ

ンダ615のポート端子に接続された全ての演出装置を同時期に制御することが可能であ

るので、I2CI/Oエクスパンダ615のポート端子に接続された一つの演出装置を一

つのグループとして制御することができる。

In addition, since the I 2 CI /

そして、各装飾制御装置610に備わるI2CI/Oエクスパンダ615同士は、互い

に異なる個別アドレスが割り当てられているので、演出装置が複数のグループに分割され

た形態となっている。即ち、各装飾制御装置610に備わるI2CI/Oエクスパンダ6

15は、演出装置をグループ単位で制御可能なグループ単位制御手段として構成されてい

るものである。

And since I 2 CI /

従って、装飾制御装置610を統括する演出制御装置550は、グループ単位制御手段

を統括して制御するグループ統括制御手段として機能している。

Therefore, the

リセット信号発生回路639には、I2CI/Oエクスパンダ615に電源を供給する

接続線Vccと接続されるVcc端子、及び外部からのリセット信号を受け付けるRES

ET端子が接続されている。

The reset

ET terminal is connected.

リセット信号発生回路639は、I2CI/Oエクスパンダ615に電源が投入され、

電圧が所定値まで立ち上がった場合、リセット信号を発生させ、発生させたリセット信号

をバスコントローラ634、出力設定レジスタ635、及び出力コントローラ636に入

力する。

The reset

When the voltage rises to a predetermined value, a reset signal is generated, and the generated reset signal is input to the

なお、外部からLOWレベルのリセット信号が入力された場合には、リセット信号発生

回路639はリセット信号を出力するので、演出制御装置550のCPU551から、N

ORゲート回路590を経由して、RESET端子からリセット信号を入力するようにし

てもよい。RESET端子を使用しない場合は、図8A及び図8Bに示すようにRESE

T端子はHIGHにプルアップされていてもよい。

Since the reset

A reset signal may be input from the RESET terminal via the

The T terminal may be pulled up to HIGH.

図8Aは、本発明の第1の実施形態の装飾装置620を制御する装飾制御装置610の

I2CI/Oエクスパンダ615周辺の回路図である。

FIG. 8A is a circuit diagram around the I 2 CI /

I2CI/Oエクスパンダ615は、入力端子としてNC端子、RESET端子、SC

L端子、SDA端子、Vcc端子、A0〜A3端子、及びGND端子を備え、出力端子と

して、PORT0〜PORT15を備える。

I 2 CI /

An L terminal, an SDA terminal, a Vcc terminal, an A0 to A3 terminal, and a GND terminal are provided, and PORT0 to PORT15 are provided as output terminals.

RESET端子には、プルアップ抵抗Rを介してI2CI/Oエクスパンダ615に供

給される電源が接続されている。このため、リセット端子に印加される電圧は常にHIG

Hに維持されている。

The power supply supplied to the I 2 CI /

H is maintained.

SCL端子は接続線SCLに接続され、SDA端子は接続線SDAに接続される。 The SCL terminal is connected to the connection line SCL, and the SDA terminal is connected to the connection line SDA.

Vcc端子には、I2CI/Oエクスパンダ615に供給される電源が接続される。ま

た、Vcc端子には、電源ノイズを除去するコンデンサCPが接続される。

The power supply supplied to the I 2 CI /

A0端子〜A3端子は、I2CI/Oエクスパンダ615に固有のアドレスを設定する

ための端子である。なお、通常I2CI/Oエクスパンダ615のアドレスは、4ビット

で表現され、この端子にI2CI/Oエクスパンダ615の電源が印加されている場合に

はバスコントローラ634に「1」が設定され、この端子がグランドに接続されている場

合にはバスコントローラ634に「0」が設定される。

Terminals A0 to A3 are terminals for setting an address unique to the I 2 CI /

したがって、図8Aに示すI2CI/Oエクスパンダ615のアドレスは「0100」

であり、図8Bに示すI2CI/Oエクスパンダ615のアドレスは「0110」である

。GND端子は、電圧をグランドするための端子である。

Therefore, the address of the I 2 CI /

The address of the I 2 CI /

各PORT0端子〜PORT15端子は、電流制限抵抗R0〜R15を介して各LED

0〜LED15からなる装飾装置620に接続される。なお、PORT0にように、ポー

ト1個に対して1個のLEDを接続してもよいが、PORT1〜15のように、ポート1

個に対して複数個のLEDを接続してもよい。

The PORT0 to PORT15 terminals are connected to the LEDs via the current limiting resistors R0 to R15.

It is connected to a

A plurality of LEDs may be connected to each.

全てのポートにLEDを1個ずつ設ける場合は、1個のI2CI/Oエクスパンダ61

5によって、最大で16個のLEDを制御できることになる。また、各ポートに接続され

るLEDの個数が異なる場合は、1個のポートに直列に接続された全てのLEDを1種類

のLEDということにすれば、1個のI2CI/Oエクスパンダ615によって、最大で

16種類のLEDを制御できることになる。

If one LED is provided for every port, one I 2 CI / O expander 61

5 will allow up to 16 LEDs to be controlled. In addition, when the number of LEDs connected to each port is different, if all LEDs connected in series to one port are one type of LED, one I 2 CI / O expander With 615, up to 16 types of LEDs can be controlled.

PORT0端子〜PORT15端子に接続されるトランジスタ638A〜638P(図

7参照)のゲートに対してドライバ637から電圧が印加されると、電圧が印加されたト

ランジスタ638A〜638Pのドレインからソースへ電流が流れることが可能になり、

PORT0端子〜PORT15端子に接続されるLED0〜LED15に電流が流れ、各

LED0〜LED15は点灯する。

When a voltage is applied from the

A current flows through the

一方、ドライバ637がトランジスタ638A〜638Pのゲートに電圧を印加しなけ

れば、各LED0〜LED15に電流が流れない状態になり、各LED0〜LED15は

点灯しない。

On the other hand, if the

なお、I2CI/Oエクスパンダ615のPORT0端子〜PORT15端子には、L

EDの代わりに、モータやソレノイドを接続することも可能であるので、I2CI/Oエ

クスパンダ615を用いて、モータやソレノイドを駆動する場合について説明する。

Note that the PORT0 to PORT15 terminals of the I 2 CI /

Since a motor or a solenoid can be connected instead of the ED, a case where the motor or the solenoid is driven using the I 2 CI /

図8Bは、本発明の第1の実施形態の役物駆動MOT561及び役物駆動SOL560

を制御する装飾制御装置610のI2CI/Oエクスパンダ615周辺の回路図である。

FIG. 8B shows the

FIG. 16 is a circuit diagram of the periphery of the I 2 CI /

役物駆動MOT561はステッピングモータにより構成され、ステッピングモータを駆

動する各相の信号端子に、所定の電圧を順次印加することで回動する。本実施形態では、

役物駆動MOT561の各相の信号端子が、PORT0端子〜PORT3端子に接続され

る。

The

The signal terminals of each phase of the

役物駆動MOT561に接続されているPORT0端子〜PORT3端子に接続される

トランジスタ638A〜638Dのいずれかのゲートに対してドライバ637から電圧が

印加されると、電圧が印加されたトランジスタ638A〜638Dのドレインからソース

へ電流が流れることが可能になり、PORT0端子〜PORT3端子に接続される役物駆

動MOT561に電流が流れ、役物駆動MOT561が駆動する。

When a voltage is applied from the

なお、各PORT0端子〜PORT3端子と役物駆動MOT561とを接続する接続線

は分岐し、分岐した一方の接続線は、役物駆動MOT561に供給される電源にダイオー

ドD及びツェナダイオードZDを介して接続される。

The connection line connecting the PORT0 terminals to the PORT3 terminals to the

また、PORT端子15は、役物駆動SOL560に接続される。役物駆動SOL56

0に接続されているPORT15端子に接続されるトランジスタ638Pのゲートに対し

てドライバ637から電圧が印加されると、電圧が印加されたトランジスタ638Pのド

レインからソースへ電流が流れることが可能になり、PORT15端子に接続される役物

駆動SOL560に電流が流れ、役物駆動SOL560が駆動する。

In addition, the

When a voltage is applied from the

なお、図8Bでは、I2CI/Oエクスパンダ615に役物駆動MOT561及び役物

駆動SOL560の双方が接続されているが、一つのI2CI/Oエクスパンダ615に

対して、役物駆動MOT561及び役物駆動SOL560の少なくとも一方だけを接続し

た構成でもよい。

In FIG. 8B, with respect to I 2 CI / O Aix although both character object drive MOT561 and character object

例えば、ステッピングモータだけを制御するグループとしてのI2CI/Oエクスパン

ダ615を専用に設けたり、ソレノイドだけを制御するグループとしてのI2CI/Oエ

クスパンダ615を専用に設けるようにしてもよい。このような構成により、同一グルー

プに属する演出装置を同じタイミングで制御することが可能となるので、高速処理が必要

な演出装置だけをグループ化して効率よく制御することも可能となる。

For example, the I 2 CI /

図9は、本発明の第1実施形態の中継基板600の入出力に関する接続線の回路図であ

る。

FIG. 9 is a circuit diagram of connection lines related to input and output of the

中継基板600は、上流コネクタ601、二つの下流コネクタ602A、602B、及

びI2CI/Oエクスパンダ615を備える。

The

上流コネクタ601は中継基板600よりも上流のマスタIC570に接続されるコネ

クタであり、コネクタ602A、602Bは、中継基板600よりも下流の装飾制御装置

610に接続される。

The

二つの下流コネクタ602A、602Bに接続線SDAを接続するために、上流コネク

タ601から延びる内部接続線SDA911は分岐901で第1接続線SDA921と第

2接続線SDA931とに分岐する。第1接続線SDA921は下流コネクタ602Aに

接続され、第2接続線SDA931は下流コネクタ602Bに接続される。

In order to connect the connection line SDA to the two

同じく、上流コネクタ601から延びる内部接続線SCL912は分岐902で第1接

続線SCL922と第2接続線SCL932とに分岐する。第1接続線SCL922は下

流コネクタ602Aに接続され、第2接続線SCL932は下流コネクタ602Bに接続

される。

Similarly, the internal

接続線SDAをI2CI/Oエクスパンダ615に接続するために、第2接続線SDA

931は分岐903で分岐し、分岐した第2接続線SDA931はI2CI/Oエクスパ

ンダ615の図8A及び図8に示すSDA端子に接続される。また、接続線SCLをI2

CI/Oエクスパンダ615に接続するために、第2接続線SCL932は分岐904で

分岐し、分岐した第2接続線SCL932はI2CI/Oエクスパンダ615の図8A及

び図8Bに示すSCL端子に接続される。

In order to connect the connection line SDA to the I 2 CI /

The

In order to connect to the CI /

なお、I2CI/Oエクスパンダ615には、I2CI/Oエクスパンダ615の電源電

圧となる電圧Vccが供給されている。また、図9では図示されていないが、I2CI/

Oエクスパンダ615からは、中継基板600に設けたLED(装飾装置200)を駆動

する各ポート0〜15の信号線(図8A参照)が出力されている。

The I 2 CI /

The O expander 615 outputs signal lines (see FIG. 8A) of

また、I2CI/Oエクスパンダ615は、第2接続線SDA931及び第2接続線S

CL932が接続されるとしたが、第1接続線SDA921及び第1接続線SCL922

に接続されてもよい。

In addition, the I 2 CI /

Although it is assumed that the

It may be connected to

I2CI/Oエクスパンダ615が上流のマスタIC570に接続線SDAを介して出

力する信号、及び上流のマスタIC570から中継基板600のI2CI/Oエクスパン

ダ615へ接続線SDAを介して入力される信号のノイズを除去するために、内部接続線

SDA911にはツェナダイオードZD941が接続されている。

A signal that the I 2 CI /

具体的には、内部接続線SDA911は分岐905で分岐し、分岐した内部接続線SD

A911はツェナダイオードZD941のカソード側に接続され、ツェナダイオードZD

941のアノード側は接地されている。

Specifically, internal connection line SDA 911 is branched at

A 911 is connected to the cathode side of

The anode side of 941 is grounded.

このため、内部接続線SDA911に印加された所定以上の電圧(例えば、パルス性の

ノイズ信号)は、ツェナダイオードZD941によって逃がされる。

Therefore, a voltage (for example, a pulse noise signal) higher than a predetermined voltage applied to the internal connection line SDA 911 is released by the

また、上流のマスタIC570から中継基板600のI2CI/Oエクスパンダ615

へ接続線SCLを介して入力される信号のノイズを除去するために、内部接続線SCL9

12にはツェナダイオードZD942が接続されている。

Also, the I 2 CI /

In order to eliminate noise on the signal input through connection line SCL, internal connection line SCL9

The

具体的には、内部接続線SCL912は分岐906で分岐し、分岐した内部接続線SC

L912はツェナダイオードZD942のカソード側に接続され、ツェナダイオードZD

942のアノード側は接地されている。

Specifically, internal

The anode side of 942 is grounded.

このため、内部接続線SCL912に印加された所定以上の電圧(例えば、パルス性の

ノイズ信号)は、ツェナダイオードZD942によって逃がされる。

For this reason, a voltage (for example, a pulse noise signal) higher than a predetermined voltage applied to the internal connection line SCL912 is released by the Zener diode ZD942.

中継基板600のI2CI/Oエクスパンダ615が下流コネクタ602Aに接続され

た装飾制御装置610に接続線SDAを介して出力する信号、及び下流コネクタ602A

に接続された装飾制御装置610から中継基板600のI2CI/Oエクスパンダ615

へ接続線SDAを介して入力される信号のノイズを除去するために、第1接続線SDA9

21にはツェナダイオードZD943が接続されている。

A signal output from the I 2 CI /

The I 2 CI /

In order to remove noise of the signal input through connection line SDA, first connection line SDA9

The Zener diode ZD943 is connected to the

具体的には、第1接続線SDA921は分岐907で分岐し、分岐した第1接続線SD

A921はツェナダイオードZD943のカソード側に接続され、ツェナダイオードZD

943のアノード側は接地されている。

Specifically, the first

A 921 is connected to the cathode side of zener diode ZD943, zener diode ZD

The anode side of 943 is grounded.

このため、内部接続線SDA921に印加された所定以上の電圧(例えば、パルス性の

ノイズ信号)は、ツェナダイオードZD943によって逃がされる。

Therefore, a voltage (for example, a pulse noise signal) higher than a predetermined voltage applied to the internal

また、第1接続線SDA921に接続されるツェナダイオードZD943と同じく、第

2接続線SDA931にもツェナダイオード945が接続される。

Further, similarly to the Zener diode ZD943 connected to the first connection line SDA921, the

また、中継基板600のI2CI/Oエクスパンダ615から下流コネクタ602Aに

接続された装飾制御装置610へ接続線SCLを介して入力される信号のノイズを除去す

るために、第1接続線SCL922にはツェナダイオードZD944が接続されている。

In addition, in order to remove noise of a signal input from the I 2 CI /

具体的には、第1接続線SCL922は分岐908で分岐し、分岐した第1接続線SC

L922はツェナダイオードZD944のカソード側に接続され、ツェナダイオードZD

944のアノード側は接地されている。

Specifically, the first

The anode side of 944 is grounded.

このため、内部接続線SCL922に印加された所定以上の電圧(例えば、パルス性の

ノイズ信号)は、ツェナダイオードZD944によって逃がされる。

Therefore, a voltage (for example, a pulse noise signal) higher than a predetermined voltage applied to the internal

また、第1接続線SCL922に接続されるツェナダイオードZD944と同じく、第

2接続線SCL932にもツェナダイオードZD946が接続される。

Further, similarly to the

また、マスタIC570に接続される上流側の接続線SDA、及び装飾制御装置610

に接続される下流側の接続線SDAの電圧をプルアップするためのプルアップ抵抗R95

1が、第1接続線SDA921に接続される。同じく、マスタIC570に接続される上

流側の接続線SCL、及び装飾制御装置610に接続される下流側の接続線SCLの電圧

をプルアップするためのプルアップ抵抗R952が、第1接続線SDA922に接続され

る。

Also, the upstream connection line SDA connected to the

Pull-up resistor R95 for pulling up the voltage of the downstream connection line SDA connected to

1 is connected to the first

具体的には、第1接続線SDA921は分岐909で分岐し、分岐した第1接続線SD

A921はプルアップ抵抗R951に接続される。同じく第1接続線SCL922は分岐

910で分岐し、分岐した第1接続線SCL922はプルアップ抵抗R952に接続され

る。

Specifically, the first

A 921 is connected to pull-up

なお、接続線SDA及び接続線SCLの電圧をプルアップするプルアップ抵抗951、

952は、中継基板600が備えなくてもよく、マスタIC570が備えてもよいし、中

継基板600以外の装飾制御装置610が備えてもよい。要するに、接続線SDA及び接

続線SCLを駆動するトランジスタのドレインの端子に、電圧Vccを供給できる箇所で

あれば、どこでもよい。

Note that a pull-up

The

中継基板600のI2CI/Oエクスパンダ615に電源電圧を供給する接続線Vcc

に接続される上流コネクタ601のVcc端子から延びる内部接続線Vcc971と、上

流コネクタ601のGND端子から延び、接地されている内部接続線GND972とは、

平滑コンデンサC961及びバイパスコンデンサ962を介して接続されている。

Connection line Vcc that supplies power supply voltage to I 2 CI /

The internal

It is connected via the smoothing capacitor C 961 and the

平滑コンデンサC961は、電源の電圧波形を滑らかにするためのコンデンサであり、

バイパスコンデンサCP962は、電源の電圧のノイズを除去するためのコンデンサであ

る。

The smoothing capacitor C961 is a capacitor for smoothing the voltage waveform of the power supply,

The bypass capacitor CP962 is a capacitor for removing noise of the voltage of the power supply.

このため、中継基板600のI2CI/Oエクスパンダ615に供給される電源電圧は

、平滑コンデンサC961により電圧が平滑化され、バイパスコンデンサ962によりノ

イズが除去されて、I2CI/Oエクスパンダ615に供給される。

For this reason, the power supply voltage supplied to the I 2 CI /

同じく、下流コネクタ602A、602BのVcc端子から延びる内部接続線Vcc9

73と、GND端子から延びる内部接続線GND974とは、平滑コンデンサC961及

びバイパスコンデンサ962を介して接続されている。これによって、平滑化され、ノイ

ズが除去された電圧が下流の装飾制御装置610に接続される接続線Vccに印加される

。

Similarly, internal connection line Vcc9 extending from the Vcc terminal of

73 and the internal

図10は、本発明の第1実施形態の装飾制御装置610の入出力に関する接続線の回路

図である。

FIG. 10 is a circuit diagram of connection lines regarding input and output of the

装飾制御装置610は、上流コネクタ611、I2CI/Oエクスパンダ615、及び

下流コネクタ612を備える。

The

上流コネクタ611には、中継基板600又は上流側の装飾制御装置610からバスが

接続される。下流コネクタ612には、下流側の装飾制御装置610に接続するバスが接

続される。

A bus is connected to the

上流コネクタ611のSDA端子と下流コネクタ612のSDA端子とは、内部接続線

SDA1011によって接続されている。また、上流コネクタ611のSCL端子と下流

コネクタ612のSCL端子とは、内部接続線SCL1012によって接続されている。

The SDA terminal of the

接続線SDAをI2CI/Oエクスパンダ615に接続するために、内部接続線SDA

1011は分岐1001で分岐し、分岐した内部接続線SDA1011はI2CI/Oエ

クスパンダ615の図8A及び図8に示すSDA端子に接続される。また、接続線SCL

をI2CI/Oエクスパンダ615に接続するために、内部接続線SCL1012は分岐

1002で分岐し、分岐した内部接続線SCL1012はI2CI/Oエクスパンダ61

5の図8A及び図8Bに示すSCL端子に接続される。

In order to connect connection line SDA to I 2 CI /

1011 is branched at

In order to connect the I 2 CI /

5 is connected to the SCL terminal shown in FIGS. 8A and 8B.

なお、I2CI/Oエクスパンダ615には、I2CI/Oエクスパンダ615の電源電

圧となる電圧Vccが供給されている。また、図10では図示されていないが、I2CI

/Oエクスパンダ615からは、当該装飾制御装置610に係わるLED(装飾装置20

0)を駆動する各ポート0〜15の信号線(図8A参照)が出力されている。

The I 2 CI /

LED relating to the decoration control device 610 (decorative device 20)

Signal lines (see FIG. 8A) of

図10に示す装飾制御装置610のI2CI/Oエクスパンダ615が上流コネクタ6

11に接続された上流の装飾制御装置610又は中継基板600に接続線SDAを介して

出力する信号、及び上流コネクタ611に接続された上流の装飾制御装置610又は中継

基板600から図10に示す装飾制御装置610のI2CI/Oエクスパンダ615へ接

続線SDAを介して入力される信号のノイズを除去するために、内部接続線SDA101

1にはツェナダイオードZD1041が接続されている。

The I 2 CI /

A signal shown in FIG. 10 from an upstream

The Zener diode ZD1041 is connected to 1.

具体的には、内部接続線SDA1011は分岐1003で分岐し、分岐した内部接続線

SDA1011はツェナダイオードZD1041のカソード側に接続され、ツェナダイオ

ードZD1041のアノード側は接地されている。

Specifically, the internal connection line SDA1011 branches at a branch 1003, the branched internal connection line SDA1011 is connected to the cathode side of the Zener diode ZD1041, and the anode side of the Zener diode ZD1041 is grounded.

このため、内部接続線SDA1011に印加された所定以上の電圧(例えば、パルス性

のノイズ信号)は、ツェナダイオードZD1041によって逃がされる。

For this reason, a voltage (for example, a pulsating noise signal) applied to the internal connection line SDA1011 is exceeded by the Zener diode ZD1041.

また、上流コネクタ611に接続される上流の装飾制御装置610又は中継基板600

から図10に示す装飾制御装置610のI2CI/Oエクスパンダ615へ接続線SCL

を介して入力される信号のノイズを除去するために、内部接続線SCL1012にはツェ

ナダイオードZD942が接続されている。

Also, the upstream

10 to the I 2 CI /

The Zener diode ZD942 is connected to the internal connection line SCL1012 in order to remove noise of the signal input via the.

具体的には、内部接続線SCL1012は分岐1004で分岐し、分岐した内部接続線

SCL1012はツェナダイオードZD1042のカソード側に接続され、ツェナダイオ

ードZD1042のアノード側は接地されている。

Specifically, the internal connection line SCL1012 branches at a branch 1004, the branched internal connection line SCL1012 is connected to the cathode side of the Zener diode ZD1042, and the anode side of the Zener diode ZD1042 is grounded.

このため、内部接続線SCL1012に印加された所定以上の電圧(例えば、パルス性

のノイズ信号)は、ツェナダイオードZD1042によって逃がされる。

Therefore, a voltage (for example, a pulse noise signal) higher than a predetermined voltage applied to the internal connection line SCL1012 is released by the Zener diode ZD1042.

図10に示す装飾制御装置610のI2CI/Oエクスパンダ615が下流コネクタ6

12に接続された下流の装飾制御装置610に接続線SDAを介して出力する信号、及び

下流コネクタ612に接続された下流の装飾制御装置610から図10に示す装飾制御装

置のI2CI/Oエクスパンダ615へ接続線SDAを介して入力される信号のノイズを

除去するために、内部接続線SDA1011にはツェナダイオードZD1043が接続さ

れている。

The I 2 CI /

A signal output to the downstream

具体的には、内部接続線SDA1011は分岐1005で分岐し、分岐した内部接続線

SDA1011はツェナダイオードZD1043のカソード側に接続され、ツェナダイオ

ードZD1043のアノード側は接地されている。

Specifically, the internal connection line SDA1011 branches at a

このため、内部接続線SDA1011に印加された所定以上の電圧(例えば、パルス性

のノイズ信号)は、ツェナダイオードZD1043によって逃がされる。

Therefore, a voltage (for example, a pulse noise signal) higher than a predetermined voltage applied to the internal connection line SDA1011 is released by the Zener diode ZD1043.

また、図10に示す装飾制御装置610のI2CI/Oエクスパンダ615から下流コ

ネクタ612に接続された下流の装飾制御装置610へ接続線SCLを介して入力される

信号のノイズを除去するために、内部接続線SCL1012にはツェナダイオードZD1

044が接続されている。

Also, in order to remove noise of a signal input via connection line SCL from I 2 CI /

044 is connected.

具体的には、内部接続線SCL1012は分岐1006で分岐し、分岐した内部接続線

SCL1012はツェナダイオードZD1044のカソード側に接続され、ツェナダイオ

ードZD1044のアノード側は接地されている。

Specifically, the internal connection line SCL1012 branches at a

このため、内部接続線SCL1012に印加された所定以上の電圧(例えば、パルス性

のノイズ信号)は、ツェナダイオードZD1044によって逃がされる。

Therefore, a voltage (for example, a pulse noise signal) higher than a predetermined voltage applied to the internal connection line SCL1012 is released by the Zener diode ZD1044.

装飾制御装置610のI2CI/Oエクスパンダ615に電源電圧を供給する接続線V

ccに接続される上流コネクタ611のVcc端子から延びる内部接続線Vcc1071

と、上流コネクタ611のGND端子から延び、接地されている内部接続線GND107

2とは、平滑コンデンサC1061及びバイパスコンデンサ1062を介して接続されて

いる。

Connection V for supplying power supply voltage to the I 2 CI /

Internal connection line Vcc1071 extending from the Vcc terminal of the

And the internal connection line GND 107 extending from the GND terminal of the

2 is connected via the smoothing capacitor C1061 and the

平滑コンデンサC1061は図9に示す平滑コンデンサC961と同じコンデンサであ

り、バイパスコンデンサCP1062は図9に示すバイパスコンデンサ962と同じコン

デンサである。

The smoothing capacitor C1061 is the same as the smoothing capacitor C961 shown in FIG. 9, and the bypass capacitor CP1062 is the same as the

また、下流コネクタ612のVcc端子から延びる内部接続線Vcc1073と、GN

D端子から延びる内部接続線GND1074とは、平滑コンデンサC1061及びバイパ

スコンデンサ1062を介して接続されている。

Also, an internal

The internal

図11は、本発明の第1の実施形態の演出制御装置550から装飾制御装置610に出

力されるデータに含まれるスレーブアドレス1100の説明図である。

FIG. 11 is an explanatory diagram of a

スレーブアドレス1100は、上位3ビットからなる固定アドレス部1101及び下位

5ビットからなる可変アドレス部1102を含む。

The

固定アドレス部1101は、「110」が予め設定されていて、I2CI/Oエクスパ

ンダ615が変更できないアドレスである。

The fixed

可変アドレス部1102は、I2CI/Oエクスパンダ615に設定可能なアドレスで

あり、制御対象となるI2CI/Oエクスパンダ615のA0〜A3の端子に設定されて

いるパターンに対応した4ビットのI2CI/Oエクスパンダアドレス1103と、当該

データが読み出し要求であるのか書き込み要求であるのかを示す1ビットのR/W識別デ

ータ1104と、が含まれる。

演出制御装置550から装飾制御装置610に出力される演出制御データは、書き込み

要求であるので、R/W識別データ1104には、通常「0」が登録される。

Since the effect control data output from the

図12は、本発明の第1の実施形態のI2CI/Oエクスパンダアドレステーブル12

00の説明図である。

FIG. 12 shows the I 2 CI / O expander address table 12 according to the first embodiment of this invention.

FIG.

I2CI/Oエクスパンダアドレステーブル1200は、マスタIC570によって管

理されるテーブルである。I2CI/Oエクスパンダアドレステーブル1200は、スレ

ーブアドレス1201とI2CI/Oエクスパンダアドレス1202との対応関係を示し

ている。

The I 2 CI / O expander address table 1200 is a table managed by the

スレーブアドレス1201には、演出制御装置550により送受信の対象として指定さ

れる装飾制御装置610のスレーブアドレスが格納されている。スレーブアドレスは、図

13で前述したように、上位3ビットからなる固定アドレス部と、4ビットのI2CI/

Oエクスパンダアドレスと、1ビットのR/W識別データとを組み合わせて構成される。

The

It is configured by combining the O expander address and 1-bit R / W identification data.

I2CI/Oエクスパンダアドレス1202には、図8Aや図8Bで前述したように、

各スレーブアドレスに対応する4ビットのI2CI/Oエクスパンダアドレスが登録され

る。

As described above with reference to FIGS. 8A and 8B, the I 2 CI /

A 4-bit I 2 CI / O expander address corresponding to each slave address is registered.

ただし、I2CI/Oエクスパンダアドレスのうち、アドレス「1000」及びアドレ

ス「1011」は、各I2CI/Oエクスパンダ615を相互に識別するための固有のア

ドレスとしては使用できない。

However, among the I 2 CI / O expander addresses, the address “1000” and the address “1011” can not be used as unique addresses for mutually identifying the respective I 2 CI /

「1000」は、すべての装飾制御装置610に対する指令を出力する場合に指定され

るアドレス(オールコールアドレス)の電源投入時のデフォルト値として用いられる。「

1011」はソフトウェアによって、マスタIC570に接続されている全ての装飾制御

装置610を無条件にリセットする場合に用いられる共通アドレスである。

“1000” is used as a power-on default value of an address (all call address) specified when outputting a command to all the

1011 "is a common address used when software unconditionally resets all

このように、装飾制御装置610のI2CI/Oエクスパンダ615に設定可能な固有

アドレスは14個であるために、演出制御装置550は、14個のI2CI/Oエクスパ

ンダ615を制御できる。また、一つの装飾制御装置610は、PORT0〜PORT1

5を備えるので、16個(言い換えれば16種類)のLEDを制御できる。よって、演出

制御装置550は、224個(言い換えれば224種類)のLEDを制御できる。

Thus, since there are 14 unique addresses that can be set in the I 2 CI /

Since 5 is provided, 16 (16 in other words) LEDs can be controlled. Thus, the

図13は、本発明の第1の実施形態のI2CI/Oエクスパンダ615に備わる出力設

定レジスタ635(図7参照)に割り当てられたワークレジスタを説明するための図であ

る。

FIG. 13 is a diagram for describing a work register assigned to the output setting register 635 (see FIG. 7) provided in the I 2 CI /

I2CI/Oエクスパンダ615の出力設定レジスタ635には、ワークレジスタ(デ

バイスレジスタ)と、コントロールレジスタ(制御レジスタ)とが割り当てられている。

ワークレジスタは、I2CI/Oエクスパンダ615に対して予め定義されている設定を

行うための情報や、I2CI/Oエクスパンダ615に接続されている演出装置(例えば

、LED)の出力態様を特定するための情報を記憶するものである。また、コントロール