JP6212754B2 - 光半導体装置及びその製造方法 - Google Patents

光半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP6212754B2 JP6212754B2 JP2013137067A JP2013137067A JP6212754B2 JP 6212754 B2 JP6212754 B2 JP 6212754B2 JP 2013137067 A JP2013137067 A JP 2013137067A JP 2013137067 A JP2013137067 A JP 2013137067A JP 6212754 B2 JP6212754 B2 JP 6212754B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- optical waveguide

- semiconductor

- region

- cladding region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Semiconductor Lasers (AREA)

Description

Grating Distributed Reflector)を備える半導体レーザ等が提案されている(例えば、特許文献1参照)。

Grating Distributed Reflector)領域α、SG−DFB(Sampled Grating Distributed Feedback)領域β、及びPC(Power

Control)領域γを順に連結させた構造を有する。SD−DR領域αの光進行方向に沿ってメサ溝48が形成されている。

Coolor)400上に設置されている。温度制御装置400は、ペルチェ素子によって半導体レーザチップ300の温度を制御する装置である。

Vapor Phase Epitaxy)法を用いることができる。図6(b)のように、下側クラッド層32b上に形成したレジストマスク(不図示)をマスクとして、下側クラッド層32bに対してエッチング処理を施す。エッチング処理は、例えばCH4ガスとO2ガスとエッチングガスを用いたRIEエッチングで行うことができる。このエッチング処理により、回折格子94が形成される。

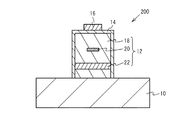

12 半導体領域

14、40 絶縁膜

16、42 ヒータ

18 クラッド領域

20、36 光導波路層

22、34 熱伝導抑制層

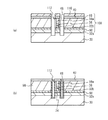

50 メサ半導体領域

32a、32b 下側クラッド層

38a、38b 上側クラッド層

60 低熱伝導率層

108 積層半導体層

110 マスク層

106 第1メサストライプ

112 第2メサストライプ

200 分布反射器

300 半導体レーザチップ

400 温度制御装置

Claims (4)

- 下側クラッド領域、光導波路層、及び上側クラッド領域からなる光導波路を含み、波長選択機能を有するサンプルドグレーティング分布反射領域と、前記サンプルドグレーティング分布反射領域に配置され、前記光導波路の温度を変化させることで屈折率を変化させるヒータと、を備える光半導体装置の製造方法において、

半導体基板上に、半導体層と、前記半導体層上に設けられた前記下側クラッド領域と、前記下側クラッド領域上に設けられた前記光導波路層と、前記光導波路層上に設けられた前記上側クラッド領域と、を有する積層半導体層を形成する工程と、

ストライプ状の第1のマスク層を用いて前記積層半導体層のうち、前記下側クラッド領域と前記光導波路層と前記上側クラッド領域をエッチングし、前記光導波路層の側面が露出した第1のメサストライプを形成する工程と、

前記第1のメサストライプの両側に埋め込み層を形成する工程と、

前記第1のマスク層の幅より大きいストライプ状の第2のマスク層を用いて前記積層半導体層をエッチングし、前記半導体層の側面が露出した第2のメサストライプを形成する工程と、

前記第2のメサストライプに対して酸化雰囲気中で熱処理を行い、前記半導体基板と前記光導波路層の間に設けられた前記半導体層の側面から前記半導体層の内部まで酸化させる工程と、

前記第2のメサストライプ上に、前記ヒータを形成する工程と、を備える、光半導体装置の製造方法。 - 前記半導体層を酸化させる工程は、酸化作用を有する気体を1%以上含む雰囲気中で、300℃以上且つ700℃未満の温度で熱処理を行う、請求項1に記載の光半導体装置の製造方法。

- 前記半導体基板および前記下側クラッド領域は、InPの材料を含み、

前記半導体層は、GaXAlYIn(1−X−Y)PZAs(1−Z)(但し、0≦X≦0.08、0.20≦Y≦0.40、0<Z<1.0)を含む、請求項1または2に記載の光半導体装置の製造方法。 - 半導体基板と、前記半導体基板上に設けられた下側クラッド領域と、前記下側クラッド領域上に設けられた光導波路層と、前記光導波路層上に設けられた上側クラッド領域と、前記半導体基板と前記光導波路層の間に配置され、前記下側クラッド領域より小さい熱伝導率を有し、かつ、酸化された半導体層を含む熱伝導抑制層と、を含み、前記熱伝導抑制層の側面が露出されたメサストライプと、

前記メサストライプを含み、波長選択機能を有するサンプルドグレーティング分布反射領域と、

前記サンプルドグレーティング分布反射領域に配置され、前記光導波路層の温度を変化させることで屈折率を変化させるヒータと、を備え、

前記熱伝導抑制層は、前記側面から内部まで酸化され、

前記熱伝導抑制層の熱伝導率が、前記熱伝導抑制層の中央部より前記側面の方が小さい、光半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013137067A JP6212754B2 (ja) | 2013-06-28 | 2013-06-28 | 光半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013137067A JP6212754B2 (ja) | 2013-06-28 | 2013-06-28 | 光半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015012176A JP2015012176A (ja) | 2015-01-19 |

| JP2015012176A5 JP2015012176A5 (ja) | 2016-08-18 |

| JP6212754B2 true JP6212754B2 (ja) | 2017-10-18 |

Family

ID=52305079

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013137067A Active JP6212754B2 (ja) | 2013-06-28 | 2013-06-28 | 光半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6212754B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6782082B2 (ja) * | 2016-03-11 | 2020-11-11 | 古河電気工業株式会社 | 半導体光素子、およびその製造方法 |

| JP6667325B2 (ja) * | 2016-03-11 | 2020-03-18 | 古河電気工業株式会社 | 半導体光素子 |

| JP6782083B2 (ja) * | 2016-03-11 | 2020-11-11 | 古河電気工業株式会社 | 半導体光素子、およびその製造方法 |

| JP7145765B2 (ja) | 2017-02-07 | 2022-10-03 | 古河電気工業株式会社 | 光導波路構造 |

| JP7012409B2 (ja) * | 2018-03-14 | 2022-01-28 | 古河電気工業株式会社 | 光導波路構造及びその製造方法 |

| CN113396512A (zh) * | 2019-02-08 | 2021-09-14 | 古河电气工业株式会社 | 半导体元件 |

| DE102019108701A1 (de) * | 2019-04-03 | 2020-10-08 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Verfahren zur Herstellung einer Mehrzahl von Bauteilen, Bauteil und Bauteilverbund aus Bauteilen |

| JP7309667B2 (ja) * | 2020-05-29 | 2023-07-18 | 日本ルメンタム株式会社 | ヒータを集積したリッジ型半導体光素子 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4164679B2 (ja) * | 2004-02-16 | 2008-10-15 | セイコーエプソン株式会社 | 面発光型半導体レーザ |

| JP2007273644A (ja) * | 2006-03-30 | 2007-10-18 | Eudyna Devices Inc | 光半導体装置、レーザチップおよびレーザモジュール |

| KR101295896B1 (ko) * | 2009-12-17 | 2013-08-12 | 한국전자통신연구원 | 레이저 소자 |

| JP5366149B2 (ja) * | 2010-03-16 | 2013-12-11 | 独立行政法人産業技術総合研究所 | 半導体レーザー装置 |

| JP5303580B2 (ja) * | 2011-01-11 | 2013-10-02 | 住友電工デバイス・イノベーション株式会社 | 光半導体装置、レーザチップおよびレーザモジュール |

| JP2013033892A (ja) * | 2011-06-29 | 2013-02-14 | Sumitomo Electric Ind Ltd | 半導体レーザおよびレーザ装置 |

| JP2013026254A (ja) * | 2011-07-15 | 2013-02-04 | Sumitomo Electric Ind Ltd | 光導波路および光導波路の製造方法 |

-

2013

- 2013-06-28 JP JP2013137067A patent/JP6212754B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015012176A (ja) | 2015-01-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6212754B2 (ja) | 光半導体装置及びその製造方法 | |

| CN107431331B (zh) | 波长可变激光元件以及激光模块 | |

| EP1841023B1 (en) | Temperature tuning of the wavelength of a laser diode by heating | |

| US20130156052A1 (en) | Methods and apparatus for temperature tuning of semiconductor lasers | |

| JP4954992B2 (ja) | 半導体光反射素子及び該半導体光反射素子を用いる半導体レーザ及び該半導体レーザを用いる光トランスポンダ | |

| US20030016720A1 (en) | Semiconductor laser device having selective absortion qualities | |

| US7949028B2 (en) | Method of tuning a semiconductor laser device having coupled cavities | |

| WO2016152274A1 (ja) | 波長可変レーザ素子およびレーザモジュール | |

| JP6667325B2 (ja) | 半導体光素子 | |

| JPH11214793A (ja) | 分布帰還型半導体レーザ | |

| Rauter et al. | Single-mode tapered quantum cascade lasers | |

| JP7145765B2 (ja) | 光導波路構造 | |

| JP2003023208A (ja) | 波長可変半導体レーザ | |

| JP4215984B2 (ja) | 異質インターサブバンド(hisb)光デバイス | |

| JP2017163081A (ja) | 半導体光素子、およびその製造方法 | |

| JP5272859B2 (ja) | 半導体レーザ素子 | |

| JP5303580B2 (ja) | 光半導体装置、レーザチップおよびレーザモジュール | |

| JPH0697604A (ja) | 分布反射型半導体レーザ | |

| JP5163355B2 (ja) | 半導体レーザ装置 | |

| JP2014220388A (ja) | 光半導体素子、光半導体装置、および光半導体素子の制御方法 | |

| JPH06177481A (ja) | 半導体レーザ装置 | |

| WO2023135629A1 (ja) | 半導体レーザおよびモジュール素子 | |

| JP4718020B2 (ja) | 光半導体装置 | |

| JP2012059844A (ja) | 半導体発光素子、及び半導体発光素子を作製する方法 | |

| JP6782082B2 (ja) | 半導体光素子、およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160624 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160624 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170407 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170822 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170825 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6212754 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |