以下では、本明細書に開示する発明の実施の形態について図面を用いて詳細に説明する。ただし、本明細書に開示する発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本明細書に開示する発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

また、「ソース」および「ソース電極」ならびに「ドレイン」および「ドレイン電極」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。また本明細書等において、チャネル領域とは、ソース領域(ソース電極)およびドレイン領域(ドレイン電極)の対向する領域をいう。

なお、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

(実施の形態1)

本実施の形態では、半導体装置の一形態の構成およびその材料について、図1を参照して説明する。

<<半導体装置の構成>>

図1(A−1)はトランジスタ31および容量素子32の平面図であり、図1(A−2)は図1(A−1)の一点鎖線A−Bの断面図、図1(A−3)は図1(A−1)の一点鎖線C−Dの断面図である。なお、図1(A−1)では煩雑になることを避けるために、トランジスタ31および容量素子32の構成要素の一部(例えば、絶縁膜16など)を省略して図示する。また図1(B)はトランジスタ31および容量素子32の接続を示す回路図である。

図1に示すトランジスタ31は、絶縁表面を有する基板10上に設けられた半導体膜12aと、絶縁膜16と、絶縁膜を挟んで半導体膜と重畳するように設けられたゲート電極18aと、半導体膜12aの外周端部およびゲート電極18aの外周端部に至らない内側に設けられ、かつ半導体膜と接する第1の電極14aと、半導体膜と接する第2の電極14bと、を有する。

トランジスタ31の絶縁膜16はゲート絶縁膜、電極14aはドレイン電極、電極14bはソース電極として機能する。

また容量素子32は、絶縁膜16と、第2の電極14bと、絶縁膜16を挟んで第2の電極14bと少なくとも一部が重なる第3の電極18bと、を有する。

なお本明細書等において、外周端部とは島状または環状の電極等を平面視したときの電極等の外周の端部である。また内周端部は環状である電極等を平面視したときの電極の内周の端部である。たとえば図1のトランジスタ31において、ゲート電極18aの外周端部は、電極18bと対向している端部である。またゲート電極18aの内周端部は、電極14aと対向している端部である。

なお環状である電極等の一部に切り欠きがあっても(たとえばU字状等であっても)、同様に外周端部、内周端部と表現する。

トランジスタのオフ電流の発生要因の一つとしては、寄生チャネルの発生が挙げられる。寄生チャネルとは意図しないキャリアの移動経路である。たとえば半導体膜の外周端部の側面が他の部分よりも低抵抗となり、当該領域にソースとドレインが電気的に接続されると、該低抵抗領域に寄生チャネルが発生しうる。つまりゲートと重畳する領域の半導体膜であって、ゲートとソース間の電圧に応じてソースとドレイン間の最短経路に形成されるチャネル(前者のチャネルともいう)と、寄生チャネル(後者のチャネルともいう)との2種のチャネルが形成されうることになる。

2種のチャネルが形成されうるトランジスタにおいては、多くの場合、それぞれのチャネルが形成されるゲートとソース間のしきい値電圧が異なる。典型的には、前者のチャネルが形成されるしきい値電圧は、後者のチャネルが形成されるしきい値電圧よりも高い。そして、前者のチャネルの電流駆動能力は、後者のチャネルの電流駆動能力よりも高い。よって、オフ状態にある当該トランジスタのゲートとソース間の電圧を上昇させていった場合、ソースとドレイン間の電流が2段階の変化をすることになる。具体的には、後者のチャネルが形成されるしきい値電圧の近傍において1段階目の変化(ソースとドレイン間の電流の増加)が確認され、さらに、前者のチャネルが形成されるしきい値電圧の近傍において2段階目の変化(ソースとドレイン間の電流の増加)が確認される。

従って、寄生チャネル(後者のチャネル)が形成されることで、トランジスタのしきい値電圧がマイナスにシフトし、オフ電流が増大するという問題が生じる。

そこで図1のようにドレイン電極(電極14a)の外周端部を、ゲート電極(ゲート電極18a)および半導体膜12aの外周端部の内側に位置させることで、ドレイン電極(電極14a)と、半導体膜12aの外周端部の側面とが接しない構造としている。そのため、半導体膜12aの側面が他の部分よりも低抵抗となってもトランジスタの特性は影響を受けない。これにより寄生チャネルの発生を防止し、トランジスタ31のしきい値電圧がマイナスにシフトすることを防止できる。そのため安定した電気的特性を有し、低消費電力なトランジスタを提供することができる。

しかしながら、ドレイン電極がゲート電極および半導体膜の外周端部の内側に設けられる構成とすることで、トランジスタ1つあたりの占有面積が広くなる恐れがある。

そこで、電極14bと電極18bの少なくとも一部を重畳して設ける構成とする。これにより、トランジスタ1つ分の面積にトランジスタおよび容量素子を設けることができる。したがって、オフ電流の低いトランジスタを有する半導体装置の集積度を向上させることができる。

またトランジスタ31と容量素子32で電極14bおよび絶縁膜16を共有させることで、トランジスタの作製と同じ工程数で、トランジスタ31と容量素子32を形成することができ、生産性高く作製可能な半導体装置を提供することができる。

<<半導体装置の構成材料>>

<基板10>

基板10に使用することができる基板に大きな制限はないが、少なくとも、半導体装置製造の際の加熱処理に耐えうる程度の耐熱性を有することが必要となる。例えば、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することもでき、これらの基板上に半導体素子が設けられたものを、基板10として用いてもよい。

また、基板10として、可撓性基板を用いてもよい。可撓性を有する半導体装置とするには、可撓性基板上に半導体膜12aを含むトランジスタ31を直接作製してもよいし、他の作製基板に半導体膜12aを含むトランジスタ31を作製し、その後、可撓性基板に剥離、転置してもよい。なお、作製基板から可撓性基板に剥離、転置するために、作製基板と半導体膜12aを含むトランジスタ31との間に剥離層(例えば、金属層や酸化タングステン層)を設けるとよい。

また基板10上に、下地膜として機能する絶縁膜を設けてもよい。絶縁膜としては、PECVD法またはスパッタリング法により、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ハフニウム、酸化ガリウムなどの酸化物絶縁材料、窒化シリコン、酸化窒化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁材料、またはこれらの混合材料を用いて、単層構造または積層構造で、設けることが出来る。

絶縁膜として例えば、窒化シリコン膜と酸化窒化シリコン膜との積層構造を用いることが好ましい。窒化シリコン膜を用いることにより、基板から金属や水素などが半導体膜12aに達することを抑制できる。

<半導体膜12a>

半導体膜12aとしては、シリコン(Si)、ゲルマニウム(Ge)、ヒ化ガリウム(GaAs)、リン化インジウム(InP)等を用いることができる。またシリコンよりもバンドギャップが広い窒化ガリウム(GaN)などの化合物半導体、酸化亜鉛(ZnO)などの金属酸化物でなる酸化物半導体などを用いてもよい。中でも酸化物半導体は、スパッタリング法や湿式法(印刷法など)により作製可能であり、量産性に優れるといった利点がある。さらに酸化物半導体は、安価で入手しやすいガラス基板上への成膜が可能であり、また集積回路上に、酸化物半導体による半導体素子を積層させることも可能である。また、基板の大型化にも対応が可能である。よって、上述した半導体の中でも、特に酸化物半導体は量産性が高いというメリットを有する。また、トランジスタの性能(例えば信頼性)を向上させるために結晶性の酸化物半導体を得ようとする場合でも、250℃から800℃の加熱処理によって結晶性の酸化物半導体を得ることができる。

本実施の形態では、半導体膜12aとして、酸化物半導体を用いることとする。

半導体膜12aに酸化物半導体を用いる場合、少なくともインジウム(In)または亜鉛(Zn)を含むことが好ましい。特にInおよびZnを含むことが好ましい。また、それらに加えて、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーを有することが好ましい。スタビライザーとしては、ガリウム(Ga)、スズ(Sn)、ハフニウム(Hf)およびアルミニウム(Al)の少なくともいずれかを有すればよい。

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種または複数種を有してもよい。

例えば、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物や、三元系金属の酸化物であるIn−Ga−Zn系酸化物、In−Sn−Zn系酸化物、In−Al−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物や、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物や、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物や、In−Ga系の材料、一元系金属の酸化物であるIn系酸化物、Sn系酸化物、Zn系酸化物などを用いることができる。

なお、ここで、例えば、In−Ga−Zn系酸化物とは、In、GaおよびZnを主成分として有する酸化物という意味であり、In、GaおよびZnの比率は問わない。

また、酸化物半導体として、InMO3(ZnO)m(m>0)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、In2SnO5(ZnO)n(n>0)で表記される材料を用いてもよい。

例えば、In:Ga:Zn=3:1:2、In:Ga:Zn=1:1:1またはIn:Ga:Zn=2:2:1の原子数比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いることができる。または、In:Sn:Zn=1:1:1、In:Sn:Zn=2:1:3またはIn:Sn:Zn=2:1:5の原子数比のIn−Sn−Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)の酸化物のrだけ近傍であるとは、a、b、cが、

(a―A)2+(b―B)2+(c―C)2≦r2

を満たすことをいう。rとしては、例えば、0.05とすればよい。他の酸化物でも同様である。

しかし、これらに限られず、必要とする半導体特性(電界効果移動度、しきい値電圧等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

酸化物半導体をチャネル領域に用いたトランジスタは、酸化物半導体を高純度化することにより、オフ電流(ここでは、オフ状態のとき、たとえばソース電位を基準としたときのゲート電位との電位差が0V以下またはしきい値電圧以下のときのドレイン電流とする)を十分に低くすることが可能である。例えば、加熱成膜により酸化物半導体にとって悪性の不純物である水素や水酸基を膜中に含ませないようにし、または成膜後の加熱により膜中から除去し、高純度化を図ることができる。高純度化されることにより、チャネル領域にIn−Ga−Zn系酸化物を用いたトランジスタで、チャネル長が10μm、半導体層の膜厚が30nm、ドレイン電圧が1V〜10V程度の範囲である場合、オフ電流を、1×10−13A以下とすることが可能である。またチャネル幅あたりのオフ電流(オフ電流をトランジスタのチャネル幅で除した値)を1×10−23A/μm(10yA/μm)から1×10−22A/μm(100yA/μm)程度とすることが可能である。

半導体膜12aは、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。

また、半導体膜12aは、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜であることが好ましい。

CAAC−OSは、例えば、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像で、結晶部を確認することができる場合がある。CAAC−OSに含まれる結晶部は、例えば、TEMによる観察像で、一辺100nmの立方体内に収まる大きさであることが多い。また、CAAC−OSは、TEMによる観察像で、結晶部と結晶部との境界を明確に確認できない場合がある。また、CAAC−OSは、TEMによる観察像で、粒界(グレインバウンダリーともいう。)を明確に確認できない場合がある。CAAC−OSは、例えば、明確な粒界を有さないため、不純物が偏析することが少ない。また、CAAC−OSは、例えば、明確な粒界を有さないため、欠陥準位密度が高くなることが少ない。また、CAAC−OSは、例えば、明確な粒界を有さないため、電子移動度の低下が小さい。

CAAC−OSは、例えば、複数の結晶部を有し、当該複数の結晶部においてc軸が被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃っている場合がある。そのため、CAAC−OSは、例えば、X線回折(XRD:X−Ray Diffraction)装置を用い、out−of−plane法による分析を行うと、2θが31°近傍のピークが現れる場合がある。2θが31°近傍のピークは、InGaZnO4の結晶であれば、(009)面に配向していることを示す。また、CAAC−OSは、例えば、2θが36°近傍のピークが現れる場合がある。2θが36°近傍のピークは、Ga2ZnO4の結晶であれば、(222)面に配向していることを示す。CAAC−OSは、好ましくは、2θが31°近傍にピークが現れ、2θが36°近傍にピークが現れない。

また、CAAC−OSは、例えば、異なる結晶部間で、それぞれa軸およびb軸の向きが揃っていない場合がある。例えば、InGaZnO4の結晶を有するCAAC−OSであれば、XRD装置を用い、c軸に垂直な方向からX線を入射させるin−plane法による分析を行うと、2θが56°近傍のピークが現れる場合がある。2θが56°近傍のピークは、InGaZnO4の結晶の(110)面を示す。ここで、2θを56°近傍で固定し、表面の法線ベクトルを軸(φ軸)として試料を回転させて分析(φスキャン)を行うと、a軸およびb軸の向きが揃っている単結晶酸化物半導体の場合は6つの対称性のピークが現れるが、CAAC−OSの場合は明瞭なピークが現れない。

このように、CAAC−OSは、例えば、c軸配向し、a軸または/およびb軸はマクロに揃っていない場合がある。

また、CAAC−OSは、例えば、電子線回折像で、スポット(輝点)が観測される場合がある。なお、特に、ビーム径が10nmφ以下、または5nmφ以下の電子線を用いて得られる電子線回折像を、極微電子線回折像と呼ぶ。

CAAC−OSに含まれる結晶部は、例えば、c軸がCAAC−OSの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃い、かつab面に垂直な方向から見て金属原子が三角形状または六角形状に配列し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、80°以上100°以下、好ましくは85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−10°以上10°以下、好ましくは−5°以上5°以下の範囲も含まれることとする。

また、CAAC−OSは、例えば、欠陥準位密度を低減することで形成することができる。酸化物半導体において、例えば、酸素欠損は欠陥準位である。酸素欠損は、トラップ準位となることや、水素を捕獲することによってキャリア発生源となることがある。CAAC−OSを形成するためには、例えば、酸化物半導体に酸素欠損を生じさせないことが重要となる。従って、CAAC−OSは、欠陥準位密度の低い酸化物半導体である。または、CAAC−OSは、酸素欠損の少ない酸化物半導体である。

不純物濃度が低く、欠陥準位密度の低い(酸素欠損の少ない)ことを高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる場合がある。従って、当該酸化物半導体をチャネル形成領域に用いたトランジスタは、しきい値電圧がマイナスとなる電気特性(ノーマリーオンともいう。)になることが少ない場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。従って、当該酸化物半導体をチャネル形成領域に用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる場合がある。なお、酸化物半導体のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体をチャネル形成領域に用いたトランジスタは、電気特性が不安定となる場合がある。

また、高純度真性または実質的に高純度真性であるCAAC−OSを用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

酸化物半導体は、例えば多結晶を有してもよい。なお、多結晶を有する酸化物半導体を、多結晶酸化物半導体と呼ぶ。多結晶酸化物半導体は複数の結晶粒を含む。

酸化物半導体は、例えば微結晶を有してもよい。なお、微結晶を有する酸化物半導体を、微結晶酸化物半導体と呼ぶ。

微結晶酸化物半導体は、例えば、TEMによる観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体に含まれる結晶部は、例えば、1nm以上100nm以下、または1nm以上10nm以下の大きさであることが多い。特に、例えば、1nm以上10nm以下の微結晶をナノ結晶(nc:nanocrystal)と呼ぶ。ナノ結晶を有する酸化物半導体を、nc−OS(nanocrystalline Oxide Semiconductor)と呼ぶ。また、nc−OSは、例えば、TEMによる観察像では、結晶部と結晶部との境界を明確に確認できない場合がある。また、nc−OSは、例えば、TEMによる観察像では、明確な粒界を有さないため、不純物が偏析することが少ない。また、nc−OSは、例えば、明確な粒界を有さないため、欠陥準位密度が高くなることが少ない。また、nc−OSは、例えば、明確な粒界を有さないため、電子移動度の低下が小さい。

nc−OSは、例えば、微小な領域(例えば、1nm以上10nm以下の領域)において原子配列に周期性を有する場合がある。また、nc−OSは、例えば、結晶部と結晶部との間で規則性がないため、巨視的には原子配列に周期性が見られない場合、または長距離秩序が見られない場合がある。従って、nc−OSは、例えば、分析方法によっては、非晶質酸化物半導体と区別が付かない場合がある。nc−OSは、例えば、XRD装置を用い、結晶部よりも大きいビーム径のX線でout−of−plane法による分析を行うと、配向を示すピークが検出されない場合がある。また、nc−OSは、例えば、結晶部よりも大きいビーム径(例えば、20nmφ以上、または50nmφ以上)の電子線を用いる電子線回折像では、ハローパターンが観測される場合がある。また、nc−OSは、例えば、結晶部と同じか結晶部より小さいビーム径(例えば、10nmφ以下、または5nmφ以下)の電子線を用いる極微電子線回折像では、スポットが観測される場合がある。また、nc−OSの極微電子線回折像は、例えば、円を描くように輝度の高い領域が観測される場合がある。また、nc−OSの極微電子線回折像は、例えば、当該領域内に複数のスポットが観測される場合がある。

nc−OSは、微小な領域において原子配列に周期性を有する場合があるため、非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、nc−OSは、結晶部と結晶部との間で規則性がないため、CAAC−OSと比べて欠陥準位密度が高くなる。

なお、酸化物半導体が、CAAC−OS、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体の二種以上を有する混合膜であってもよい。混合膜は、例えば、非晶質酸化物半導体の領域、微結晶酸化物半導体の領域、多結晶酸化物半導体の領域、CAAC−OSの領域、のいずれか二種以上の領域を有する場合がある。また、混合膜は、例えば、非晶質酸化物半導体の領域、微結晶酸化物半導体の領域、多結晶酸化物半導体の領域、CAAC−OSの領域、のいずれか二種以上の領域の積層構造を有する場合がある。

なお、本実施の形態では、半導体膜12aがCAAC−OS膜であるとして説明を行うが、単結晶、多結晶(ポリクリスタルともいう)、または非晶質であってもよい。

半導体膜12aとして酸化物半導体を用いる場合、チャネル形成領域は、水又は水素などの不純物が低減され、かつ酸素欠損が低減されることで高純度化された領域であることが好ましい。高純度化された酸化物半導体(purified OS)は、i型(真性半導体)またはi型に限りなく近い。そのため、上記酸化物半導体をチャネル形成領域に用いたトランジスタは、オフ電流が著しく低く、しきい値電圧のマイナス方向のシフトが少ない(すなわちノーマリオフの特性が得られやすい)という特性を有する。

具体的に、半導体膜12aのチャネル形成領域は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)による水素濃度の測定値が、5×1018/cm3未満、より好ましくは5×1017/cm3以下、更に好ましくは1×1016/cm3以下とすることが好ましい。また、ホール効果測定により測定できる酸化物半導体膜のキャリア密度は、1×1014/cm3未満、好ましくは1×1012/cm3未満、更に好ましくは1×1011/cm3未満とすることが好ましい。また、酸化物半導体のバンドギャップは、2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。不純物濃度が十分に低減され、かつ酸素欠損が低減されることで高純度化された酸化物半導体をチャネルが形成される領域に用いることにより、トランジスタのオフ電流を下げ、しきい値電圧のマイナス方向のシフトを少なくする(すなわちノーマリオフの特性を得る)ことができる。

半導体膜12aにおいて、水素や酸素欠損が低減されていることにより、キャリアの発生を抑制することができる。キャリア密度が高まることを抑制することで、しきい値電圧のマイナス方向のシフトを小さくすることができる。なお半導体膜12aの端部では酸素が脱離しやすいため、キャリア密度が高まりやすい。

そこで、本発明の一態様では、図1に示すように、ドレイン電極として機能する電極14aの外周端部を、ゲート電極18aの外周端部の内側に位置させることで、ドレイン電極として機能する14aと、半導体膜12aの外周端部の側面とが接しない構造としている。そのため、半導体膜12aの外周端部の影響を受けない。その結果、トランジスタ31のしきい値電圧がマイナスにシフトすることを防止できる。

また半導体膜12aとして酸化物半導体を用いる場合は、下地膜として熱が与えられることにより酸素を放出する絶縁膜を設けることが好ましい。酸化物半導体と、熱が与えられることにより酸素を放出する絶縁膜とを接して設けることにより、加熱処理の際に、絶縁膜から酸素を放出し酸化物半導体に拡散(又は供給)させることができる。これにより、酸化物半導体の酸素欠損密度を低減することができる。また絶縁膜及び酸化物半導体の界面準位を低減することができる。この結果、トランジスタの動作などに起因して生じうる電荷などが、絶縁膜及び酸化物半導体の界面に捕獲されることを抑制することができるため、しきい値電圧がマイナス方向へシフトすることを抑制することができる。

熱が与えられることにより酸素を放出する絶縁膜としては、化学量論比を満たす酸素よりも多くの酸素を含む絶縁膜を用いることが好ましい。絶縁膜として、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化ハフニウム、酸化イットリウム等を用いることができる。

また、半導体膜12aとゲート絶縁層108aとの界面は、平坦であることが好ましい。界面が平坦であると、界面状態がよいためトランジスタの特性が向上する。たとえば、JIS B 0601:2001の算術平均粗さ(Ra)が0.2nm以下であることが好ましい。

<電極14a、電極14b>

ドレイン電極として機能する電極14a、ソース電極として機能する電極14bとして、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いることができる。また電極14a、電極14bは、酸化インジウム酸化スズ、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウムスズ酸化物、酸化インジウム酸化亜鉛、酸化ケイ素を添加したインジウムスズ酸化物などの導電性材料を用いることもできる。また、電極14a、電極14bは、上記の導電材料を用いて、単層構造または積層構造とすることができる。

電極14a、電極14bを単層構造とする場合は、例えば、膜厚100nmのタングステン膜を用いればよい。

電極14a、電極14bを2層の積層構造とする場合は、例えば、膜厚30nmの窒化タンタル膜と膜厚200nmの銅膜の積層構造とすればよい。銅膜を用いることにより、配線抵抗を低減することができる。また膜厚30nmの窒化タンタル膜に代えて、タングステン膜、窒化タングステン膜、窒化モリブデン膜、窒化チタン膜を用いてもよい。また膜厚200nmの銅膜に代えて、タングステン膜を用いてもよい。

また電極14a、電極14bを3層の積層構造とする場合は、例えば、膜厚30nmの窒化タンタル膜、膜厚200nmの銅膜、膜厚30nmのタングステン膜を用いればよい。また、膜厚30nmの窒化タンタル膜に代えて、タングステン膜、窒化タングステン膜、窒化モリブデン膜、窒化チタン膜を用いてもよい。また、膜厚30nmのタングステン膜に代えて、モリブデン膜を用いてもよい。銅膜を用いることにより、配線抵抗を低減することができる。また、銅膜上に、タングステン膜またはモリブデン膜を積層することで、銅が達することを抑制できる。

<絶縁膜16>

ゲート絶縁膜として機能する絶縁膜16としては、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ハフニウム、酸化ガリウムなどの酸化物絶縁材料、窒化シリコン、酸化窒化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁材料、またはこれらの混合材料を用いて、単層構造または積層構造で、設けることが出来る。また半導体膜12aとして酸化物半導体を用いる場合は、絶縁膜16として熱が与えられることにより酸素を放出する絶縁膜を用いることが好ましい。

<ゲート電極18a、電極18b>

ゲート電極18a、容量素子電極として機能する電極18bとしては、電極14a、電極14bと同様の材料を用いることができる。

なおタングステン膜またはモリブデン膜は、仕事関数が比較的高いため、ゲート電極として用いると、トランジスタのしきい値電圧がプラスになりやすい(すなわちノーマリオフのトランジスタとしやすい)ため、好適である。なお絶縁膜16によって、銅が半導体膜12に達することを防止することができれば、タングステン膜およびモリブデン膜は形成しなくともよい。

なお図示しないが、トランジスタ31および容量素子32上に絶縁膜を設けることが好ましい。絶縁膜は、1つの工程で形成してもよいし、複数の工程を経て形成してもよい。また異なる材料からなる膜を積層させてもよい。絶縁膜の材料としては、絶縁膜16と同様の材料を用いることができる。

(実施の形態2)

本実施の形態では、実施の形態1と異なる半導体装置の一形態の構成について、図2乃至図6を参照して説明する。

図2(A−1)はトランジスタ31および容量素子32の平面図であり、図2(A−2)は図2(A−1)の一点鎖線A−Bの断面図、図2(A−3)は図2(A−1)の一点鎖線C−Dの断面図である。なお、図2(A−1)では煩雑になることを避けるために、トランジスタ31および容量素子32の構成要素の一部(例えば、絶縁膜16など)を省略して図示する。

実施の形態1の図1の半導体装置と、図2の半導体装置の主な相違点は、図2では半導体膜12aが不純物添加領域12a1を有する点である。不純物添加領域12a1は、半導体膜12aの導電率を変化させる不純物を有する領域であり、ゲート電極18a、電極14aおよび電極14bのいずれとも重畳しない領域に設けられる。

不純物添加領域12a1を設けることにより、該領域がトランジスタ31のLDD領域として機能する。LDD領域を設けることにより、ドレイン電極端部における電界集中を緩和し、ホットキャリア劣化を防ぐことができる。また、ソース電極端部において、ドレイン電極端部からの電界の影響が小さくなるため、DIBLによるパンチスルー現象を抑制できる。

なお、半導体膜12aのうち、不純物が添加された領域(不純物添加領域12a1)は結晶構造が乱れ、非晶質状態になりやすい。このため、半導体膜12aとしてCAAC−OS膜などの結晶性を有する膜を用い、当該膜に対して不純物を添加した場合、チャネル形成領域はCAAC−OS膜の状態を保ち、不純物添加領域12a1は非晶質状態の酸化物半導体膜(または、非晶質状態を多く含む酸化物半導体膜。)になりやすい。

非晶質状態の酸化物半導体膜(または、非晶質状態を多く含む酸化物半導体膜。)は、接して設けられたCAAC−OS膜などの結晶性を有する酸化物半導体膜に含まれる水素などのドナーとなる不純物をゲッタリングしやすい。このため、チャネル形成領域から不純物添加領域12a1に水素などのドナーとなる不純物がゲッタリングされトランジスタ31の電気的特性を良好なものとすることができる。

なお、不純物としては、15族元素(代表的にはリン(P)、砒素(As)、アンチモン(Sb))、ホウ素(B)、アルミニウム(Al)、窒素(N)、アルゴン(Ar)、ヘリウム(He)、ネオン(Ne)、インジウム(In)、フッ素(F)、塩素(Cl)、チタン(Ti)、及び亜鉛(Zn)のいずれかから選択される一以上を用いることができる。イオン注入法は、必要なイオンのみを取り出す質量分離器を用いているため、対象物に対して不純物のみを選択的に添加できる。このため、イオンドーピング法を用いて添加した場合と比べて半導体膜12a中への不純物(例えば水素など)の混入が少なくなるため好ましい。ただし、イオンドーピング法を除外するものではない。

図3(A−1)はトランジスタ31および容量素子32の平面図であり、図3(A−2)は図3(A−1)の一点鎖線A−Bの断面図、図3(A−3)は図3(A−1)の一点鎖線C−Dの断面図である。なお、図3(A−1)では煩雑になることを避けるために、トランジスタ31および容量素子32の構成要素の一部(例えば、絶縁膜16など)を省略して図示する。

実施の形態1の図1の半導体装置と、図3の半導体装置の主な相違点はドレイン電極およびソース電極の配置である。図1ではドレイン電極およびソース電極として機能する電極14aおよび電極14bが半導体膜12a上に設けられていたのに対して、図2ではドレイン電極およびソース電極として機能する電極20aおよび電極20bは半導体膜12aの下に設けられている。

このような構成としても、寄生チャネルの発生を防止し、トランジスタ31のしきい値電圧がマイナスにシフトすることを防止できる。またソース電極として機能する電極14bと容量素子電極として機能する電極18bを重畳して設けるため、半導体装置の集積度を向上させることができる。

図4(A−1)はトランジスタ31および容量素子32の平面図であり、図4(A−2)は図4(A−1)の一点鎖線A−Bの断面図、図4(A−3)は図4(A−1)の一点鎖線C−Dの断面図である。なお、図4(A−1)では煩雑になることを避けるために、トランジスタ31および容量素子32の構成要素の一部(例えば、絶縁膜16など)を省略して図示する。

実施の形態1の図1の半導体装置と、図4の半導体装置の主な相違点はゲート電極の配置である。図1ではゲート電極18aが半導体膜12a上に設けられていたのに対して、図4ではゲート電極22aは半導体膜12aの下に設けられている。また、図4の容量素子32は、電極18bと、絶縁膜23と、電極14aとを有している。

このような構成としても、これにより寄生チャネルの発生を防止し、トランジスタ31のしきい値電圧がマイナスにシフトすることを防止できる。そのためオフ電流が低く、安定した電気的特性を有し、低消費電力なトランジスタを提供することができる。また電極14bと電極18bとを重畳して設ける構成とすることで、オフ電流の低いトランジスタを有する半導体装置の集積度を向上させることができる。

なお図4の半導体装置ではゲート電極22aと容量素子電極として機能する電極18bを異なる導電層からなる構成としたが、これに限らない。ゲート電極と容量素子電極として機能する電極が同一層かつ同一材料からなる構成としてもよい。このような構成とすることで、生産性高く作製可能な半導体装置を提供することができる。

図5(A−1)はトランジスタ31および容量素子32の平面図であり、図5(A−2)は図5(A−1)の一点鎖線A−Bの断面図、図5(A−3)は図5(A−1)の一点鎖線C−Dの断面図である。なお、図5(A−1)では煩雑になることを避けるために、トランジスタ31および容量素子32の構成要素の一部(例えば、絶縁膜16など)を省略して図示する。

実施の形態1の図1の半導体装置と、図5の半導体装置の主な相違点は半導体膜12aの形状である。図1では半導体膜12aの外周端部が電極14bと接して設けられているのに対して、図5では半導体膜12aは電極14bより外側にも設けられている。

このような構成としても、寄生チャネルの発生を防止し、トランジスタ31のしきい値電圧がマイナスにシフトすることを防止できる。そのためオフ電流が低く、安定した電気的特性を有し、低消費電力なトランジスタを提供することができる。またソース電極として機能する電極14bと容量素子電極として機能する電極18bを重畳して設けるため、オフ電流の低いトランジスタを有する半導体装置の集積度を向上させることができる。

図6(A−1)はトランジスタ31および容量素子32の平面図であり、図6(A−2)は図6(A−1)の一点鎖線A−Bの断面図、図6(A−3)は図6(A−1)の一点鎖線C−Dの断面図である。なお、図6(A−1)では煩雑になることを避けるために、トランジスタ31および容量素子32の構成要素の一部(例えば、絶縁膜16など)を省略して図示する。

実施の形態1の図1の半導体装置と、図6の半導体装置の主な相違点は電極14bおよび電極18bの配置および形状である。図1ではゲート電極18aを囲うように電極14bおよび電極18bが設けられていたのに対して、図6ではゲート電極18aの一辺と対向して電極14bおよび電極18bが設けられている。

このような構成としても、寄生チャネルの発生を防止し、トランジスタ31のしきい値電圧がマイナスにシフトすることを防止できる。またソース電極として機能する電極14bと容量素子電極として機能する電極18bを重畳して設けるため、オフ電流の低いトランジスタを有する半導体装置の集積度を向上させることができる。

なお、図1乃至図6ではゲート電極18aまたはゲート電極22aは、ソース電極として機能する電極およびドレイン電極として機能する電極と重畳しない構成、すなわちオフセット領域またはLDD領域を有する構成について説明した。しかし電極が、絶縁膜を介してソース電極として機能する電極およびドレイン電極として機能する電極と重畳する構成としてもよい。

また図1乃至図6ではゲート電極、ドレイン電極およびソース電極として機能する電極が矩形のトランジスタについて説明したが、これらの構成要素はそれぞれ円形等、他の形状であってもよい。

また、図1乃至図6のトランジスタの特徴を組み合わせて有するトランジスタとしてもよい。

(実施の形態3)

本実施の形態では、本発明の一態様に係る記憶素子の一例について図1(B)および図7を参照して説明する。

図1(B)のトランジスタ31と容量素子32はDRAM(Dynamic Random Access Memory)の記憶素子として用いることができる。DRAMは、記憶素子を構成するトランジスタを選択して容量素子に電荷を蓄積することで、情報を記憶する。

DRAMの記憶素子に用いる場合、トランジスタ31の半導体膜には酸化物半導体を用いることが好ましい。酸化物半導体を用いることで、オフ電流が極めて小さいトランジスタとすることができる。このため、トランジスタ31をオフ状態とすると容量素子32に与えられた電荷を長期間にわたって保持することができる。そのためリフレッシュ動作の頻度を極めて低くし、消費電力をより低減することが可能である。

すなわちトランジスタ31および容量素子32を用いて、実質的に不揮発性のランダムアクセスメモリを実現することが可能となる。

ところで、不揮発性のランダムアクセスメモリとして磁気トンネル接合素子(MTJ素子)が知られている。MTJ素子は、絶縁膜を介して上下に配置している膜中のスピンの向きが平行であれば低抵抗状態、反平行であれば高抵抗状態となることで情報を記憶する素子である。したがって、本実施の形態で示す酸化物半導体を用いたメモリとは原理が全く異なっている。表1はMTJ素子と、本実施の形態に係る半導体装置との対比を示す。

MTJ素子は磁性材料を使用するためキュリー温度以上にすると磁性が失われてしまうという欠点がある。また、MTJ素子は電流駆動であるため、シリコンのバイポーラデバイスと相性が良いが、バイポーラデバイスは集積化に不向きである。そして、MTJ素子は書き込み電流が微小とはいえメモリの大容量化によって消費電力が増大してしまうといった問題がある。

また、MTJ素子は、1セルあたりの書き込み電流が50μA〜500μAと言われているが、本実施の形態に係る半導体装置では、容量素子への電荷の供給によりデータの待避を行っているので、データの書き込みに要する電流をMTJ素子の1/100程度に抑えることができる。そのため、本発明の一態様に係る半導体装置ではより消費電力を低減することができる。

また、原理的にMTJ素子は磁界耐性に弱く強磁界にさらされるとスピンの向きが狂いやすい。また、MTJ素子に用いる磁性体のナノスケール化によって生じる磁化揺らぎを制御する必要がある。

さらに、MTJ素子は希土類元素を使用するため、MTJ素子はビット当たりの材料コストから見ても高価であると考えられる。

一方、本実施の形態で示す酸化物半導体を用いたトランジスタは、チャネルを形成する半導体材料が金属酸化物であること以外は、素子構造や動作原理がシリコンMOSFETと同様である。また、酸化物半導体を用いたトランジスタは磁界の影響を受けず、ソフトエラーも生じ得ないといった特質を有する。このことからシリコン集積回路と非常に整合性が良いといえる。

次に図7を用いて、図1(B)と異なる記憶素子の一例を示す。

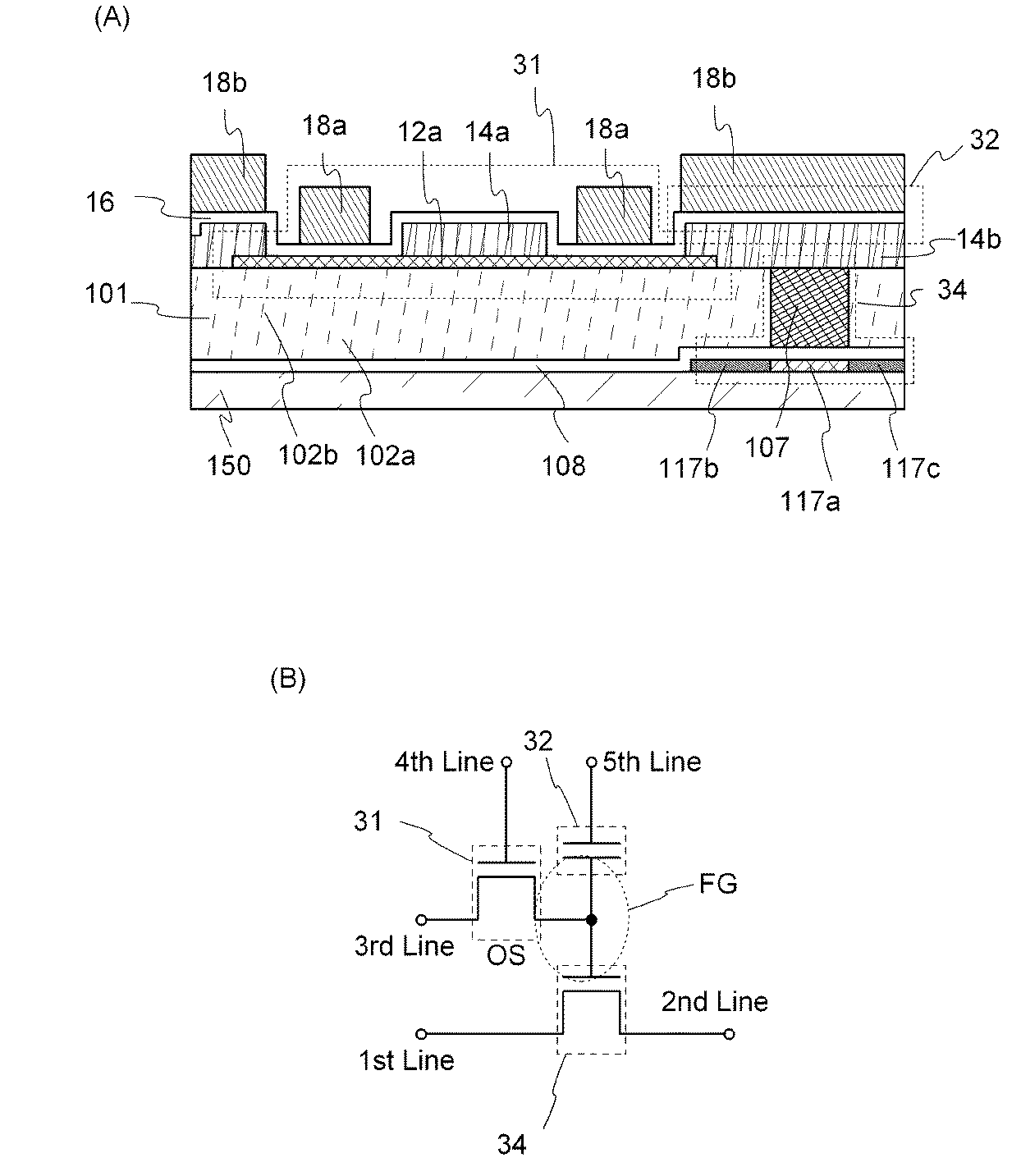

図7(A)は、本発明の一態様に係る記憶素子の断面図、図7(B)はその回路図である。図7に示す記憶素子はトランジスタ31、容量素子32およびトランジスタ34を有する。トランジスタ31と容量素子32には、実施の形態1および実施の形態2で示したトランジスタおよび容量素子を適用することができる。

図7(A)に示すように、半導体膜12a、絶縁膜16、電極14a、電極14b、ゲート電極18aでトランジスタ31を構成する。また電極14b、絶縁膜16、電極18bで容量素子32を構成する。またチャネル形成領域117a、ドレイン電極117b、ソース電極117c、ゲート絶縁膜108、ゲート電極107でトランジスタ34を構成する。

また図7(B)に示すように、本発明の一態様に係る記憶素子は第1の配線(1st Line)とトランジスタ34のソース電極またはドレイン電極117bとは、電気的に接続され、第2の配線(2nd Line)とトランジスタ34のドレイン電極またはソース電極117cとは、電気的に接続されている。また、第3の配線(3rd Line)とトランジスタ31のドレイン電極として機能する電極14aとは、電気的に接続され、第4の配線(4th Line)と、トランジスタ31のゲート電極18aとは、電気的に接続されている。そして、トランジスタ34のゲート電極107と、トランジスタ31のソース電極として機能する電極14b電気的に接続され、また電極14bは容量素子32の電極の一方を兼ねている。また第5の配線(5th Line)と、容量素子32の電極の他方として機能する18bは電気的に接続されている。

ここでトランジスタ31の半導体膜には酸化物半導体を用いることが好ましい。酸化物半導体を用いることでオフ電流が極めて小さいトランジスタとすることができる。このため、トランジスタ31をオフ状態とすることで、トランジスタ34のゲート電極の電位を極めて長期間にわたって保持することが可能である。そして、容量素子32を有することにより、トランジスタ34のゲート電極に与えられた電位の保持が容易になり、また、保持されたデータの読み出しが容易になる。

トランジスタ34は、基板150上に、チャネル形成領域117a、ソース電極またはドレイン電極117b、ドレイン電極またはソース電極117cを有する半導体膜と、ゲート絶縁膜108と、ゲート電極107とを有する。またトランジスタ34の周囲には絶縁膜101が設けられている。

なお、トランジスタ34としては、チャネルの導電型とその半導体材料については特に限定されない。トランジスタのチャネルの導電型については、pチャネル型を用いると、低電位を用いずに読み出しを行うことができるため、低電位を生成する周辺回路が不要となる。一方、nチャネル型を用いると、高速な読み出しが可能となる。半導体材料については、データの読み出し速度を向上させるという観点からは、例えば、単結晶シリコンを用いたトランジスタなど、スイッチング速度の高いトランジスタを適用するのが好適である。

本実施の形態で示す半導体装置においては、ノードFGが、フラッシュメモリ等のフローティングゲート型トランジスタのフローティングゲートと同等の作用をするが、本実施の形態のノードFGは、フラッシュメモリ等のフローティングゲートと本質的に異なる特徴を有している。

フラッシュメモリでは、コントロールゲートに印加される電位が高いため、その電位が、隣接するセルのフローティングゲートに影響を与えないように、セルとセルとの間隔をある程度保つ必要が生じる。このことは、半導体装置の高集積化を阻害する要因の一つである。そして、当該要因は、高電圧をかけてトンネル電流を発生させるというフラッシュメモリの根本的な原理に起因するものである。

一方、本実施の形態に係る半導体装置は、トランジスタ31のスイッチングによって動作し、上述のようなトンネル電流による電荷注入の原理を用いない。すなわち、フラッシュメモリのような、電荷を注入するための高電圧が不要である。これにより、隣接セルに対する、コントロールゲートによる高電圧の影響を考慮する必要がないため、高集積化が容易になる。

また、高電界が不要であり、大型の周辺回路(昇圧回路など)が不要である点も、フラッシュメモリに対するアドバンテージである。例えば、本実施の形態に係るメモリセルに印加される電圧(メモリセルの各端子に同時に印加される電位の最大のものと最小のものの差)の最大値は、2段階(1ビット)のデータを書き込む場合、一つのメモリセルにおいて、5V以下、好ましくは3V以下とすることができる。

(実施の形態4)

本実施の形態では、本発明の一態様に係る半導体回路について説明する。なお、半導体回路に設けられるトランジスタおよび容量素子には、先の実施の形態で示したトランジスタおよび容量素子を適用することができる。先の実施の形態で示したトランジスタおよび容量素子は、安定した電気的特性を有し、低消費電力であるため、半導体回路の信頼性を高め消費電力を低減することができる。

図8に本発明の一態様に係る半導体回路の構成例として、nチャネル型トランジスタを用いて構成されたバッファ回路100を示す。

図8に示すバッファ回路200は、第1乃至第6のトランジスタと容量素子を有し、第1のトランジスタ201では、第1端子及び第3端子は、高電位側の電源線Vddに接続され、第2端子は、第2のトランジスタ202の第1端子及び第3のトランジスタ203の第3端子に接続され、第2のトランジスタ202では、第2端子は、低電位側の電源線Vssに接続され、第3端子は、バッファ回路200の入力部Vinに接続され、第3のトランジスタ203では、第1端子は、高電位側の電源線Vddに接続され、第2端子は、第4のトランジスタ204の第1端子及び第5のトランジスタ205の第3端子に接続され、第4のトランジスタ204では、第2端子は、低電位側の電源線Vssに接続され、第3端子は、バッファ回路200の入力部Vinに接続され、第5のトランジスタ205では、第1端子は、高電位側の電源線Vddに接続され、第2端子は、第6のトランジスタ206の第1端子及びバッファ回路200の出力部Voutに接続され、第6のトランジスタ206では、第2端子は、低電位側の電源線Vssに接続され、第3端子は、バッファ回路200の入力部Vinに接続され、第1のトランジスタ201の第2端子は、容量素子207を介して出力部Voutに接続されている。

図8に示すバッファ回路200は、駆動能力が高く、高周波成分の利得を大きくすることができる。更には、このようなバッファ回路は、スルーレートも高いものとなる。更には、同一極性のトランジスタにより構成することが可能なため、簡略な工程により作製することができる。

また、例えばトランジスタ206および容量素子207として、先の実施の形態のトランジスタおよび容量素子を適用することができる。これにより低消費電力で、専有面積の小さなバッファ回路とすることができる。

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

(実施の形態5)

本実施の形態では、本発明の一態様に係る半導体回路について説明する。なお、半導体回路に設けられるトランジスタおよび容量素子には、先の実施の形態で示したトランジスタおよび容量素子を適用することができる。先の実施の形態で示したトランジスタおよび容量素子は、安定した電気的特性を有し、低消費電力であるため、半導体回路の信頼性を高め消費電力を低減することができる。

図9に本発明の一態様に係る半導体回路の構成例として、記憶素子300を示す。記憶素子300は、記憶回路301と、記憶回路302と、スイッチ303と、スイッチ304と、スイッチ305と、論理値を反転させる論理素子306と、容量素子307と、を有する。記憶回路301は、電源電圧が供給されている期間のみデータを保持する。記憶回路302は、容量素子308と、トランジスタ309と、トランジスタ310と、を有する。

なお、記憶素子300は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の回路素子をさらに有していても良い。

例えばトランジスタ309および容量素子308に、先の実施の形態のトランジスタおよび容量素子を適用することができる。これにより低消費電力で、集積度の高いバッファ回路とすることができる。

図9では、スイッチ303は、一導電型(例えば、nチャネル型)のトランジスタ313を用いて構成され、スイッチ304は、一導電型とは異なる導電型(例えば、pチャネル型)のトランジスタ314を用いて構成した例を示す。ここで、スイッチ303の第1の端子はトランジスタ313のソースとドレインの一方に対応し、スイッチ303の第2の端子はトランジスタ313のソースとドレインの他方に対応し、スイッチ303はトランジスタ313のゲートに入力される制御信号S2によって、第1の端子と第2の端子の間の導通または非導通(つまり、トランジスタ313のオン状態またはオフ状態)が選択される。スイッチ304の第1の端子はトランジスタ314のソースとドレインの一方に対応し、スイッチ304の第2の端子はトランジスタ314のソースとドレインの他方に対応し、スイッチ304はトランジスタ314のゲートに入力される制御信号S2によって、第1の端子と第2の端子の間の導通または非導通(つまり、トランジスタ314のオン状態またはオフ状態)が選択される。

トランジスタ309のソースとドレインの一方は、容量素子308の一対の電極のうちの一方、及びトランジスタ310のゲートと電気的に接続される。ここで、接続部分をノードM2とする。トランジスタ310のソースとドレインの一方は、電位V1が与えられる電源線に電気的に接続され、他方は、スイッチ303の第1の端子(トランジスタ313のソースとドレインの一方)と電気的に接続される。スイッチ303の第2の端子(トランジスタ313のソースとドレインの他方)はスイッチ304の第1の端子(トランジスタ314のソースとドレインの一方)と電気的に接続される。スイッチ304の第2の端子(トランジスタ314のソースとドレインの他方)は電位V2が与えられる電源線と電気的に接続される。スイッチ303の第2の端子(トランジスタ313のソースとドレインの他方)と、スイッチ304の第1の端子(トランジスタ314のソースとドレインの一方)と、論理値を反転させる論理素子306の入力端子と、容量素子307の一対の電極のうちの一方と、は電気的に接続される。ここで、接続部分をノードM1とする。容量素子307の一対の電極のうちの他方は、一定の電位が入力される構成とすることができる。例えば、低電源電位(接地電位等)または高電源電位が入力される構成とすることができる。容量素子307の一対の電極のうちの他方は、電位V1が与えられる電源線と電気的に接続されていてもよい。容量素子308の一対の電極のうちの他方は、一定の電位が入力される構成とすることができる。例えば、低電源電位(接地電位等)または高電源電位が入力される構成とすることができる。容量素子308の一対の電極のうちの他方は、電位V1が与えられる電源線と電気的に接続されていてもよい。図9では、容量素子307の一対の電極のうちの他方、及び容量素子308の一対の電極のうちの他方は、電位V1が与えられる電源線と電気的に接続されている例を示す。

なお、容量素子307は、トランジスタの寄生容量等を積極的に利用することによって省略することも可能である。容量素子308は、トランジスタの寄生容量等を積極的に利用することによって省略することも可能である。

トランジスタ309のゲートには、制御信号S1が入力される。スイッチ303及びスイッチ304は、制御信号S1とは異なる制御信号S2によって第1の端子と第2の端子の間の導通状態または非導通状態を選択され、一方のスイッチの第1の端子と第2の端子の間が導通状態のとき他方のスイッチの第1の端子と第2の端子の間は非導通状態となる。スイッチ305は、制御信号S1及び制御信号2とは異なる制御信号S3によって第1の端子と第2の端子の間の導通状態または非導通状態を選択される。

トランジスタ309のソースとドレインの他方には、記憶回路301に保持されたデータに対応する信号が入力される。図9では、記憶回路301の出力端子(図9中、OUTと記載)から出力された信号が、トランジスタ309のソースとドレインの他方に入力される例を示した。スイッチ303の第2の端子(トランジスタ313のソースとドレインの他方)から出力される信号は、論理値を反転させる論理素子306によってその位相が反転された反転信号となり、制御信号S3によって第1の端子と第2の端子間が導通状態となったスイッチ305を介して記憶回路301に入力される。

なお、図9では、スイッチ303の第2の端子(トランジスタ313のソースとドレインの他方)から出力される信号は、論理値を反転させる論理素子306及びスイッチ305を介して記憶回路301の入力端子(図9中、INと記載)に入力する例をしめしたがこれに限定されない。スイッチ303の第2の端子(トランジスタ313のソースとドレインの他方)から出力される信号が、位相を反転させられることなく、記憶回路301に入力されてもよい。例えば、記憶回路301内に、入力端子から入力された信号の位相が反転した信号が保持されるノードが存在する場合に、スイッチ303の第2の端子(トランジスタ313のソースとドレインの他方)から出力される信号を当該ノードに入力することができる。

図9において、電位V1と電位V2の電位差に相当する電圧が、電源電圧として記憶素子300に供給されている。記憶回路301には電位V1と電位V2の電位差に相当する電圧が、電源電圧として供給されていてもよい。記憶回路301に電源電圧が供給されない期間では、電位V1と電位V2の電位差を(実質的に)無くすことができる。

なお、スイッチ305は、トランジスタを用いて構成することができる。当該トランジスタはnチャネル型トランジスタであってもよいし、pチャネル型トランジスタであってもよい。また、nチャネル型トランジスタとpチャネル型トランジスタを組み合わせて用いてもよい。例えば、スイッチ305は、アナログスイッチとすることができる。

図9において、トランジスタ309は、酸化物半導体層を挟んで上下に2つのゲートを有するトランジスタとすることもできる。一方のゲートに制御信号S1を入力し、他方のゲートには、制御信号S4を入力することができる。制御信号S4は、一定の電位の信号であってもよい。一定の電位は、電位V1や電位V2であってもよい。なお、酸化物半導体層を挟んで上下に設けられた2つのゲートを電気的に接続し、制御信号S1を入力してもよい。トランジスタ309の他方のゲートに入力される信号によって、トランジスタ309のしきい値電圧を制御することができる。例えば、トランジスタ309のオフ電流を更に低減することもできる。

図9において、記憶素子300に用いられるトランジスタのうち、トランジスタ309以外のトランジスタは、酸化物半導体以外の半導体でなる層または基板にチャネルが形成されるトランジスタとすることができる。例えば、シリコン層またはシリコン基板にチャネルが形成されるトランジスタとすることができる。また、記憶素子300に用いられるトランジスタ全てを、チャネルが酸化物半導体層に形成されるトランジスタとすることもできる。または、記憶素子300は、トランジスタ309以外にも、チャネルが酸化物半導体層に形成されるトランジスタを含んでいてもよく、残りのトランジスタは酸化物半導体以外の半導体でなる層または基板にチャネルが形成されるトランジスタとすることもできる。

図9における記憶回路301は、第1の論理値を反転させる論理素子及び第2の論理値を反転させる論理素子を有し、第1の論理値を反転させる論理素子の入力端子は第2の論理値を反転させる論理素子の出力端子と電気的に接続され、第2の論理値を反転させる論理素子の入力端子は第1の論理値を反転させる論理素子の出力端子と電気的に接続された構成を用いることができる。第1の論理値を反転させる論理素子及び第2の論理値を反転させる論理素子は、それぞれ電源電位が供給されている期間のみ、入力された信号に対応する信号を出力する。

また、論理値を反転させる論理素子としては、例えばインバータやクロックドインバータ等を用いることができる。

記憶素子300では、電源電圧が供給されない間は、揮発性のメモリに相当する記憶回路301に記憶されていたデータを、記憶回路302に設けられた容量素子308によって保持することができる。

また、トランジスタ309の半導体膜として酸化物半導体を用いた場合、トランジスタ309のオフ電流を、例えば結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて極めて小さくすることができる。そのため、記憶素子300に電源電圧が供給されない間も容量素子308に保持された信号は長期間にわたり保たれる。こうして、記憶素子300は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。

また、スイッチ303及びスイッチ304を設けることによって、上記プリチャージ動作を行うことを特徴とする記憶素子であるため、電源電圧供給再開後に、記憶回路301が元のデータを保持しなおすまでの時間を短くすることができる。

また、記憶回路302において、容量素子308によって保持された信号はトランジスタ310のゲートに入力される。そのため、記憶素子300への電源電圧の供給が再開された後、容量素子308によって保持された信号を、トランジスタ310の状態(オン状態、またはオフ状態)に変換して、記憶回路302から読み出すことができる。それ故、容量素子308に保持された信号に対応する電位が多少変動していても、元の信号を正確に読み出すことが可能である。

このような記憶素子300を、信号処理回路が有するレジスタやキャッシュメモリなどの記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。よって、信号処理回路全体、もしくは信号処理回路を構成する一または複数の論理回路において、短い時間でも電源停止を行うことができるため、消費電力を抑えることができる信号処理回路、消費電力を抑えることができる当該信号処理回路の駆動方法を提供することができる。

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

(実施の形態6)

本実施の形態では、本発明の一態様に係る表示装置について説明する。

<EL素子を用いた表示装置の例>

まず図10および図11を用いて、EL素子を用いた表示装置の例について説明する。

図10は、画素410の構成例を示す回路図である。ここでは、表示素子として、一対の電極間に電流励起によって発光する有機物を備えた素子(以下、有機エレクトロルミネッセンス(EL)素子ともいう)を用いる場合について説明する。

図10に示す画素410は、トランジスタ411〜416と、容量素子417、418と、有機EL素子419とを有する。

ここで、例えばトランジスタ416および容量素子418に先の実施の形態で示したトランジスタおよび容量素子を適用することができる。先の実施の形態で示したトランジスタおよび容量素子を適用することで、画素410が有する回路の消費電力を低減し、集積度を向上させることができる。

トランジスタ411では、ソースおよびドレインの一方が信号線408に電気的に接続され、ゲートが走査線406に電気的に接続されている。

トランジスタ412では、ソースおよびドレインの一方が電位V1を供給する配線に電気的に接続され、ゲートが走査線405に電気的に接続されている。なお、ここでは、電位V1は、高電源電位(Vdd)よりも低電位でありかつ低電源電位(Vss)よりも高電位であることとする。

トランジスタ413では、ソースおよびドレインの一方が電源線409に電気的に接続され、ゲートがトランジスタ412のソースおよびドレインの他方に電気的に接続されている。

トランジスタ414では、ソースおよびドレインの一方がトランジスタ411のソースおよびドレインの一方に電気的に接続され、ソースおよびドレインの他方がトランジスタ413のソースおよびドレインの他方に電気的に接続され、ゲートが走査線405に電気的に接続されている。

トランジスタ415では、ソースおよびドレインの一方が電位V0を供給する配線に電気的に接続され、ソースおよびドレインの他方がトランジスタ413のソースおよびドレインの他方、およびトランジスタ414のソースおよびドレインの他方に電気的に接続され、ゲートが走査線404に電気的に接続されている。なお、ここでは、電位V0は、電位V1よりも低電位でありかつ低電源電位(Vss)よりも高電位であることとする。

トランジスタ416では、ソースおよびドレインの一方がトランジスタ413のソースおよびドレインの他方、トランジスタ414のソースおよびドレインの他方、およびトランジスタ415のソースおよびドレインの他方に電気的に接続され、ゲートが反転走査線407に電気的に接続されている。

容量素子417では、一方の電極がトランジスタ412のソースおよびドレインの他方、およびトランジスタ413のゲートに電気的に接続され、他方の電極がトランジスタ411のソースおよびドレインの他方、およびトランジスタ414のソースおよびドレインの一方に電気的に接続されている。

容量素子418では、一方の電極がトランジスタ411のソースおよびドレインの他方、トランジスタ414のソースおよびドレインの一方、および容量素子417の他方の電極に電気的に接続され、他方の電極がトランジスタ413のソースおよびドレインの他方、トランジスタ414のソースおよびドレインの他方、トランジスタ415のソースおよびドレインの他方、およびトランジスタ416のソースおよびドレインの一方に電気的に接続されている。

有機EL素子419では、アノードがトランジスタ416のソースおよびドレインの他方、に電気的に接続され、カソードが共通電位を供給する配線に電気的に接続されている。なお、上述のトランジスタ412のソースおよびドレインの一方が電気的に接続する配線に与えられる共通電位と、有機EL素子419のカソードに与えられる共通電位とが異なる電位であってもよい。

なお、ここでは、電源線409が供給する電位は、高電源電位(Vdd)よりも低電位でありかつ電位V1よりも高電位であり、共通電位は、低電源電位(Vss)よりも低電位であることとする。

また、以下においては、トランジスタ412のソースおよびドレインの他方、トランジスタ13のゲート、および容量素子417の一方の電極が電気的に接続するノードをノードDと呼び、トランジスタ411のソースおよびドレインの他方、トランジスタ414のソースおよびドレインの一方、容量素子417の他方の電極、および容量素子418の一方の電極が電気的に接続するノードをノードEと呼び、トランジスタ413のソースおよびドレインの他方、トランジスタ414のソースおよびドレインの他方、トランジスタ415のソースおよびドレインの他方、トランジスタ416のソースおよびドレインの一方、および容量素子418の他方の電極が電気的に接続するノードをノードFと呼ぶこととする。

図11(A)に、画素410の断面図のうちトランジスタ416および容量素子418を含む部分を示す。

トランジスタ416および容量素子418上には、トランジスタ416のソース電極またはドレイン電極に達する開口部を有する平坦化絶縁膜480が設けられる。

平坦化絶縁膜480上には、アノード481が設けられる。アノード481は、平坦化絶縁膜480の有する開口部でトランジスタ416のソース電極またはドレイン電極と接する。

アノード481上には、アノード481に達する開口部を有する隔壁484が設けられる。

隔壁484上には、隔壁484に設けられた開口部でアノード481と接する発光層482が設けられる。

発光層482上には、カソード483が設けられる。

アノード481、発光層482およびカソード483の重畳する領域が、有機EL素子419となる。

なお、平坦化絶縁膜480は、平坦化絶縁膜4126として示した材料から選択して用いればよい。

発光層482は、一層に限定されず、複数種の発光材料などを積層して設けてもよい。例えば、図11(B)に示すような構造とすればよい。図11(B)は、中間層485a、発光層486a、中間層485b、発光層486b、中間層485c、発光層486cおよび中間層485dの順番で積層した構造である。このとき、第1の発光層486a、発光層486bおよび発光層486cに適切な発光色の材料を用いると演色性の高い、または発光効率の高い、有機EL素子419を形成することができる。

発光材料を複数種積層して設けることで、白色光を得てもよい。図11(A)には示さないが、白色光を、着色層を介して取り出す構造としても構わない。

ここでは発光層482を3層および中間層を4層設けた構造を示しているが、これに限定されるものではなく、適宜発光層の数および中間層の数を変更することができる。例えば、中間層485a、発光層486a、中間層485b、発光層486bおよび中間層485cのみで構成することもできる。また、中間層485a、発光層486a、中間層485b、発光層486b、発光層486cおよび中間層485dで構成し、中間層485cを省いた構造としても構わない。

また、中間層は、正孔注入層、正孔輸送層、電子輸送層および電子注入層などを積層構造で用いることができる。なお、中間層は、これらの層を全て備えなくてもよい。これらの層は適宜選択して設ければよい。なお、同様の機能を有する層を重複して設けてもよい。また、中間層としてキャリア発生層のほか、電子リレー層などを適宜加えてもよい。

アノード481は、可視光透過性を有する導電膜を用いればよい。可視光透過性を有するとは、可視光領域(例えば400nm〜800nmの波長範囲)における平均の透過率が70%以上、特に80%以上であることをいう。

アノード481としては、例えば、In−Zn−W系酸化物膜、In−Sn系酸化物膜、In−Zn系酸化物膜、In系酸化物膜、Zn系酸化物膜およびSn系酸化物膜などの酸化物膜を用いればよい。また、前述の酸化物膜は、Al、Ga、Sb、Fなどが微量添加されてもよい。また、光を透過する程度の金属薄膜(好ましくは、5nm〜30nm程度)を用いることもできる。例えば5nmの膜厚を有するAg膜、Mg膜またはAg−Mg合金膜を用いてもよい。

または、アノード481は、可視光を効率よく反射する膜が好ましい。アノード481は、例えば、リチウム、アルミニウム、チタン、マグネシウム、ランタン、銀、シリコンまたはニッケルを含む膜を用いればよい。

カソード483は、アノード481として示した膜から選択して用いることができる。ただし、アノード481が可視光透過性を有する場合は、カソード483が可視光を効率よく反射すると好ましい。また、アノード481が可視光を効率よく反射する場合は、カソード483が可視光透過性を有すると好ましい。

なお、アノード481およびカソード483を図11(A)に示す構造で設けているが、アノード481とカソード483を入れ替えても構わない。アノードとして機能する電極には、仕事関数の大きい材料を用いることが好ましく、カソードとして機能する電極には仕事関数の小さい材料を用いることが好ましい。ただし、アノードと接してキャリア発生層を設ける場合には、仕事関数を考慮せずに様々な導電性材料を陽極に用いることができる。

隔壁484は、平坦化絶縁膜4126として示した材料から選択して用いればよい。

有機EL素子419と接続するトランジスタ416は、電気的特性のばらつきが小さいため、表示装置の表示品質を高めることができる。

<液晶素子を用いた表示装置の例>

図10および図11では、表示素子として有機EL素子を用いた表示装置について詳細に示したが、これに限らない。例えば、表示素子として、液晶素子を用いた表示装置に本実施の形態を適用することは、当業者であれば容易に想到しうるものである。

具体的な例として、液晶素子を用いた表示装置に適用可能な画素の構成について、図12を用いて以下に説明する。

図12(A)は、液晶素子を用いた表示装置の画素の構成例を示す回路図である。図12(A)に示す画素450は、トランジスタ451と、容量素子452と、一対の電極間に液晶材料の充填された素子(以下液晶素子ともいう)453とを有する。

ここで、トランジスタ451と容量素子452に、先の実施の形態で示したトランジスタおよび容量素子を適用することができる。先の実施の形態で示したトランジスタおよび容量素子を適用することで、画素450が有する回路の消費電力を低減し、集積度を向上させることができる。

トランジスタ451では、ソースおよびドレインの一方が信号線455に電気的に接続され、ゲートが走査線454に電気的に接続されている。

容量素子452では、一方の電極がトランジスタ451のソースおよびドレインの他方に電気的に接続され、他方の電極が共通電位を供給する配線に電気的に接続されている。

液晶素子453では、一方の電極がトランジスタ451のソースおよびドレインの他方に電気的に接続され、他方の電極が共通電位を供給する配線に電気的に接続されている。なお、上述の容量素子452の他方の電極が電気的に接続する配線に与えられる共通電位と、液晶素子453の他方の電極に与えられる共通電位とが異なる電位であってもよい。

図12(B)に、画素450の断面のうちトランジスタ451および容量素子452を含む部分を示す。

トランジスタ451および容量素子452上には、トランジスタ451のソース電極またはドレイン電極に達する開口部を有する平坦化絶縁膜490が設けられる。

平坦化絶縁膜490上には、電極491が設けられる。電極491は、平坦化絶縁膜490の有する開口部でトランジスタ451のソース電極またはドレイン電極と接する。

電極491上には、配向膜として機能する絶縁膜492が設けられる。

絶縁膜492上には、液晶層493が設けられる。

液晶層493上には、配向膜として機能する絶縁膜494が設けられる。

絶縁膜494上には、スペーサ495が設けられる。

スペーサ495および絶縁膜494上には、電極496が設けられる。

電極496上には、基板497が設けられる。

なお、平坦化絶縁膜490は、平坦化絶縁膜4126として示した材料から選択して用いればよい。

液晶層493は、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶などを用いればよい。これらの液晶材料は、条件により、コレステリック相、スメクチック相、キュービック相、カイラルネマチック相、等方相などを示す。

なお、液晶層493として、ブルー相を示す液晶材料を用いてもよい。その場合、配向膜として機能する絶縁膜492、494を設けない構成とすればよい。

電極491は、可視光透過性を有する導電膜を用いればよい。

電極491としては、例えば、In−Zn−W系酸化物膜、In−Sn系酸化物膜、In−Zn系酸化物膜、In系酸化物膜、Zn系酸化物膜およびSn系酸化物膜などの酸化物膜を用いればよい。また、前述の酸化物膜は、Al、Ga、Sb、Fなどが微量添加されてもよい。また、光を透過する程度の金属薄膜(好ましくは、5nm〜30nm程度)を用いることもできる。

または、電極491は、可視光を効率よく反射する膜が好ましい。電極491は、例えば、アルミニウム、チタン、クロム、銅、モリブデン、銀、タンタルまたはタングステンを含む膜を用いればよい。

電極496は、電極491として示した膜から選択して用いることができる。ただし、電極491が可視光透過性を有する場合は、電極496が可視光を効率よく反射すると好ましい。また、電極491が可視光を効率よく反射する場合は、電極496が可視光透過性を有すると好ましい。

なお、電極491および電極496を図9(B)に示す構造で設けているが、電極491と電極496を入れ替えても構わない。

絶縁膜492、494は、有機化合物材料または無機化合物材料から選択して用いればよい。

スペーサ495は、有機化合物材料または無機化合物材料から選択して用いればよい。なお、スペーサ495の形状は、柱状、球状など様々にとることができる。

液晶素子453と接続するトランジスタ451は、電気的特性のばらつきが小さいため、表示装置の表示品質を高めることができる。

電極491、絶縁膜492、液晶層493、絶縁膜494および電極496の重畳する領域が、液晶素子453となる。

基板497は、ガラス材料、樹脂材料または金属材料などを用いればよい。基板497は可撓性を有してもよい。

トランジスタ451は、電気的特性のばらつきが小さいため、表示装置の表示品質を高めることができる。

本実施の形態に示したように、先の実施の形態で示したトランジスタを表示装置の一部に適用することができる。当該トランジスタは電気的特性のばらつきが小さいため、表示装置の表示品質を高めることができる。

(実施の形態7)

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機、携帯型ゲーム機、携帯情報端末、音響再生装置、遊技機(パチンコ機、スロットマシン等)、ゲーム筐体が挙げられる。これらの電子機器の具体例を図13に示す。

図13(A)は、表示部を有するテーブル9000を示している。テーブル9000は、筐体9001に表示部9003が組み込まれており、表示部9003により映像を表示することが可能である。なお、4本の脚部9002により筐体9001を支持した構成を示している。また、電力供給のための電源コード9005を筐体9001に有している。

先の実施の形態に示す半導体装置は、表示部9003に用いることが可能であり、電子機器の消費電力を低減することができる。

表示部9003は、タッチ入力機能を有しており、テーブル9000の表示部9003に表示された表示ボタン9004を指などで触れることで、画面操作や、情報を入力することができ、また他の家電製品との通信を可能とする、または制御を可能とすることで、画面操作により他の家電製品をコントロールする制御装置としてもよい。例えば、表示部9003にタッチ入力機能を持たせてもよい。

また、筐体9001に設けられたヒンジによって、表示部9003の画面を床に対して垂直に立てることもでき、テレビジョン装置としても利用できる。狭い部屋においては、大きな画面のテレビジョン装置は設置すると自由な空間が狭くなってしまうが、テーブルに表示部が内蔵されていれば、部屋の空間を有効に利用することができる。

図13(B)は、テレビジョン装置9100を示している。テレビジョン装置9100は、筐体9101に表示部9103が組み込まれており、表示部9103により映像を表示することが可能である。なお、ここではスタンド9105により筐体9101を支持した構成を示している。

テレビジョン装置9100の操作は、筐体9101が備える操作スイッチや、別体のリモコン操作機9110により行うことができる。リモコン操作機9110が備える操作キー9109により、チャンネルや音量の操作を行うことができ、表示部9103に表示される映像を操作することができる。また、リモコン操作機9110に、当該リモコン操作機9110から出力する情報を表示する表示部9107を設ける構成としてもよい。

図13(B)に示すテレビジョン装置9100は、受信機やモデムなどを備えている。テレビジョン装置9100は、受信機により一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、または受信者間同士など)の情報通信を行うことも可能である。

先の実施の形態に示す半導体装置は、表示部9103、9107に用いることが可能であり、テレビジョン装置、およびリモコン操作機の消費電力を低減することができる。

図13(C)はコンピュータであり、本体9201、筐体9202、表示部9203、キーボード9204、外部接続ポート9205、ポインティングデバイス9206等を含む。

先の実施の形態に示す半導体装置は、表示部9203に用いることが可能であり、低消費電力なコンピュータとすることが可能となる。

図14(A)および図14(B)は2つ折り可能なタブレット型端末である。図14(A)は、開いた状態であり、タブレット型端末は、筐体9630、表示部9631a、表示部9631b、表示モード切り替えスイッチ9034、電源スイッチ9035、省電力モード切り替えスイッチ9036、留め具9033、操作スイッチ9038、を有する。

先の実施の形態に示す半導体装置は、表示部9631a、表示部9631bに用いることが可能であり、低消費電力なタブレット型端末とすることが可能となる。

表示部9631aは、一部をタッチパネルの領域9632aとすることができ、表示された操作キー9638にふれることでデータ入力をすることができる。なお、表示部9631aにおいては、一例として半分の領域が表示のみの機能を有する構成、もう半分の領域がタッチパネルの機能を有する構成を示しているが該構成に限定されない。表示部9631aの全ての領域がタッチパネルの機能を有する構成としてもよい。例えば、表示部9631aの全面をキーボードボタン表示させてタッチパネルとし、表示部9631bを表示画面として用いることができる。

また、表示部9631bにおいても表示部9631aと同様に、表示部9631bの一部をタッチパネルの領域9632bとすることができる。また、タッチパネルのキーボード表示切り替えボタン9639が表示されている位置に指やスタイラスなどでふれることで表示部9631bにキーボードボタン表示することができる。

また、タッチパネルの領域9632aとタッチパネルの領域9632bに対して同時にタッチ入力することもできる。

また、表示モード切り替えスイッチ9034は、縦表示または横表示などの表示の向きを切り替え、白黒表示やカラー表示の切り替えなどを選択できる。省電力モード切り替えスイッチ9036は、タブレット型端末に内蔵している光センサで検出される使用時の外光の光量に応じて表示の輝度を最適なものとすることができる。タブレット型端末は光センサだけでなく、ジャイロ、加速度センサ等の傾きを検出するセンサなどの他の検出装置を内蔵させてもよい。

また、図14(A)では表示部9631bと表示部9631aの表示面積が同じ例を示しているが特に限定されず、一方のサイズともう一方のサイズが異なっていてもよく、表示の品質も異なっていてもよい。例えば一方が他方よりも高精細な表示を行える表示パネルとしてもよい。

図14(B)は、閉じた状態であり、タブレット型端末は、筐体9630、太陽電池9633、充放電制御回路9634、バッテリー9635、DCDCコンバータ9636を有する。なお、図14(B)では充放電制御回路9634の一例としてバッテリー9635、DCDCコンバータ9636を有する構成について示している。

なお、タブレット型端末は2つ折り可能なため、未使用時に筐体9630を閉じた状態にすることができる。従って、表示部9631a、表示部9631bを保護できるため、耐久性に優れ、長期使用の観点からも信頼性の優れたタブレット型端末を提供できる。

また、この他にも図14(A)および図14(B)に示したタブレット型端末は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付または時刻などを表示部に表示する機能、表示部に表示した情報をタッチ入力操作または編集するタッチ入力機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。

タブレット型端末の表面に装着された太陽電池9633によって、電力をタッチパネル、表示部、または映像信号処理部等に供給することができる。なお、太陽電池9633は、筐体9630の一面または二面に効率的なバッテリー9635の充電を行う構成とすることができるため好適である。なお、バッテリー9635としては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。

また、図14(B)に示す充放電制御回路9634の構成、および動作について図14(C)にブロック図を示し説明する。図14(C)には、太陽電池9633、バッテリー9635、DCDCコンバータ9636、コンバータ9637、スイッチSW1乃至SW3、表示部9631について示しており、バッテリー9635、DCDCコンバータ9636、コンバータ9637、スイッチSW1乃至SW3が、図14(B)に示す充放電制御回路9634に対応する箇所となる。

まず、外光により太陽電池9633により発電がされる場合の動作の例について説明する。太陽電池で発電した電力は、バッテリー9635を充電するための電圧となるようDCDCコンバータ9636で昇圧または降圧がなされる。そして、表示部9631の動作に太陽電池9633からの電力が用いられる際にはスイッチSW1をオンにし、コンバータ9637で表示部9631に必要な電圧に昇圧または降圧をすることとなる。また、表示部9631での表示を行わない際には、SW1をオフにし、SW2をオンにしてバッテリー9635の充電を行う構成とすればよい。

なお、太陽電池9633については、発電手段の一例として示したが、特に限定されず、圧電素子(ピエゾ素子)や熱電変換素子(ペルティエ素子)などの他の発電手段によるバッテリー9635の充電を行う構成であってもよい。例えば、無線(非接触)で電力を送受信して充電する無接点電力電送モジュールや、また他の充電手段を組み合わせて行う構成としてもよい。

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。