以下、本発明の実施形態について、添付図面を参照して詳細に説明する。

(第1の実施形態)

図1は、本発明の第1の実施形態に係る固体撮像素子を表す回路図である。画素部101には、その各々が入射光を電荷に変換する光電変換素子(光電変換部)を含み、電荷をアナログ電気信号として出力する複数の画素102がマトリクス状にN行M列で配置されている。ここでは例として、行方向に6画素、列方向に4画素に配列された画素部を示す。なお、画素102の各々には、図29に示すようなベイヤー配列のカラーフィルタが配置され、各画素はカラーフィルタの色に応じた画素値を出力する。なお、図29では、Bフィルタと同じ列に配置されるGフィルタをG1フィルタ、Rフィルタと同じ列に配置されるGフィルタをG2フィルタとする。図29のように、R画素とG2画素が配置されたRG列と、G1画素とB画素が配置されたGB列が交互に繰り返されるものである。以下に説明する実施形態では、説明をわかりやすくするために、GB列については図示せず、RG列が複数列連続して並んでいるものして説明するが、実際にはRG列の間にRG列と同様に構成されたGB列が配置されている。

画素102は、行選択線104を介して水平レジスタ103と接続されており、選択された行選択線104に接続された6画素が同時に選択される。ここでは、1〜4行目までの行選択線104をPv1〜Pv4とする。行選択線104がHIGHのとき、行が選択され、画素102からアナログ電気信号が列出力線105に出力される。また、行選択線104がLOWのとき、行の選択は解除され、画素102と列出力線105との接続は切断される。行選択線104のPv1〜Pv4を1行ずつ選択することで、1〜4行目の画素のアナログ電気信号を列出力線105へ順次出力する。

ADコンバータ(ADC)106は、列出力線105に出力されたアナログ電気信号をデジタル信号へ変換する。各列出力線105とA/Dコンバータ106の間には、加算バッファ111(加算部)、列トランジスタ107及びADトランジスタ108がある。また、行トランジスタ109が列トランジスタ107とADトランジスタ108の間にあり、他の列と接続/切断することが可能である。列トランジスタ107、ADトランジスタ108、行トランジスタ109は、垂直レジスタ110で接続、切断を制御する。

列トランジスタ107を接続しているときには、列出力線105のアナログ電気信号を読みだすことができる。また、列トランジスタ107を切断しているときには、列出力線105のアナログ電気信号を読みだすことができない。ADトランジスタ108を接続しているときには、ADコンバータ106がアナログ電気信号を読み込むことができる。また、ADトランジスタ108を切断しているときには、ADコンバータ106がアナログ電気信号を読み込むことができない。行トランジスタ109は、或る列の画素から列出力線105に出力されたアナログ電気信号を、別の列のADコンバータ106を用いてAD変換するときに用いる。

次に、図1の画素102の詳細な構造について、図2を用いて説明する。フォトダイオード(以下、PDと表記する)301は、光電変換により入射光に応じた電荷を発生する。PD301とフローティングディフュージョン(以下、FDと表記する)領域303の間に、転送トランジスタ302が配置されており、転送制御パルスpTXがLOWのときはPD301とFD領域303は切断されており、転送制御パルスpTXがHIGHのときは接続されて、PD301で発生した電荷がFD領域303へ転送される。

リセットトランジスタ304は、リセット電源とFD領域303の間に配置され、リセット制御パルスpRESがLOWの場合は切断状態である。また、リセット制御パルスpRESがHIGHの場合はリセット電源とFD領域303が接続される。このとき、FD領域303はリセット電源と同電位になる。また、このときに転送制御パルスpTXもHIGHにすると、PD301もリセット電圧と同電位になる。このようにリセット制御パルスpRESをHIGHにすることで、各部がリセット電圧と同電位になるようなリセット動作を行なう。

選択トランジスタ305は、画素電源と増幅トランジスタ306の間に配置され、選択制御パルスpSELがLOWの場合に増幅トランジスタ306と画素電源を切断し、選択制御パルスpSELがHIGHの場合に接続する。ここで、選択制御パルスpSELがHIGHの場合に、増幅トランジスタ306は、FD領域303に保持された電荷に応じた電圧を増幅してアナログ電気信号として列出力線105へ出力する。

容量309は、列出力線105に出力されたアナログ電気信号をAD変換する期間、アナログ電気信号を保持するための容量である。また、列出力線105と容量309の間には、出力線トランジスタ308が配置されており、制御パルスpSIGがLOWの場合には、列出力線105と容量309は切断され、制御パルスpSIGがHIGHの場合には接続される。

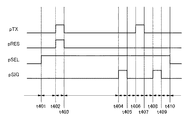

次に、図2の具体的な動作について、図3を用いて説明する。ここでは基準成分のアナログ電気信号と、信号成分のアナログ電気信号を列出力線へ出力する動作について説明する。

時刻t401に、読み出し画素の行の選択制御パルスpSELをHIGHにする。この動作により、読み出し行の増幅トランジスタ306のゲートへ入力されている、FD領域303の電圧が増幅されて、列出力線105へ出力される。

次に、時刻t402にて転送制御パルスpTXとリセット制御パルスpRESをHIGHにする。この動作によって、リセット電源とPD301の電圧、FD領域303の電圧が同電圧になり、PD301とFD領域303がリセットされる。

次に、時刻t403にて転送制御パルスpTXとリセット制御パルスpRESをLOWにする。この動作によって、PD301とFD領域303のリセット動作を終了する。また、リセット動作を終了した時点からPD301の電荷蓄積が開始される。

次に、時刻t404にて制御パルスpSIGをHIGHにする。この動作によって、列出力線105と容量309が電気的に接続され、列出力線105へ出力されている基準成分のアナログ電気信号が容量309へ入力される。次に、時刻t405にて制御パルスpSIGをLOWにする。この動作によって、列出力線105と容量309が電気的に切断され、この時点のアナログ電気信号の電圧を容量309が保持する。また、時刻t405で保持した容量309の電圧は後段のADC106で読み出す。

次に、時刻t406にて転送制御パルスpTXをHIGHにする。この動作によって、PD301における光電変換により蓄積された電荷をFD領域303へ転送する。次に、時刻t407にて転送制御パルスpTXをLOWにする。この動作によって、PD301からFD領域303への電荷の転送を終了する。時刻t403からt407までの期間が電荷の蓄積時間となる。また、時刻t407の時点で、蓄積時間中に蓄積された信号成分の電荷に応じた電圧が増幅トランジスタ306によって増幅され、列出力線105へ出力される。

次に、時刻t408にて制御パルスpSIGをHIGHにする。この動作によって、列出力線105と容量309が電気的に接続され、列出力線105へ出力されている信号成分のアナログ電気信号が容量309へ入力される。次に、時刻t409にて制御パルスpSIGをLOWにする。この動作によって、列出力線105と容量309が電気的に切断され、この時点のアナログ電気信号の電圧を容量309が保持する。

次に、時刻t410に、読み出し画素の行の選択制御パルスpSELをLOWにする。この動作により、読み出し行の増幅トランジスタ306の、列出力線105へのアナログ電気信号の出力が止まる。以下、次の行の画素に対して同様の動作を繰り返すことで、画素信号を読み出すことができる。

次に、図1のADC106の詳細な構造について、図4を用いて説明する。図4の出力線トランジスタ308、容量309は、図2の出力線トランジスタ308、容量309と同じものである。

増幅アンプ503は、アナログ電気信号ASIGと基準電圧VREFの差分電圧を増幅して比較器506へ出力する。ここで増幅アンプ503の増幅率は容量504によって決定される。

ランプ信号発生器505は、ランプ波(ランプ信号)を比較器506へ出力する。比較器506は、増幅後のアナログ電気信号pGSIGと、ランプ信号発生器505のランプ信号pLAMPとを比較し、電圧の大小関係が逆転すると、出力信号pCOMPが反転する。ここでは、増幅後のアナログ電気信号pGSIGの電圧よりランプ信号発生器のランプ信号pLAMPの電圧が低い場合にLOWを、ランプ信号発生器のランプ信号pLAMPの電圧が高い場合にHIGHを出力する。

グレイコードカウンタ507は、ランプ信号発生器505の動作開始のタイミングでカウントを開始し、カウント値をメモリ508へ入力する。メモリ508は、比較器506からの入力信号がHIGHになったときの、グレイコードカウンタ507のカウント値を保持する。

ランプ信号発生器505の出力が1周期動作した後に、メモリ508が保持しているカウント値を読みだす。クロック509は、ランプ信号発生器505とグレイコードカウンタ507の同期信号を発生している。

次に、図4に示したアナログ電気信号をデジタル信号に変換するADC106の動作について、図5を用いて説明する。

時刻t601に制御パルスpSIGをHIGHにする。この動作により、容量309に図4の増幅後のアナログ電気信号pVSIGの電圧が充電される。同時に図4の増幅アンプ503へアナログ電気信号pVSIGが入力され、アナログ電気信号pVSIGが増幅された信号pGSIGが比較器506へ出力される。次に、時刻t602にて制御パルスpSIGをLOWにする。この動作によって、pVSIGのアナログ電気信号の電圧を容量309が保持する。

次に、時刻t603にてランプ信号発生器505からランプ信号pLAMPが出力される。また、同時にグレイコードカウンタ507からメモリ508にグレイコード信号pCNTを出力する。ここでは、説明を分かりやすくするため3ビットのグレイコードカウンタを用いて説明する。また、ランプ信号pLAMPの電圧に同期してグレイコード信号pCNTは変化する。このカウントは、時刻t605まで行う。

ここで、比較器506は、信号pGSIGとランプ信号pLAMPを比較し、信号pGSIGよりランプ信号pLAMPが低い場合に出力信号pCOMPがLOWになり、信号pGSIGよりランプ信号pLAMPが高い場合に出力信号pCOMPがHIGHになる。出力信号pCOMPがHIGHになる時刻をt604とすると、メモリ508は、この時点で入力されている出力信号pCNTを記憶する。

次に、ADコンバータ106を用いた画素信号の読み出し動作について説明する。図1において、画素部101の選択行の各画素102からは、アナログ電気信号として、1回目の読出し動作で画素信号の雑音を含む基準成分ΔV(N信号)が読み出され、2回目の読出し動作で信号成分Vsig(S信号)が読み出される。そして、基準成分ΔVと信号成分Vsigとが列出力線105を通してADコンバータ106に入力される。

1回目に読み出される基準成分ΔVには、画素102ごとにばらつく固定パターンノイズがオフセットとして含まれている。2回目の読出し動作では、基準成分ΔVと、画素102ごとの入射光量に応じた信号成分Vsigを加えたVsig+ΔVが読み出される。そして、2回目の読み出し(Vsig+ΔV)と1回目の読み出し(ΔV)の差分から、求める信号値Vsigが得られる。

そして、1回目のAD変換処理を基準成分ΔVについて行なう場合、2回目のAD変換処理は基準成分ΔVに信号成分Vsigを加えた信号についての処理となる。

次に、詳細なADコンバータの動作について図6を用いて説明する。最初に基準成分ΔVのAD変換について説明する。

時刻t71において、画素102より基準成分ΔVのアナログ電気信号が入力される。次に時刻t72〜t74において、参照電圧RAMPを単位時間毎に一定量ずつ変化させる。このとき参照電圧RAMPとアナログ電気信号の比較を行い、電圧が一致する時刻t73を測定する。ここで、参照電圧RAMPの単位時間当たりの電圧変化量と、t72〜t73の時間の積が、基準成分ΔVとしてデジタルデータに変換される。

次に、信号成分VsigのAD変換について説明する。時刻t75において、画素102より信号成分Vsigが入力される。次に時刻t76〜t78において、参照電圧RAMPを単位時間毎に一定量ずつ変化させる。このとき参照電圧RAMPとアナログ電気信号の比較を行い、電圧が一致する時刻t77を測定する。ここで、参照電圧RAMPの単位時間当たりの電圧変化量と、t76〜t78の時間の積が、信号成分Vsigとしてデジタルデータに変換される。

ここで求められた2回目の読み出し(Vsig+ΔV)と1回目の読み出し(ΔV)の差分を画素の信号値として出力する。

次に、図1の撮像素子を用いた場合の、全画素読み出しの駆動について説明する。全画素読み出し駆動では、各列の画素102のアナログ電気信号は、画素102のある各列のADコンバータ106によって読み出される。

そのため、全ての列トランジスタ107、ADトランジスタ108をHIGHにして接続状態にし、全ての行トランジスタ109をLOWにして切断状態にする。こうすることで、図1の撮像素子において、画素102の画素の信号は、画素102がある列のADコンバータによって信号が読み出される。

次に、全画素読みを行う際の具体的な動作について、図7を用いて説明する。まず、t801において、行選択信号Pv1と列トランジスタ107の制御パルスである列Tr1〜6、ADトランジスタ108の制御パルスであるADCTr1〜6がHIGHとなる。行選択信号Pv1がHIGHになることで、1行目にある画素11〜16のアナログ電気信号が各列の列出力線105に出力される。

また、列Tr1〜6とADCTr1〜6がHIGHになることで、各列の列出力線105のアナログ電気信号は、各列のADコンバータ106へ出力される。このときのADコンバータ106の状態は、図6のt71の状態に相当する。また、t801〜t802は図6のt71〜t72に相当し、t801〜t802間でアナログ電気信号をADコンバータ106に入力する。

次に、t802において、1行目の画素102に対して図6のt72に相当する基準成分ΔVの読み出しを開始する。ここでは、ADCTr1〜6をLOWにして、列出力線105とADコンバータ106の接続を切断する。これにより、ADコンバータ106が基準成分ΔVのアナログ電気信号の電圧を保持する。それと同時に、基準成分ΔVのアナログ電気信号と参照電圧RAMPとの比較動作を開始する。

次に、t803において、1行目の画素102に対する基準成分ΔVの読み出しを終了する。ADコンバータ106の動作としては、図6のt74の状態に相当する。また、ADCTr1〜6をHIGHにして、1行目の画素部102の信号成分Vsigの読み出しを開始する。

次に、t804において、図6のt76に相当する信号成分Vsigの読み出しを、1行目の画素102に対して開始する。ここでは、ADCTr1〜6をLOWにして、列出力線105とADコンバータ106の接続が切断される。これにより、ADコンバータ106が信号成分Vsigのアナログ電気信号の電圧を保持する。それと同時に、信号成分Vsigのアナログ電気信号と参照電圧RAMPとの比較動作を開始する。

また、t804〜t805は、図6のt76〜t78に相当し、t804〜t805間でアナログ電気信号をADコンバータ106に入力する。そして、t805にて信号成分Vsigのアナログ電気信号と参照電圧RAMPとの比較動作を終了する。また、行選択信号Pv1をLOWにして、行選択信号Pv2と列Tr1〜6、ADCTr1〜6をHIGHにする。この制御によって、2行目の画素102の信号値の読み出しを開始する。

以下、1行目と同様に基準成分と信号成分のアナログ電気信号をAD変換して信号値を読み出す。

次に、図1の撮像素子を用いた場合の、行に沿った方向に1/2間引き読み出しする駆動方法について説明する。本実施形態では、撮像素子を画素間引き駆動する際に、読み出し画素信号を読み出し画素列のADコンバータ106と間引き画素列のADコンバータ106に振り分けて入力し、AD変換する。その結果、間引き量が増えるほど、1読み出し列が使用できるADコンバータの数を増やすことができ、1フレームの画素信号読み出しに要するAD変換の回数を減らすことができ、AD変換に要する時間を短縮できる。

図8を用いて、本実施形態の動作の概要を説明する。図8(a)で1/2間引きの動作を説明する。図8(a)の(1)に示すように、ここでは、1列、3列、5列の画素信号を読み出し、2列、4列、6列の画素信号を読み出さない。まず、図8(a)の(2)で1行目の画素信号を1列、3列、5列のADコンバータに転送する。次に、図8(a)の(3)で2行目の画素信号を2列、4列、6列のADコンバータに転送する。そして、図8(a)の(4)でADコンバータの読み出し動作を開始する。

以上の動作により、一度の読み出し動作で、2行分の信号を同時にAD変換することが可能となる。また、図8(b)では、同様に1/3間引きの動作を説明しており、この動作では3行分の信号を同時にAD変換することが可能となる。

従来の撮像素子では、画素102の信号は、各画素のある列のADコンバータ106がAD変換を行っていた。そのため、行に沿った方向の加算量や間引き量が多くなるにつれ、画素信号の読み出しを行っていないADコンバータが増えていた。しかし、本実施形態では、行に沿った方向の加算/列間引き読み出し駆動を行う場合には、間引かれた列のADコンバータ106にも画素信号を入力して読み出しを行う。こうすることで、列間引き量に応じて1度に(同時に)AD変換を行う行を増やすことができる。

次に、行に沿った方向に1/2間引き読み出し駆動を行う際の、具体的な動作について、図9を用いて説明する。

まず、1行目の画素102の基準成分ΔVのアナログ電気信号をADコンバータ106に入力する。t901において、行選択信号Pv1と列Tr1〜列Tr6のうちの列Tr1、3、5、ADCTr1〜ADCTr6のうちのADCTr1、3、5がHIGHとなる。行選択信号Pv1がHIGHになることで、1行目にある画素11、13、15の基準成分ΔVのアナログ電気信号が1列目、3列目、5列目の各列の列出力線105に出力される。また、列Tr1、3、5とADCTr1、3、5がHIGHになることで、1列目、3列目、5列目の各列の列出力線のアナログ電気信号が、各列のADコンバータ106へ出力される。

次に、t902において、1行目の画素102とADコンバータ106の接続を切断し、2行目の画素102の基準成分ΔVのアナログ電気信号をADコンバータ106に入力する。まず、Pv1とADCTr1、3、5をLOWとする。この制御により、1列目、3列目、5列目のADコンバータが、1行目の画素11、13、15の基準成分ΔVのアナログ電気信号の電圧を保持する。そして、Pv2とADCTr1〜ADCTr6のうちのADCTr2、4、6、行Tr1〜行Tr5のうちの行Tr1、3、5をHIGHにする。行選択信号Pv2がHIGHになることで、2行目にある画素11、13、15の基準成分ΔVのアナログ電気信号が1列目、3列目、5列目の各列の列出力線105に出力される。

次に、t903において、2行目の画素102とADコンバータ106の接続を切断し、ADコンバータ106が保持している1行目と2行目の画素102の基準成分ΔVのアナログ電気信号の読み出しを開始する。

まず、Pv2とADCTr2、4、6、行Tr1、3、5をLOWとする。この制御により、2列目、4列目、6列目のADコンバータが、2行目の画素21、23、25の基準成分ΔVのアナログ電気信号の電圧を保持する。そして、ADCRESをHIGHにして、図6のt72の動作で1行目と2行目の画素の基準成分のアナログ電気信号の読み出しを開始する。

次に、t904において、1行目と2行目の画素の基準成分ΔVのアナログ電気信号の読み出しを終了し、信号成分Vsigの読み出しを行う。まず、ADCRESをLOWにして、ADコンバータ106の基準成分読み出し動作を終了する。

次に、t901と同様に、行選択信号Pv1と列Tr1〜列Tr6のうちの列Tr1、3、5、ADCTr1〜ADCTr6のうちのADCTr1、3、5をHIGHとする。行選択信号Pv1をHIGHとすることで、1行目にある画素11、13、15の信号成分Vsigのアナログ電気信号が各列の垂直出力線105に出力される。また、列Tr1、3、5とADCTr1、3、5がHIGHになることで、1列目、3列目、5列目の各列の垂直出力線のアナログ電気信号が各列のADコンバータ106へ出力される。

次に、t905において、1行目の画素102とADコンバータ106の接続を切断し、2行目の画素102の信号成分Vsigのアナログ電気信号をADコンバータ106に入力する。まず、Pv1とADCTr1、3、5をLOWとする。この操作により、1列目、3列目、5列目のADコンバータが、1行目の画素11、13、15の信号成分Vsigのアナログ電気信号の電圧を保持する。

そして、Pv2とADCTr1〜ADCTr6のうちのADCTr2、4、6、行Tr1〜行Tr5のうちの行Tr1、3、5をHIGHにする。行選択信号Pv2がHIGHになることで、2行目にある画素11、13、15のアナログ電気信号が1列目、3列目、5列目の各列の列出力線105に出力される。

次に、t906において、2行目の画素102とADコンバータ106の接続を切断し、ADコンバータ106が保持している1行目と2行目の画素の、信号成分Vsigのアナログ電気信号の読み出しを開始する。まず、Pv2とADCTr2、4、6、行Tr1、3、5をLOWとする。この制御により、2列目、4列目、6列目のADコンバータが、2行目の画素21、23、25の信号成分のアナログ電気信号の電圧を保持する。

そして、ADCSIGをHIGHにして、図6のt72の動作で1行目と2行目の画素の信号成分のアナログ電気信号の読み出しを開始する。

次に、t907において、1行目と2行目の画素の信号成分Vsigのアナログ電気信号の読み出しを終了し、3行目の基準成分ΔVの読み出しを行う。

そして、ADCSIGをLOWにしてADコンバータ106の基準成分読み出し動作を終了する。次に、行選択信号Pv3をHIGHにし、t901と同様に列Tr1、3、5、ADCTr1、3、5をHIGHにして、行選択信号Pv3をHIGHとすることで、3行目にある画素31、33、35の信号成分のアナログ電気信号を各列の列出力線105に出力する。

また、列Tr1、3、5とADCTr1、3、5がHIGHになることで、各列の列出力線のアナログ電気信号は各列のADコンバータ106へ出力される。

以下、1行目、2行目の読み出し動作と同様に基準成分と信号成分の読み出し動作を行う。

次に、加算バッファ111を用いて画素信号の加算を行なう場合について説明する。本実施形態では加算バッファ111の一例として、電荷加算平均回路を用いた3列の加算バッファを用いる。なお、ここで紹介する電荷加算平均回路は一例であり、他の構成でもよく、電荷を加算する電荷加算回路でもよい。

次に、加算バッファの構成について説明する。加算バッファの構成を図10に示す。入力線pVIN1〜3を介して列出力線からのアナログ電気信号が入力される。また、出力線pVOUT1〜3を介してアナログ電気信号を出力する。

入力トランジスタ1101〜1103は、制御信号pISIG1〜3により制御され、出力トランジスタ1107〜1109は、制御信号pOSIG1〜3により制御される。また、加算ソースフォロワ(以下、加算SF)1110〜1112は、直列に接続している出力トランジスタの制御信号pOSIGがHIGHのときに、ゲートの電荷信号をアナログ電気信号に変換して出力する。

加算トランジスタ1113、1114は、制御信号pSHR1、pSHR2により制御され、この加算トランジスタが接続されたときに、両端にある容量1104〜1106の電荷(画素信号同士)が加算平均される。図10の加算バッファの場合、制御信号pSHR1がHIGHのとき、容量1104と容量1105に蓄積された電荷が加算平均され、制御信号pSHR1とpSHR2がHIGHのときは、容量1104〜1106に蓄積された電荷が加算平均され、加算信号が生成される。

次に、図11を用いて、3画素加算平均動作について説明する。入力線pVIN1〜3に列出力線のアナログ電気信号が入力されており、時刻t1201にて、制御信号pISIG1〜3をHIGHにする。すると容量1104〜1106に対応する列出力線のアナログ電気信号が入力される。

次に、時刻t1202にて、制御信号pISIG1〜3をLOWにする。この動作によって、列出力線のアナログ電気信号を保持する。次に、時刻t1203にて制御信号pSHR1とpSHR2をHIGHにする。この動作によって、容量1104〜1106の電荷を加算する。加算動作を行うと、図11に示すように、加算した容量C1104〜1106の電圧はすべて一定となる。また、容量1104〜1106の容量値を変更することで、蓄積する電荷を変更でき、列ごとに重みを付けて加算することも可能である。

次に、時刻t1204にて制御信号pSHR1とpSHR2をLOWにして画素加算を終了する。

次に、加算結果を出力する列の出力トランジスタをONする。ここでは出力線pVOUT1の列へ加算結果を出力するため、時刻t1205にて制御信号pOSIG1をHIGHにする。ADCへの出力が終了したら、時刻t1206にて制御信号pOSIG1をLOWにする。

本実施形態では、撮像素子を画素加算駆動する際に、複数の行の画素信号のAD変換を同時に行う。こうすることで、加算量が増えるほど、1フレームのAD変換の回数を減らすことができ、AD変換に要する時間を短縮できる。また、以下の各実施形態において、加算バッファへ入力され加算される画素信号は同色画素であることが望ましい。

次に、図12を用いて、本実施形態の動作の概要を説明する。図12(a)で2画素加算の動作を説明する。ここでは、1列+2列、3列+4列、5列+6列の信号をそれぞれ加算して読み出す。

まず、図12(a)の(2)で1行目の各列の画素信号を加算バッファにおいて2列ずつ加算し、1、3、5列のADコンバータに転送する。次に、図12(a)の(3)で2行目の各列の画素信号を加算バッファにおいて2列ずつ加算し、2、4、6列のADコンバータに転送する。そして、図12(a)の(4)でADコンバータの読み出し動作を開始する。

以上の動作により、一度の読み出し動作で、2画素加算された2行分の信号を同時にAD変換することが可能となる。

また、図12(b)では、同様に3画素加算の動作を説明しており、この動作では3行分の信号を同時にAD変換することが可能となる。加算バッファの加算平均動作以外の動作については、列間引き読み出し駆動を行う場合と同様であるため、説明を省略する。

(第2の実施形態)

図13は、本発明の第2の実施形態に係る固体撮像素子を表す回路図である。第2の実施形態の回路図は、列トランジスタ107が削除された点以外は、図1と同様である。本実施形態では、撮像素子を画素間引き駆動する際、或いは撮像素子を画素加算駆動する際に、任意の行の画素信号のAD変換を、複数のADコンバータを用いて行う。こうすることで、間引く量が増えるほど、1画素の読み出しに使用できるADコンバータの数を増やすことができ、AD変換に要する時間を短縮できる。また、加算量が増えるほど、加算後の信号読み出しに使用できるADコンバータの数を増やすことができ、AD変換に要する時間を短縮できる。

次に、図14を用いて、本実施形態の動作の概要を説明する。図14(a)で1/2間引きの動作を説明する。

図14(a)の(1)に示すように、ここでは、1列、3列、5列の画素信号を読み出し、2列、4列、6列の画素信号を間引く。まず、図14(a)の(2)で1行目の1列、3列、5列の画素信号を1列と2列、3列と4列、5列と6列のADコンバータでそれぞれA/D変換し、図14(a)の(3)でADコンバータの読み出し動作を開始する。以上の動作により、1画素あたり2つのADコンバータを使用することが可能となる。

また、図14(b)では、同様に1/3間引きの動作を説明しており、この動作では1画素あたり3つのADコンバータを使用することが可能となる。

本実施形態では、画素信号を間引き読み出しで読みだす時、同一の基準成分/信号成分のアナログ電気信号を複数のADコンバータ1406へ入力し、AD変換処理を行う。図15にADコンバータの回路図を示す。図15のADコンバータは、直流電圧付加回路1610が追加されたこと以外は、図4と同様の構成である。この直流電圧付加回路1610は、決められた直流電圧の入力の有無を、任意のタイミングで切り替えることができる。

次に、図15のADコンバータ1406の動作について、図16のタイミングチャートを用いて説明する。ここで、画素1402からADコンバータ1406にアナログ電気信号を入力するまでの動作と、ADコンバータのAD変換の仕組みは、第1の実施形態と同様であるため説明を省略する。ここでは例として、2個のADコンバータをそれぞれADコンバータa、ADコンバータbとし、ADコンバータaを用いた動作を、図16(a)、ADコンバータbを用いた動作を、図16(b)を用いて説明する。

最初に、基準成分ΔVのAD変換について説明する。図16より、時刻t1701において、画素1402より基準成分ΔVが入力される。次に、時刻t1702〜t1704において、参照電圧RAMPを単位時間毎に一定量ずつ変化させる。このとき参照電圧RAMPと基準成分ΔVのアナログ電気信号の比較を行い、電圧が一致する時刻t1703を測定する。ここで、参照電圧RAMPの単位時間当たりの電圧変化量と、t1702〜t1703の時間の積が、基準成分ΔVとしてデジタルデータに変換される。

次に、信号成分VsigのAD変換について説明する。時刻t1705において、画素1402より信号成分Vsigが入力される。時刻t1706において、ADコンバータbへの入力電圧である参照電圧RAMP2に直流電圧付加回路の電圧を加えて入力する。

ここで、AD変換で変換可能な電圧の範囲を入力電圧範囲としたとき、本実施形態では、ADコンバータa、bで入力電圧範囲を上位と下位とに分け、下位をADコンバータaで読み出し、上位をADコンバータbで読み出す。具体的には、ADコンバータbは参照電圧RAMP2に直流電圧付加回路の直流電圧を加えて、ADコンバータaとは異なる参照信号オフセット電圧から信号の比較を行う。

次に、時刻t1707〜t1709において、参照電圧RAMP1,2を単位時間毎に一定量ずつ変化させる。このとき参照電圧RAMP1,2と信号成分Vsigのアナログ電気信号の比較を行い、ADコンバータa、bのどちらかの電圧が一致する時刻t1708を測定する。ここで、参照電圧RAMP1,2の単位時間当たりの電圧変化量と、t1707〜t1708の時間の積が、信号成分Vsigとしてデジタルデータに変換される。ここで求められた2回目の読み出し(Vsig+ΔV)と1回目の読み出し(ΔV)の差分を画素の信号値として出力する。

AD変換が終了したら、時刻t1710にて参照電圧RAMP2の直流電圧付加回路の直流電圧の入力を停止することで、参照電圧RAMP1と参照電圧RAMP2を同じ電圧にする。

次に、図13の撮像素子を用いた場合の、行に沿った方向に1/2間引いて読み出す駆動方法について説明する。従来の撮像素子では、画素1402の信号は、画素1402の各列のADコンバータがAD変換を行っていた。そのため、行に沿った方向の間引き量が多くなるにつれ、画素信号の読み出しに使用しないADコンバータが余っていた。しかし、本実施形態では、列間引き読み出し駆動を行う場合には、間引かれた列のADコンバータ1406も使用して読み出しを行う。こうすることで、列間引き量に応じて1度に(同時に)AD変換を行う行を増やすことができる。

次に、行に沿った方向に1/2間引き読み出し駆動を行う際の、具体的な動作について、図17を用いて説明する。まず、1行目の画素1402の基準成分ΔVのアナログ電気信号をADコンバータ1406に入力する。t1801において、行選択信号Pv1と、ADCTr1〜6と行Tr1〜行Tr5のうちの行Tr1、3、5がHIGHとなる。行選択信号Pv1がHIGHになることで、1行目にある画素11、13、15の基準成分ΔVのアナログ電気信号が各列の列出力線1405に出力される。また、ADCTr1〜6と行Tr1、3、5がHIGHになることで、画素信号を読み出す画素の列の垂直出力線のアナログ電気信号は、読み出し画素の列と、読み出し画素の列と行Trで接続された列のADコンバータ1406へ出力される。

次にt1802において、1行目の画素1402とADコンバータ1406の接続を切断し、ADコンバータ1406が保持している1行目の画素の基準成分ΔVのアナログ電気信号の読み出しを開始する。まず、Pv1とADCTr1〜6をLOWとする。この制御により、1、2列目のADコンバータが、画素11の基準成分ΔVのアナログ電気信号の電圧を保持する。

同様に3、4列目のADコンバータが画素13の基準成分ΔVのアナログ電気信号の電圧を保持し、5、6列目のADコンバータが画素15の基準成分ΔVのアナログ電気信号の電圧を保持する。そして、ADCRESをHIGHにして、図16(a)、16(b)のt1702の動作で1行目の画素の基準成分ΔVのアナログ電気信号の読み出しを開始する

次にt1803において、1行目の基準成分ΔVのアナログ電気信号の読み出しを終了し、信号成分Vsigの読み出しを行う。まず、ADCRESをLOWにしてADコンバータ1406の基準成分読み出し動作を終了する。

次にt1801と同様に、行選択信号Pv1とADCTr1〜6をHIGHとする。行選択信号Pv1をHIGHとすることで、1行目にある画素11、13、15の信号成分Vsigのアナログ電気信号が各列の列出力線105に出力される。また、ADCTr1〜6がHIGHになることで、各列の列出力線のアナログ電気信号は各列のADコンバータ1406へ出力される。

次にt1804において、1行目の画素1402とADコンバータ1406の接続を切断し、ADコンバータの参照信号RAMPに直流電圧を加える。まず、Pv1とADCTr1〜6をLOWとする。この制御により、1〜6列目のADコンバータが、画素11、13、15の信号成分Vsigのアナログ電気信号の電圧を保持する。そしてADCOFFSETをHIGHにして、図16のt1706の動作で各ADコンバータ毎に所望の直流電圧を参照信号RAMPへ加える。

次にt1805において、ADコンバータ1406が保持している1行目の画素の信号成分Vsigのアナログ電気信号の読み出しを開始する。ADCSIGをHIGHにして、図16のt1707の動作で、1行目の画素の信号成分Vsigのアナログ電気信号の読み出しを開始する。次にt1806において、1行目の画素の信号成分Vsigのアナログ電気信号の読み出しを終了する。ADCSIGをLOWにしてADコンバータ1406の信号成分読み出し動作を終了する。

次にt1807において、ADコンバータの参照信号RAMPに加えられた直流電圧の入力を停止し、2行目の画素1402の基準成分ΔVをADコンバータ1406に入力する。T1807において、ADCOFFSETをLOWにして、図16のt1710の動作で各ADコンバータの参照信号RAMPへ加えられた直流電圧の入力をする。

次に、行選択信号Pv2と、ADCTr1〜6と行Tr1、3、5をHIGHにする。行選択信号Pv2がHIGHになることで、2行目にある画素11、13、15の基準成分ΔVのアナログ電気信号が各列の列出力線1405に出力される。また、ADCTr1〜6と行Tr1、3、5がHIGHになることで、画素信号を読みだす画素の列の列出力線のアナログ電気信号は、読み出し画素の列と、読み出し画素の列と行トランジスタで接続された列のADコンバータ1406へ出力される。

以下、1行目の読み出し動作と同様に基準成分と信号成分の読み出し動作を行う。

次に図18を用いて、加算バッファ1910により画素信号の加算を行なう場合について説明する。図18(a)で2画素加算の動作を説明する。ここでは、1列+2列、3列+4列、5列+6列の信号をそれぞれ加算して読み出す。

まず、図18(a)の(2)で1行目の2列ずつ加算された画素信号を1列と2列、3列と4列、5列と6列のADコンバータにそれぞれ入力し、そして、図18(a)の(3)でADコンバータの読み出し動作を開始する。

以上の動作により、1画素あたり2つのADコンバータを使用することが可能となる。また、図18(b)では、同様に3画素加算の動作を説明しており、この動作では加算後の信号1つに対して3つのADコンバータを使用することが可能となる。加算バッファの加算平均動作以外の動作については、列間引き読み出し駆動を行う場合と同様であるため、説明を省略する。

(第3の実施形態)

以下、本発明の第3の実施形態について説明する。図19は、第3の実施形態に係る固体撮像素子を表す回路図である。画素171−1,171−2は光電変換により、入射光に基づく信号を出力し、撮像部172には画素171がN行M列で配置されている。列出力線173−1、173−2は、行選択部174で選ばれた行の画素出力を列毎に出力する。本実施形態の固体撮像素子は、1画素列あたりに2本の列出力線173−1、173−2を有しており、同じ画素列において1行おきの画素が、交互に列出力線173−1、173−2に接続される構成になっている。本実施形態では画素171−1は出力線173−1へ、画素171−2は出力線173−2へと接続されている。

列アンプ175は列出力線173からの信号を入力とし、信号を増幅して列ごとに設けられたAD変換回路177へと出力する。各列の列アンプには、列アンプ基準電圧176が供給される。クランプSW114は信号をクランプする。

ランプ信号発生回路111はランプ信号を発生する。また、ラッチメモリ回路178−1,178−2はAD変換結果を一時記憶し、デジタル出力線180−1、180−2へと読み出すことができる。列選択回路179は、ラッチメモリ回路を順次選択しデジタル信号を順次、デジタル出力線110へと転送する。

S信号用のメモリ178−1及び出力線110−1はS信号を記憶して出力し、N信号用のメモリ178−2及び出力線110−2はN信号を記憶して出力する。また、画素列130−1、130−2は1画素列単位を示しており、本実施形態では、1画素列に対して列出力線が2本、列アンプが1つ、列AD変換回路が1つという構成となっている。また、グレイコードカウンタ113はグレイコードをカウントし、デジタル処理回路112はデジタル処理を行う。

加算回路120は、画素列130−1と画素列130−2から出力される画素信号を加算することができる。この加算回路120は、複数のスイッチと複数の容量で形成されている。そして、スイッチ121−1、121−2、122−1、122−2、123−1、123−2、124−1、124−2をオンオフすることにより、列出力線173−1に出力された画素信号を読み出すか、列出力線173−2に出力された画素信号を読み出すか、或いは、列出力線173−1または173−2に出力された画素信号を隣接する画素列の列出力線173−1または173−2に出力された画素信号とを加算するかを切り替えることができる。

本実施形態の特徴は、画素列に対して設けられたAD変換回路177と複数の画素列の信号を加算する加算回路120と、撮影条件に応じて、加算された画素信号を任意のAD変換回路に入力する切り替えスイッチを有することである。

AD変換回路177は、差動入力構成のコンパレータとなっていて、+入力端子には列アンプ175の出力信号が入力される。また、−入力端子には、ランプ信号発生回路111の出力が入力され、+入力端子の電圧が−入力端子よりも高い場合にはHighレベルを出力し、+入力端子の電圧がー入力端子よりも低い場合にはLowレベルを出力する。

ラッチメモリ回路178−1、178−2は、グレイコードカウンタ113のカウント値を、コンパレータの反転タイミングでラッチし記憶を行う、ラッチメモリ回路である。本実施形態では、コンパレータ177の出力がHiからLoに切り替わったときのグレイコードカウンタの出力を保持する。

図20は、図19における画素部171の回路構成の一例を示す回路図である。フォトダイオード152は、光電変換により入射光に応じた電荷を発生する。転送トランジスタ153は、ソースがフォトダイオード152、ゲートが転送制御線162、ドレインがフローティングディフージョン(以下、FDと表記する)領域154にそれぞれ電気的に接続されている。

FD領域154は、PD152から転送トランジスタ153を介して転送された電荷を一時的に保持する領域である。リセットトランジスタ155は、ソースがFD領域154、ゲートがリセット制御線161、ドレインが電源電圧にそれぞれ電気的に接続されている。増幅トランジスタ156は、制御電極であるゲートがFD領域154、ドレインが電源電圧、ソースが選択トランジスタ157にそれぞれ電気的に接続されている。選択トランジスタ157は、ゲートが選択制御線163、ソースが列出力線173、ドレインが増幅トランジスタ156のソースに接続されている。

増幅トランジスタ156は、FD領域154に保持された電荷に基づいた信号を、選択トランジスタ157を介して列出力線173に増幅出力する。リセット制御線161、転送制御線162、選択制御線163は、行選択部104にそれぞれ電気的に接続されている。

なお、図20において列出力線173、リセット制御線161、転送制御線162、選択制御線163については、行選択部174の1行目と2行目の駆動を分けて説明するために、1行目には「−1」を付け、2行目には「−2」を付けている。しかし、フォトダイオードなど152〜157で表わされる素子に関しては同一の動きであるため、各行毎の説明と符号を省略する。

図21は、図19に示した加算回路120の拡大図である。図21において、スイッチ121−1、123−1、121−2、123−2はオンの状態であり、スイッチ122−1、124−1、122−2、124−2はオフの状態を示している。これらのスイッチは、それぞれ図21(b)、図21(c) に示すようにスイッチング制御を行い、オン状態とオフ状態を切り替えることができる。

図21(a)、図21(b)、図21(c)は、それぞれモード毎のスイッチング状態を示しており、 図21Aは、列出力線173−1に出力された画素信号を読み出すモード、図21(b)は、列出力線173−2に出力された画素信号を読み出すモードである。また図21(c)は、画素列130−1の列出力線173−1に出力された画素信号を隣接する画素列130−2の列出力線173−1に出力された画素信号と加算してAD変換器へ出力するとともに、画素列130−1の列出力線173−2に出力された画素信号を隣接する画素列130−2の列出力線173−2に出力された画素信号と加算してAD変換器へ出力するモードである。図21(a)と図21(b)のモードに対して、列出力線173−1の画素信号と列出力線173−2の画素信号を同時に読み出すことができるため、高速に読み出すことが可能となる。

本実施形態では隣接する2列を加算しているが、実施形態はこれに限ったものではなく、一列または複数列離れた列との加算を行っても同様の効果が得られる。また、加算列の組み合わせや、加算の重み付けなどもこれに限ったものではなく、色重心のズレの無い加算なども考えられる。

図22は、図19、図20、図21に例示した固体撮像装置の駆動方法を例示したタイミング図である。図22(a)は、加算回路120が図21(a)及び図21(b)のスイッチ接続状態でのタイミングであり、図22(b)は、加算回路120が図21Cの状態でのタイミングである。

図22に例示したタイミング図においては、制御パルスをHighレベル(以下、Hレベルと表記する)とした場合に、制御パルスが印加されたMOSトランジスタの、ソースとドレイン間が導通する。一方、Lowレベル(以下、Lレベルと表記する)とした場合には、ソースとドレイン間が電気的に遮断される。なお、Lレベルの制御パルスがゲートに印加されることで、ソースとドレイン間が導通するMOSトランジスタを用いた場合には、図22に示したパルスのHレベルとLレベルを反対にすることで、本実施形態と同様の動作をすることができる。

以下、図22(a)のタイミング図に基づいて、時刻t0から順を追って、本実施形態の固体撮像装置の駆動方法について図19、図20、図21の回路動作を説明する。

はじめに、時刻t0において、読み出しを行う行の選択制御線163−1に出力される選択制御パルスがHレベルとなり、第1行が読み出し行として選択される。次に、時刻t1において、リセット制御線161−1に出力されるリセット制御パルスをHレベルからLレベルにすることで、FD領域154をリセットする。これにより列出力線173−1の電圧V173は、時刻t1においてリセットレベルに変化する。列出力線の出力が安定した時刻t2において制御パルス170をLレベルにしてクランプ動作を行う。

その後t3でAD変換を開始する。ここで図21に示す加算回路120のスイッチング動作関係は、図21(a)の状態となっている。したがって、水力出力線173−1の出力は、そのまま同列の列アンプ、列AD変換器へと接続されている。

ランプの傾きに応じて、時刻t3から電圧V204−は低下する。同時にカウンタ202がカウントを開始してカウンタ出力203が変化する。波形D203は、このカウンタのデジタルのコードに基づいて、出力値に換算した値を示す。

時刻t4において、電圧V204−と電圧V204+が反転したタイミングでコンパレータの出力が反転し、このときのカウンタ値D203を保持する。この保持値がリセットレベルAD変換結果である。t5において、リセットレベルのAD変換が終了し、ランプが初期レベルへと変化する。次に、t6で転送制御線161−1に出力される転送制御パルスをHレベルとし、フォトダイオード102で生じた電荷がFD領域174に転送され、t7で転送生後パルスがLレベルとなることで信号レベルが確定する。時刻t8において、AD変換を開始する。リセットレベルのAD変換と同様に、時刻t9でコンパレータの出力が反転し、このときのカウンタ値D203を保持する。リセットレベルの保持値と信号レベルの保持値の差分図示AがAD変換結果となる。この差分処理は、デジタル処理回路112で行われる。

次に、t10でセレクト制御線163−2に出力される選択制御パルスがHレベルとなり、第2行が読み出し行として選択される。また、セレクト制御線163−1、転送制御線162−1、リセット制御線161−1に出力される制御パルスは、それぞれLレベルへと戻る。これより先のタイミングでは、選択行が変わり、列出力線173−2に画素信号が出力されるようになること以外は動作が同じであるため、説明を省略する。ただし、図21に示す加算回路120のスイッチング動作関係は、図21(b)の状態となっている。したがって、列出力線173−1の出力は、スイッチングで切り替えられて同列の列アンプ、列AD変換器へと接続されている。

次に、図22(b)のタイミング図について説明する。はじめに、時刻t0において、読み出しを行う行の選択制御線163−1、163−2にそれぞれ出力される選択制御パルスが共にHレベルとなり、第1行及び第2行が共に読み出し行として選択される。次に、時刻t1において、リセット制御線161−1,161−2に出力されるリセット制御パルスを共にHレベルからLレベルにすることで、FD領域をリセットする。これにより列出力線173−1、173−2の電圧V173は、時刻t1においてリセットレベルに変化する。即ち、2行の画素信号を同時に読み出している。

図21(c)に示すような加算回路120のスイッチング制御により、画素列130−1の列出力線173−1の画素信号と隣の画素列130−2の列出力線173−1の画素信号とを容量を介して同一の列アンプに入力している。これにより、画素列130−1の列出力線173−1の画素信号と隣の画素列130−2の列出力線173−1の画素信号との加算を行っている。隣の列では、画素列130−1の列出力線173−2の画素信号と隣の列130−2の列出力線173−2の画素信号とを容量を介して同一の列アンプに入力している。このように加算した結果をそれぞれの列ADに接続して同時にAD変換することで、二行同時に読み出しを行うことができ、読み出しを高速化している。以下、時刻t2以降は、図22(a)と同様である。

なお、以下の説明では、画素をNチャネルトランジスタで構成した例を説明する。画素をPチャネルトランジスタで構成する場合にも、Nチャネルトランジスタで構成する場合に対して電圧の極性を反対にすることによって、本発明を適用することができる。また、AD変換方式は本実施形態に限ったものではなく、列カウンタを用いたり、逐次比比較方式や、シグマデルタを用いたAD変換であっても、加算回路とAD変換装置への接続を変更できれば同様の効果が得られる。

(第4の実施形態)

図23は、第4の実施形態を示す回路図である。第3の実施形態における図19と同じ回路に関しては同じ番号を付してあるため説明を省略する。本実施形態は列アンプを用いない構成であり、このような構成においても、列出力線173−1、列出力線173−2のそれぞれの画素信号をスイッチと容量を用いてサンプルホールドを行った後、平均化することで加算平均を行うことができる。以下、本実施形態における駆動方法に関して説明する。

列出力線173−1、173−2の画素信号をそれぞれ読み出す場合のスイッチング制御は、第3の実施形態の図21(a)、図21(b)と同じであるため説明を省略する。列出力線173−1、173−2の画素信号を加算して読み出す場合の駆動タイミングを図24に示す。なおスイッチ121−1、−2などは同じ動きであるため、タイミングを省略する。

はじめに、時刻t0において、読み出しを行う行の選択制御線163−1、163−2にそれぞれ出力される選択制御パルスが共にHレベルとなり、第1行及び第2行が共に読み出し行として選択される。次に、時刻t1において、リセット制御線161−1,161−2に出力されるリセット制御パルスを共にHレベルからLレベルにすることで、FD領域をリセットする。これにより列出力線173−1、173−2の電圧V173は、時刻t1においてリセットレベルに変化する。即ち、2行の画素信号を同時に読み出している。

この場合、スイッチ121−1、122−2、124−1、124−2はオン状態である。したがって容量125−1には、画素列130−1における列出力線173−1の電圧が入力され、容量125−2には、出力線173−2の電圧が入力される。また、容量126−1には、画素列130−2における列出力線173−1の電圧が、容量126−2には、画素列130−2における列出力線173−2の電圧が、それぞれサンプリングされている。時刻t2において、スイッチ121、124をオンからオフにすることで、上記列出力線173−1、173−2のリセットレベルがサンプリングさせる。

時刻t3において、スイッチ123−1、123−2がオンになることで、容量125−1と容量126−1、容量125−2と容量126−2がショートして、2つの信号が加算平均される。この後、時刻T4において、スイッチ123をオフし、時刻t5からAD変換を開始する。時刻t6以降の動作は第3の実施形態と同じであるため、説明を省略する。

その後、時刻t7で転送制御線の転送制御パルスをHレベルにして信号を読み出すが、この場合のスイッチ121、124のサンプリング動作はリセット信号を出力する場合のt1〜t4にかけての動作と同じである。このようにしてスイッチと容量を用いてサンプルホールドと平均化を行うことで加算を行い、加算された加算画素信号を任意のAD変換回路に入力するように切り替えることで、AD変換を同時に行い読み出しを高速化している。

(第5の実施形態)

図25は、第5の実施形態を示す回路図である。本実施形態の固体撮像素子は、1画素列あたりに4本の列出力線173−1、173−2、173−3、173−4を有するものである。本実施形態では、同じ画素列において列方向に連続する4行の画素が、それぞれ4本の列出力線173−1〜173−4の各々に接続されている。行選択回路174によって、4行を同時に選択して読み出すことができる。

したがって、本実施形態では、1画素列に対して上下2つの列アンプおよび列AD変換回路を設けているが、第3の実施形態等と同様に、加算された加算画素信号を任意の列のAD変換回路に入力するように切り替えることで、AD変換を同時に行い、読み出しを高速化することができる。

(第6の実施形態)

図26は、第6の実施形態を示す回路図である。本実施形態の加算回路121は、3列の加算回路であり、画素列130−1、130−2、130−3の3列の列出力線173−1の画素信号を加算し、加算された画素信号を画素列130−1のAD変換回路177へ入力する。また、画素列130−1、130−2、130−3の3列の列出力線173−2の画素信号を加算し、加算された画素信号を画素列130−2のAD変換回路177へ入力している。図27に加算回路のスイッチの接続状態を示す。他の実施形態と同様に、加算された加算画素信号を任意のAD変換回路に入力するように切り替えることで、AD変換を同時に行い、読み出しを高速化することができる。

図27(a)、27(b)、27(c)は、それぞれモード毎のスイッチング状態を示しており、 図27(a)は、列出力線173−1に出力された画素信号を画素列毎に読み出すモード、図27(b)は、列出力線173−2に出力された画素信号を画素列毎に読み出すモードである。また、図27(c)は、画素列130−1の列出力線173−1に出力された画素信号を隣接する画素列130−2、130−3の列出力線173−1にそれぞれ出力された画素信号と加算してAD変換器へ出力し、画素列130−1の列出力線173−2に出力された画素信号を隣接する画素列130−2、130−3の列出力線103−2に出力された画素信号と加算してAD変換器へ出力するモードである。図27(a)、図27(b)のモードに対して、列出力線173−1と列出力線173−2の画素信号を同時に読み出すことができるため、高速に読み出すことが可能となる。

本実施形態では隣接する2列を加算しているが、実施形態はこれに限ったものではなく、一列または複数列離れた列との加算を行っても同様の効果が得られる。また、加算列の組み合わせや、加算の重み付けなどもこれに限ったものではなく、色重心のズレの無い加算なども考えられる。

また、画素列130−3の列AD変換回路は使用していないので、動作させずに電力を削減するようにしてもよい。もしくは、さらに列出力線を増やすことで、3行同時に画素信号を読み出した場合のAD変換に用いて、高速化を行っても良い。

(第7の実施形態)

図28は、第7の実施形態による撮像装置の全体構成を示すブロック図である。撮影レンズ1010は被写体の光学像を撮像素子100に結像させる光学系であり、レンズ駆動回路1009によってズーム制御、フォーカス制御、絞り制御などが行われる。撮像素子100は、撮影レンズ1010で結像された被写体像を画像信号として取り込むためのものであり、第1〜第6の実施形態で説明した構成のいずれかを有している。信号処理回路1003は、撮像素子100から出力される画像信号に各種の補正を行ったり、データを圧縮したりする。タイミング発生回路1002は、撮像素子100に駆動タイミング信号を出力する。全体制御・演算回路1004は各種演算を行うとともに、撮像装置全体を制御する。メモリ回路1005は画像データを一時的に記憶し、表示回路1006は各種情報や撮影画像を表示する。記録回路1007は、画像データの記録または読み出しを行うための半導体メモリ等の着脱可能な記録回路である。操作回路1008は、デジタルカメラの操作部材への操作を電気的に受け付けるものである。