JP6096957B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6096957B2 JP6096957B2 JP2016047256A JP2016047256A JP6096957B2 JP 6096957 B2 JP6096957 B2 JP 6096957B2 JP 2016047256 A JP2016047256 A JP 2016047256A JP 2016047256 A JP2016047256 A JP 2016047256A JP 6096957 B2 JP6096957 B2 JP 6096957B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- wiring

- terminal

- electrically connected

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

- Electronic Switches (AREA)

Description

れており、第1のトランジスタの第2の端子が第2のトランジスタの第2の端子と電気的

に接続された回路が知られている。

れており、第1のトランジスタの第2の端子が第2のトランジスタの第2の端子と電気的

に接続された回路を有する半導体装置の動作を安定させることを第1の目的とする。

は、前記第1のトランジスタの第1の端子と電気的に接続されており、前記第1の配線は

、前記第2のトランジスタの第1の端子と電気的に接続されており、前記第2の配線は、

前記第3のトランジスタの第1の端子と電気的に接続されており、前記第3の配線は、前

記第1のトランジスタのゲート端子と電気的に接続されており、前記第3の配線は、前記

第3のトランジスタのゲート端子と電気的に接続されており、前記第4の配線は、前記第

2のトランジスタのゲート端子と電気的に接続されており、前記第3のトランジスタの第

2の端子は、前記第1のトランジスタの第2の端子と電気的に接続されており、前記第3

のトランジスタの第2の端子は、前記第2のトランジスタの第2の端子と電気的に接続さ

れており、前記第1のトランジスタは、第1のN型トランジスタであり、前記第2のトラ

ンジスタは、P型トランジスタであり、前記第3のトランジスタは、第2のN型トランジ

スタであり、前記第2のトランジスタは、シリコンを有するチャネル形成領域を有し、前

記第3のトランジスタは、酸化物半導体を有するチャネル形成領域を有することを特徴と

する半導体装置である。

は、前記第4のトランジスタの第1の端子と電気的に接続されており、前記第2の配線は

、前記第3のトランジスタの第1の端子と電気的に接続されており、前記第3の配線は、

前記第1のトランジスタのゲート端子と電気的に接続されており、前記第3の配線は、前

記第3のトランジスタのゲート端子と電気的に接続されており、前記第3の配線は、前記

第4のトランジスタのゲート端子と電気的に接続されており、前記第4の配線は、前記第

2のトランジスタのゲート端子と電気的に接続されており、前記第4のトランジスタの第

2の端子は、前記第1のトランジスタの第1の端子と電気的に接続されており、前記第4

のトランジスタの第2の端子は、前記第2のトランジスタの第1の端子と電気的に接続さ

れており、前記第3のトランジスタの第2の端子は、前記第1のトランジスタの第2の端

子と電気的に接続されており、前記第3のトランジスタの第2の端子は、前記第2のトラ

ンジスタの第2の端子と電気的に接続されており、前記第1のトランジスタは、第1のN

型トランジスタであり、前記第2のトランジスタは、P型トランジスタであり、前記第3

のトランジスタは、第2のN型トランジスタであり、前記第4のトランジスタは、第3の

N型トランジスタであり、前記第2のトランジスタは、シリコンを有するチャネル形成領

域を有し、前記第3のトランジスタは、酸化物半導体を有するチャネル形成領域を有し、

前記第4のトランジスタは、酸化物半導体を有するチャネル形成領域を有することを特徴

とする半導体装置である。

は、前記第4のトランジスタの第1の端子と電気的に接続されており、前記第2の配線は

、前記第3のトランジスタの第1の端子と電気的に接続されており、前記第3の配線は、

前記第1のトランジスタのゲート端子と電気的に接続されており、前記第3の配線は、前

記第3のトランジスタのゲート端子と電気的に接続されており、前記第4の配線は、前記

第2のトランジスタのゲート端子と電気的に接続されており、前記第4の配線は、前記第

4のトランジスタのゲート端子と電気的に接続されており、前記第4のトランジスタの第

2の端子は、前記第1のトランジスタの第1の端子と電気的に接続されており、前記第4

のトランジスタの第2の端子は、前記第2のトランジスタの第1の端子と電気的に接続さ

れており、前記第3のトランジスタの第2の端子は、前記第1のトランジスタの第2の端

子と電気的に接続されており、前記第3のトランジスタの第2の端子は、前記第2のトラ

ンジスタの第2の端子と電気的に接続されており、前記第1のトランジスタは、第1のN

型トランジスタであり、前記第2のトランジスタは、第1のP型トランジスタであり、前

記第3のトランジスタは、第2のN型トランジスタであり、前記第4のトランジスタは、

第2のP型トランジスタであり、前記第2のトランジスタは、シリコンを有するチャネル

形成領域を有し、前記第3のトランジスタは、酸化物半導体を有するチャネル形成領域を

有し、前記第4のトランジスタは、シリコンを有するチャネル形成領域を有することを特

徴とする半導体装置である。

れており、第1のトランジスタの第2の端子が第2のトランジスタの第2の端子と電気的

に接続された回路を有する半導体装置の動作を安定させることができる。

当業者であれば容易に理解される。

ない。

符号を共通して用い、その繰り返しの説明を省略する。

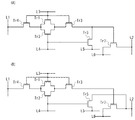

図1に半導体装置の一例を示す。

されている。

されている。

とができる機能を有する。

を有する。

)を変化させることによって、配線L1と配線L2との間の導通状態を制御することがで

きる。

。

好ましい。

基準電位(又は基準電圧)よりも高い電位(又は電圧)が「0(Low)」である。

の逆の極性は「0(Low)」である。

ンジスタをオン状態とすることができる。

ジスタをオフ状態とすることができる。

ンジスタをオフ状態とすることができる。

ジスタをオン状態とすることができる。

例を示す。

性にする構成の一例である。

ている。

ている。

性にする構成の一例である。

ている。

ている。

た配線の電気的状態(信号、電圧、電流、電位等)が安定しないことがある。

い。

力端子と電気的に接続されている。

電気的に接続されている。

がP型であり、トランジスタTr3がN型であると好ましい。

がN型であり、トランジスタTr3をP型であると好ましい。

通状態のときに、配線L1と配線L2との間の抵抗値を増やすことができる。

る。

するチャネル形成領域を有するトランジスタ、有機半導体を有するチャネル形成領域を有

するトランジスタ等があるが限定されない。

層を有するトランジスタ、シリコンを有する半導体基板(シリコンウェハ等)を用いて形

成されたトランジスタ、SOI基板を用いて形成されたトランジスタ等があるが限定され

ない。

するトランジスタ等があるが限定されない。

を有するチャネル形成領域を有するトランジスタはオフ電流が極めて小さい。

ャネル形成領域を有するトランジスタよりもオン電流を大きくすることができる。

タを作製することは不可能ではないが、現状の技術水準からすると困難である。

ジスタを作製することは現状の技術水準であれば容易である。

成領域を有するN型トランジスタであることが好ましい。

するP型トランジスタであることが好ましい。

るN型トランジスタである場合、配線L1と配線L2とが導通状態のときに、配線L1と

配線L2との間に流れる電流を大きくすることができるというメリットがある。

N型トランジスタであることによって、配線L1と配線L2とが非導通状態のときのリー

ク電流を大幅に低減することができる。

の少なくとも一部と適宜組み合わせて実施することができる。

図3は、図1において、トランジスタTr4を追加した図面の一例である。

説明は省略する。

されている。

されている。

されている。

されている。

がP型であり、トランジスタTr3がN型であり、トランジスタTr4がN型であると好

ましい。

がN型であり、トランジスタTr3がP型であり、トランジスタTr4がP型であると好

ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図4は、図1においてトランジスタTr4を追加した図面の一例である。

説明は省略する。

されている。

されている。

されている。

がP型であり、トランジスタTr3がN型であり、トランジスタTr4がP型であると好

ましい。

がN型であり、トランジスタTr3がP型であり、トランジスタTr4がN型であると好

ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図5は、図1においてトランジスタTr3を除外しトランジスタTr5を追加した図面

の一例である。

説明は省略する。

されている。

されている。

されている。

がP型であり、トランジスタTr5がN型であると好ましい。

がN型であり、トランジスタTr5がP型であると好ましい。

態とすることができる。

となり、配線L2の電気的状態が安定しない場合がある。

態のとき、配線L2が配線L5と導通するので、配線L2の電気的状態を安定させること

ができる。

に、配線L2の出力が変動してしまう場合がある。

トランジスタであることが好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図6は図5においてトランジスタTr3を追加した図面の一例である。

についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

がP型であり、トランジスタTr3がN型であり、トランジスタTr5がN型であると好

ましい。

がN型であり、トランジスタTr3がP型であり、トランジスタTr5がP型であると好

ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図7は図5においてトランジスタTr3を追加した図面の一例である。

についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

されている。

がP型であり、トランジスタTr3がP型であり、トランジスタTr5がN型であると好

ましい。

がN型であり、トランジスタTr3がN型であり、トランジスタTr5がP型であると好

ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図8は図5においてトランジスタTr4を追加した図面の一例である。

についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

がP型であり、トランジスタTr4がP型であり、トランジスタTr5がN型であると好

ましい。

がN型であり、トランジスタTr4がN型であり、トランジスタTr5がP型であると好

ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図9は図5においてトランジスタTr4を追加した図面の一例である。

についての繰り返しの説明は省略する。

されている。

されている。

されている。

がP型であり、トランジスタTr4がN型であり、トランジスタTr5がN型であると好

ましい。

がN型であり、トランジスタTr4がP型であり、トランジスタTr5がP型であると好

ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図10は図6においてトランジスタTr4を追加した図面の一例である。

、配線L1〜配線L5についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

2がP型であり、トランジスタTr3がN型であり、トランジスタTr4がP型であり、

トランジスタTr5がN型であると好ましい。

2がN型であり、トランジスタTr3がP型であり、トランジスタTr4がN型であり、

トランジスタTr5がP型であると好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図11は図6においてトランジスタTr4を追加した図面の一例である。

、配線L1〜配線L5についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

2がP型であり、トランジスタTr3がN型であり、トランジスタTr4がN型であり、

トランジスタTr5がN型であると好ましい。

2がN型であり、トランジスタTr3がP型であり、トランジスタTr4がP型であり、

トランジスタTr5がP型であると好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図12は図5においてトランジスタTr6を追加した図面の一例である。

についての繰り返しの説明は省略する。

されている。

されている。

2がP型であり、トランジスタTr5がN型であり、トランジスタTr6がP型であると

好ましい。

2がN型であり、トランジスタTr5がP型であり、トランジスタTr6がN型であると

好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L5と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

こともできる。

ジスタTr1をオン状態にすることができる電位(又は電圧)となり、配線L4の電位(

又は電圧)がトランジスタTr2をオン状態にすることができる電位(又は電圧)となる

。

Tr6の双方がオフ状態となるので、配線L5と配線L2とは非導通状態となる。

ジスタTr1をオン状態にすることができる電位(又は電圧)となり、配線L4の電位(

又は電圧)がトランジスタTr2をオフ状態にすることができる電位(又は電圧)となる

。

が、トランジスタTr6がオフ状態となるので、配線L5と配線L2とは非導通状態とな

る。

ジスタTr1をオフ状態にすることができる電位(又は電圧)となり、配線L4の電位(

又は電圧)がトランジスタTr2をオン状態にすることができる電位(又は電圧)となる

。

が、トランジスタTr5がオフ状態となるので、配線L5と配線L2とは非導通状態とな

る。

タTr1をオフ状態にすることができる電位(又は電圧)となり、配線L4の電位(又は

電圧)がトランジスタTr2をオフ状態にすることができる電位(又は電圧)となる。

6の双方がオン状態になるので、配線L5と配線L2とは導通状態となる。

乃至第3の導通状態の抵抗値が変化する。

の少なくとも一部と適宜組み合わせて実施することができる。

図13は図12においてトランジスタTr3を追加した図面の一例である。

、配線L1〜配線L5についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

されている。

2がP型であり、トランジスタTr3がN型であり、トランジスタTr5がN型であり、

トランジスタTr6がP型であると好ましい。

2がN型であり、トランジスタTr3がP型であり、トランジスタTr5がP型であり、

トランジスタTr6がN型であると好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図14は図12においてトランジスタTr3を追加した図面の一例である。

、配線L1〜配線L5についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

されている。

2がP型であり、トランジスタTr3がP型であり、トランジスタTr5がN型であり、

トランジスタTr6がP型であると好ましい。

2がN型であり、トランジスタTr3がN型であり、トランジスタTr5がP型であり、

トランジスタTr6がN型であると好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図15は図12においてトランジスタTr4を追加した図面の一例である。

、配線L1〜配線L5についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

2がP型であり、トランジスタTr4がN型であり、トランジスタTr5がN型であり、

トランジスタTr6がP型であると好ましい。

2がN型であり、トランジスタTr4がP型であり、トランジスタTr5がP型であり、

トランジスタTr6がN型であると好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図16は図12においてトランジスタTr4を追加した図面の一例である。

、配線L1〜配線L5についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

2がP型であり、トランジスタTr4がP型であり、トランジスタTr5がN型であり、

トランジスタTr6がP型であると好ましい。

2がN型であり、トランジスタTr4がN型であり、トランジスタTr5がP型であり、

トランジスタTr6がN型であると好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図17は図13においてトランジスタTr4を追加した図面の一例である。

、トランジスタTr6、配線L1〜配線L5についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

されている。

2がP型であり、トランジスタTr3がN型であり、トランジスタTr4がN型であり、

トランジスタTr5がN型であり、トランジスタTr6がP型であると好ましい。

2がN型であり、トランジスタTr3がP型であり、トランジスタTr4がP型であり、

トランジスタTr5がP型であり、トランジスタTr6がN型であると好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図18は図13においてトランジスタTr4を追加した図面の一例である。

、トランジスタTr6、配線L1〜配線L5についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

2がP型であり、トランジスタTr3がN型であり、トランジスタTr4がP型であり、

トランジスタTr5がN型であり、トランジスタTr6がP型であると好ましい。

2がN型であり、トランジスタTr3がP型であり、トランジスタTr4がN型であり、

トランジスタTr5がP型であり、トランジスタTr6がN型であると好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図19は図14においてトランジスタTr4を追加した図面の一例である。

、トランジスタTr6、配線L1〜配線L5についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

2がP型であり、トランジスタTr3がP型であり、トランジスタTr4がN型であり、

トランジスタTr5がN型であり、トランジスタTr6がP型であると好ましい。

2がN型であり、トランジスタTr3がN型であり、トランジスタTr4がP型であり、

トランジスタTr5がP型であり、トランジスタTr6がN型であると好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

図20は図14においてトランジスタTr4を追加した図面の一例である。

、トランジスタTr6、配線L1〜配線L5についての繰り返しの説明は省略する。

されている。

されている。

されている。

されている。

されている。

2がP型であり、トランジスタTr3がP型であり、トランジスタTr4がP型であり、

トランジスタTr5がN型であり、トランジスタTr6がP型であると好ましい。

2がN型であり、トランジスタTr3がN型であり、トランジスタTr4がN型であり、

トランジスタTr5がP型であり、トランジスタTr6がN型であると好ましい。

のリーク電流を低減することができる。

ンジスタであると、配線L1と配線L2とが非導通状態のときのリーク電流を格段に低減

することができるので好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

トランジスタTr1、トランジスタTr2、トランジスタTr3、又はトランジスタT

r4を有することによって、配線L2の出力が下がってしまう場合がある。

好ましい。

続されている。

続されている。

できる構成を有している。

ンジスタTr7のゲート端子が、トランジスタTr3の第1の端子と電気的に接続されて

いる。

1側に配置した例である。

されている。

1の端子と電気的に接続されている。

1の端子と電気的に接続されている。

ート端子と電気的に接続されている。

2の端子と電気的に接続されている。

2の端子と電気的に接続されている。

ことが好ましい。

、トランジスタTr7のゲート端子が、トランジスタTr3の第1の端子と電気的に接続

されている。

、トランジスタTr7のゲート端子が、トランジスタTr3の第1の端子と電気的に接続

されている。

トランジスタTr7を介して配線L2と電気的に接続されるので、配線L2の出力を上げ

ることができる。

であると、配線L2の出力がより上がるので好ましい。

出力端子として機能させた例を示したが、配線L6を出力端子として機能させても良い。

素子C及び配線L7を追加すると好ましい。

容量素子Cの一方の電極と電気的に接続し、配線L7を容量素子Cの他方の電極と電気的

に接続した例である。

端子を容量素子Cの一方の電極と電気的に接続し、配線L7を容量素子Cの他方の電極と

電気的に接続した例である。

端子を容量素子Cの一方の電極と電気的に接続し、配線L7を容量素子Cの他方の電極と

電気的に接続した例である。

端子を容量素子Cの一方の電極と電気的に接続し、配線L7を容量素子Cの他方の電極と

電気的に接続した例である。

蓄積することができる。

の電位(又は電圧)を「1(High)」とすることができる。

ていない場合、トランジスタTr7のゲート端子の電位(又は電圧)を「0(Low)」

とすることができる。

号、電圧、電流、電位等)と配線L7と電気的状態(信号、電圧、電流、電位等)とを制

御することによって、容量素子Cに蓄積される電荷量を制御することができる。

ときに、トランジスタTr7の導通状態を維持することができるようになる。

形成領域を有するN型トランジスタである場合、配線L1と容量素子Cの一方の電極とが

非導通状態のときのリーク電流を格段に低減することができるので好ましい。

量素子Cへの電荷蓄積動作を頻繁に行う必要があり消費電力が大きくなる。

通状態のときのリーク電流を少なくすることが好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

トランジスタTr1、トランジスタTr2、トランジスタTr3、トランジスタTr4

、トランジスタTr5、又はトランジスタTr6を有することによって、配線L2の出力

が下がってしまう場合がある。

好ましい。

続されている。

続されている。

ことができる構成を有している。

ンジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続されて

いる。

ンジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続されて

いる。

ンジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続されて

いる。

ンジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続されて

いる。

ンジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続されて

いる。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7のゲート端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

A)、図31(A)、図32(A)、図33(A)、図34(A)、図35(A)、図3

6(A)、図37(A)、図38(A)、図39(A)、及び図40(A)において、配

線L2と配線L6がトランジスタTr7を介して電気的に接続されるので、配線L2の出

力を上げることができる。

であると、配線L2の出力がより上がるので好ましい。

A)、図31(A)、図32(A)、図33(A)、図34(A)、図35(A)、図3

6(A)、図37(A)、図38(A)、図39(A)、及び図40(A)において、配

線L2を出力端子として機能させた例を示したが、配線L6を出力端子として機能させて

も良い。

A)、図31(A)、図32(A)、図33(A)、図34(A)、図35(A)、図3

6(A)、図37(A)、図38(A)、図39(A)、及び図40(A)は、以下のよ

うな動作を行うことができる。

スタTr7のゲート端子とが非導通状態となる第1の状態において、配線L1の電気的状

態(信号、電圧、電流、電位等)に応じて、トランジスタTr7をオン状態又はオフ状態

の一方とすることができる。

ジスタTr7のゲート端子とが導通状態となる第2の状態において、配線L5の電気的状

態(信号、電圧、電流、電位等)に応じて、トランジスタTr7をオン状態又はオフ状態

の他方とすることができる。

2と電気的に接続されるので、配線L2の出力を上げることができる。

、図30(B)、図31(B)、図32(B)、図33(B)、図34(B)、図35(

B)、図36(B)、図37(B)、図38(B)、図39(B)、及び図40(B)に

示す。

ンジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続されて

いる。

ンジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続されて

いる。

ンジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続されて

いる。

ンジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続されて

いる。

ンジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続されて

いる。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

ランジスタTr7の第2の端子が、トランジスタTr5の第1の端子と電気的に接続され

ている。

B)、図31(B)、図32(B)、図33(B)、図34(B)、図35(B)、図3

6(B)、図37(B)、図38(B)、図39(B)、及び図40(B)は、以下のよ

うな動作を行うことができる。

配線L1の電気的状態(信号、電圧、電流、電位等)に応じて、トランジスタTr7がオ

ン状態になる。

、トランジスタTr7がオフ状態になる。

第1の入力端子として機能させることができ、配線L6を第2の入力端子として機能させ

ることができる。

力端子として機能させることができ、配線L6を第2の出力端子として機能させることが

できる。

ンジスタTr5及びトランジスタTr7はシリコンを有するチャネル形成領域を有するト

ランジスタであることが好ましい。

の少なくとも一部と適宜組み合わせて実施することができる。

配線L1乃至配線L7に素子を電気的に接続することができる。

、表示素子等があるが限定されない。

の少なくとも一部と適宜組み合わせて実施することができる。

配線L5に配線L1を電気的に接続させることにより、トランジスタTr1及びトラン

ジスタTr2がオフ状態のとき、配線L1と配線L2とをトランジスタTr5を介して電

気的に接続させることができる。

ジスタTr2がオフ状態のとき、配線L3と配線L2とをトランジスタTr5を介して電

気的に接続させることができる。

ジスタTr2がオフ状態のとき、配線L4と配線L2とをトランジスタTr5を介して電

気的に接続させることができる。

の少なくとも一部と適宜組み合わせて実施することができる。

AがBと電気的に接続されている状態とは、AがBと直接接続されている状態、Aが回

路動作に影響のない素子を介してBと接続されている状態等である。

することができる素子であり、具体的には、抵抗素子、スイッチ、トランジスタ、ダイオ

ード等である。

とができる素子であり、具体的には、抵抗素子、スイッチ、トランジスタ、ダイオード、

容量素子等である。

の少なくとも一部と適宜組み合わせて実施することができる。

他の実施形態では、トランジスタTr1の極性とトランジスタTr2の極性とが異なる

例を示したが、トランジスタTr1の極性とトランジスタTr2の極性とが同じであって

も良い。

例を示したが、配線L3に配線L4の同じ極性の電位(又は電圧)を入力しても良い。

L3に配線L4の逆の極性の電位(又は電圧)を入力すると、トランジスタTr1又はト

ランジスタTr2の一方をオン状態とすることができ、トランジスタTr1又はトランジ

スタTr2の他方をオフ状態とすることができる。

L3に配線L4との同じ極性の電位(又は電圧)を入力すると、トランジスタTr1及び

トランジスタTr2の双方をオン状態とすることができる。

線L3に配線L4の逆の極性の電位(又は電圧)を入力すると、トランジスタTr1及び

トランジスタTr2の双方をオン状態とすることができる。

線L3に配線L4と同じ極性の電位(又は電圧)を入力すると、トランジスタTr1又は

トランジスタTr2の一方をオン状態とすることができ、トランジスタTr1又はトラン

ジスタTr2の他方をオフ状態とすることができる。

ることによって、トランジスタTr1の第1の端子とトランジスタTr2の第1の端子と

の接続点Aと、トランジスタTr1の第2の端子とトランジスタTr2の第2の端子との

接続点Bと、の間の抵抗値を変化させることができる。

の少なくとも一部と適宜組み合わせて実施することができる。

トランジスタTr3は、トランジスタTr1よりもオフ電流が小さいことが好ましい。

成領域を有するトランジスタと、シリコンを有するチャネル形成領域を有するトランジス

タと、を用いる方式である。

ャネル形成領域を有するトランジスタよりもオフ電流が極めて小さい。

ャネル形成領域を有するトランジスタよりもオン電流を大きくすることができる。

する方式である。

さくすることによって、一方のトランジスタのオフ電流を小さくすることができる。

、他方のトランジスタのオン電流を大きくすることができる。

する方式である。

きくすることによって、一方のトランジスタのオフ電流を小さくすることができる。

、他方のトランジスタのオン電流を大きくすることができる。

くすることによってオフ電流を小さくする方式である。

することによって、一方のトランジスタのオフ電流を小さくすることができる。

方のトランジスタのオン電流を大きくすることができる。

くすることによってオフ電流を小さくする方式である。

さくすることによって、一方のトランジスタのオフ電流を小さくすることができる。

、他方のトランジスタのオン電流を大きくすることができる。

ができるのであれば、第1の方式乃至第5の方式以外の方式を採用しても良い。

の少なくとも一部と適宜組み合わせて実施することができる。

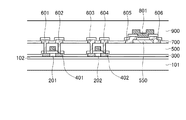

図41に半導体装置の一例を示す。

上、導電層605上、及び導電層606上に絶縁層700を有する。

することができる。

、を有する。

砒素等)が含有されている。

することができる。

、を有する。

ボロン等)が含有されている。

能することができる。

能することができる。

することができる。

。

することができる。

。

することができる。

するソース領域と電気的に接続されている。

するドレイン領域と電気的に接続されている。

するソース領域と電気的に接続されている。

するドレイン領域と電気的に接続されている。

有するN型トランジスタのソース電極として機能することができる。

有するN型トランジスタのドレイン電極として機能することができる。

有するN型トランジスタのゲート絶縁膜として機能することができる。

有するN型トランジスタのゲート電極として機能することができる。

。

ンを有するチャネル形成領域を有するP型トランジスタ、及び酸化物半導体を有するチャ

ネル形成領域を有するN型トランジスタを同一基板に形成することができる。

することができる。

としても良い。半導体層の上下にゲート電極を有するダブルゲート型トランジスタとして

も良い。

リコンを有するチャネル形成領域を有するP型トランジスタが、薄膜トランジスタである

例を示したが、半導体基板、SOI基板を用いたトランジスタとしても良い。

の少なくとも一部と適宜組み合わせて実施することができる。

基板、絶縁層、導電層、及び半導体層の材料について説明する。

)等を用いることができるがこれらに限定されない。

限定されない。

膜、窒化アルミニウムを有する膜、酸化アルミニウムを有する膜、酸化ハフニウムを有す

る膜等があるが限定されない。

、シロキサンを有する膜、エポキシを有する膜等があるが限定されない。

が好ましい。

金、銀、銅、アルカリ金属、アルカリ土類金属等があるが限定されない。

限定されない。

い。

があるが限定されない。

リコン膜等があるが限定されない。

は酸化物半導体層として機能することができる。

が限定されない。

−Zn系酸化物膜、Zn−Mg系酸化物膜、Sn−Mg系酸化物膜、In−Mg系酸化物

膜、In−Ga系酸化物膜等があるが限定されない。

Zn系酸化物膜、Sn−Ga−Zn系酸化物膜、In−Al−Zn系酸化物膜、In−H

f−Zn系酸化物膜、In−La−Zn系酸化物膜、In−Ce−Zn系酸化物膜、In

−Pr−Zn系酸化物膜、In−Nd−Zn系酸化物膜、In−Sm−Zn系酸化物膜、

In−Eu−Zn系酸化物膜、In−Gd−Zn系酸化物膜、In−Tb−Zn系酸化物

膜、In−Dy−Zn系酸化物膜、In−Ho−Zn系酸化物膜、In−Er−Zn系酸

化物膜、In−Tm−Zn系酸化物膜、In−Yb−Zn系酸化物膜、In−Lu−Zn

系酸化物膜、Al−Ga−Zn系酸化物膜、Sn−Al−Zn系酸化物膜等があるが限定

されない。

味する。

a−Zn系酸化物膜、In−Al−Ga−Zn系酸化物膜、In−Sn−Al−Zn系酸

化物膜、In−Sn−Hf−Zn系酸化物膜、In−Hf−Al−Zn系酸化物膜等があ

るが限定されない。

有する膜を意味する。

しい。

が可能であるが、N型トランジスタの方がP型トランジスタよりも実用的なので好ましい

。

好ましい。

−Axis Aligned Crystal)と呼ぶ。

度以上100度以下であっても良い。

るに際して、成膜時の基板温度を200℃以上450℃以下とする第1の方法がある。

0℃以上3分以上の加熱処理を施す第2の方法がある。

法のパターンA)。

CAACを形成することができる(第2の方法のパターンB)。

物半導体層上に第2の酸化物半導体層を形成する第3の方法がある。

定されない。

以上100度以下である結晶を形成することができる。

形成することができる。

の少なくとも一部と適宜組み合わせて実施することができる。

半導体装置とは、半導体を有する素子を有する装置である。

ある。

、RFID、プロセッサ等があるが限定されない。

の少なくとも一部と適宜組み合わせて実施することができる。

Tr2 トランジスタ

Tr3 トランジスタ

Tr4 トランジスタ

Tr5 トランジスタ

Tr6 トランジスタ

Tr7 トランジスタ

L1 配線

L2 配線

L3 配線

L4 配線

L5 配線

L6 配線

L7 配線

Lin 配線

INV1 インバータ

INV2 インバータ

C 容量素子

101 基板

102 絶縁層

201 半導体層

202 半導体層

300 絶縁層

401 導電層

402 導電層

500 絶縁層

550 半導体層

601 導電層

602 導電層

603 導電層

604 導電層

605 導電層

606 導電層

700 絶縁層

801 導電層

900 絶縁層

Claims (2)

- 第1乃至第3のトランジスタと、第1乃至第5の配線を有し、

前記第1の配線は、前記第1のトランジスタの第1の端子と電気的に接続されており、

前記第1の配線は、前記第2のトランジスタの第1の端子と電気的に接続されており、

前記第2の配線は、前記第1のトランジスタの第2の端子と電気的に接続されており、

前記第2の配線は、前記第2のトランジスタの第2の端子と電気的に接続されており、

前記第2の配線は、前記第3のトランジスタの第1の端子と電気的に接続されており、

前記第3の配線は、前記第1のトランジスタのゲート端子と電気的に接続されており、

前記第4の配線は、前記第2のトランジスタのゲート端子と電気的に接続されており、

前記第4の配線は、前記第3のトランジスタのゲート端子と電気的に接続されており、

前記第5の配線は、前記第3のトランジスタの第2の端子と電気的に接続されており、

前記第1のトランジスタは、第1のN型トランジスタであり、

前記第2のトランジスタは、P型トランジスタであり、

前記第3のトランジスタは、第2のN型トランジスタであり、

前記第2のトランジスタは、シリコンを有するチャネル形成領域を有し、

前記第3のトランジスタは、酸化物半導体を有するチャネル形成領域を有することを特徴とする半導体装置。 - 第1乃至第4のトランジスタと、第1乃至第5の配線を有し、

前記第1の配線は、前記第3のトランジスタの第1の端子と電気的に接続されており、

前記第2の配線は、前記第1のトランジスタの第1の端子と電気的に接続されており、

前記第2の配線は、前記第2のトランジスタの第1の端子と電気的に接続されており、

前記第2の配線は、前記第4のトランジスタの第1の端子と電気的に接続されており、

前記第3の配線は、前記第1のトランジスタのゲート端子と電気的に接続されており、

前記第3の配線は、前記第3のトランジスタのゲート端子と電気的に接続されており、

前記第4の配線は、前記第2のトランジスタのゲート端子と電気的に接続されており、

前記第4の配線は、前記第4のトランジスタのゲート端子と電気的に接続されており、

前記第5の配線は、前記第4のトランジスタの第2の端子と電気的に接続されており、

前記第3のトランジスタの第2の端子は、前記第1のトランジスタの第2の端子と電気的に接続されており、

前記第3のトランジスタの第2の端子は、前記第2のトランジスタの第2の端子と電気的に接続されており、

前記第1のトランジスタは、第1のN型トランジスタであり、

前記第2のトランジスタは、P型トランジスタであり、

前記第3のトランジスタは、第2のN型トランジスタであり、

前記第4のトランジスタは、第3のN型トランジスタであり、

前記第2のトランジスタは、シリコンを有するチャネル形成領域を有し、

前記第3のトランジスタは、酸化物半導体を有するチャネル形成領域を有し、

前記第4のトランジスタは、酸化物半導体を有するチャネル形成領域を有することを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016047256A JP6096957B2 (ja) | 2016-03-10 | 2016-03-10 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016047256A JP6096957B2 (ja) | 2016-03-10 | 2016-03-10 | 半導体装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012195987A Division JP5902590B2 (ja) | 2012-09-06 | 2012-09-06 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016149561A JP2016149561A (ja) | 2016-08-18 |

| JP6096957B2 true JP6096957B2 (ja) | 2017-03-15 |

Family

ID=56688025

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016047256A Expired - Fee Related JP6096957B2 (ja) | 2016-03-10 | 2016-03-10 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6096957B2 (ja) |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04156716A (ja) * | 1990-10-19 | 1992-05-29 | Nec Kyushu Ltd | Cmos型アナログスイッチ回路 |

| JPH04178012A (ja) * | 1990-11-13 | 1992-06-25 | Nec Kyushu Ltd | 半導体装置 |

| JPH0559971U (ja) * | 1992-01-14 | 1993-08-06 | シチズン時計株式会社 | スイッチ回路 |

| US8664658B2 (en) * | 2010-05-14 | 2014-03-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP5558222B2 (ja) * | 2010-06-18 | 2014-07-23 | シャープ株式会社 | 薄膜トランジスタ基板の製造方法 |

| WO2012008390A1 (en) * | 2010-07-16 | 2012-01-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2012014790A1 (en) * | 2010-07-27 | 2012-02-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

-

2016

- 2016-03-10 JP JP2016047256A patent/JP6096957B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016149561A (ja) | 2016-08-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7194859B1 (ja) | 半導体装置 | |

| JP6096233B2 (ja) | 半導体装置の作製方法、及び半導体装置 | |

| JP7233464B2 (ja) | 半導体装置 | |

| JP5667840B2 (ja) | 半導体装置 | |

| CN105765729B (zh) | 半导体装置 | |

| US10872907B2 (en) | Semiconductor device | |

| JP6096957B2 (ja) | 半導体装置 | |

| TW201605053A (zh) | 薄膜電晶體 | |

| JP5902590B2 (ja) | 半導体装置 | |

| US20210151604A1 (en) | Thin film transistor | |

| KR20100061290A (ko) | 반도체 소자 및 그 제조방법 | |

| WO2022252041A1 (zh) | 半导体器件 | |

| KR20100061064A (ko) | 반도체 소자 및 그 제조방법 | |

| JP2018195630A (ja) | トランジスタおよび表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161213 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170125 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170207 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170216 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6096957 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |