JP6095289B2 - 情報処理装置、情報処理装置の制御方法、及びプログラム - Google Patents

情報処理装置、情報処理装置の制御方法、及びプログラム Download PDFInfo

- Publication number

- JP6095289B2 JP6095289B2 JP2012164610A JP2012164610A JP6095289B2 JP 6095289 B2 JP6095289 B2 JP 6095289B2 JP 2012164610 A JP2012164610 A JP 2012164610A JP 2012164610 A JP2012164610 A JP 2012164610A JP 6095289 B2 JP6095289 B2 JP 6095289B2

- Authority

- JP

- Japan

- Prior art keywords

- processing apparatus

- information processing

- information

- stored

- state

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/60—Protecting data

- G06F21/602—Providing cryptographic facilities or services

Description

また、LUKS(Linux(登録商標) Unified Key Setup)等のように、不揮発性記憶装置上のファイルシステムを暗号化ファイルシステムにすることで、不揮発性記憶装置に保存する際にソフトウエアでメモリ上の情報全体を暗号化する方法もある。

また、情報処理装置の全メモリを対象としてしまうため、適切な暗号化のアルゴリズムを使用しないと、暗号化後のデータのパターンから暗号アルゴリズムが特定されてしまう等の課題があった。

情報処理装置であって、前記情報処理装置の第1の電力状態から前記情報処理装置の少なくとも一部に電力が供給されない第2の電力状態へ遷移する前に、前記情報処理装置が実行するアプリケーションの状態を示す情報を記憶する揮発性記憶手段と、前記揮発性記憶手段に記憶される前記アプリケーションの状態を示す情報を、前記情報処理装置が前記第2の電力状態である間保持する不揮発性記憶手段と、前記情報処理装置が前記第1の電力状態から前記第2の電力状態に移行する場合に、前記アプリケーションの状態を示す情報のうちの前記揮発性記憶手段の特定領域以外に記憶される情報を前記不揮発性記憶手段に暗号化せずに記憶し、続いて、前記アプリケーションの状態を示す情報のうちの前記揮発性記憶手段の前記特定領域に記憶される情報を暗号化して前記不揮発性記憶手段に記憶する制御を行う制御手段と、を備えることを特徴とする。

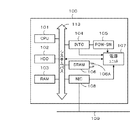

<システム構成の説明>

〔第1実施形態〕

本実施形態では、不揮発性記憶装置としてHDDを用いた例を記載するが、他の不揮発性記憶装置(例えば、SSD、USBメモリ)を用いても構わない。

なお、本実施形態では、アプリケーションの起動に際して、パスワード等の機密情報を入力する必要がある場合、当該機密情報を特定の情報として、かつ、RAM103上の特定の領域(暗号化対象領域202)で管理している。なお、複数のアプリケーションが起動している場合には、アプリケーションに対応づけられた特定の情報が複数記憶されている場合がある。

また、CPU101は、電源スイッチ(POW−SW)105により電源をオン状態へ遷移させる指示を受け付けた場合、HDD102に暗号化して退避させた特定の領域の情報については、復号化処理を実行してRAM103上に復帰させる制御を行う。さらに、CPU101は、暗号化していないアプリケーションに関わる情報についてはそのままRAM103上に復帰させる制御を行う。

したがって、当該特定の情報の復号化処理と、復帰処理については短時間に効率よく処理できる。

図2において、暗号化非対象領域201は、CPU101を動作させるためのプログラムやハイバネーション時に暗号化の必要がないデータが含まれている。特定領域に対応する暗号化対象領域202は、機密情報を含み、ハイバネーション時に暗号化が必要なデータが含まれている。

また、暗号アルゴリズムが使用する鍵情報も一時的にRAM103に保持する必要がある。その際は、暗号処理のために追加でRAM103領域が必要になるが、その場合は退避済の暗号化非対象領域201を使用してもよい。なお、RAM103の暗号化対象領域202のサイズや、アドレスを自動的に割り当てる構成とするが、暗号化処理の方式に応じてそのサイズ等を変更できるように構成してもよい。また、暗号化方式は、定期的に変更できるように構成してもよい。

また、暗号アルゴリズムにより、暗号化後のデータ長が変化する。データ長が大きくなる暗号アルゴリズムを使用する際にも、退避済の暗号化非対象領域201を使用してもよい。

そして、最後に、CPU101は、暗号化済の暗号化対象領域202をHDD102に退避する(S305)。全てのメモリ退避が完了した時点で、HDD102にメモリ退避した旨を示すハイバネーション情報を記録して(S306)、本処理を終了する。

図4は、本実施形態を示す情報処理装置の電力制御方法を説明するフローチャートである。本例は、ハイバネーション状態から復帰する際の処理例である。なお、各ステップは、CPU101がHDD102に記憶される制御プログラムを実行することで実現される。本実施形態では、通常電力状態に移行する要因があった場合に、特定にハイバネーションモードに基づく処理のうち、特に上述したアプリケーションの機能に必要な機密情報の管理処理と、暗号化、復元化処理に関わる処理について説明する。

ここで、通常の起動処理とは、HDD102に保存されたオペレーティングシステムの読み込みおよび初期化処理、デバイスドライバの読み込みおよび初期化処理、他のソフトウエアの読み込みおよび初期化処理などを指す。

一方、S401で、ハイバネーション情報が存在した場合(S401:Y)は、HDD102に退避されたRAM103の情報を復元する処理を開始する。

まず、暗号化対象領域202に記憶されていたデータをHDD102からRAM103へ復元する(402)。

そして、最後に暗号化非対象領域201に記憶されていたデータをHDD102からRAM103へ復元する(S404)。

この時点で、HDD102に退避していた全てのRAM103の情報が復元されたことになる。

その後、リジューム処理を行う(S405)。リジューム処理は、ハードウェア毎に初期設定を行ったり、終了処理302で保持された設定を再度ハードウェアに設定したりする処理を行う。

〔第2実施形態〕

終了処理が終了すると、CPU101は、RAM103の内容をHDD102に退避する処理を開始する。次に、CPU101は、上記特定領域以外に対応する暗号化非対象領域201をHDD102に退避する(S313)。そして、最後に、CPU101は、暗号化対象領域202をSRAM106に退避して(S315)、本処理を終了する。

図6は、本実施形態を示す情報処理装置の電力制御方法を説明するフローチャートである。本例は、ハイバネーション状態から復帰する際の処理例である。なお、各ステップは、CPU101がHDD102に記憶される制御プログラムを実行することで実現される。なお、図6に示したS401,S405,S406の処理に関しては、図4のフロー図の処理と同一なので割愛する。本実施形態では、特にハイバネーションモードに基づく処理のうち、特に上述したアプリケーションの機能に必要な機密情報の管理処理と、暗号化、復元化処理に関わる処理について説明する。

S401で、ハイバネーション情報が存在するとCPU101が判断した場合(S401:Y)は、CPU101は、HDD102に退避されたRAM103の情報を復元する処理を開始する。具体的には、CPU101は、暗号化対象領域202に記憶されていたデータをSRAM106からRAM103へ復元する(S412)。そして、最後に、CPU101は、暗号化非対象領域201をHDD102からRAM103へ復元して(S414)、本処理を終了する。

なお、上記実施形態では、POW−SW105がOFF指示を受け付けた場合に上述したハイバネーション処理を実行する例について説明した。しかしながら、図1に示すようにネットワーク対応の情報処理装置の場合、ジョブ等の受信状態を監視してハイバネーション処理を実現する構成にも本発明を適用可能である。

102 HDD

103 RAM

107 電源ユニット

Claims (7)

- 情報処理装置であって、

前記情報処理装置の第1の電力状態から前記情報処理装置の少なくとも一部に電力が供給されない第2の電力状態へ遷移する前に、前記情報処理装置が実行するアプリケーションの状態を示す情報を記憶する揮発性記憶手段と、

前記揮発性記憶手段に記憶される前記アプリケーションの状態を示す情報を、前記情報処理装置が前記第2の電力状態である間保持する不揮発性記憶手段と、

前記情報処理装置が前記第1の電力状態から前記第2の電力状態に移行する場合に、前記アプリケーションの状態を示す情報のうちの前記揮発性記憶手段の特定領域以外に記憶される情報を前記不揮発性記憶手段に暗号化せずに記憶し、続いて、前記アプリケーションの状態を示す情報のうちの前記揮発性記憶手段の前記特定領域に記憶される情報を暗号化して前記不揮発性記憶手段に記憶する制御を行う制御手段と、

を備えることを特徴とする情報処理装置。 - 前記制御手段は、前記情報処理装置が前記第2の電力状態から前記第1の電力状態に移行する場合に、前記不揮発性記憶手段に暗号化された記憶された情報を復号化して前記特定領域に記憶し、続いて、前記不揮発性記憶手段に暗号化されずに記憶された情報を前記特定領域以外の領域に記憶する、ことを特徴とする請求項1記載の情報処理装置。

- 前記不揮発性記憶手段は、ハードディスクであることを特徴とする請求項1記載の情報処理装置。

- 前記不揮発性記憶手段は、電池を用いて情報を保持する半導体メモリであることを特徴とする請求項1記載の情報処理装置。

- 前記半導体メモリは、前記情報処理装置に対して着脱可能なコントローラボードに設けることを特徴とする請求項4記載の情報処理装置。

- 揮発性記憶手段と不揮発性記憶手段とを有する情報処理装置の制御方法であって、

前記情報処理装置の第1の電力状態から前記情報処理装置の少なくとも一部に電力が供給されない第2の電力状態へ遷移する前に、前記情報処理装置が実行するアプリケーションの状態を示す情報を前記揮発性記憶手段に記憶する揮発性記憶工程と、

前記揮発性記憶手段に記憶される前記アプリケーションの状態を示す情報を、前記情報処理装置が前記第2の電力状態である間前記不揮発性記憶手段に保持する不揮発性記憶工程と、

前記情報処理装置が前記第1の電力状態から前記第2の電力状態に移行する場合に、前記アプリケーションの状態を示す情報のうちの前記揮発性記憶手段の特定領域以外に記憶される情報を前記不揮発性記憶手段に暗号化せずに記憶し、続いて、前記アプリケーションの状態を示す情報のうちの前記揮発性記憶手段の前記特定領域に記憶される情報を暗号化して前記不揮発性記憶手段に記憶する制御を行う制御工程と、

を備えることを特徴とする情報処理装置の制御方法。 - 請求項6記載の情報処理装置の制御方法をコンピュータに実行させることを特徴とするプログラム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012164610A JP6095289B2 (ja) | 2012-07-25 | 2012-07-25 | 情報処理装置、情報処理装置の制御方法、及びプログラム |

| US13/948,559 US9460297B2 (en) | 2012-07-25 | 2013-07-23 | Information processing apparatus, control method for information processing apparatus, and storage medium |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012164610A JP6095289B2 (ja) | 2012-07-25 | 2012-07-25 | 情報処理装置、情報処理装置の制御方法、及びプログラム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014026374A JP2014026374A (ja) | 2014-02-06 |

| JP2014026374A5 JP2014026374A5 (ja) | 2015-09-10 |

| JP6095289B2 true JP6095289B2 (ja) | 2017-03-15 |

Family

ID=49996137

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012164610A Active JP6095289B2 (ja) | 2012-07-25 | 2012-07-25 | 情報処理装置、情報処理装置の制御方法、及びプログラム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9460297B2 (ja) |

| JP (1) | JP6095289B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6547306B2 (ja) | 2015-01-27 | 2019-07-24 | 富士ゼロックス株式会社 | 情報処理装置、データ退避方法およびプログラム |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10260912A (ja) * | 1997-03-17 | 1998-09-29 | Mitsubishi Electric Corp | メモリカード |

| JP3453498B2 (ja) * | 1997-08-27 | 2003-10-06 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 情報処理装置及び省電力装置 |

| JP2001202167A (ja) * | 2000-01-20 | 2001-07-27 | Toyo Commun Equip Co Ltd | コンピュータ及びその制御方法 |

| JP2001297038A (ja) * | 2000-04-11 | 2001-10-26 | Toshiba Corp | データ記憶装置および記録媒体並びに記録媒体制御方法 |

| US7210045B2 (en) * | 2003-08-19 | 2007-04-24 | Intel Corporation | Storing encrypted and/or compressed system context information when entering a low-power state |

| JP2006252021A (ja) * | 2005-03-09 | 2006-09-21 | Ricoh Co Ltd | データ保護機能付不揮発性記憶装置 |

| US20070101158A1 (en) * | 2005-10-28 | 2007-05-03 | Elliott Robert C | Security region in a non-volatile memory |

| GB2446658B (en) | 2007-02-19 | 2011-06-08 | Advanced Risc Mach Ltd | Hibernating a processing apparatus for processing secure data |

| JP2010214904A (ja) * | 2009-03-18 | 2010-09-30 | Ricoh Co Ltd | 画像形成装置 |

-

2012

- 2012-07-25 JP JP2012164610A patent/JP6095289B2/ja active Active

-

2013

- 2013-07-23 US US13/948,559 patent/US9460297B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20140032936A1 (en) | 2014-01-30 |

| US9460297B2 (en) | 2016-10-04 |

| JP2014026374A (ja) | 2014-02-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101565223B1 (ko) | 인플레이스 암호화 시스템 및 방법 | |

| US8775824B2 (en) | Protecting the security of secure data sent from a central processor for processing by a further processing device | |

| US8862898B2 (en) | Secure environment management during switches between different modes of multicore systems | |

| KR102013841B1 (ko) | 데이터의 안전한 저장을 위한 키 관리 방법 및 그 장치 | |

| CN109684030B (zh) | 虚拟机内存密钥生成装置、以及方法、加密方法和SoC系统 | |

| EP2874151B1 (en) | Method and apparatus for controlling access to encrypted data | |

| EP2062191B1 (en) | System and method for securely restoring a program context from a shared memory | |

| US8713328B2 (en) | Code conversion apparatus, code conversion method, and computer product | |

| WO2006099785A1 (fr) | Puce de sécurité | |

| JP2008226158A (ja) | 情報処理装置、ソフトウェア更新方法及び画像処理装置 | |

| WO2005004382A1 (ja) | 暗号処理装置 | |

| JP2006018685A (ja) | マルチタスク実行システム | |

| KR20190014444A (ko) | 보안 장치, 이를 포함하는 전자 장치 및 전자 장치의 동작 방법 | |

| US9037868B2 (en) | System and method for protecting information and related encryption keys | |

| US11531626B2 (en) | System and method to protect digital content on external storage | |

| EP3777017B1 (en) | Ephemeral regions within non-volatile memory devices | |

| JP6095289B2 (ja) | 情報処理装置、情報処理装置の制御方法、及びプログラム | |

| CN108475316B (zh) | 使数据安全 | |

| JP2016111391A (ja) | メモリデバイス | |

| JP2009025947A (ja) | バックアップシステム | |

| JP4784105B2 (ja) | 情報処理装置およびその制御方法、情報管理システム | |

| JP5370695B2 (ja) | 記憶装置制御システム及び記憶装置制御システムの記憶装置管理方法 | |

| JP2014026374A5 (ja) | ||

| KR101639059B1 (ko) | 저전력 데이터 보안 장치 및 이를 이용한 저전력 데이터 보안 방법 | |

| JP2008112306A (ja) | 情報処理装置および情報処理方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150722 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150722 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20150724 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160630 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160719 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160916 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170117 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170214 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6095289 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |