JP6071296B2 - 通信制御装置及び通信制御方法 - Google Patents

通信制御装置及び通信制御方法 Download PDFInfo

- Publication number

- JP6071296B2 JP6071296B2 JP2012161268A JP2012161268A JP6071296B2 JP 6071296 B2 JP6071296 B2 JP 6071296B2 JP 2012161268 A JP2012161268 A JP 2012161268A JP 2012161268 A JP2012161268 A JP 2012161268A JP 6071296 B2 JP6071296 B2 JP 6071296B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- communication

- address

- current data

- communication control

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30145—Instruction analysis, e.g. decoding, instruction word fields

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05B—CONTROL OR REGULATING SYSTEMS IN GENERAL; FUNCTIONAL ELEMENTS OF SUCH SYSTEMS; MONITORING OR TESTING ARRANGEMENTS FOR SUCH SYSTEMS OR ELEMENTS

- G05B19/00—Programme-control systems

- G05B19/02—Programme-control systems electric

- G05B19/04—Programme control other than numerical control, i.e. in sequence controllers or logic controllers

- G05B19/042—Programme control other than numerical control, i.e. in sequence controllers or logic controllers using digital processors

- G05B19/0428—Safety, monitoring

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05B—CONTROL OR REGULATING SYSTEMS IN GENERAL; FUNCTIONAL ELEMENTS OF SUCH SYSTEMS; MONITORING OR TESTING ARRANGEMENTS FOR SUCH SYSTEMS OR ELEMENTS

- G05B2219/00—Program-control systems

- G05B2219/20—Pc systems

- G05B2219/23—Pc programming

- G05B2219/23282—Detect erroneous instructions in asic systems

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L1/00—Arrangements for detecting or preventing errors in the information received

- H04L1/08—Arrangements for detecting or preventing errors in the information received by repeating transmission, e.g. Verdan system

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Automation & Control Theory (AREA)

- General Engineering & Computer Science (AREA)

- Communication Control (AREA)

- Information Transfer Systems (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

Description

このような装置が、以下の各段階により通信制御を行う。

(1)前記保持手段に保管される前記前回データと今回の通信により受信した今回データとの内容を比較する段階。

(2)前記比較の結果、前記前回データと前記今回データとの内容が一致するときに、前記今回データの書き込み先のアドレスが前記領域であるか否かを確認する段階。

(3)前記今回データの書き込み先のアドレスが前記領域であれば、前記今回データの前記記憶手段への書き込みを禁止する段階。

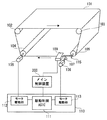

図1は、本実施形態のシリアル通信システムを用いた画像形成装置に内蔵される、中間転写ベルト(以下、「ITB(Intermediate Transfer Belt)」という。)の駆動制御機構の構成図である。

ITB101は、ITB駆動ローラ104とITB寄り制御ローラ105、及びこれらのローラに従動する従動ローラ102、103の回転に伴い回転駆動される。また、ITB101は、これらのローラにより、寄り制御される。ITB駆動ローラ104は、ITB駆動モータ106により回転駆動される。ITB寄り制御ローラ105は、ITB寄り制御モータ108により駆動されるITB寄り制御用偏心カム107及びITB寄り制御レバー115によりITB101の寄りを制御する。ベルト位置検出センサ109は、ITB101のベルト位置をアナログ値で検出する。

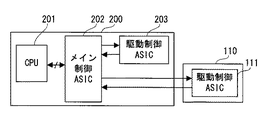

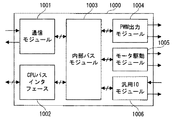

ASIC1000は、通信モジュール1001、CPUバスインタフェース1002、内部バスモジュール1003、PWM出力モジュール1004、モータ駆動モジュール1005、及び汎用IOモジュール1006を備える。

シリアル−パラレル変換部1101は、受信したシリアルデータをパラレルデータに変換する。パラレル−シリアル変換部1102は、パラレルデータをシリアルデータに変換して送信する。通信制御部1103は、通信モジュール1001内の各部間の通信制御を行う。内部バスインタフェース部1104は、図4の内部バスモジュール1003に接続される。レジスタ部1105は、設定値などを記憶する。

CRCが不一致となるのは、例えば、送信中にデータに対してノイズが混入し、データの特定のビットが反転したと認識された場合などである。

CRCは、巡回冗長検査と呼ばれ、任意長のデータ入力に対して固定サイズの値を出力する関数であり、連続する誤りを検出するための誤り検出符号の一種である。パリティ・チェックサム方式に比べて誤り検出精度が高く、高速に演算できる。また、1ビットずつの走査により計算ができるために、ハードウェア構成が容易に済むなどの特徴を持つ。そのために、ネットワークからハードウェア回路におけるデータ転送に幅広く用いられる。

主局は、フレームデータを従局に送信すると、従局からのACKコマンド又はNACKコマンドの送信待機状態になる(S501、S502)。所定の時間内にACKコマンド又はNACKコマンドを受信した場合に主局は、受信したコマンドがACKコマンドであるかを確認する(S502:Y、S503)。ACKコマンドである場合に主局は、通信が成功したと判断して送信処理を終了する(S503:Y)。

所定の時間を経過してもACKコマンド又はNACKコマンドを受信しない場合(S502:N、S504)、或いはNACKコマンドを受信した場合(S503:N)に、主局は、通信が失敗したと判断してフレームデータを再送する(S505)。

CRCによる誤り検出は、図6の通常のライト実行時と同様であり、その結果に応じてACKコマンドあるいはNACKコマンドが従局から主局に送られる。主局は、これにより通信の成否を判断し、失敗している場合に、データの再送を行う。

CRCによる誤り検出は、図7の通常のリード実行時と同様であり、その結果に応じてACKコマンドあるいはNACKコマンドが従局から主局に送られる。主局は、これにより通信の成否を判断して、失敗している場合に、データの送信を行う。成功している場合に主局は、受信したデータに対してCRCによる誤り検出を行う。主局は、検出の結果受信したデータに誤りがあれば、データの送信を行う。

バーストライト実行時には、データのフレームデータを格納する格納部に、連続転送されるデータの最後のデータが格納される。バーストライト時に送信されるデータをすべて格納することにすると、格納部の容量が大きくなって回路規模が増大する。そのために、回路規模をできるだけ小さくするように、最後のデータのみを格納することとする。

例えば、ITB101の寄り制御の場合、モータ駆動モジュール1005の動作設定レジスタに対する2回連続のライト実行が、結果として、寄り制御の効果が低減、もしくはITB101の寄り切りという、意図した動作を阻害することになる。

通信制御部1103は、フレームデータが一致する場合、図6〜図9に示す通信プロトコルに基づく通信の終了まで、S401の処理を繰り返す(S401:Y、S402)。つまり、S401、S402では、図6〜図9の各通信プロトコルに従い受信したコマンド、アドレス、データ(ライト時のみ)、CRCの各フレームデータが、前回の通信により受信したフレームデータとまったく同じデータであるかを判断する。同一アドレスに対する同一データのライト実行あるいは同一アドレスへのリード実行でない限り、意図しない2回連続ライト実行あるいはリード実行が発生しないため、ステップS408へと移行する。本実施形態では、コマンド、アドレス、データ、CRCのそれぞれを受信するごとに、一時格納部に格納されている対応するデータと比較する。通信完了後に受信したフレームデータと、一時格納部に格納されているフレームデータとを比較するようにしてもかまわない。

通信エラーが発生していない(正常にフレームデータを受信した)場合、通信制御部1103は、一時格納部の内容を今回受信した最新のデータに更新するとともに、主局にACKコマンドを送信する(S406:N、S407、S409)。そして、フレームデータで指示された処理を実行する。

このようにして、特定アドレスへの2回連続のアクセスを防止する。

前回とは異なるコマンドである場合には、CRCを用いた通信エラーの確認処理に移行する(S403:N、S406)。

Claims (6)

- 被制御装置の動作を制御するためのデータが記憶される記憶手段と、

前記記憶手段への書き込み先のアドレスを含む前記データを通信により受信する受信手段と、

前回の通信により受信したデータを保持する保持手段と、

前記保持手段に保持された前記前回の通信により受信された前回データと、今回の通信により受信した今回データとの内容が一致した場合、前記今回データの前記記憶手段への書き込み先のアドレスが所定のアドレスであれば前記今回データの前記記憶手段への書き込みを禁止し、前記今回データの前記記憶手段への書き込み先のアドレスが前記所定のアドレスでなければ、前記今回データを前記記憶手段へ書き込む通信制御手段と、を備えることを特徴とする、

通信制御装置。 - 前記記憶手段における前記所定のアドレスは、前記被制御装置であるモータの動作を制御するための動作設定レジスタに対応することを特徴とする、

請求項1記載の通信制御装置。 - 前記通信制御手段は、前記前回データの受信終了から前記今回データの受信終了までの時間を測定し、測定した時間が予め定められた時間以上であれば、前記前回データと前記今回データとの内容が一致しかつ前記今回データの書き込み先のアドレスが前記所定のアドレスを指している場合であっても、前記今回データの前記記憶手段への書き込みを許可することを特徴とする、

請求項1または2記載の通信制御装置。 - 前記データは誤り検出符号を含んでおり、

前記通信制御手段は、前記今回データの前記記憶手段への書き込みが許可されているときに、前記今回データの前記誤り検出符号を用いたデータ誤り検出を行い、データに誤りが無ければ、前記記憶手段への書き込みを行うとともに、前記保持手段に保持されているデータを前記今回データに更新することを特徴とする、

請求項3記載の通信制御装置。 - 前記受信手段は、受信した前記データを内部バスを介して前記記憶手段に送信するものであり、

前記通信制御手段は、前記記憶手段への書き込みを禁止するときに、前記受信手段による前記データの前記内部バスへの送信を禁止することを特徴とする、

請求項4記載の通信制御装置。 - 被制御装置の動作を制御するためのデータが記憶され、前記データの書き込みが重複することで前記被制御装置に不安定な動作が生じる可能性のある領域を有する記憶手段、前記記憶手段への書き込み先のアドレスを含む前記データを通信により受信する受信手段、及び前回の通信により受信した前回データを保持する保持手段を備える装置により実行される方法であって、

前記保持手段に保管される前記前回データと今回の通信により受信した今回データとの内容を比較する段階と、

前記比較の結果、前記前回データと前記今回データとの内容が一致するときに、前記今回データの書き込み先のアドレスが前記領域であるか否かを確認する段階と、

前記今回データの書き込み先のアドレスが前記領域であれば、前記今回データの前記記憶手段への書き込みを禁止する段階と、を含むことを特徴とする、

通信制御方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012161268A JP6071296B2 (ja) | 2012-07-20 | 2012-07-20 | 通信制御装置及び通信制御方法 |

| US13/940,094 US9286070B2 (en) | 2012-07-20 | 2013-07-11 | Control apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012161268A JP6071296B2 (ja) | 2012-07-20 | 2012-07-20 | 通信制御装置及び通信制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014023013A JP2014023013A (ja) | 2014-02-03 |

| JP6071296B2 true JP6071296B2 (ja) | 2017-02-01 |

Family

ID=49947576

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012161268A Active JP6071296B2 (ja) | 2012-07-20 | 2012-07-20 | 通信制御装置及び通信制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9286070B2 (ja) |

| JP (1) | JP6071296B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6303907B2 (ja) | 2014-08-08 | 2018-04-04 | 株式会社デンソー | 運転者監視装置 |

| FR3026515B1 (fr) * | 2014-09-26 | 2017-12-01 | Valeo Systemes Thermiques | Transmission de donnees synchrones par l'intermediaire d'un bus de donnees serie, notamment un bus spi |

| US10841039B2 (en) * | 2018-10-30 | 2020-11-17 | Infineon Technologies Ag | System and method for transferring data and a data check field |

| JP2021168431A (ja) * | 2020-04-09 | 2021-10-21 | ミネベアミツミ株式会社 | チェックサム付加方法およびチェックサム付加装置 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS64833A (en) * | 1987-02-12 | 1989-01-05 | Matsushita Electric Ind Co Ltd | Data transmission equipment |

| US5384565A (en) * | 1992-08-03 | 1995-01-24 | Motorola, Inc. | Method and apparatus for identifying duplicate data messages in a communication system |

| JP2000041057A (ja) | 1998-07-21 | 2000-02-08 | Canon Inc | シリアル通信システムと通信データの制御方法、及び画像形成装置 |

| JP2006191188A (ja) * | 2004-12-28 | 2006-07-20 | Sharp Corp | 画像転送装置および画像表示装置 |

| JP2007148592A (ja) * | 2005-11-24 | 2007-06-14 | Funai Electric Co Ltd | データ通信装置 |

| JP2007317263A (ja) | 2006-05-24 | 2007-12-06 | Hitachi Global Storage Technologies Netherlands Bv | シリアル・データ転送方法、そのシステム及びデータ記憶装置 |

| WO2010061482A1 (ja) * | 2008-11-28 | 2010-06-03 | 株式会社アドバンテスト | 試験装置、シリアル伝送システム、プログラム、および、記録媒体 |

| JP2011008879A (ja) * | 2009-06-26 | 2011-01-13 | Toshiba Storage Device Corp | ディスクドライブ装置 |

| JP5609443B2 (ja) * | 2009-09-30 | 2014-10-22 | 富士通株式会社 | 再送制御を行う装置及び方法 |

-

2012

- 2012-07-20 JP JP2012161268A patent/JP6071296B2/ja active Active

-

2013

- 2013-07-11 US US13/940,094 patent/US9286070B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US9286070B2 (en) | 2016-03-15 |

| JP2014023013A (ja) | 2014-02-03 |

| US20140025936A1 (en) | 2014-01-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6071296B2 (ja) | 通信制御装置及び通信制御方法 | |

| US10153887B2 (en) | Patch download with improved acknowledge mechanism | |

| US20230379085A1 (en) | Method for controlling retransmission in physical layer | |

| CN112395237B (zh) | 一种至少两个控制器之间通信的方法及其系统 | |

| JP5250767B2 (ja) | 冗長3ワイヤ通信システムおよび方法 | |

| JP4508732B2 (ja) | 電子制御装置 | |

| RU2740163C2 (ru) | Устройство связи, способ связи, программа и система связи | |

| CN107852275B (zh) | 数据传输装置和数据传输方法、接收装置和接收方法 | |

| US8880972B2 (en) | Serial transmission apparatus, information processing apparatus, and serial transmission method | |

| CN111327393A (zh) | 一种基于串行通讯接口的图像探测器参数传输方法 | |

| CN114138542A (zh) | 电能表的数据配置方法、电能表及可读存储介质 | |

| JP4458873B2 (ja) | シリアルデータ転送方法とその装置 | |

| TW202103466A (zh) | 實施混合自動重傳請求過程的系統及方法 | |

| JP2017208713A (ja) | 通信装置、通信方法、プログラム、および、通信システム | |

| JP2020061655A (ja) | 通信システム | |

| JP2011039897A (ja) | データ通信装置、データ通信制御方法、データ通信制御プログラム及び記録媒体 | |

| JP3852600B2 (ja) | 通信インタフェース装置およびプログラム | |

| WO2022086798A1 (en) | Repeated in sequence packet transmission for checksum comparison | |

| CN117278173A (zh) | 一种ota数据的传输系统及车辆 | |

| US20160218984A1 (en) | Communication device and control method of communication device | |

| JP2003324497A (ja) | 通信システム及び通信制御装置 | |

| JPS63246055A (ja) | パケツト送受信装置 | |

| JP6734031B2 (ja) | 送信装置、送受信システム、送信方法およびプログラム | |

| JP2020025194A (ja) | 情報処理装置、情報処理システム、情報処理方法、及びプログラム | |

| JPH11234364A (ja) | 通信制御方法及び通信モジュール |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150714 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160414 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160426 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160627 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20161206 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20161227 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6071296 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |