JP5960993B2 - 複数のインタフェースタイプおよび終端をサポートするフィールドバスインタフェース回路基板 - Google Patents

複数のインタフェースタイプおよび終端をサポートするフィールドバスインタフェース回路基板 Download PDFInfo

- Publication number

- JP5960993B2 JP5960993B2 JP2012009513A JP2012009513A JP5960993B2 JP 5960993 B2 JP5960993 B2 JP 5960993B2 JP 2012009513 A JP2012009513 A JP 2012009513A JP 2012009513 A JP2012009513 A JP 2012009513A JP 5960993 B2 JP5960993 B2 JP 5960993B2

- Authority

- JP

- Japan

- Prior art keywords

- section

- termination

- transceiver

- interface

- types

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 claims description 13

- 238000013507 mapping Methods 0.000 claims description 4

- 230000006870 function Effects 0.000 description 5

- 238000010586 diagram Methods 0.000 description 4

- 229940102240 option 2 Drugs 0.000 description 4

- 238000004590 computer program Methods 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- 230000000644 propagated effect Effects 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000004075 alteration Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000000835 fiber Substances 0.000 description 1

- 238000003780 insertion Methods 0.000 description 1

- 230000037431 insertion Effects 0.000 description 1

- 239000013307 optical fiber Substances 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 230000032258 transport Effects 0.000 description 1

- 238000012795 verification Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/382—Information transfer, e.g. on bus using universal interface adapter

- G06F13/385—Information transfer, e.g. on bus using universal interface adapter for adaptation of a particular data processing system to different peripheral devices

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

- G06F13/4063—Device-to-bus coupling

- G06F13/4068—Electrical coupling

- G06F13/4086—Bus impedance matching, e.g. termination

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Dc Digital Transmission (AREA)

- Combinations Of Printed Boards (AREA)

- Small-Scale Networks (AREA)

Description

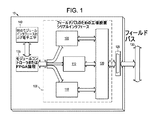

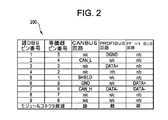

100 インタフェース回路基板

105、115、UT1、UT2、UT3 トランシーバセクション

110、T 終端セクション

120 行列セクション

125 接続セクション

130 フィールドバス

135 コントローラセクション

140 インタフェース/電子工学

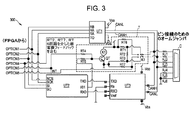

300 回路

RT1、RT2、RT3、RT4、RT5、RT6、RT7 抵抗器

K1 継電器

QT トランジスタ

OPTION1、OPTION2、OPTION3、OPTION4、OPTION5、OPTION6 入力線

RJ1、RJ2、RJ3、RJ4、RJ5、RJ6 出力線

C 外部コネクタ

VBS フローティング供給電圧

VCO 制御電圧

CANL 信号

CANH 出力

Claims (9)

- インタフェース回路基板装置であって、

共有回路基板(100)ベースと、

前記回路基板(100)ベースの上に配置されたトランシーバセクション(115)であって、複数のトランシーバコンポーネントタイプを受け取る回路トランシーバサイトを有するトランシーバセクション(115)と、

前記回路基板(100)ベースの上に配置された終端セクション(110)であって、複数の終端コンポーネントタイプを受け取る回路終端サイトを有する終端セクション(110)と、

前記トランシーバおよび終端セクション(115、110)に動作結合された接続セクション(125)と、

前記トランシーバおよび前記終端セクション(110)と、前記接続セクション(125)との間に配置された手動設定変更可能なジャンパのセクションと、

を備え、

前記手動設定変更可能なジャンパは、特定の接続タイプの信号マッピングをサポートするように、製造時に設定され、

前記トランシーバセクション(115)、前記終端セクション(110)および前記手動設定変更可能なジャンパのセクションは、前記複数のトランシーバコンポーネントタイプおよび前記複数の終端コンポーネントタイプに基づく複数のインターフェイスタイプをサポートするための電気接続サイトを含み、

第1の組のトランシーバコンポーネントおよび終端コンポーネントが、第1のインターフェイスタイプをサポートするために、前記トランシーバセクションおよび前記終端セクションに搭載され、

第2の組のトランシーバコンポーネントおよび終端コンポーネントが、第2のインターフェイスタイプをサポートするために、前記トランシーバセクションおよび前記終端セクションに搭載され、

前記第2の組のトランシーバコンポーネントおよび終端コンポーネントは、前記第1の組のトランシーバコンポーネントおよび終端コンポーネントと異なる、

インタフェース回路基板装置。 - 前記手動設定変更可能なジャンパのセクションが、前記トランシーバセクション(115)と前記接続セクション(125)の間に配置される、請求項1に記載の装置。

- 前記手動設定変更可能なジャンパのセクションが、インタフェース信号を前記接続セクション(125)に配置されたコネクタに向けて経路指定する電気接続を提供する、請求項1または2に記載の装置。

- 前記手動設定変更可能なジャンパのセクションが、前記複数のインタフェースタイプをサポートするジャンパ接続サイトを含み、

前記複数のインタフェースタイプの各々が、前記コネクタへの独自の信号マッピングを有する、

請求項3に記載の装置。 - 前記トランシーバセクション(115)および前記終端セクション(110)が複数のコントローラ信号入力を受け取る電気接続を有し、

前記コントローラ信号入力の各々が前記複数のインタフェースタイプのうちの選択されたインタフェースタイプに基づく独自の構成を有する、

請求項1から4のいずれかに記載の装置。 - 前記終端セクション(110)が、前記複数のインタフェースタイプのための複数の終端タイプをサポートする電気接続を有する、請求項1から5のいずれかに記載の装置。

- 前記終端セクション(110)が、前記複数のインタフェースタイプの各々のための終端をサポートするように構成された複数の終端抵抗器を含む、請求項6に記載の装置。

- 前記終端セクション(110)が、前記終端抵抗器と前記接続セクションとの間に配置され、継電器が閉じると全ての前記終端抵抗器を前記接続セクションに接続するように前記継電器を含む、請求項7に記載の装置。

- 前記トランシーバセクション(115)が、前記複数のインタフェースタイプをサポートするように構成された1つまたは複数のトランシーバタイプをサポートする電気接続を有する、請求項1から8のいずれかに記載の装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/012,376 US8625295B2 (en) | 2011-01-24 | 2011-01-24 | Fieldbus interface circuit board supporting multiple interface types and terminations |

| US13/012,376 | 2011-01-24 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012155719A JP2012155719A (ja) | 2012-08-16 |

| JP2012155719A5 JP2012155719A5 (ja) | 2015-02-26 |

| JP5960993B2 true JP5960993B2 (ja) | 2016-08-02 |

Family

ID=45562708

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012009513A Active JP5960993B2 (ja) | 2011-01-24 | 2012-01-20 | 複数のインタフェースタイプおよび終端をサポートするフィールドバスインタフェース回路基板 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8625295B2 (ja) |

| EP (1) | EP2479678B1 (ja) |

| JP (1) | JP5960993B2 (ja) |

| CN (1) | CN102693204B (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014115756A (ja) * | 2012-12-07 | 2014-06-26 | Tamagawa Seiki Co Ltd | 通信方式選択回路及びその方法 |

| BR112016015581A2 (pt) * | 2014-01-03 | 2017-08-08 | Phoenix Contact Development And Mfg Inc | Acoplador de barramento de campo |

| US9840220B2 (en) | 2015-04-27 | 2017-12-12 | L & B Manufacturing, Inc. | Wireless airbag control system |

| FR3038807B1 (fr) | 2015-07-09 | 2017-07-21 | Continental Automotive France | Dispositif d'emetteur-recepteur apte a etre connecte sur un reseau de communication par bus de type can ou flexray |

| BE1026569B1 (de) | 2018-08-27 | 2020-03-23 | Phoenix Contact Gmbh & Co | Steuer- und Datenübertragungsanlage zur Unterstützung verschiedener Kommunikationsprotokolle und ein Adaptermodul |

| CN108965118B (zh) * | 2018-08-31 | 2021-04-16 | 杭州和利时自动化有限公司 | 一种dp转ff通信网关及dp转ff的方法 |

| DE102018121885A1 (de) * | 2018-09-07 | 2020-03-12 | Phoenix Contact Gmbh & Co. Kg | Elektronisches Gerät zum Einsatz in einem Automatisierungssystem sowie ein Automatisierungssystem |

| EP4099640A1 (en) | 2021-06-03 | 2022-12-07 | Nxp B.V. | Transceiver device |

| EP4099641A1 (en) * | 2021-06-03 | 2022-12-07 | Nxp B.V. | Transceiver device |

| CN113848788B (zh) * | 2021-09-27 | 2022-12-02 | 厦门四信通信科技有限公司 | 一种扩展电路及系统 |

| CN114281743A (zh) * | 2021-11-29 | 2022-04-05 | 浪潮(山东)计算机科技有限公司 | 一种pcie转rs232接口和ttl接口的装置、方法及存储介质 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4124889A (en) * | 1975-12-24 | 1978-11-07 | Computer Automation, Inc. | Distributed input/output controller system |

| US5832244A (en) * | 1996-02-20 | 1998-11-03 | Iomega Corporation | Multiple interface input/output port for a peripheral device |

| US6088754A (en) * | 1997-12-31 | 2000-07-11 | Cisco Technology, Inc. | Generic serial interface with automatic reconfigurability |

| US6334160B1 (en) * | 1999-01-28 | 2001-12-25 | Hewlett-Packard Co. | Apparatus and method for providing multiple protocols through a common connector in a device |

| US6740821B1 (en) | 2002-03-01 | 2004-05-25 | Micron Technology, Inc. | Selectively configurable circuit board |

| US7035773B2 (en) * | 2002-03-06 | 2006-04-25 | Fisher-Rosemount Systems, Inc. | Appendable system and devices for data acquisition, analysis and control |

| US6839790B2 (en) | 2002-06-21 | 2005-01-04 | Smar Research Corporation | Plug and play reconfigurable USB interface for industrial fieldbus network access |

| US7246194B2 (en) * | 2003-01-30 | 2007-07-17 | Rosemount, Inc. | Interface module for use with a fieldbus device network and with internet and non-internet based process control networks |

| US7245501B2 (en) | 2003-09-09 | 2007-07-17 | Hewlett-Packard Development Company, L.P. | Configurable circuit board and fabrication method |

| TWI321414B (en) | 2004-10-15 | 2010-03-01 | Sony Computer Entertainment Inc | Methods and apparatus for supporting multiple configurations in a multi-processor system |

| CN2811962Y (zh) * | 2005-07-18 | 2006-08-30 | 北京金自天正智能控制股份有限公司 | 一种基于Profibus-DP现场总线的同步电机状态检测仪 |

| CN2884280Y (zh) * | 2005-11-09 | 2007-03-28 | 沈阳新松机器人自动化股份有限公司 | 现场总线位置控制装置 |

| US7715433B2 (en) * | 2006-07-14 | 2010-05-11 | Boren Gary W | Universal controller and signal monitor |

| US20080065805A1 (en) * | 2006-09-11 | 2008-03-13 | Cameo Communications, Inc. | PCI-Express multimode expansion card and communication device having the same |

| US20090282437A1 (en) * | 2008-05-09 | 2009-11-12 | Tap.Tv | System and Method for Controlling Media at a Plurality of Output Devices |

-

2011

- 2011-01-24 US US13/012,376 patent/US8625295B2/en active Active

-

2012

- 2012-01-10 EP EP12150538.2A patent/EP2479678B1/en active Active

- 2012-01-20 JP JP2012009513A patent/JP5960993B2/ja active Active

- 2012-01-29 CN CN201210026067.3A patent/CN102693204B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN102693204B (zh) | 2016-06-15 |

| US20120188731A1 (en) | 2012-07-26 |

| US8625295B2 (en) | 2014-01-07 |

| JP2012155719A (ja) | 2012-08-16 |

| EP2479678A2 (en) | 2012-07-25 |

| EP2479678B1 (en) | 2016-10-12 |

| EP2479678A3 (en) | 2013-09-11 |

| CN102693204A (zh) | 2012-09-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5960993B2 (ja) | 複数のインタフェースタイプおよび終端をサポートするフィールドバスインタフェース回路基板 | |

| CN108302742B (zh) | 空调机组的控制器和空调器 | |

| JP2012234582A (ja) | 非対称ユニバーサルシリアルバス通信 | |

| CN104054064B (zh) | 基于接口耦合的灵活的端口配置 | |

| CN107391419B (zh) | 支持多主机的通用序列汇流排集线设备及车用主机 | |

| CN101436170A (zh) | Spi设备通信电路 | |

| US10271113B2 (en) | Chassis switch using distributed backplane to interconnect line cards | |

| CN101539900A (zh) | 解决具有相同定址地址的两i2c从属装置间产生冲突的装置 | |

| CN204904151U (zh) | 一种内置式转接卡 | |

| CN204883525U (zh) | 一种外置式转接卡 | |

| CN105703935B (zh) | 具自动切换共享网络功能的服务器系统 | |

| JP2010028670A5 (ja) | ||

| CN109561032B (zh) | 一种交换机模块及包括其的交换机 | |

| US8131903B2 (en) | Multi-channel memory connection system and method | |

| CN117742451A (zh) | 一种板卡 | |

| CN211124034U (zh) | 多路采集卡及具有其的服务器 | |

| JP2008522550A (ja) | マルチレート光トランスポンダ | |

| EA013318B1 (ru) | Способ и устройство для организации подключений в гирляндной конфигурации | |

| US20120036294A1 (en) | Computer integrated display integrated display and control method of the same | |

| CN107515833A (zh) | 用于存储设备的输入输出卡以及存储设备 | |

| CN105515607A (zh) | 通信电路 | |

| US8583849B2 (en) | Signal switch connector set applied to motherboard of computer system | |

| CN210123977U (zh) | 中继线缆及增强现实系统 | |

| CN210270889U (zh) | 智能分析扩展设备及服务器 | |

| US7668985B2 (en) | Information processing apparatus with upgradeable modular components including processor, system memory, and hard disk drives |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150113 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150113 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20151111 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151117 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160212 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160531 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160624 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5960993 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |