以下、本発明の実施の形態を図面を参照して詳細に説明する。

[第1の実施形態]

第1の実施形態では、画像処理パラメータ(例えば、FIRフィルタにおけるフィルタ係数)を画像端の周辺領域で制御する技術について説明する。

図1は、本発明の第1の実施形態に係る画像処理装置の構成例を示すブロック図である。

図1において、101は、例えば、FIRフィルタ等で構成され、入力画像データ(INDAT)が入力されると、出力画像データ(OUTDAT)を出力する画像処理部である。102は、画像領域の位置情報を制御する画像領域制御部であり、画像処理部101にOUTWINを出力し、係数選択値生成部103にKWINを出力する。OUTWINは画像出力領域を表す制御信号である。KWINはFIRフィルタの係数切り替えを画像領域によって行うための制御信号である。画像処理部101にOUTWINが入力され、出力画像領域が制御される。

係数選択値生成部103は、画像領域制御部102からKWINが入力され、画像領域に従った係数選択値KSELを生成する。係数組選択制御部105は、係数組選択値KSETSELを生成してセレクタ(MUX)104に出力する。

106〜108は、FIRフィルタの係数の組テーブルである。本実施形態では、係数テーブル1_106〜係数テーブルM108のM種類の係数テーブルがあるものとする。

セレクタ104は、係数組選択制御部105から入力される係数組選択値KSETSELに応じて、係数テーブル1_106〜係数テーブルM108から所定の係数(K1〜KN)を選択する。選択されたN個の係数K1〜KNは、FIR係数として、セレクタ104から画像処理部101に出力される。

図2は、図1の画像処理装置を搭載した撮像装置4100の構成例を示すブロック図である。本実施形態では、図1に示す画像処理装置を図2の画像処理部424として説明する。

図2において、4103はフォーカスレンズを含む撮影レンズ、4101は絞り機能を備えるシャッター、422は光学像を電気信号に変換するCCDやCMOS素子等で構成される撮像部である。4102はバリアであり、撮影レンズ4103を含む撮像系を覆うことにより、撮影レンズ4103、シャッター4101、撮像部422を含む撮像系の汚れや破損を防止する。

423はA/D変換器であり、アナログ信号をデジタル信号に変換する。A/D変換器423は、撮像部422から出力されるアナログ信号をデジタル信号に変換するために用いられる。

424は撮像装置4100の画像処理部であり、例えば、図1に示す画像処理装置で構成される。画像処理部424は、A/D変換器423からのデータやメモリ制御部415からのデータに対して、所定の画素補間、縮小といったリサイズ処理や色変換処理を行う。

また、画像処理部424では、撮像した画像データを用いて所定の演算処理が行われ、得られた演算結果に基づいてシステム制御部450が露光制御、測距制御を行う。これにより、TTL(スルー・ザ・レンズ)方式のAF(オートフォーカス)処理、AE(自動露出)処理、EF(フラッシュプリ発光)処理が行われる。画像処理部424では、さらに、撮像した画像データを用いて所定の演算処理が行われ、得られた演算結果に基づいてTTL方式のAWB(オートホワイトバランス)処理が行われる。画像処理部424の入力画像データは撮影画像であってもよく、出力画像データは撮影画像に対して記録画像データを生成する一過程の結果であってもよく、さまざまな撮影条件、画像特徴などから決定される画像処理が施されている。詳細ついては後述する。

A/D変換器423からの出力データは、画像処理部424及びメモリ制御部415を介して、或いは、メモリ制御部415を介してメモリ432に直接書き込まれる。メモリ432は、撮像部422によって得られ、A/D変換器423によりデジタルデータに変換された画像データや、表示部428に表示するための画像データを格納する。メモリ432は、所定枚数の静止画像や所定時間の動画像及び音声を格納するのに十分な記憶容量を備えている。また、メモリ432は、画像表示用のメモリ(ビデオメモリ)を兼ねている。

413はD/A変換器であり、メモリ432に格納されている画像表示用のデータをアナログ信号に変換して表示部428に供給する。こうして、メモリ432に書き込まれた表示用の画像データは、D/A変換器413を介して表示部428により表示される。表示部428は、LCD等の表示器上に、D/A変換器413からのアナログ信号に応じた表示を行う。

不揮発性メモリ456は、電気的に消去・記憶可能なメモリであり、例えばEEPROM等が用いられる。不揮発性メモリ456には、システム制御部450の動作用の定数、プログラム等が記憶される。ここでいうプログラムとは、本実施形態にて後述する各種フローチャートを実行するためのプログラムのことである。

システム制御部450は、図2の撮像装置4100全体を制御する。前述した不揮発性メモリ456に記憶されたプログラムを実行することで、後述する本実施形態の各処理を実現する。452はシステムメモリであり、RAMで構成される。システムメモリ452には、システム制御部450の動作用の定数、変数等が記憶されると共に、不揮発性メモリ456から読み出したプログラム等を展開するためのメモリとして用いられる。また、システム制御部450は、メモリ432、D/A変換器413、表示部428等を制御することにより表示制御も行う。

加速度センサー482は、撮像装置4100に加えられた物理的な加速度を、その方向と共に検知することができるセンサーである。加速度センサーの制御は、システム制御部450によって行われ、検知される情報は後述する本実施形態の処理によって適宜扱われる。

モード切替スイッチ460、第1シャッタースイッチ462、第2シャッタースイッチ464、及び操作部470は、システム制御部450に各種の動作指示を入力するための操作手段である。

モード切替スイッチ460は、システム制御部450の動作モードを静止画記録モード、動画記録モード、再生モード等のいずれかに切り替える。第1シャッタースイッチ462は、撮像装置4100に設けられたシャッターボタン(不図示)の半押し(撮影準備指示)でONとなり、第1シャッタースイッチ信号SW1をシステム制御部450に出力する。第1シャッタースイッチ信号SW1により、AF(オートフォーカス)処理、AE(自動露出)処理、AWB(オートホワイトバランス)処理、EF(フラッシュプリ発光)処理等の動作が開始される。

第2シャッタースイッチ464は、シャッターボタンの全押し(撮影指示)でONとなり、第2シャッタースイッチ信号SW2をシステム制御部450に出力する。システム制御部450は、第2シャッタースイッチ信号SW2により、撮像部422からの信号読み出しから記録媒体4200に画像データを書き込むまでの一連の撮影処理の動作が開始される。

操作部470には各種操作部材が配置されており、各種操作部材で表示部428に表示される種々の機能アイコンを選択操作することができる。また、操作部材には、場面ごとに適宜機能が割り当てられ、各種機能ボタンとして作用する。機能ボタンとしては、例えば終了ボタン、戻るボタン、画像送りボタン、ジャンプボタン、絞込みボタン、属性変更ボタン等がある。例えば、メニューボタンが押されると、各種設定が可能なメニュー画面が表示部428に表示される。利用者は、表示部428に表示されたメニュー画面と、不図示の4方向ボタンやSETボタンを用いて直感的に各種設定を行うことができる。

480は電源制御部であり、電池検出回路、DC−DCコンバータ、通電するブロックを切り替えるスイッチ回路等により構成され、電池の装着の有無、電池の種類、電池残量の検出を行う。また、電源制御部480は、その検出結果及びシステム制御部450の指示に基づいてDC−DCコンバータ(不図示)を制御し、必要な電圧を必要な期間、記録媒体4200を含む各部へ供給する。

430は電源部であり、アルカリ電池やリチウム電池等の一次電池、NiCd電池、NiMH電池、Li電池等の二次電池、またはACアダプター等からなる。418は、メモリカードやハードディスク等の記録媒体4200とのインターフェース(I/F)である。記録媒体4200はメモリカード等の記録媒体であり、半導体メモリや磁気ディスク等から構成される。

図3は、図1における画像処理部101の内部構成を示す図である。

501〜507はDフリップフロップ(D−FF)であり、内部クロックに同期して入力画像の画素値を保持、シフトする遅延素子である。508〜513は乗算器であり、各D−FF501〜507の出力とFIR係数KN〜K1の乗算を行う。514は加算器であり、乗算器508〜513の出力を全て加算して出力する。加算器514の出力は、FIRフィルタのOUTDATとして出力される。

図4は、図1における係数テーブル1_106〜係数テーブルM108の内部構成を示す図である。

601は、係数テーブル1_106〜係数テーブルM108の各係数テーブルである。係数テーブル601は、K1テーブル602〜KNテーブル604の複数のテーブルで構成される。K1テーブル602〜KNテーブル604には、係数選択値KSELが入力される。K1テーブル602〜KNテーブル604は、入力された係数選択値KSELに従って、係数K1〜KNをそれぞれ出力する。係数テーブル601は、1組N個の係数K1〜KNを係数選択値KSELに従って出力する。

図5は、図1における係数テーブル1_106〜M108の内容例を示す図である。図示例では、3種類の係数テーブルの内容を示している。図5(a)は係数テーブル1_106の内容であり、図5(b)は係数テーブル2_107の内容、図5(c)は係数テーブル3の内容である。係数テーブル1〜3の出力係数はKSET1、KSET2、KSET3である。

図6A及び図6Bは、図1の画像処理装置における入出力信号のタイミングチャートである。

CLK801は同期クロック信号である。CLK801のクロック信号の1サイクルごとに1画素ずつ画像処理が行われる。なお、図示例では、クロック信号の1サイクルごとに‘1’から順に番号を付し、クロック1〜クロックnとして説明する。

INDAT802は入力画像データの信号である。OUTDAT803は出力画像データの信号である。OUTWIN804は出力画像領域の制御信号である。KWIN805は係数用領域制御信号である。KSEL806は係数選択値である。KSET1_807は係数テーブル1の出力係数セットである。KSET2_808は係数テーブル2の出力係数セットである。KSET3_809は係数テーブル3の出力係数セットである。

KSETSEL810は、係数テーブル1の出力係数セットKSET1_807を選択する場合の係数組選択値である。KSET811は、KSET1_807が選択された場合の係数セットを示す。

KSETSEL812は、係数テーブル2の出力係数セットKSET2_808を選択する場合の係数組選択値である。KSET813は、KSET2_808が選択された場合の係数セットを示す。

KSETSEL814は、係数テーブル3の出力係数セットKSET3_809を選択する場合の係数組選択値である。KSET815は、KSET3_809が選択された場合の係数セットを示す。

INDAT802は、クロック1〜3では不定値‘X’である。クロック4〜17の間は、順次有効画素値が入力される。入力画像データの有効画素の左端はクロック4であり、画素値はD1である。左端から入力画像データの画素値はD1,D2,D3の順で入力され、クロック13からDn−4,Dn−3,Dn−2,Dn−1,Dnと入力される。入力画像データの有効画素の右端はクロック17であり、画素値はDnである。クロック18以降のINDAT802は不定値‘X’である。

OUTDAT803は、クロック7〜クロック20の間で出力される。出力画像データの左端はクロック7で出力値がO1であり、出力画像データの右端がクロック20で出力値はOnである。

出力画像領域はOUTWIN804によって制御される。OUTWIN804が‘H’の期間、OUTDAT803は有効である。また、OUTWIN804によって、画像処理及びINDAT802の有効画素領域を考慮した適切な出力画像領域が制御できる。

係数選択値KSEL806は、係数選択値生成部103によって、係数用領域制御信号KWIN805を基に制御される。本実施形態では、KWIN805が‘H’の次のクロックでKSEL806がインクリメントされる。KSEL806の初期値は‘0’であり、画像左端では、クロック7から1クロックごとにKSEL806に1,2,3,4とインクリメントされる。クロック10〜17の間ではKSEL806は‘4’であり、画像右端では、クロック18から1クロックごとに、5,6,7,0となる。係数選択値生成部103には、予め係数選択値KSELの最大値‘7’が設定されており、これによって初期値0に戻る。

係数セットKSET1_807は、係数選択値KSEL806によって係数テーブル1_106から選択出力される。選択出力される係数セットKSET1は、図5(a)に示す係数テーブル1_106に従って決まる。クロック1〜6では、KSEL806は0でKSET1はK1tap、クロック7ではKSEL806は1でKSET1はK1tap、クロック8,9,10ではそれぞれKSEL806は2,3,4でKSET1はいずれもK3tapとなる。KSEL806は、クロック11以降クロック17まで4であり、係数セットKSET1_807はK3tapである。クロック18,19でKSEL806は5,6となり、KSET1_807はK3tapである。クロック20でKSEL806は7となり、KSET1_807はK1tapである。クロック21以降KSEL806は0となり、KSET1_807はK1tapである。このように、画像端周辺において、FIRフィルタで使用する係数セットが選択される。

同様に、係数セットKSET2_808は、係数選択値KSEL806によって係数テーブル2_107から選択出力される。選択出力される係数セットKSET2は、図5(b)に示す係数テーブル2_107に従って決まる。係数セットKSET2_808では、クロック1〜クロック7はK1tap、クロック8はK3tap、クロック9〜18はK5tap、クロック19はK3tap、クロック20以降はK1tapとなる。

同様に、係数セットKSET3_809は、係数選択値KSEL806によって係数テーブル3から選択出力される。選択出力される係数セットKSET3は、図5(c)に示す係数テーブル3に従って決まる。

係数セットKSET3_809では、クロック1〜クロック6はK1tap、クロック7はK5tap1、クロック8はK5tap2、クロック9はK5tap3、クロック10〜17はK7tapとなる。また、クロック18はK5tap3、クロック19はK5tap4、クロック20はK5tap5、クロック21以降はK1tapとなる。

KSET811は、KSETSEL810が1のときを示し、KSETにKSET1がセレクタ104によって選択されている場合を示す。KSET813は、KSETSEL812が2のときを示し、KSETにKSET2がセレクタ104によって選択されている場合を示す。KSET815は、KSETSEL814が3であって、KSETにKSET3がセレクタ104によって選択されている場合を示す。

図7は、図1における係数組選択制御部105の内部構成を示す図である。

図7において、902はノイズレベル検出部であり、INDATからノイズレベル(SN比)を検出して出力する。903は画像特徴抽出部であり、INDATから画像特徴を抽出して出力する。画像特徴にはエッジ、ベタがあり、特にエッジの場合はエッジ方向などの情報がある。904は周波数特性部であり、INDATの周波数特性を検出して周波数帯域を出力する。

905は垂直位置判別部であり、画像の垂直方向の画像領域制御信号VWINが入力される。垂直位置判別部905は、この垂直方向の画像領域制御信号VWINを基に垂直方向の画像端である上端下端からの距離情報を出力する。

なお、ここまでの一連の説明では、水平方向の画像処理の場合を想定している。垂直方向の画像処理の場合、905は水平位置判別部となり、水平方向の画像領域制御信号が入力される。

906は係数組選択決定部である。係数組選択決定部906では、画像データに付加されている撮影時の撮影条件、ノイズレベル、画像特徴、周波数帯域、上下端距離(または水平端距離)が入力され、これら情報を基にKSETSELを出力する。

図8は、図7における係数組選択決定部906において、入力される情報ごとに係数セットKSETを決めるための条件テーブルの一例を示す図である。図示のKSET1、KSET2、KSET3は、図5(a)、図5(b)、図5(c)に示すような、定義された係数セットのことである。

図8(a)は、撮影条件に対して決まる係数セットKSETaを示す。図示例では、撮影条件の一例としてISO感度を利用している。ISO感度が低い方から順に、KSET1、KSET2、KSET3が適用される。なお、ISO感度に限らず、他の撮影条件、例えばシャッタースピードで決まるTV値などでも同様に条件テーブルで定義できる。

図8(b)は、ノイズレベルとして、SN比に対して決まる係数セットKSETbを示す。SN比は、ノイズレベルに対する信号レベルの大きさを示す値である。ノイズレベルが低い方から順に、KSET1、KSET2、KSET3が適用される。

図8(c)は、画像特徴に対して決まる係数セットKSETcを示す。垂直方向のエッジ画像の場合にはKSET1、斜めエッジの場合にはKSET2、水平エッジとベタの場合にはKSET3が適用される。なお、本実施形態では、水平方向の画像処理の場合について説明したが、垂直方向の画像処理に適用する場合は、KSET1が水平方向のエッジ画像に、KSET3が垂直エッジ画像に適用されるものとする。

図8(d)は、周波数特性に対して決まる係数セットKSETdを示す。高周波数帯域画像の方から順に、KSET1、KSET2、KSET3が適用される。

図8(e)は、入力画像の垂直位置に対して決まる係数セットKSETeを示す。画像処理対象の注目画素が、上端若しくは下端からの距離が遠い方から順に、KSET1、KSET2、KSET3が適用される。なお、本実施形態では、水平方向の画像処理の場合について説明したが、垂直方向の画像処理に適用する場合は、画像処理対象の注目画素が左端若しくは右端からの距離が遠い方から順に、KSET1、KSET2、KSET3が適用されるものとする。

本実施形態では、上述した図8(a)〜図8(e)に示す条件テーブルに基づいて決定された係数セットKSETa〜KSETeから最終的に一つの係数セットKSETを求める。KSETの求め方の一例としては、次式1のように、KSETa〜KSETeの最大値を求める方法がある。

KSET=MAX(KSETa,KSETb,KSETc,KSETd,KSETe)

式1

ただし、KSET1<KSET2<KSET3とする。

次に、係数テーブル1_106〜係数テーブルM108に定義される係数の算出方式について説明する。

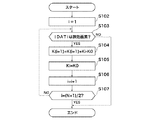

図9は、画像左端用の係数を係数算出方式1で算出する算出処理の流れを示すフローチャートである。なお、以下に説明する処理は、例えば、画像処理装置内のCPU等が実行するものとして説明するが、これに限定されるものではない。

図示例では、いずれも画像端でない画像中央領域における画像処理の係数K1〜KNが与えられたものとして、画像端用の係数が算出される。画像端用の係数は、注目画素が画像端に対してどの位置にあるかによってそれぞれ個別に後述の算出方式によって求められる。画像端用の係数が適用されるのは、注目画素に対して参照する周辺画素に入力画像外の領域の無効画素が含まれる場合である。

まず、ステップS102では、CPUは、処理画素位置i=1にして初期化を行う。次に、ステップS103では、CPUは、入力画素IDATiが無効画素か否かを判断する。無効画素でないと判定した場合は、本処理を終了する。一方、無効画素であると判定した場合はステップS104に進み、CPUは、右隣の画素用の係数K(i+1)に無効画素用の係数Ki−K0を加算して、新たな係数K(i+1)とする。ここで係数値K0は無効画素用の係数値とする。

次に、ステップS105では、CPUは、無効画素用の係数KiをK0にする。次に、ステップS106では、CPUは、処理画素位置iを1つ増やす。

次に、ステップS107では、CPUは、処理画素位置iが(N+1)/2に等しいか否かを判定する。ここでNはタップ(TAP)数を示し、係数はK1〜KNとする。また、(N+1)/2は、TAP処理の中央画素である注目画素の画素位置のことである。

ステップS107の判定の結果、等しいと判定した場合は、本処理を終了する。一方、等しくないと判定した場合は、ステップS103に戻り、係数算出処理を繰り返す。

図10は、画像右端用の係数を係数算出方式1で算出する算出処理の流れを示すフローチャートである。

まず、ステップS202では、CPUは、処理画素位置i=Nで初期化する。次に、ステップS203では、CPUは、入力画素IDATiが無効画素か否かを判断する。無効画素でないと判定した場合は、本処理を終了する。一方、無効画素であると判定した場合はステップS204に進み、CPUは、左隣の画素用の係数K(i−1)に無効画素用の係数Ki−K0を加算して、新たな係数K(i−1)とする。ここで係数値K0は無効画素用の係数値とする。

次に、ステップS205では、CPUは、無効画素用の係数KiをK0にする。次に、ステップS206では、CPUは、処理画素位置iを1つ減らす。

次に、ステップS207では、CPUは、処理画素位置iが(N+1)/2に等しいか否かを判定する。ここでNはタップ数を示し、係数はK1〜KNとする。また、(N+1)/2は、TAP処理の中央画素である注目画素の画素位置のことである。ステップS207の判定の結果、等しいと判定した場合は、本処理を終了する。一方、等しくないと判定した場合は、ステップS203に戻り、係数算出処理を繰り返す。

次に、2種類の係数の算出方式を用いて実際に算出した係数について図11を参照して説明する。

図11(a)は、係数算出方式2を用いて実際に算出した係数の一例を示す図である。なお、図11(b)については後述する。

図11(a)では、11TAPの係数K1〜K11の場合について示している。表の左側は、各タップに入力される画素が無効画素(×)か有効画素(○)かを示しており、K6の入力画素が注目画素(◎)で有効画素を前提としている。表の右側は、表の左側に対応する係数K1〜K11の値を示しており、実際の係数はここで示される値を係数の合計値66で割った値である。

1701は画像左端の画素が注目画素の場合であり、1702は画像左端から2画素目が注目画素の場合である。1703は画像左端から3画素目、1704は4画素目、1705は5画素目の場合である。

1711は画像右端の画素が注目画素の場合、1710は画像右端から2画素目、1709は3画素目、1708は4画素目、1707は5画素目の場合である。

1706は画像左端6画素目から内側でかつ画像右端6画素目から内側の場合である。

次に、画像左端に無効画素がある場合の係数算出方式1による係数について説明する。

1705は1706と比較するとK1が無効画素であり、K1の値を“0”とし、1706のK1の値“1”をK2の値“2”に加算して、1705のK2の値を“3”とする。

1704は1705と比較するとK2が無効画素であり、K2の値を“0”とし、1705のK2の値“3”をK3の値“4”に加算して、1704のK3の値を“7”とする。

以下同様に、1703の係数K4が“13”、1702の係数K5が“23”、1701の係数K6が“43”というように算出することができる。

一方、画像右端に無効画素がある場合も、上記と同様に係数を算出することができる。例えば、1707の係数K10が“3”、1708の係数K9が“7”、1709の係数K8が“13”、1710の係数K7が“23”、1711の係数K6が“43”というように算出することができる。

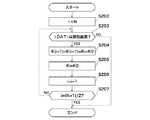

図12は、画像左端用の係数を係数算出方式2で算出する算出処理を示すフローチャートである。

図示例では、いずれも画像端でない画像中央領域における画像処理の係数K1〜KNが与えられたものとして、画像端用の係数が算出される。画像端用の係数は、注目画素が画像端に対してどの位置にあるかによってそれぞれ個別に後述の算出方式によって求められる。画像端用の係数が適用されるのは、注目画素に対して参照する周辺画素に入力画像外の領域の無効画素が含まれる場合である。

まず、ステップS302では、CPUは、処理画素位置i=1にして初期化を行う。次に、ステップS303では、CPUは、入力画素IDATiが無効画素か否かを判断する。無効画素でないと判定した場合は、本処理を終了する。一方、無効画素であると判定した場合はステップS304に進み、CPUは、右隣の画素用の係数K(i+1)に無効画素用の係数Ki−K0を加算して、新たな係数K(i+1)とする。ここで係数値K0は無効画素用の係数値とする。

次に、ステップS305では、CPUは、無効画素用の係数KiをK0にする。次に、ステップS306では、CPUは、処理画素位置iを1つ増やす。

次に、ステップS307では、CPUは、処理画素位置iが(N+1)/2に等しいか否かを判定する。ここでNはタップ(TAP)数を示し、係数はK1〜KNとする。また、(N+1)/2は、TAP処理の中央画素である注目画素の画素位置のことである。

ステップS307の判定の結果、等しくないと判定した場合はステップS303に戻り、ステップS303からステップS307の処理を繰り返す。一方、ステップS307で等しいと判定した場合はステップS308に進む。

ステップS308では、CPUは、係数Kiと左隣の画素用の係数K(i−1)を比較し、Kiの方が大きいと判定した場合は、本処理を終了する。一方、係数Kiの方が小さいか等しい(係数以下)と判定した場合はステップS309に進み、CPUは、KiとK(i−1)の係数の値を入れ替える。

次に、ステップS310では、CPUは、処理画素位置iが(N+1)/2に等しいか否かを判定する。等しいと判定した場合は、本処理を終了する。一方、等しくないと判定した場合はステップS312に進み、CPUは、処理画素位置iを1つ増やす。次に、ステップS308に戻り、ステップS308からステップS310の処理を繰り返す。

図13は、画像右端用の係数を係数算出方式2で算出する算出処理を示すフローチャートである。

まず、ステップS402では、CPUは、処理画素位置i=Nにして初期化を行う。次に、ステップS403では、CPUは、入力画素IDATiが無効画素か否かを判断する。無効画素でないと判定した場合は、本処理を終了する。一方、無効画素であると判定した場合はステップS404に進み、CPUは、左隣の画素用の係数K(i−1)に無効画素用の係数Ki−K0を加算して、新たな係数K(i−1)とする。ここで係数値K0は無効画素用の係数値とする。

次に、ステップS405では、CPUは、無効画素用の係数KiをK0にする。次に、ステップS406では、CPUは、処理画素位置iを1つ減らす。

次に、ステップS407では、CPUは、処理画素位置iが(N+1)/2に等しいか否かを判定する。ここでNはタップ(TAP)数を示し、係数はK1〜KNとする。また、(N+1)/2は、TAP処理の中央画素である注目画素の画素位置のことである。

ステップS407の判定の結果、等しくないと判定した場合はステップS403に戻り、ステップS403からステップS407の処理を繰り返す。一方、ステップS407で等しいと判定した場合はステップS408に進む。

ステップS408では、CPUは、係数Kiと右隣の画素用の係数K(i+1)を比較し、Kiの方が大きいと判定した場合は、本処理を終了する。一方、係数Kiの方が小さいか等しい(係数以下)と判定した場合はステップS409に進み、CPUは、KiとK(i+1)の係数の値を入れ替える。

次に、ステップS410では、CPUは、処理画素位置iが(N+1)/2に等しいか否かを判定する。等しいと判定した場合は、本処理を終了する。一方、等しくないと判定した場合はステップS412に進み、CPUは、処理画素位置iを1つ減らす。次に、ステップS408に戻り、ステップS408からステップS410の処理を繰り返す。

図11(b)は、係数算出方式2を用いて実際に算出した係数の一例を示す図である。

図11(b)では、11TAPの係数K1〜K11の場合について示している。表の左側は、各タップに入力される画素が無効画素(×)か有効画素(○)かを示しており、K6の入力画素が注目画素(◎)で有効画素を前提としている。表の右側は、表の左側に対応する係数K1〜K11の値を示しており、実際の係数はここで示される値を係数の合計値66で割った値である。

1712は画像左端の画素が注目画素の場合であり、1713は画像左端から2画素目が注目画素の場合である。1714は画像左端から3画素目、1715は4画素目、1716は5画素目の場合である。

1722は画像右端の画素が注目画素の場合、1721は画像右端から2画素目、1720は3画素目、1719は4画素目、1718は5画素目の場合である。

1717は画像左端6画素目から内側でかつ画像右端6画素目から内側の場合である。

次に、画像左端に無効画素がある場合の係数算出方式2による係数について説明する。

1716は1717と比較するとK1が無効画素であり、K1の値を“0”とし、1717のK1の値“1”をK2の値“2”に加算し、1716のK2の値を“3”とする。K3の値は“4”であり、K2の値“3”より大きいので算出を終了する。

1715は1716と比較するとK2が無効画素であり、K2の値を“0”とし、1716のK2の値“3”をK3の値“4”に加算し、1715のK3の値を“7”とする。K4は“6”でK3の“7”より小さいので、K3とK4の値を入れ替えてK3を“6”、K4を“7”とする。K5は“10”でK4の“7”より大きいので、算出を終了する。

以下同様にして、係数が算出できる。

以上のように、係数テーブル1_106〜係数テーブルM108、係数用領域KWIN、及び出力画像領域OUTWINによって、画像端周辺においても画像処理における有効画素領域を考慮した適切な画質設計が行える。

また、係数組選択制御部105によって、各種条件ごとに適用する係数テーブルを切り替えることで、画像端周辺においても各種条件ごとに適切な画質設計が行える。

なお、本実施形態では、FIRフィルタを採用した場合について説明したが、周辺画素を参照しつつ処理を行う他の画像処理の場合についても同様に適用することができる。

また、本実施形態では、3種類の係数テーブルを例に説明したが、4種類以上であっても同様に本発明を実現することができる。

さらに、本実施形態では、水平方向の画像処理を例に説明したが、垂直方向の画像処理についても同様に実現できる。

また、本実施形態では、2つの係数算出方式について説明したが、これに限るものではない。係数テーブルも算出方式に依存するものでなく、画質設計におけるタップ数、係数値に応じて自由に定義することができる。

[第2の実施形態]

第2の実施形態では、画像処理における参照画素範囲、例えばFIRフィルタにおけるタップ数を画像端の周辺領域で制御する例について説明する。

図14は、本発明の第2の実施形態に係る画像処理装置の構成例を示すブロック図である。なお、第2の実施形態では、第1の実施形態と同様に、図2の画像処理部424が、図14に示す画像処理装置で構成されるものとする。

図14において、1101は周辺画素COPY部である。周辺画素COPY部1101は、INDATの画像端より外側の無効画素領域を、画像端の有効画素でコピー置換して擬似的に有効画像領域を外側方向に広げる画像処理を行う(第一の画像処理)。INDATは、周辺画素COPY部1101で周辺画素コピー処理され、CPDATとして出力される。

1113〜1115、及び1102,1103,1104は画像処理部(例えば、フィルタ)である(第二の画像処理)。本実施形態では、1TAP(フィルタ処理なし)、3TAP、5TAP、7TAPで構成される場合について説明する。N_TAPとは、フィルタ処理における参照画素範囲がN画素であることを示す。

1113,1114,1115はDフリップフロップ(D−FF)であり、1TAPOUTはCPDATの3クロック遅延となる。

1105は第一のセレクタ(MUX)である。第一のセレクタ1105は、入力されるフィルタ選択値FSELに従って、出力1TAPOUT、3TAPフィルタ1102の出力3TAPOUT、5TAPフィルタ1103の出力5TAPOUT、7TAPフィルタ1104の出力7TAPOUTから選択する。そして、出力画像データ(OUTDAT)として出力する。

1106は画像領域制御部であり、ウィンドウ制御信号COPYLWIN、COPYRWIN、OUTWIN、FWINを出力する。COPYLWINは画像左端の画素コピー領域の制御信号である。COPYRWINは画像右端の画素コピー領域の制御信号である。OUTWINは画像出力領域を表す制御信号である。FWINは画像処理部の各フィルタの切り替えを行う画像領域を指定する制御信号である。OUTWINは、出力画像領域を制御するための制御信号であり、各画像処理部1102,1103,1104に入力される。

1107はフィルタ番号生成部であり、画像領域制御部1106からFWINが入力され、画像領域に従ったフィルタ番号FNOを生成する。フィルタ選択テーブル1_1110〜フィルタ選択テーブルM1112は、フィルタ処理なしも含めた各フィルタからフィルタ番号FNOに従ってフィルタを選択するフィルタ選択値のテーブルである。図示例では、M種類のフィルタ選択テーブルがある場合を示す。

1108は第二のセレクタ(MUX)である。第二のセレクタ1108は、入力されるフィルタ組選択値FSELSELに従って、フィルタ選択テーブル1_1110〜M1112から選択したフィルタ選択値FSELを第一のセレクタ1105に出力する。

1109はフィルタ組選択制御部である。フィルタ組選択制御部1109は、フィルタ組選択値FSELSELを生成して出力する。

図15は、図14におけるフィルタ選択テーブル1_1110〜M1112の内容例を示す図である。図示例では、3種類のフィルタ選択テーブルの内容を示している。

図15において、FNOは、フィルタ番号生成部1107から出力されるフィルタ番号である。

フィルタ番号FNOに対するフィルタ選択値FSEL1、FSEL2、FSEL3が、フィルタ選択テーブル1_1110、フィルタ選択テーブル2_1111、フィルタ選択テーブル3の内容である。例えば、フィルタ選択テーブル2_1111では、FNOが0,1では1tap、2では3tap、FNOが3,4,5では5tap、6では3tap、7では1tapである。

1tap、3tap、5tap、7tapは、第一のセレクタ1105が、1TAPOUT、3TAPOUT、5TAPOUT、7TAPOUTを選択するためのフィルタ選択値FSELである。例えば、図16A〜図16Dは、図14の画像処理装置における入出力信号のタイミングチャートである。

CLK1301は同期クロックである。CLK1301のクロック信号の1サイクルごとに1画素ずつ画像処理が行われる。なお、図示例では、クロック信号の1サイクルごとに‘1’から順に番号を付し、クロック1〜クロックnとして説明する。

INDAT1302は入力画像データの信号である。CPDAT1303は周辺画素コピー後の画像データである。1TAPOUT1304はCPDAT1303の3クロック遅延の画像データである。3TAPOUT1305は3TAPフィルタの出力画像データである。5TAPOUT1306は5TAPフィルタの出力画像データである。7TAPOUT1307は7TAPフィルタの出力画像データである。OUTDAT1308は第一のセレクタ1105で選択された出力画像データである。

COPYLWIN1309は、画像左端の画素コピー領域の制御信号である。COPYRWIN1310は画像右端の画素コピー領域の制御信号である。OUTWIN1311は出力画像領域の制御信号である。FWIN1312はフィルタ選択用領域制御信号である。FNO1313はフィルタ番号である。FSEL1_1314は、フィルタ選択テーブル1の出力フィルタ選択値である。FSEL2_1315は、フィルタ選択テーブル2の出力フィルタ選択値である。FSEL3_1316は、フィルタ選択テーブル3の出力フィルタ選択値である。

FSELSEL1317は、フィルタ選択テーブル1の出力フィルタ選択値FSEL1_1314を選択する場合のフィルタ組選択値である。FSEL1318は、FSEL1_1314が選択された場合のフィルタ選択値を示す。OUTDAT1319は、フィルタ選択値がFSEL1318の場合に第一のセレクタ1105で選択出力された出力画像データを示す。

FSELSEL1320は、フィルタ選択テーブル2の出力フィルタ選択値FSEL2_1315を選択する場合のフィルタ組選択値である。FSEL1321は、FSEL2_1315が選択された場合のフィルタ選択値を示す。OUTDAT1322は、フィルタ選択値がFSEL1321の場合に第一のセレクタ1105で選択出力された出力画像データを示す。

FSELSEL1323は、フィルタ選択テーブル3の出力フィルタ選択値FSEL3_1316を選択する場合のフィルタ組選択値である。FSEL1324は、FSEL3_1316が選択された場合のフィルタ選択値を示す。OUTDAT1325は、フィルタ選択値がFSEL1324の場合に第一のセレクタ1105で選択出力された出力画像データを示す。

INDAT1302は、クロック1〜2では不定値‘X’である。クロック3からクロック18まで順次、有効画素値が入力される。入力画像の有効画素の左端は、クロック3であり、画素値はD1である。左端から入力画像の画素値はD1,D2,D3の順で入力され、クロック15からDn−3,Dn−2,Dn−1,Dnと入力される。入力画像データの有効画素の右端はクロック18であり、画素値はDnである。クロック19以降はINDAT1302は不定値‘X’である。

CPDAT1303は、INDAT1302のクロック3の画像左端の画素値D1がコピーされ、クロック4,5では画素値がD1となる。画像左端のコピー領域は、COPYLWIN1309が‘H’のときに行われる。

CPDAT1303は、INDAT1302のクロック18の画像右端の画素値Dnがコピーされ、クロック22,23では画素値がDnとなる。画像右端のコピー領域は、COPYRWIN1310が‘H’のときに行われる。

OUTDAT1308は、クロック9〜クロック24の間で出力される。出力画像データの左端はクロック9で出力値がO1であり、出力画像データの右端がクロック24で出力値はOnである。

出力画像領域はOUTWIN1311によって制御される。OUTWIN1311が‘H’の期間、OUTDAT1308は有効である。また、OUTWIN1308によって、画像処理及びINDAT1302の有効画素領域を考慮した適切な出力画像領域が制御できる。

フィルタ番号FNO1313は、フィルタ番号生成部1107によって、フィルタ選択用領域制御信号FWIN1312を基に制御される。本実施形態では、FWIN1312が‘H’の次のクロックでFNO1313がインクリメントされる。FNO1313の初期値は‘0’であり、画像左端では、クロック9から1クロックごとに1,2,3,4とインクリメントされる。クロック21まではFNO1313は‘4’で、画像右端では、クロック22から1クロックごとに5,6,7,0となる。フィルタ番号生成部1107には、予めフィルタ番号FNOの最大値‘7’が設定されており、これによって初期値0に戻る。

フィルタ選択値FSEL1_1314は、フィルタ番号FNO1313によってフィルタ選択テーブル1_1310から選択出力される。選択出力されるフィルタ選択値FSEL1_1314は、図15に示すフィルタ選択テーブルに従って決まる。クロック1〜8では、FNO1313は0でFSEL1_1314は1tap、クロック9ではFNO1313は1でFSEL1_1314は1tapとなる。また、クロック10,11,12ではそれぞれFNO1313は2,3,4でFSEL1_1314はいずれも3tapとなる。

FNO1313は、クロック13以降クロック21まで4であり、フィルタ選択値FSEL1_1314は3tapである。クロック22,23でFNO1313は5,6となり、FSEL1_1314は3tapである。クロック24でFNO1313は7となり、FSEL1_1314は1tapである。クロック25以降FNO1313は0となり、FSEL1_1314は1tapである。このように、画像端周辺において、フィルタで使用するフィルタ選択テーブルが選択される。

同様に、フィルタ選択値FSEL2_1315は、フィルタ番号FNO1313によってフィルタ選択テーブル2_1111から選択出力される。選択出力されるフィルタ選択値FSEL2は、図15に示すフィルタ選択テーブルに従って決まる。フィルタ選択値FSEL2_1315では、クロック1〜クロック9は1tap、クロック10は3tap、クロック11〜22は5tap、クロック23は3tap、クロック24以降は1tapとなる。

同様に、フィルタ選択値FSEL3_1316は、フィルタ番号FNO1313によってフィルタ選択テーブル3から選択出力される。選択出力されるフィルタ選択値FSEL3は、図15に示すフィルタ選択テーブルに従って決まる。フィルタ選択値FSEL3_1316では、クロック1〜クロック8は1tap、クロック9〜11は5tap、クロック12〜21までは7tap、クロック22〜24は5tap、クロック25以降は1tapとなる。

FSEL1318は、フィルタ組選択値FSELSEL1317が1のときを示し、第二のセレクタ1108によってFSEL1が選択されている場合を示す。このとき、OUTDAT1308はOUTDAT1319のようになる。

FSEL1321は、フィルタ組選択値FSELSEL1320が2のときを示し、第二のセレクタ1108によってFSEL2が選択されている場合を示す。このとき、OUTDAT1308はOUTDAT1322のようになる。

FSEL1324は、フィルタ組選択値FSELSEL1323が3のときを示し、第二のセレクタ1108によってFSEL3が選択されている場合を示す。このとき、OUTDAT1308はOUTDAT1325のようになる。

図17は、図14におけるフィルタ組選択制御部1109の内部構成を示す図である。

図17において、1402はノイズレベル検出部であり、INDATからノイズレベル(SN比)を検出して出力する。1403は画像特徴抽出部であり、INDATから画像特徴を抽出して出力する。画像特徴にはエッジ、ベタがあり、特にエッジの場合はエッジ方向などの情報がある。1404は周波数特性部であり、INDATの周波数特性を検出して周波数帯域を出力する。

1405は垂直位置判別部であり、画像の垂直方向の画像領域制御信号VWINが入力される。垂直位置判別部1405は、この垂直方向の画像領域制御信号VWINを基に垂直方向の画像端である上端下端からの距離情報を出力する。

なお、ここまでの一連の説明では、水平方向の画像処理の場合を想定している。垂直方向の画像処理の場合、1405は水平位置判別部となり、水平方向の画像領域制御信号が入力される。

1406はフィルタ組選択決定部である。フィルタ組選択決定部1406では、画像データに付加されている撮影時の撮影条件、ノイズレベル、画像特徴、周波数帯域、上下端距離が入力され、これら情報を基にフィルタ組選択値FSELSELを出力する。

図18は、図17におけるフィルタ組選択決定部1406において、入力される情報ごとにフィルタ選択値FSELを決めるための条件テーブルの一例を示す図である。図示のFSEL1、FSEL2、FSEL3は、図15で定義されたフィルタ選択値のテーブル出力のことである。

図18(a)は、撮影条件に対して決まるフィルタ選択値FSELaを示す。図示例では、撮影条件の一例としてISO感度を利用している。ISO感度が低い方から順に、FSEL1、FSEL2、FSEL3が適用される。なお、ISO感度に限らず、他の撮影条件、例えばシャッタースピードで決まるTV値などでも同様に条件テーブルで定義できる。

図18(b)は、ノイズレベルとして、SN比に対して決まるフィルタ選択値FSELbを示す。SN比は、ノイズレベルに対する信号レベルの大きさを示す値である。ノイズレベルが低い方から順に、FSEL1、FSEL2、FSEL3が適用される。

図18(c)は、画像特徴に対して決まるフィルタ選択値FSELcを示す。垂直方向のエッジ画像の場合FSEL1、斜めエッジの場合FSEL2、水平エッジとベタの場合KFSEL3が適用される。なお、本実施形態では、水平方向の画像処理の場合について説明したが、垂直方向の画像処理に適用する場合は、FSEL1が水平方向のエッジ画像に、FSEL3が垂直エッジ画像に適用されるものとする。

図18(d)は、周波数特性に対して決まるフィルタ選択値FSELdを示す。高周波数帯域画像の方から順に、FSEL1、FSEL2、FSEL3が適用される。

図18(e)は、入力画像の垂直位置に対して決まるフィルタ選択値FSELeを示す。画像処理対象の注目画素が、上端若しくは下端からの距離が遠い方から順に、FSEL1、FSEL2、FSEL3が適用される。なお、本実施形態では、水平方向の画像処理の場合について説明したが、垂直方向の画像処理に適用する場合は、画像処理対象の注目画素が左端若しくは右端からの距離が遠い方から順に、FSEL1、FSEL2、FSEL3が適用されるものとする。

本実施形態では、上述した図18(a)〜図18(e)に示す条件テーブルに基づいて決定されたフィルタ選択値FSELa〜FSELeから最終的に一つのフィルタ選択値FSELを求める。FSELの求め方の一例としては、次式2のように、FSELa〜FSELeの最大値を求める方法がある。

FSEL=MAX(FSELa,FSElb,FSELc,FSELd,FSELe)

式2

ただし、FSEL1<FSEL2<FSEL3とする。

以上のように、フィルタ選択テーブル1_1110〜フィルタ選択テーブルM1112、フィルタ選択用領域FWIN、及び出力画像領域OUTWINによって、画像端周辺においても画像処理における有効画素領域を考慮した適切な画質設計が行える。

また、フィルタ組選択制御部1109によって、各種条件ごとに適用するフィルタ選択テーブルを切り替えることで、画像端周辺においても各種条件ごとに適切な画質設計が行える。

なお、本実施形態では、画像処理としてNタップ(TAP)フィルタを採用した場合について説明したが、周辺画素を参照しつつ処理を行う他の画像処理の場合についても同様に適用することができる。

また、本実施形態では、3種類のフィルタ選択テーブルを例に説明したが、4種類以上であっても同様に本発明を実現することができる。

さらに、本実施形態では、水平方向の画像処理を例に説明したが、垂直方向の画像処理についても同様に本発明を実現できる。

また、本実施形態では、周辺画素COPY部1101を利用した場合について説明したが、これに限るものでない。例えば、画像処理部であるフィルタ1102〜1104で画像端の有効画素を考慮した処理を行うか、画像端用の画像処理行う専用フィルタなどを設けることにより、周辺画素COPY部1101を利用することなく、画像端周辺での適切な画像処理を実現できる。

さらに、各画像処理の係数の算出については、第1の実施形態で説明した2つの係数算出方式をそのまま適用できる。

また、本実施形態では、2つの係数算出方式について説明したが、これに限るものではない。各画像処理も算出方式に依存するものでなく、画質設計におけるタップ数、係数値に応じて自由に定義することができる。

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。