JP5867765B2 - マルチプロトコルのi/o相互接続の時間同期化 - Google Patents

マルチプロトコルのi/o相互接続の時間同期化 Download PDFInfo

- Publication number

- JP5867765B2 JP5867765B2 JP2014550304A JP2014550304A JP5867765B2 JP 5867765 B2 JP5867765 B2 JP 5867765B2 JP 2014550304 A JP2014550304 A JP 2014550304A JP 2014550304 A JP2014550304 A JP 2014550304A JP 5867765 B2 JP5867765 B2 JP 5867765B2

- Authority

- JP

- Japan

- Prior art keywords

- time

- integrated circuit

- circuit device

- switch

- local

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004744 fabric Substances 0.000 claims description 82

- 238000000034 method Methods 0.000 claims description 79

- 230000002093 peripheral effect Effects 0.000 claims description 41

- 230000004044 response Effects 0.000 claims description 21

- 230000005540 biological transmission Effects 0.000 claims description 16

- 238000004891 communication Methods 0.000 claims description 14

- 238000012937 correction Methods 0.000 claims description 14

- 230000010354 integration Effects 0.000 claims description 2

- 230000001360 synchronised effect Effects 0.000 claims 1

- 230000005641 tunneling Effects 0.000 description 24

- 230000008569 process Effects 0.000 description 16

- 238000004364 calculation method Methods 0.000 description 11

- 238000013507 mapping Methods 0.000 description 10

- 238000012545 processing Methods 0.000 description 10

- 238000011144 upstream manufacturing Methods 0.000 description 10

- GJWAPAVRQYYSTK-UHFFFAOYSA-N [(dimethyl-$l^{3}-silanyl)amino]-dimethylsilicon Chemical compound C[Si](C)N[Si](C)C GJWAPAVRQYYSTK-UHFFFAOYSA-N 0.000 description 8

- 239000000872 buffer Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 230000003287 optical effect Effects 0.000 description 6

- 230000006870 function Effects 0.000 description 5

- 238000005259 measurement Methods 0.000 description 5

- 230000007246 mechanism Effects 0.000 description 5

- 238000012546 transfer Methods 0.000 description 5

- 230000003111 delayed effect Effects 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 230000011664 signaling Effects 0.000 description 3

- 238000012549 training Methods 0.000 description 3

- 230000000295 complement effect Effects 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- 230000006978 adaptation Effects 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 230000002085 persistent effect Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/12—Synchronisation of different clock signals provided by a plurality of clock generators

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0638—Clock or time synchronisation among nodes; Internode synchronisation

- H04J3/0658—Clock or time synchronisation among packet nodes

- H04J3/0661—Clock or time synchronisation among packet nodes using timestamps

- H04J3/0667—Bidirectional timestamps, e.g. NTP or PTP for compensation of clock drift and for compensation of propagation delays

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

- G06F13/4004—Coupling between buses

- G06F13/4022—Coupling between buses using switching circuits, e.g. switching matrix, connection or expansion network

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4204—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus

- G06F13/4221—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus being an input/output bus, e.g. ISA bus, EISA bus, PCI bus, SCSI bus

- G06F13/423—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus being an input/output bus, e.g. ISA bus, EISA bus, PCI bus, SCSI bus with synchronous protocol

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0685—Clock or time synchronisation in a node; Intranode synchronisation

- H04J3/0697—Synchronisation in a packet node

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Signal Processing (AREA)

- Computer Networks & Wireless Communication (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Computer Hardware Design (AREA)

- Information Transfer Systems (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Electric Clocks (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Small-Scale Networks (AREA)

Description

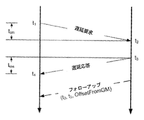

t4=受信した遅延応答タイムスタンプ+RxTimetoWire

本発明の例を下記の各項目として示す。

[項目1]

マルチプロトコルの相互接続の時間同期化のための方法であって、

マルチプロトコルの相互接続のスイッチングファブリックの第1のスイッチの第1のローカル時間を、前記スイッチングファブリックの第2のスイッチに提供する段階と、

前記第2のスイッチの第2のローカル時間を前記第1のローカル時間に調節する段階と

を備える方法。

[項目2]

前記調節する段階は、前記第2のスイッチの自励発振器のタイムスタンプに少なくとも部分的に基いて前記第2のローカル時間を決定する段階を有する、項目1に記載の方法。

[項目3]

前記調節する段階は、前記第1のスイッチから受信した前記タイムスタンプおよび前記第1のローカル時間に少なくとも部分的に基いてオフセット値を算出する段階と、

前記オフセット値によって前記第2のローカル時間を調節する段階と

を更に有する、項目2に記載の方法。

[項目4]

前記第2のスイッチの第1のポートから前記第2のスイッチの第2のポートに、前記調節された第2のローカル時間を提供する段階を更に有する、項目2または3に記載の方法。

[項目5]

前記第1のローカル時間を前記第2のスイッチに提供する段階は、前記第1のスイッチの第1のポートから前記第2のスイッチの第2のポートに、前記第1のローカル時間を提供する段階を有する、項目1〜4のいずれか一項に記載の方法。

[項目6]

前記第2のスイッチから前記スイッチングファブリックの第3のスイッチに、前記第1のローカル時間を提供する段階を更に有する、項目1〜5のいずれか一項に記載の方法。

[項目7]

前記第3のスイッチの第3のローカル時間を前記第1のローカル時間に調節する段階を更に有する、項目6に記載の方法。

[項目8]

前記第1のローカル時間を前記第2のスイッチに提供する前記段階は前記第1のスイッチの自励発振器の周波数の値を前記第2のスイッチに提供する段階を有し、前記方法は前記第2のスイッチから前記第3のスイッチに前記周波数の値を提供する段階を更に有する、項目6または7に記載の方法。

[項目9]

前記第1のスイッチおよび前記第2のスイッチは第1のドメインを有し、

前記方法は前記第2のスイッチから前記スイッチングファブリックの第2のドメインの第3のスイッチに、前記第1のローカル時間を提供する段階を更に有する、項目1〜6のいずれか一項に記載の方法。

[項目10]

前記第3のスイッチから前記第2のドメインの第4のスイッチに前記第1のローカル時間を提供する段階と、

前記第4のスイッチの第4のローカル時間を前記第1のローカル時間に調節する段階と

を更に有する、項目9に記載の方法。

[項目11]

前記調節された第4のローカル時間を前記第3のスイッチに提供する段階と、

前記第3のスイッチの第3のローカル時間を前記調節された第4のローカル時間に調節する段階と

を備える、項目10に記載の方法。

[項目12]

前記調節された第4のローカル時間を前記第2のドメインの第5のスイッチに提供する段階と、

前記第5のスイッチの第5のローカル時間を前記調節された第4のローカル時間に調節する段階と

を更に備える、項目10または11に記載の方法。

[項目13]

マルチプロトコルの相互接続の時間同期化のためのプログラムであって、

コンピュータに、

マルチプロトコルの相互接続のスイッチングファブリックの第1のスイッチの第1のローカル時間を前記スイッチングファブリックの第2のスイッチに提供する手順と、

前記第2のスイッチの第2のローカル時間を前記第1のローカル時間に調節する手順とを実行させるプログラム。

[項目14]

前記調節する手順は、前記第2のスイッチの自励発振器のタイムスタンプに少なくとも部分的に基いて前記第2のローカル時間を決定する手順を含む、項目13に記載のプログラム。

[項目15]

前記第1のローカル時間を前記第2のスイッチに提供する手順は、前記第1のスイッチの第1のポートから前記第2のスイッチの第2のポートに前記第1のローカル時間を提供する手順を含む、項目13または14に記載のプログラム。

[項目16]

コンピュータに、前記第2のスイッチから前記スイッチングファブリックの第3のスイッチに前記第1のローカル時間を提供する手順を更に実行させる、項目13〜15のいずれか一項に記載のプログラム。

[項目17]

前記第1のスイッチおよび前記第2のスイッチは第1のドメインを有し、

コンピュータに、前記第2のスイッチから前記スイッチングファブリックの第2のドメインの第3のスイッチに前記第1のローカル時間を提供する手順を更に実行させる、項目13〜16のいずれか一項に記載のプログラム。

[項目18]

マルチプロトコルの相互接続の時間同期化ためのシステムであって、

複数のスイッチを有するスイッチングファブリックを有するマルチプロトコルの相互接続を含むI/O複合体と、

前記I/O複合体と動作可能に結合された1つまたは複数のプロセッサと、

前記1つまたは複数のプロセッサと動作可能に結合され、内部に複数のプログラミング命令を記憶したコンピュータ読取可能な非一時的記憶媒体であって、前記複数のプログラミング命令の実行に応答して、前記システムが

前記スイッチングファブリックの第1のスイッチの第1のローカル時間を前記スイッチングファブリックの第2のスイッチに提供し、

前記第2のスイッチの第2のローカル時間を前記第1のローカル時間に調節することを可能にするコンピュータ読取可能な非一時的記憶媒体と、

前記I/O複合体および前記1つまたは複数のプロセッサに動作可能に結合された表示装置と

を備えるシステム。

[項目19]

前記システムは、デスクトップコンピュータ、ラップトップコンピュータ、ハンドヘルドコンピュータ、タブレットコンピュータ、ネットブックコンピュータ、サーバー、セットトップボックス、デジタル記録装置、ゲームコンソール、スマートフォン、携帯情報端末、携帯電話、デジタルメディアプレーヤ、またはデジタルカメラのうちの選択された1つである、項目18に記載のシステム。

[項目20]

バスによって前記I/O複合体に動作可能に結合され、無線ネットワークの1つまたは複数のコンポーネントとの無線通信リンクを確立する1つまたは複数のアンテナを更に備える、項目18または19に記載のシステム。

[項目21]

スイッチと、

自励発振器であるローカルクロックと、

少なくとも1つのポートと、

を備える集積回路デバイスであり、

前記集積回路デバイスは、第1の集積回路デバイスであり、

前記第1の集積回路デバイスの第1のローカル時間に、第1の時間同期化メッセージを第2の集積回路デバイスに、送信し、

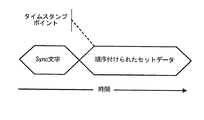

前記少なくとも1つのポートのうちの第1ポートにより、第2の時間同期化メッセージを、前記第2の集積回路デバイスから受信し、前記第2の時間同期化メッセージは、タイムスタンプポイントを有する順序付けられたデータセットを含み、

前記第2の時間同期化メッセージの前記タイムスタンプポイントが前記第1の集積回路デバイス内の参照点を渡すときに、タイムスタンプを生成し、前記タイムスタンプは、前記第1の集積回路デバイスの第2のローカル時間であり、

前記第2の集積回路デバイスの第3および第4のローカル時間を含む第3の時間同期化メッセージを受信し、前記第3の時間同期化メッセージは、前記第2の時間同期化メッセージとは異なる時間で受信され、

前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の第1のオフセット値を決定し、該決定することは、前記第1の集積回路デバイス内で生成される前記タイムスタンプおよび前記第1の集積回路デバイスの前記第1のローカル時間、前記第2の集積回路デバイスの前記第3および第4のローカル時間、ならびに前記第1の集積回路デバイスおよび前記第2の集積回路デバイスの間の送信および受信パスの間の時間非対称修正に少なくとも部分的に基づいて、前記第1のオフセット値を算出することを含み、前記時間非対称修正は、前記第1の集積回路デバイスおよび前記第2の集積回路デバイスの間の前記送信および受信パスの間の非対称を修正する、集積回路デバイス。

[項目22]

前記タイムスタンプは、少なくとも8ナノ秒の解像度を有する、項目21に記載の集積回路デバイス。

[項目23]

前記集積回路デバイスは、さらに、周波数オフセット値を決定し、前記周波数オフセット値は、前記第2の集積回路デバイスのクロックと前記第1の集積回路デバイスの前記自励発振器との間の周波数の前記オフセットを表す、項目21または22に記載の集積回路デバイス。

[項目24]

前記集積回路デバイスは、さらに、PCI Express、USB,およびDisplayPortプロトコルに従って複数のデバイス間でデータを送信するマルチプロトコル入出力ファブリックの一部である、項目21から23のいずれか一項に記載の集積回路デバイス。

[項目25]

前記第1の時間同期化メッセージは、時間sync通知に順序付けられたセット(TSNOS)である、項目21から24のいずれか一項に記載の集積回路デバイス。

[項目26]

前記集積回路デバイスは、さらに、決定された時間オフセット値を格納する時間オフセットレジスタを含む、項目21から25のいずれか一項に記載の集積回路デバイス。

[項目27]

前記集積回路デバイスは、さらに、決定された周波数オフセット値を格納する周波数オフセットレジスタを含む、項目23に記載の集積回路デバイス。

[項目28]

前記集積回路デバイスは、さらに、前記少なくとも1つのポートのうちの第2ポートにより、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記第1のオフセット値を、第3の集積回路デバイスに送信する、項目21から27のいずれか一項に記載の集積回路デバイス。

[項目29]

前記集積回路デバイスは、さらに、第3の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の第2のオフセット値を決定し、前記第2のオフセット値は、前記第3の集積回路デバイスのローカル時間からの前記第2の集積回路デバイスのローカル時間の第3のオフセット値と、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記第1のオフセット値と、の和であり、前記第3の時間同期化メッセージは、さらに、前記第3のオフセット値を含む、項目21から28のいずれか一項に記載の集積回路デバイス。

[項目30]

プロセッサと、

前記プロセッサに操作可能に連結されたメモリと、

前記プロセッサに操作可能に連結された入出力相互接続(I/O相互接続)と、

を備えるシステムであり、前記入出力相互接続は、

スイッチと、自励発振器であるローカルクロックと、少なくとも1つのポートと、を含む集積回路デバイスであり、前記集積回路デバイスは、第1の集積回路デバイスであり、

前記第1の集積回路デバイスの第1のローカル時間にて、第2の集積回路デバイスに第1の時間同期化メッセージを送信し、

前記少なくとも1つのポートのうちの第1ポートにより、前記第2の集積回路デバイスからの第2の時間同期化メッセージを受信し、前記第2の時間同期化メッセージは、タイムスタンプポイントを有する順序付けられたデータセットを含み、

前記第2の時間同期化メッセージの前記タイムスタンプポイントが前記第1の集積回路デバイス内の参照点を渡すときに、タイムスタンプを生成し、前記タイムスタンプは、前記第1の集積回路デバイスの第2のローカル時間であり、

前記第2の集積回路デバイスの第3および第4のローカル時間を含む第3の時間同期化メッセージを受信し、前記第3の時間同期化メッセージは、前記第2の時間同期化メッセージとは異なる時間で受信され、

前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間のオフセット値を決定し、該決定することは、前記第1の集積回路デバイス内で生成される前記タイムスタンプおよび前記第1の集積回路デバイスの前記第1のローカル時間、前記第2の集積回路デバイスの前記第3および第4のローカル時間、ならびに前記第1の集積回路デバイスおよび前記第2の集積回路デバイスの間の送信および受信パスの間の時間非対称修正に少なくとも部分的に基づいて、前記オフセット値を算出することを含み、前記時間非対称修正は、前記第1の集積回路デバイスおよび前記第2の集積回路デバイスの間の前記送信および受信パスの間の非対称を修正する、システム。

[項目31]

前記タイムスタンプは、少なくとも8ナノ秒の解像度を有する、項目30に記載のシステム。

[項目32]

前記集積回路デバイスは、さらに、周波数オフセット値を決定し、前記周波数オフセット値は、前記第2の集積回路デバイスのクロックと前記第1の集積回路デバイスの前記自励発振器との間の周波数の前記オフセットを表す、項目30または31に記載のシステム。

[項目33]

前記集積回路デバイスは、さらに、PCI Express、USB,およびDisplayPortプロトコルに従って複数のデバイス間でデータを送信するマルチプロトコル入出力ファブリックの一部である、項目30から32のいずれか一項に記載のシステム。

[項目34]

前記第1の時間同期化メッセージは、時間sync通知に順序付けられたセット(TSNOS)である、項目30から33のいずれか一項に記載のシステム。

[項目35]

前記集積回路デバイスは、さらに、決定された時間オフセット値を格納する時間オフセットレジスタを含む、項目30から34のいずれか一項に記載のシステム。

[項目36]

前記集積回路デバイスは、さらに、決定された周波数オフセット値を格納する周波数オフセットレジスタを含む、項目32に記載のシステム。

[項目37]

前記集積回路デバイスは、さらに、前記少なくとも1つのポートのうちの第2ポートにより、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記オフセット値を、第3の集積回路デバイスに送信する、項目30から36のいずれか一項に記載のシステム。

[項目38]

前記集積回路デバイスは、さらに、第3の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の追加のオフセット値を決定し、前記追加のオフセット値は、前記第3の集積回路デバイスのローカル時間からの前記第2の集積回路デバイスのローカル時間のオフセット値と、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記オフセット値と、の和である、項目30から37のいずれか一項に記載のシステム。

[項目39]

プロセッサと、

集積回路デバイスと、

を備えるシステムであり、前記プロセッサおよび前記集積回路デバイスは操作可能に接続され、前記システムは周辺デバイスであり、前記集積回路デバイスは、

スイッチと、

自励発振器であるローカルクロックと、

少なくとも2つのポートと、

を含み、前記集積回路デバイスは第1の集積回路デバイスであり、

前記第1の集積回路デバイスの第1のローカル時間にて、第2の集積回路デバイスに第1の時間同期化メッセージを送信し、

前記少なくとも2つのポートのうちの第1ポートにより、前記第2の集積回路デバイスからの第2の時間同期化メッセージを受信し、前記第2の時間同期化メッセージは、第1のタイムスタンプポイントを有する第1の順序付けられたデータセットを含み、

前記第2の時間同期化メッセージの第1のタイムスタンプポイントが前記第1の集積回路デバイス内の参照点を渡すときに、第1のタイムスタンプを生成し、前記第1のタイムスタンプは、前記第1の集積回路デバイスの第2のローカル時間であり、

前記第2の集積回路デバイスの第3および第4のローカル時間を含む第3の時間同期化メッセージを受信し、前記第3の時間同期化メッセージは、前記第2の時間同期化メッセージとは異なる時間で受信され、

前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の第1のオフセット値を決定し、該決定することは、前記第1の集積回路デバイスの前記第1のローカル時間および前記第2のローカル時間ならびに前記第2の集積回路デバイスの前記第3のローカル時間および第4のローカル時間、ならびに前記第1の集積回路デバイスおよび前記第2の集積回路デバイスの間の送信および受信パスの間の時間非対称修正に少なくとも部分的に基づいて、前記第1のオフセット値を算出することを含み、

前記第1の集積回路デバイスは、また、

前記少なくとも2つのポートのうちの第2ポートにより、第3の集積回路デバイスからの第5の時間同期化メッセージを受信し、前記第5の時間同期化メッセージは、第2のタイムスタンプポイントを有する第2の順序付けられたデータセットを含み、

前記第5の時間同期化メッセージの前記第2のタイムスタンプポイントが前記第1の集積回路デバイス内の参照点を渡すときに、第2のタイムスタンプを生成し、前記第2のタイムスタンプは、前記第1の集積回路デバイスの第5のローカル時間であり、

前記第5のローカル時間を含む第6の時間同期化メッセージを前記第3の集積回路デバイスに送信する、システム。

[項目40]

前記第1及び第2のタイムスタンプは、少なくとも8ナノ秒の解像度を有する、項目39に記載のシステム。

[項目41]

前記集積回路デバイスは、さらに、周波数オフセット値を決定し、前記周波数オフセット値は、前記第2の集積回路デバイスのクロックと前記第1の集積回路デバイスの前記自励発振器との間の周波数の前記オフセットを表す、項目39または40に記載のシステム。

[項目42]

前記集積回路デバイスは、さらに、PCI Express、USB,およびDisplayPortプロトコルに従って複数のデバイス間でデータを受信および送信する、項目39から41のいずれか一項に記載のシステム。

[項目43]

前記第1の時間同期化メッセージおよび前記第2の時間同期化メッセージは、時間sync通知に順序付けられたセット(TSNOS)である、項目39から42のいずれか一項に記載のシステム。

[項目44]

前記集積回路デバイスは、さらに、決定された時間オフセット値を格納する時間オフセットレジスタを含む、項目39から43のいずれか一項に記載のシステム。

[項目45]

前記集積回路デバイスは、さらに、決定された周波数オフセット値を格納する周波数オフセットレジスタを含む、項目41に記載のシステム。

[項目46]

前記集積回路デバイスは、さらに、前記第2ポートにより、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記第1のオフセット値を、前記第3の集積回路デバイスに送信する、項目39から45のいずれか一項に記載のシステム。

[項目47]

前記集積回路デバイスは、さらに、第4の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の第2のオフセット値を決定し、前記第2のオフセット値は、前記第4の集積回路デバイスのローカル時間からの前記第2の集積回路デバイスのローカル時間の第3のオフセット値と、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記第1のオフセット値と、の和であり、前記第3の時間同期化メッセージは、さらに、前記第3のオフセット値を含む、項目39から46のいずれか一項に記載のシステム。

[項目48]

前記システムは、さらに、ディスプレイを備え、前記ディスプレイは、前記プロセッサおよび前記集積回路デバイスに操作可能に接続される、項目39から47のいずれか一項に記載のシステム。

Claims (43)

- マルチプロトコルの相互接続のスイッチングファブリック内で複数のドメインにわたり時間を同期化する方法であって、

前記スイッチングファブリックの第1のドメインの第1のスイッチにより前記第1のスイッチの第1のローカル時間を前記第1のドメインの第2のスイッチに提供する段階と、

前記第1のドメイン内の前記第1および第2のスイッチを同期させるべく、前記第2のスイッチにより前記第2のスイッチの第2のローカル時間を前記第1のローカル時間に対して調節する段階であって、前記第1のスイッチから受信したタイムスタンプに少なくとも部分的に基いてオフセット値を算出する段階と、前記オフセット値によって前記第2のローカル時間を調節する段階とを有する、調節する段階と、

前記スイッチングファブリックの第2のドメインの第3のスイッチに対し、前記第1のローカル時間を前記第2のスイッチにより提供する段階と、

前記第1のドメインの前記第1および第2のスイッチと前記第2のドメインの前記第3のスイッチとを同期させるべく、前記第3のスイッチにより前記第3のスイッチの第3のローカル時間を前記第1のローカル時間に対して調節する段階と

を備え、

前記オフセット値は、時間同期化通知の順序付けられたセット(TSNOS)を用いた前記タイムスタンプのための送信および受信パスの間の複数の時間非対称修正に基いて計算され、

前記複数の時間非対称修正は、

前記第1のスイッチによる前記TSNOSに伴う前記タイムスタンプの送信と、前記第2のスイッチによる前記タイムスタンプの受信との間、および、前記第2のスイッチによる前記タイムスタンプの受信の応答の送信と、前記第2のスイッチによる前記応答の受信との間の時間遅延と、

前記タイムスタンプが得られるときの第1時刻と、前記TSNOSの第1ビットが送信または受信されるときの第2時刻との間の経過時間とを示す方法。 - 前記第2のスイッチによる前記調節する段階は、前記第2のスイッチの自励発振器の前記タイムスタンプに少なくとも部分的に基いて前記第2のローカル時間を決定する段階を有する、請求項1に記載の方法。

- 前記第2のスイッチの第1のポートから前記第2のスイッチの第2のポートに、前記調節された第2のローカル時間を提供する段階を更に有する、請求項2に記載の方法。

- 前記第1のローカル時間を前記第2のスイッチに提供する段階は、前記第1のスイッチの第1のポートから前記第2のスイッチの第2のポートに、前記第1のローカル時間を提供する段階を有する、請求項1〜3のいずれか一項に記載の方法。

- 前記第1のローカル時間を前記第2のスイッチに提供する前記段階は前記第1のスイッチの自励発振器の周波数の値を前記第2のスイッチに提供する段階を有し、前記方法は前記第2のスイッチから前記第3のスイッチに前記周波数の値を提供する段階を更に有する、請求項1〜4のいずれか一項に記載の方法。

- 前記第3のスイッチから前記第2のドメインの第4のスイッチに前記第1のローカル時間を提供する段階と、

前記第4のスイッチの第4のローカル時間を前記第1のローカル時間に調節する段階と

を更に有する、請求項1〜5のいずれか一項に記載の方法。 - 前記調節された第4のローカル時間を前記第3のスイッチに提供する段階と、

前記第3のスイッチの第3のローカル時間を前記調節された第4のローカル時間に調節する段階と

を備える、請求項6に記載の方法。 - 前記調節された第4のローカル時間を前記第2のドメインの第5のスイッチに提供する段階と、

前記第5のスイッチの第5のローカル時間を前記調節された第4のローカル時間に調節する段階と

を更に備える、請求項6または7に記載の方法。 - マルチプロトコルの相互接続のスイッチングファブリック内で複数のドメインにわたり時間を同期化するプログラムであって、

コンピュータに、

前記スイッチングファブリックの第1のドメインの第1のスイッチの第1のローカル時間を前記スイッチングファブリックの前記第1のドメインの第2のスイッチに提供することと、

前記第1のドメイン内の前記第1および前記第2のスイッチを同期させるべく、前記第2のスイッチの第2のローカル時間を前記第1のローカル時間に対して調節することであって、前記第1のスイッチから受信したタイムスタンプに少なくとも部分的に基いてオフセット値を算出することと、前記オフセット値によって前記第2のローカル時間を調節することとを有する、調節することと、

前記スイッチングファブリックの第2のドメインの第3のスイッチに対し、前記第2のスイッチの前記第1のローカル時間を提供することと、

前記第1のドメインの前記第1および第2のスイッチと前記第2のドメインの前記第3のスイッチとを同期させるべく、前記第3のスイッチの第3のローカル時間を前記第1のローカル時間に対して調節することと

を行わせ、

前記オフセット値は、時間同期化通知の順序付けられたセット(TSNOS)を用いた前記タイムスタンプのための送信および受信パスの間の複数の時間非対称修正に基いて計算され、

前記複数の時間非対称修正は、

前記第1のスイッチによる前記TSNOSに伴う前記タイムスタンプの送信と、前記第2のスイッチによる前記タイムスタンプの受信との間、および、前記第2のスイッチによる前記タイムスタンプの受信の応答の送信と、前記第2のスイッチによる前記応答の受信との間の時間遅延と、

前記タイムスタンプが得られるときの第1時刻と、前記TSNOSの第1ビットが送信または受信されるときの第2時刻との間の経過時間とを示すプログラム。 - 前記第2のローカル時間を調節することは、前記第2のスイッチの自励発振器のタイムスタンプに少なくとも部分的に基いて前記第2のローカル時間を決定することを含む、請求項9に記載のプログラム。

- 前記第1のローカル時間を前記第2のスイッチに提供することは、前記第1のスイッチの第1のポートから前記第2のスイッチの第2のポートに前記第1のローカル時間を提供することを含む、請求項9または10に記載のプログラム。

- 請求項9〜11のいずれか一項に記載のプログラムを格納するコンピュータ可読媒体。

- マルチプロトコルの相互接続のスイッチングファブリック内で複数のドメインにわたり時間を同期化するシステムであって、

複数のスイッチを有する前記スイッチングファブリックを有する前記マルチプロトコルの相互接続を含むI/O複合体と、

前記I/O複合体と動作可能に結合された1つまたは複数のプロセッサと、

前記1つまたは複数のプロセッサと動作可能に結合され、内部に複数のプログラミング命令を記憶したコンピュータ読取可能な非一時的記憶媒体であって、前記複数のプログラミング命令の実行に応答して、前記システムが、

前記スイッチングファブリックの第1のドメインの第1のスイッチの第1のローカル時間を前記スイッチングファブリックの前記第1のドメインの第2のスイッチに提供することと、

前記第1のドメイン内の前記第1および前記第2のスイッチを同期させるべく、前記第2のスイッチの第2のローカル時間を前記第1のローカル時間に対して調節することであって、前記第1のスイッチから受信したタイムスタンプに少なくとも部分的に基いてオフセット値を算出することと、前記オフセット値によって前記第2のローカル時間を調節することとを有する、調節することと、

前記スイッチングファブリックの第2のドメインの第3のスイッチに対し、前記第2のスイッチの前記第1のローカル時間を提供することと、

前記第1のドメインの前記第1および第2のスイッチと前記第2のドメインの前記第3のスイッチとを同期させるべく、前記第3のスイッチの第3のローカル時間を前記第1のローカル時間に対して調節することと

を可能にするコンピュータ読取可能な非一時的記憶媒体と、

前記I/O複合体および前記1つまたは複数のプロセッサに動作可能に結合された表示装置と

を備え、

前記オフセット値は、時間同期化通知の順序付けられたセット(TSNOS)を用いた前記タイムスタンプのための送信および受信パスの間の複数の時間非対称修正に基いて計算され、

前記複数の時間非対称修正は、

前記第1のスイッチによる前記TSNOSに伴う前記タイムスタンプの送信と、前記第2のスイッチによる前記タイムスタンプの受信との間、および、前記第2のスイッチによる前記タイムスタンプの受信の応答の送信と、前記第2のスイッチによる前記応答の受信との間の時間遅延と、

前記タイムスタンプが得られるときの第1時刻と、前記TSNOSの第1ビットが送信または受信されるときの第2時刻との間の経過時間とを示すシステム。 - 前記システムは、デスクトップコンピュータ、ラップトップコンピュータ、ハンドヘルドコンピュータ、タブレットコンピュータ、ネットブックコンピュータ、サーバー、セットトップボックス、デジタル記録装置、ゲームコンソール、スマートフォン、携帯情報端末、携帯電話、デジタルメディアプレーヤ、またはデジタルカメラのうちの選択された1つである、請求項13に記載のシステム。

- バスによって前記I/O複合体に動作可能に結合され、無線ネットワークの1つまたは複数のコンポーネントとの無線通信リンクを確立する1つまたは複数のアンテナを更に備える、請求項13または14に記載のシステム。

- スイッチと、

自励発振器であるローカルクロックと、

少なくとも1つのポートと、

を備える集積回路デバイスであり、

前記集積回路デバイスは、第1の集積回路デバイスであり、

前記第1の集積回路デバイスの第1のローカル時間に、第1の時間同期化メッセージを第2の集積回路デバイスに、送信し、

前記少なくとも1つのポートのうちの第1ポートにより、第2の時間同期化メッセージを、前記第2の集積回路デバイスから受信し、前記第2の時間同期化メッセージは、タイムスタンプポイントを有する順序付けられたデータセットを含み、

前記第2の時間同期化メッセージの前記タイムスタンプポイントが前記第1の集積回路デバイス内の参照点を通過するときに、タイムスタンプを生成し、前記タイムスタンプは、前記第1の集積回路デバイスの第2のローカル時間であり、

前記第2の集積回路デバイスの第3および第4のローカル時間を含む第3の時間同期化メッセージを受信し、前記第3の時間同期化メッセージは、前記第2の時間同期化メッセージとは異なる時間で受信され、

前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の第1のオフセット値を決定し、該決定することは、前記第1の集積回路デバイス内で生成される前記タイムスタンプおよび前記第1の集積回路デバイスの前記第1のローカル時間、前記第2の集積回路デバイスの前記第3および第4のローカル時間、ならびに前記第1の集積回路デバイスおよび前記第2の集積回路デバイスの間の送信および受信パスの間の時間非対称修正に少なくとも部分的に基づいて、前記第1のオフセット値を算出することを含み、前記時間非対称修正は、前記第1の集積回路デバイスおよび前記第2の集積回路デバイスの間の前記送信および受信パスの間の非対称を修正する、集積回路デバイス。 - 前記タイムスタンプは、少なくとも8ナノ秒の解像度を有する、請求項16に記載の集積回路デバイス。

- 前記集積回路デバイスは、さらに、周波数オフセット値を決定し、前記周波数オフセット値は、前記第2の集積回路デバイスのクロックと前記第1の集積回路デバイスの前記自励発振器との間の周波数の前記オフセットを表す、請求項16または17に記載の集積回路デバイス。

- 前記集積回路デバイスは、さらに、PCI Express、USB,およびDisplayPortプロトコルに従って複数のデバイス間でデータを送信するマルチプロトコル入出力ファブリックの一部である、請求項16から18のいずれか一項に記載の集積回路デバイス。

- 前記第1の時間同期化メッセージは、時間sync通知の順序付けられたセット(TSNOS)である、請求項16から19のいずれか一項に記載の集積回路デバイス。

- 前記集積回路デバイスは、さらに、決定された時間オフセット値を格納する時間オフセットレジスタを含む、請求項16から20のいずれか一項に記載の集積回路デバイス。

- 前記集積回路デバイスは、さらに、決定された周波数オフセット値を格納する周波数オフセットレジスタを含む、請求項18に記載の集積回路デバイス。

- 前記集積回路デバイスは、さらに、前記少なくとも1つのポートのうちの第2ポートにより、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記第1のオフセット値を、第3の集積回路デバイスに送信する、請求項16から22のいずれか一項に記載の集積回路デバイス。

- 前記集積回路デバイスは、さらに、第3の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の第2のオフセット値を決定し、前記第2のオフセット値は、前記第3の集積回路デバイスのローカル時間からの前記第2の集積回路デバイスのローカル時間の第3のオフセット値と、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記第1のオフセット値と、の和であり、前記第3の時間同期化メッセージは、さらに、前記第3のオフセット値を含む、請求項16から23のいずれか一項に記載の集積回路デバイス。

- プロセッサと、

前記プロセッサに操作可能に連結されたメモリと、

前記プロセッサに操作可能に連結された入出力相互接続(I/O相互接続)と、

を備えるシステムであり、前記入出力相互接続は、

スイッチと、自励発振器であるローカルクロックと、少なくとも1つのポートと、を含む集積回路デバイスであり、前記集積回路デバイスは、第1の集積回路デバイスであり、

前記第1の集積回路デバイスの第1のローカル時間にて、第2の集積回路デバイスに第1の時間同期化メッセージを送信し、

前記少なくとも1つのポートのうちの第1ポートにより、前記第2の集積回路デバイスからの第2の時間同期化メッセージを受信し、前記第2の時間同期化メッセージは、タイムスタンプポイントを有する順序付けられたデータセットを含み、

前記第2の時間同期化メッセージの前記タイムスタンプポイントが前記第1の集積回路デバイス内の参照点を通過するときに、タイムスタンプを生成し、前記タイムスタンプは、前記第1の集積回路デバイスの第2のローカル時間であり、

前記第2の集積回路デバイスの第3および第4のローカル時間を含む第3の時間同期化メッセージを受信し、前記第3の時間同期化メッセージは、前記第2の時間同期化メッセージとは異なる時間で受信され、

前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間のオフセット値を決定し、該決定することは、前記第1の集積回路デバイス内で生成される前記タイムスタンプおよび前記第1の集積回路デバイスの前記第1のローカル時間、前記第2の集積回路デバイスの前記第3および第4のローカル時間、ならびに前記第1の集積回路デバイスおよび前記第2の集積回路デバイスの間の送信および受信パスの間の時間非対称修正に少なくとも部分的に基づいて、前記オフセット値を算出することを含み、前記時間非対称修正は、前記第1の集積回路デバイスおよび前記第2の集積回路デバイスの間の前記送信および受信パスの間の非対称を修正する、システム。 - 前記タイムスタンプは、少なくとも8ナノ秒の解像度を有する、請求項25に記載のシステム。

- 前記集積回路デバイスは、さらに、周波数オフセット値を決定し、前記周波数オフセット値は、前記第2の集積回路デバイスのクロックと前記第1の集積回路デバイスの前記自励発振器との間の周波数の前記オフセットを表す、請求項25または26に記載のシステム。

- 前記集積回路デバイスは、さらに、PCI Express、USB,およびDisplayPortプロトコルに従って複数のデバイス間でデータを送信するマルチプロトコル入出力ファブリックの一部である、請求項25から27のいずれか一項に記載のシステム。

- 前記第1の時間同期化メッセージは、時間sync通知の順序付けられたセット(TSNOS)である、請求項25から28のいずれか一項に記載のシステム。

- 前記集積回路デバイスは、さらに、決定された時間オフセット値を格納する時間オフセットレジスタを含む、請求項25から29のいずれか一項に記載のシステム。

- 前記集積回路デバイスは、さらに、決定された周波数オフセット値を格納する周波数オフセットレジスタを含む、請求項27に記載のシステム。

- 前記集積回路デバイスは、さらに、前記少なくとも1つのポートのうちの第2ポートにより、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記オフセット値を、第3の集積回路デバイスに送信する、請求項25から31のいずれか一項に記載のシステム。

- 前記集積回路デバイスは、さらに、第3の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の追加のオフセット値を決定し、前記追加のオフセット値は、前記第3の集積回路デバイスのローカル時間からの前記第2の集積回路デバイスのローカル時間のオフセット値と、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記オフセット値と、の和である、請求項25から32のいずれか一項に記載のシステム。

- プロセッサと、

集積回路デバイスと、

を備えるシステムであり、前記プロセッサおよび前記集積回路デバイスは操作可能に接続され、前記システムは周辺デバイスであり、前記集積回路デバイスは、

スイッチと、

自励発振器であるローカルクロックと、

少なくとも2つのポートと、

を含み、前記集積回路デバイスは第1の集積回路デバイスであり、

前記第1の集積回路デバイスの第1のローカル時間にて、第2の集積回路デバイスに第1の時間同期化メッセージを送信し、

前記少なくとも2つのポートのうちの第1ポートにより、前記第2の集積回路デバイスからの第2の時間同期化メッセージを受信し、前記第2の時間同期化メッセージは、第1のタイムスタンプポイントを有する第1の順序付けられたデータセットを含み、

前記第2の時間同期化メッセージの第1のタイムスタンプポイントが前記第1の集積回路デバイス内の参照点を通過するときに、第1のタイムスタンプを生成し、前記第1のタイムスタンプは、前記第1の集積回路デバイスの第2のローカル時間であり、

前記第2の集積回路デバイスの第3および第4のローカル時間を含む第3の時間同期化メッセージを受信し、前記第3の時間同期化メッセージは、前記第2の時間同期化メッセージとは異なる時間で受信され、

前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の第1のオフセット値を決定し、該決定することは、前記第1の集積回路デバイスの前記第1のローカル時間および前記第2のローカル時間ならびに前記第2の集積回路デバイスの前記第3のローカル時間および第4のローカル時間、ならびに前記第1の集積回路デバイスおよび前記第2の集積回路デバイスの間の送信および受信パスの間の時間非対称修正に少なくとも部分的に基づいて、前記第1のオフセット値を算出することを含み、

前記第1の集積回路デバイスは、また、

前記少なくとも2つのポートのうちの第2ポートにより、第3の集積回路デバイスからの第5の時間同期化メッセージを受信し、前記第5の時間同期化メッセージは、第2のタイムスタンプポイントを有する第2の順序付けられたデータセットを含み、

前記第5の時間同期化メッセージの前記第2のタイムスタンプポイントが前記第1の集積回路デバイス内の参照点を通過するときに、第2のタイムスタンプを生成し、前記第2のタイムスタンプは、前記第1の集積回路デバイスの第5のローカル時間であり、

前記第5のローカル時間を含む第6の時間同期化メッセージを前記第3の集積回路デバイスに送信する、システム。 - 前記第1及び第2のタイムスタンプは、少なくとも8ナノ秒の解像度を有する、請求項34に記載のシステム。

- 前記集積回路デバイスは、さらに、周波数オフセット値を決定し、前記周波数オフセット値は、前記第2の集積回路デバイスのクロックと前記第1の集積回路デバイスの前記自励発振器との間の周波数の前記オフセットを表す、請求項34または35に記載のシステム。

- 前記集積回路デバイスは、さらに、PCI Express、USB,およびDisplayPortプロトコルに従って複数のデバイス間でデータを受信および送信する、請求項34から36のいずれか一項に記載のシステム。

- 前記第1の時間同期化メッセージおよび前記第2の時間同期化メッセージは、時間sync通知の順序付けられたセット(TSNOS)である、請求項34から37のいずれか一項に記載のシステム。

- 前記集積回路デバイスは、さらに、決定された時間オフセット値を格納する時間オフセットレジスタを含む、請求項34から38のいずれか一項に記載のシステム。

- 前記集積回路デバイスは、さらに、決定された周波数オフセット値を格納する周波数オフセットレジスタを含む、請求項36に記載のシステム。

- 前記集積回路デバイスは、さらに、前記第2ポートにより、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記第1のオフセット値を、前記第3の集積回路デバイスに送信する、請求項34から40のいずれか一項に記載のシステム。

- 前記集積回路デバイスは、さらに、第4の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の第2のオフセット値を決定し、前記第2のオフセット値は、前記第4の集積回路デバイスのローカル時間からの前記第2の集積回路デバイスのローカル時間の第3のオフセット値と、前記第2の集積回路デバイスのローカル時間からの前記第1の集積回路デバイスのローカル時間の前記第1のオフセット値と、の和であり、前記第3の時間同期化メッセージは、さらに、前記第3のオフセット値を含む、請求項34から41のいずれか一項に記載のシステム。

- 前記システムは、さらに、ディスプレイを備え、前記ディスプレイは、前記プロセッサおよび前記集積回路デバイスに操作可能に接続される、請求項34から42のいずれか一項に記載のシステム。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/338,236 US8953644B2 (en) | 2011-12-27 | 2011-12-27 | Multi-protocol I/O interconnect time synchronization |

| US13/338,236 | 2011-12-27 | ||

| PCT/US2012/067438 WO2013101393A1 (en) | 2011-12-27 | 2012-11-30 | Multi-protocol i/o interconnect time synchronization |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015505214A JP2015505214A (ja) | 2015-02-16 |

| JP2015505214A5 JP2015505214A5 (ja) | 2016-01-14 |

| JP5867765B2 true JP5867765B2 (ja) | 2016-02-24 |

Family

ID=48654515

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014550304A Active JP5867765B2 (ja) | 2011-12-27 | 2012-11-30 | マルチプロトコルのi/o相互接続の時間同期化 |

Country Status (3)

| Country | Link |

|---|---|

| US (3) | US8953644B2 (ja) |

| JP (1) | JP5867765B2 (ja) |

| WO (1) | WO2013101393A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11316628B2 (en) | 2019-10-31 | 2022-04-26 | Dell Products L.P. | Information handling system multi-stream cable throughput management |

Families Citing this family (49)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8953644B2 (en) * | 2011-12-27 | 2015-02-10 | Intel Corporation | Multi-protocol I/O interconnect time synchronization |

| JP6418417B2 (ja) * | 2013-07-16 | 2018-11-07 | マーベル ワールド トレード リミテッド | Usbデータ転送を管理するシステムおよび方法 |

| US9667370B2 (en) * | 2013-09-05 | 2017-05-30 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Communication device with peer-to-peer assist to provide synchronization |

| US9442511B2 (en) * | 2013-10-15 | 2016-09-13 | Eci Telecom Ltd. | Method and a device for maintaining a synchronized local timer using a periodic signal |

| JP2017098588A (ja) * | 2014-02-20 | 2017-06-01 | 日本電気株式会社 | 通信システム、無線通信装置及び無線通信方法 |

| US9678910B2 (en) | 2014-04-25 | 2017-06-13 | Liqid Inc. | Power handling in a scalable storage system |

| US10467166B2 (en) | 2014-04-25 | 2019-11-05 | Liqid Inc. | Stacked-device peripheral storage card |

| US9645902B2 (en) | 2014-06-23 | 2017-05-09 | Liqid Inc. | Modular switched fabric for data storage systems |

| US10362107B2 (en) * | 2014-09-04 | 2019-07-23 | Liqid Inc. | Synchronization of storage transactions in clustered storage systems |

| US9483209B2 (en) | 2014-09-22 | 2016-11-01 | Freescale Semiconductor, Inc. | Interface system and method |

| EP3226504B1 (en) * | 2014-12-16 | 2020-11-04 | Huawei Technologies Co., Ltd. | Time synchronization method and apparatus |

| US10198183B2 (en) | 2015-02-06 | 2019-02-05 | Liqid Inc. | Tunneling of storage operations between storage nodes |

| US10191691B2 (en) | 2015-04-28 | 2019-01-29 | Liqid Inc. | Front-end quality of service differentiation in storage system operations |

| US10108422B2 (en) | 2015-04-28 | 2018-10-23 | Liqid Inc. | Multi-thread network stack buffering of data frames |

| US10019388B2 (en) | 2015-04-28 | 2018-07-10 | Liqid Inc. | Enhanced initialization for data storage assemblies |

| US10701657B2 (en) * | 2015-06-24 | 2020-06-30 | Apple Inc. | Time synchronization for nodes in a wireless personal area network (WPAN) |

| US11983138B2 (en) | 2015-07-26 | 2024-05-14 | Samsung Electronics Co., Ltd. | Self-configuring SSD multi-protocol support in host-less environment |

| CN106658626B (zh) * | 2015-10-29 | 2020-12-22 | 中兴通讯股份有限公司 | 一种时钟切换的方法、装置及基站 |

| US10255215B2 (en) | 2016-01-29 | 2019-04-09 | Liqid Inc. | Enhanced PCIe storage device form factors |

| US10440598B2 (en) * | 2016-03-24 | 2019-10-08 | Marvell World Trade Ltd. | Methods and apparatus for clock drift mitigation with snoop-based ranging |

| US10210123B2 (en) | 2016-07-26 | 2019-02-19 | Samsung Electronics Co., Ltd. | System and method for supporting multi-path and/or multi-mode NMVe over fabrics devices |

| US10346041B2 (en) | 2016-09-14 | 2019-07-09 | Samsung Electronics Co., Ltd. | Method for using BMC as proxy NVMeoF discovery controller to provide NVM subsystems to host |

| US11461258B2 (en) | 2016-09-14 | 2022-10-04 | Samsung Electronics Co., Ltd. | Self-configuring baseboard management controller (BMC) |

| US11294839B2 (en) | 2016-08-12 | 2022-04-05 | Liqid Inc. | Emulated telemetry interfaces for fabric-coupled computing units |

| US11880326B2 (en) | 2016-08-12 | 2024-01-23 | Liqid Inc. | Emulated telemetry interfaces for computing units |

| EP3497571B1 (en) | 2016-08-12 | 2021-12-29 | Liqid Inc. | Disaggregated fabric-switched computing platform |

| EP3288197B1 (en) * | 2016-08-23 | 2022-06-15 | Robert Bosch GmbH | System and method of synchronizing clocks in a computer network |

| EP3288198B1 (en) * | 2016-08-23 | 2021-04-28 | Robert Bosch GmbH | System and method of clock synchronization in a computer network |

| US10856242B2 (en) * | 2016-11-21 | 2020-12-01 | Phasorlab, Inc. | Wireless time and frequency lock loop system |

| US20180293196A1 (en) * | 2017-04-10 | 2018-10-11 | Intel Corporation | System, Apparatus And Method For Link Training For A Multi-Drop Interconnect |

| CN108737001B (zh) * | 2017-04-24 | 2020-02-07 | 广东虚拟现实科技有限公司 | 一种数据处理方法及相关设备 |

| WO2018200761A1 (en) | 2017-04-27 | 2018-11-01 | Liqid Inc. | Pcie fabric connectivity expansion card |

| US10180924B2 (en) | 2017-05-08 | 2019-01-15 | Liqid Inc. | Peer-to-peer communication for graphics processing units |

| US11095556B2 (en) * | 2017-06-30 | 2021-08-17 | Intel Corporation | Techniques to support multiple protocols between computer system interconnects |

| US20190004990A1 (en) * | 2017-07-01 | 2019-01-03 | Stephen R. Van Doren | Techniques to support mulitple interconnect protocols for an interconnect |

| US11249808B2 (en) | 2017-08-22 | 2022-02-15 | Intel Corporation | Connecting accelerator resources using a switch |

| US10727966B1 (en) * | 2017-08-30 | 2020-07-28 | Amazon Technologies, Inc. | Time synchronization with distributed grand master |

| US10660228B2 (en) | 2018-08-03 | 2020-05-19 | Liqid Inc. | Peripheral storage card with offset slot alignment |

| WO2020054219A1 (ja) * | 2018-09-13 | 2020-03-19 | ソニーセミコンダクタソリューションズ株式会社 | 通信装置および通信システム |

| US10887038B2 (en) * | 2018-09-28 | 2021-01-05 | Samsung Electronics Co., Ltd. | GNSS-based multi-modal clock correction |

| US12204476B2 (en) | 2019-02-05 | 2025-01-21 | Liqid Inc. | Peer-to-peer communications initiated among communication fabric coupled endpoint devices |

| US10585827B1 (en) | 2019-02-05 | 2020-03-10 | Liqid Inc. | PCIe fabric enabled peer-to-peer communications |

| US10754559B1 (en) * | 2019-03-08 | 2020-08-25 | EMC IP Holding Company LLC | Active-active storage clustering with clock synchronization |

| EP3959608A4 (en) | 2019-04-25 | 2022-12-21 | Liqid Inc. | COMPOSITE COMPUTING SYSTEMS WITH CONVERGED AND DISAGGREGATED COMPONENT POOL |

| EP3959604B1 (en) | 2019-04-25 | 2024-08-28 | Liqid Inc. | Machine templates for predetermined compute units |

| US12107670B2 (en) * | 2019-04-29 | 2024-10-01 | Comcast Cable Communications, Llc | Container based time differentials |

| US11463187B2 (en) * | 2020-04-14 | 2022-10-04 | Google Llc | Fault tolerant design for clock-synchronization systems |

| US20200320026A1 (en) * | 2020-04-27 | 2020-10-08 | Intel Corporation | Bandwidth management allocation for displayport tunneling |

| US11442776B2 (en) | 2020-12-11 | 2022-09-13 | Liqid Inc. | Execution job compute unit composition in computing clusters |

Family Cites Families (76)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4767168A (en) | 1986-12-24 | 1988-08-30 | Prestolite Wire Corporation | Hybrid connector cable system |

| US4969924A (en) | 1989-05-18 | 1990-11-13 | General Motors Corporation | Electro-optical connector plug |

| JPH04138677A (ja) | 1990-09-28 | 1992-05-13 | Nec Corp | 複合コネクタ |

| DE4118096A1 (de) | 1991-06-03 | 1992-12-10 | Airbus Gmbh | Vorrichtung zur verbindung von leitungen |

| US5242315A (en) | 1992-05-21 | 1993-09-07 | Puritan-Bennett Corporation | Electrical-optical hybrid connector plug |

| JP3110583B2 (ja) | 1993-05-25 | 2000-11-20 | 三菱電機株式会社 | ルータ装置 |

| US5664231A (en) | 1994-04-29 | 1997-09-02 | Tps Electronics | PCMCIA interface card for coupling input devices such as barcode scanning engines to personal digital assistants and palmtop computers |

| US5419717A (en) | 1994-08-15 | 1995-05-30 | The Whitaker Corporation | Hybrid connector between optics and edge card |

| US5535036A (en) | 1995-01-18 | 1996-07-09 | Lighthouse Digital Systems, Inc. | Input/output module providing mixed optical and electrical signal connectivity in data communications equipment |

| JPH08316914A (ja) | 1995-05-15 | 1996-11-29 | Sumitomo Wiring Syst Ltd | 情報回線の配線構造 |

| US6108782A (en) | 1996-12-13 | 2000-08-22 | 3Com Corporation | Distributed remote monitoring (dRMON) for networks |

| JP3392314B2 (ja) | 1997-02-20 | 2003-03-31 | 株式会社日立インフォメーションテクノロジー | データ伝送方法 |

| JP3436650B2 (ja) | 1997-02-24 | 2003-08-11 | 三菱電機株式会社 | ネットワーク制御装置 |

| US6272551B1 (en) | 1998-04-08 | 2001-08-07 | Intel Corporation | Network adapter for transmitting network packets between a host device and a power line network |

| GB2350212B (en) | 1999-02-09 | 2003-10-08 | Adder Tech Ltd | Data routing device and system |

| JP3778479B2 (ja) | 1999-12-08 | 2006-05-24 | 矢崎総業株式会社 | 発光素子モジュール及び受光素子モジュールの位置決め方法、光コネクタ、及びハイブリッドコネクタ |

| KR100317991B1 (ko) | 2000-01-25 | 2001-12-22 | 오길록 | 기가비트 이더넷 기반 라우터에서의 병렬처리형 3계층패킷 포워딩 처리 방법 및 장치 |

| US6839771B1 (en) | 2000-04-13 | 2005-01-04 | Hewlett-Packard Development Company, L.P. | Method and system for using a universal serial bus (USB) as a peer-to-peer network |

| US6751238B1 (en) | 2000-04-20 | 2004-06-15 | Aztech Partners, Inc. | Phase re-alignment of SONET/SDH network switch without pointer manipulation |

| US6478625B2 (en) | 2000-07-11 | 2002-11-12 | Bernard R. Tolmie | Electrical-optical hybrid connector |

| US7184440B1 (en) | 2000-07-26 | 2007-02-27 | Alcatel Canada Inc. | Multi-protocol switch and method therefore |

| US6588938B1 (en) | 2000-10-18 | 2003-07-08 | Fitel Usa Corp. | Optical/electrical plug connector |

| AU2002224424A1 (en) | 2000-10-23 | 2002-05-06 | Digital Software Corporation | Method and apparatus for providing optical internetworking to wide area networks, metropolitan area networks, and local area networks using modular components |

| JP4550268B2 (ja) | 2000-12-20 | 2010-09-22 | 古河電気工業株式会社 | 光・電気複合コネクタ |

| US7002996B1 (en) | 2001-04-09 | 2006-02-21 | Applied Micro Circuits Corporation | System and method for switch timing synchronization |

| JP3972596B2 (ja) | 2001-04-20 | 2007-09-05 | 株式会社日立製作所 | ディスクアレイシステム |

| JP4494668B2 (ja) | 2001-04-27 | 2010-06-30 | 古河電気工業株式会社 | コネクタ |

| US7072996B2 (en) | 2001-06-13 | 2006-07-04 | Corrent Corporation | System and method of transferring data between a processing engine and a plurality of bus types using an arbiter |

| US7023356B2 (en) * | 2001-11-26 | 2006-04-04 | Aero-Vision Technologies, Inc. | System and method for monitoring individuals and objects associated with wireless identification tags |

| US7873028B2 (en) | 2002-01-25 | 2011-01-18 | Quanta Computer, Inc. | Method and apparatus for a flexible peripheral access router |

| JP3725828B2 (ja) | 2002-02-21 | 2005-12-14 | 日本電信電話株式会社 | 光電気パス統合網およびノード |

| US7283481B2 (en) | 2002-03-21 | 2007-10-16 | Broadcom Corporation | Auto detection of copper and fiber mode |

| US7171505B2 (en) | 2002-05-02 | 2007-01-30 | International Business Machines Corporation | Universal network interface connection |

| US7447778B2 (en) | 2002-05-06 | 2008-11-04 | Qlogic, Corporation | System and method for a shared I/O subsystem |

| ATE459053T1 (de) | 2002-07-17 | 2010-03-15 | Chronologic Pty Ltd | Synchronisierter multikanal-usb |

| JP4140334B2 (ja) | 2002-10-04 | 2008-08-27 | 富士ゼロックス株式会社 | 光分配器及び光分配システム |

| US7269348B1 (en) | 2002-11-18 | 2007-09-11 | At&T Corp. | Router having dual propagation paths for packets |

| US7330468B1 (en) | 2002-11-18 | 2008-02-12 | At&T Corp. | Scalable, reconfigurable routers |

| JP4277189B2 (ja) | 2003-02-19 | 2009-06-10 | 株式会社 インテック・ネットコア | ルータ装置及びパケット転送制御方法 |

| US7397823B2 (en) | 2003-06-04 | 2008-07-08 | Agilent Technologies, Inc. | Providing time synchronization across store-and-forward communication devices using protocol-enabled switches |

| US7613212B1 (en) * | 2003-06-10 | 2009-11-03 | Atrica Israel Ltd. | Centralized clock synchronization for time division multiplexed traffic transported over Ethernet networks |

| TWI249313B (en) | 2003-07-11 | 2006-02-11 | Ezhi Technologies Inc | Multi-tasking scheduling management system of WLAN |

| TWM251361U (en) | 2003-07-25 | 2004-11-21 | Hon Hai Prec Ind Co Ltd | Connector assembly |

| US7437738B2 (en) | 2003-11-12 | 2008-10-14 | Intel Corporation | Method, system, and program for interfacing with a network adaptor supporting a plurality of devices |

| JP2005253033A (ja) * | 2004-02-06 | 2005-09-15 | Nippon Telegr & Teleph Corp <Ntt> | 網同期装置、クロック伝達方法およびクロック伝達パケット網 |

| US7069369B2 (en) | 2004-02-12 | 2006-06-27 | Super Talent Electronics, Inc. | Extended-Secure-Digital interface using a second protocol for faster transfers |

| US7646981B2 (en) | 2004-03-01 | 2010-01-12 | Adc Telecommunications, Inc. | WDM systems and methods |

| US7358826B2 (en) * | 2004-03-22 | 2008-04-15 | Mobius Microsystems, Inc. | Discrete clock generator and timing/frequency reference |

| JP2006003118A (ja) * | 2004-06-15 | 2006-01-05 | Nec Corp | 時計時刻同期方法 |

| US7412544B2 (en) | 2004-06-18 | 2008-08-12 | International Business Machines Corporation | Reconfigurable USB I/O device persona |

| US7460550B2 (en) | 2004-06-21 | 2008-12-02 | Industrial Technology Research Institute | Storage structure and method utilizing multiple protocol processor units |

| JP2006115362A (ja) | 2004-10-18 | 2006-04-27 | Hitachi Communication Technologies Ltd | パケット中継装置 |

| JP2006245894A (ja) | 2005-03-02 | 2006-09-14 | Nippon Telegr & Teleph Corp <Ntt> | 転送経路制御装置および転送経路制御プログラム |

| US20060203851A1 (en) * | 2005-03-14 | 2006-09-14 | Eidson John C | Applications of multiple time synchronization domains |

| US20070005867A1 (en) | 2005-06-30 | 2007-01-04 | Nimrod Diamant | Virtual peripheral device interface and protocol for use in peripheral device redirection communication |

| KR20070070299A (ko) * | 2005-07-06 | 2007-07-04 | 삼성전자주식회사 | 레지덴셜 이더넷 시스템에서의 시간 동기화 방법 |

| US20070249193A1 (en) | 2006-04-04 | 2007-10-25 | Applied Optical Systems, Inc. | Universal hybrid electrical/fiber optic insert cap and hybrid connector and methods |

| US7587536B2 (en) | 2006-07-28 | 2009-09-08 | Icron Technologies Corporation | Method and apparatus for distributing USB hub functions across a network |

| US7487284B2 (en) | 2006-07-28 | 2009-02-03 | Intel Corporation | Transaction flow and ordering for a packet processing engine, located within an input-output hub |

| JP4687621B2 (ja) | 2006-09-08 | 2011-05-25 | 日立電線株式会社 | スイッチ機能付通信モジュール及び通信装置 |

| US20080069150A1 (en) | 2006-09-19 | 2008-03-20 | Sig Harold Badt | Precision Time Protocol Emulation for Network Supportive of Circuit Emulation Services |

| US7675945B2 (en) | 2006-09-25 | 2010-03-09 | Futurewei Technologies, Inc. | Multi-component compatible data architecture |

| US8051217B2 (en) | 2007-01-12 | 2011-11-01 | Dell Products L.P. | System and method for providing PCIe over displayport |

| US20080175275A1 (en) * | 2007-01-22 | 2008-07-24 | Samsung Electronics Co., Ltd. | Time synchronization method between nodes in network and apparatus for implementing the same |

| EP2003477B1 (de) | 2007-06-15 | 2012-05-23 | Trumpf Laser Marking Systems AG | Elektro-optische Hybrid-Steckverbindung zur Übertragung von hohen optischen Leistungen und elektrischen Signalen |

| US8145920B2 (en) | 2007-09-17 | 2012-03-27 | Intel Corporation | Techniques for collaborative power management for heterogeneous networks |

| US8407367B2 (en) | 2007-12-26 | 2013-03-26 | Intel Corporation | Unified connector architecture |

| JP5186229B2 (ja) | 2008-02-04 | 2013-04-17 | 三星電子株式会社 | 無線通信システム、無線通信装置、及び無線通信方法 |

| US8700821B2 (en) | 2008-08-22 | 2014-04-15 | Intel Corporation | Unified multi-transport medium connector architecture |

| US8274998B2 (en) | 2008-10-02 | 2012-09-25 | Cortina Systems, Inc. | Systems and methods for packet based timing offset determination using timing adjustment information |

| US8468417B2 (en) | 2009-02-18 | 2013-06-18 | Micron Technology, Inc. | Data integrity in memory controllers and methods |

| US8295698B2 (en) * | 2009-08-27 | 2012-10-23 | Maged E Beshai | Time-coherent global network |

| TWI411277B (zh) * | 2009-12-23 | 2013-10-01 | Ind Tech Res Inst | 網路從節點與網路系統精確時間同步之方法 |

| US8644352B1 (en) * | 2010-03-12 | 2014-02-04 | Marvell International Ltd. | System and method for accurate time sampling in presence of output delay |

| US8583957B2 (en) * | 2010-07-27 | 2013-11-12 | National Instruments Corporation | Clock distribution in a distributed system with multiple clock domains over a switched fabric |

| US8953644B2 (en) * | 2011-12-27 | 2015-02-10 | Intel Corporation | Multi-protocol I/O interconnect time synchronization |

-

2011

- 2011-12-27 US US13/338,236 patent/US8953644B2/en active Active

-

2012

- 2012-11-30 JP JP2014550304A patent/JP5867765B2/ja active Active

- 2012-11-30 WO PCT/US2012/067438 patent/WO2013101393A1/en active Application Filing

-

2014

- 2014-12-30 US US14/585,596 patent/US9164535B2/en active Active

- 2014-12-30 US US14/585,609 patent/US9141132B2/en active Active

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11316628B2 (en) | 2019-10-31 | 2022-04-26 | Dell Products L.P. | Information handling system multi-stream cable throughput management |

| US11968052B2 (en) | 2019-10-31 | 2024-04-23 | Dell Products L.P. | Information handling system multi-stream cable throughput management |

Also Published As

| Publication number | Publication date |

|---|---|

| US9141132B2 (en) | 2015-09-22 |

| US8953644B2 (en) | 2015-02-10 |

| US9164535B2 (en) | 2015-10-20 |

| US20130163617A1 (en) | 2013-06-27 |

| WO2013101393A1 (en) | 2013-07-04 |

| US20150113186A1 (en) | 2015-04-23 |

| US20150121115A1 (en) | 2015-04-30 |

| JP2015505214A (ja) | 2015-02-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5867765B2 (ja) | マルチプロトコルのi/o相互接続の時間同期化 | |

| EP2798506B1 (en) | Multi-protocol i/o interconnect time synchronization | |

| US11044196B2 (en) | Multi-protocol I/O interconnect including a switching fabric | |

| US8856420B2 (en) | Multi-protocol I/O interconnect flow control | |

| US10884965B2 (en) | PCI express tunneling over a multi-protocol I/O interconnect | |

| US10372647B2 (en) | Exascale fabric time synchronization | |

| US8976799B1 (en) | Converged computer I/O system and bridging mechanism for peer-to-peer communication | |

| JP6221143B2 (ja) | I/o相互接続を介するマルチプロトコルのトンネリング | |

| US9252970B2 (en) | Multi-protocol I/O interconnect architecture | |

| US20230032204A1 (en) | Communication apparatus, communication method, and storage medium |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150108 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150612 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150818 |

|

| A524 | Written submission of copy of amendment under article 19 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20151116 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20151208 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20151222 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5867765 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |