JP5799322B2 - Game machine - Google Patents

Game machine Download PDFInfo

- Publication number

- JP5799322B2 JP5799322B2 JP2014069171A JP2014069171A JP5799322B2 JP 5799322 B2 JP5799322 B2 JP 5799322B2 JP 2014069171 A JP2014069171 A JP 2014069171A JP 2014069171 A JP2014069171 A JP 2014069171A JP 5799322 B2 JP5799322 B2 JP 5799322B2

- Authority

- JP

- Japan

- Prior art keywords

- control device

- master

- decoration

- decoration control

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Pinball Game Machines (AREA)

- Display Devices Of Pinball Game Machines (AREA)

Description

グループに分割された演出装置を制御する複数のグループ単位制御手段と、複数のグループ単位制御手段を制御するグループ統括制御手段とを備える遊技機に関し、特に、グループ統括制御手段からグループ単位制御手段へのデータ送信方法に関する。 The present invention relates to a gaming machine including a plurality of group unit control means for controlling a production device divided into groups and a group overall control means for controlling a plurality of group unit control means, in particular, from the group overall control means to the group unit control means. It relates to the data transmission method.

サブ中継基板と電飾基板との間の配線を簡素化することができる遊技機として、トップ電飾領域の中央部に配置されたトップLED中央基板をサブ中継基板とシリアル接続し、トップ電飾領域の右側部に配置されたトップLED右基板及びトップ電飾領域の左側部に配置されたトップLED左基板をトップLED中央基板から分離して配線により接続した構成の遊技機が知られている。これにより、サブ中継基板からトップ電飾領域への配線数を減らして配線を簡素化することができる(例えば、特許文献1参照)。 As a gaming machine that can simplify the wiring between the sub-relay board and the illumination board, the top LED central board arranged in the center of the top illumination area is serially connected to the sub-relay board, and the top illumination A gaming machine having a configuration in which a top LED right substrate disposed on the right side of the region and a top LED left substrate disposed on the left side of the top illumination region are separated from the top LED central substrate and connected by wiring. . Thereby, the number of wirings from the sub relay board to the top illumination area can be reduced to simplify the wiring (for example, see Patent Document 1).

また、信号線の数を削減することができると共に不正行為の発見を容易に行うことができる遊技機として、主基板と副基板との間での信号送信をI2Cバス方式により行い、主基板及び副基板にそれぞれ双方向バスバッファを設けたものがある。この双方向バスバッファは、I2Cバスを構成する二つの双方向シリアルライン(SDA、SCL)をそれぞれ二つの片方向シリアルラインに分岐させるためのものであり、主基板に設けられた双方向バスバッファと副基板に設けられた双方向バスバッファとの間を、それらによって分岐された片方向シリアルラインの信号伝送方向が互いに一致するようにして、四つのシリアル線で接続した構成としている(例えば、特許文献2参照)。 In addition, as a gaming machine that can reduce the number of signal lines and easily detect fraudulent activities, signal transmission between the main board and the sub board is performed by the I 2 C bus method. Some boards and sub-boards are each provided with a bidirectional bus buffer. This bidirectional bus buffer is for bifurcating the two bidirectional serial lines (SDA, SCL) constituting the I 2 C bus into two unidirectional serial lines, respectively. The bus buffer and the bidirectional bus buffer provided on the sub-board are connected by four serial lines so that the signal transmission directions of the one-way serial lines branched by them match each other ( For example, see Patent Document 2).

しかしながら、従来の遊技機では、異なるグループ単位制御手段同士を効率よく制御することができなかった。However, in conventional gaming machines, different group unit control means cannot be controlled efficiently.

本発明は、異なるグループ単位制御手段同士を効率よく制御することを目的とする。 An object of the present invention is to efficiently control different group unit control means .

本発明は、遊技の演出を行う複数の演出装置を制御する演出制御手段を備え、前記複数の演出装置を複数グループに分割し、該分割されたグループに属する演出装置を制御するためのグループ単位制御手段をグループ毎に設け、前記演出制御手段を、前記グループ単位制御手段の各々を統括的に制御するグループ統括制御手段として構成するとともに、前記グループ統括制御手段と前記グループ単位制御手段との間にデータ線とタイミング信号線を備えることによって、前記グループ統括制御手段から前記グループ単位制御手段にデータの伝達を可能とし、前記伝達されるデータには、前記グループ単位制御手段を指定するためのアドレスデータと、前記演出装置の態様に関する制御情報と、前記グループ単位制御手段が前記演出装置の態様を更新させるタイミングを規定する更新規定情報が含まれ、前記グループ統括制御手段は、前記グループ単位制御手段の一部と接続されて、該グループ単位制御手段との間のデータ線とタイミング信号線の信号レベルを制御する第1の信号レベル制御手段と、前記第1の信号レベル制御手段に接続されていないグループ単位制御手段と接続されて、該グループ単位制御手段との間のデータ線とタイミング信号線の信号レベルを制御する第2の信号レベル制御手段と、を含んで構成され、前記第1の信号レベル制御手段及び前記第2の信号レベル制御手段は、互いに異なる周期で接続されているグループ単位制御手段とデータの伝達を行い、前記グループ単位制御手段は、前記各グループ単位制御手段の間で共通となる共通アドレスと、各グループ単位制御手段同士で相違する個別アドレスと、が予め割り当てられ、前記グループ統括制御手段から伝達されたアドレスデータが自身の個別アドレス又は共通アドレスを示す場合に、伝達される制御情報の取り込みを行い、前記共通アドレスを示すアドレスデータは、複数のビットで構成されるとともに、全ての複数のビットがともに同一とならない値とし、前記グループ単位制御手段は、前記グループ統括制御手段から伝達される更新規定情報に規定されるタイミングで、前記演出装置の態様を前記制御情報に対応する態様に更新する。 The present invention includes an effect control means for controlling a plurality of effect devices that perform an effect of a game, and divides the plurality of effect devices into a plurality of groups, and controls the effect devices belonging to the divided groups. A control means is provided for each group, and the effect control means is configured as a group overall control means for overall control of each of the group unit control means, and between the group overall control means and the group unit control means. Data lines and timing signal lines are provided to enable transmission of data from the group overall control means to the group unit control means, and in the transmitted data, an address for designating the group unit control means Data, control information related to the aspect of the effect device, and the group unit control means is an aspect of the effect device Update definition information which defines the timing for updating is included, the group supervisory controlling means, the connected part of the group-unit control unit, data line and the timing signal line between the group-unit control unit a first signal level control means for controlling the signal level, is connected to the group-unit control unit that is not connected to the first signal level control means, the data line between the group-unit control unit And a second signal level control means for controlling the signal level of the timing signal line , and the first signal level control means and the second signal level control means are connected at different periods. and have line transmission of each group control unit and data are, the group-unit control unit, said common address as a common between each group unit control means, each group When the individual address which is different between the group control means is pre-assigned and the address data transmitted from the group overall control means indicates its own individual address or common address, the control information transmitted is taken in. The address data indicating the common address is composed of a plurality of bits, and all the plurality of bits are set to values that are not the same, and the group unit control means is an update rule transmitted from the group overall control means. The aspect of the effect device is updated to an aspect corresponding to the control information at a timing specified by the information .

本発明によれば、異なるグループ単位制御手段同士を効率よく制御することができる。 According to the present invention, different group unit control means can be efficiently controlled.

以下、本発明の実施の形態について、図面を参照しながら説明する。 Hereinafter, embodiments of the present invention will be described with reference to the drawings.

(実施の形態)

図1は、本発明の実施の形態の遊技機1の説明図である。

(Embodiment)

FIG. 1 is an explanatory diagram of a

遊技機1の前面枠(遊技枠)3は、本体枠(外枠)2にヒンジ4を介して、遊技機1の前面に開閉回動可能に組み付けられる。前面枠3の表側には、遊技盤10(図2参照)が収装される。また、前面枠3には、遊技盤10の前面を覆うカバーガラス(透明部材)を備えたガラス枠18が取り付けられている。

A front frame (game frame) 3 of the

ガラス枠18のカバーガラスの周囲には、装飾光が発光される装飾部材9a、9bが備えられている。装飾部材9a、9bの内部にはランプやLED等からなる装飾装置が備えられている。装飾装置を所定の発光態様によって発光させることによって、装飾部材9a、9bが所定の発光態様によって発光する。

Around the cover glass of the

ガラス枠18の左右には、音響(例えば、効果音)を発するスピーカ30が備えられている。また、ガラス枠18の上方には照明ユニット11が備えられている。

照明ユニット11には、第1可動式照明13及び第2可動式照明14が左右に配置されている。第1可動式照明13及び第2可動式照明14には、LEDなどの照明部材の他に、照明駆動第1モータ(MOT)13a及び照明駆動第2モータ(MOT)14aが備えられており、演出内容に応じて動作するように制御される。

In the

照明ユニット11の右下方には、遊技機1において異常が発生したことを報知するための異常報知LED29が備えられている。

An

前面枠3の下部の開閉パネル20には図示しない打球発射装置に遊技球を供給する上皿が、固定パネル22には下皿23及び打球発射装置の操作部24等が備えられる。下皿23には、下皿23に貯まった遊技球を排出するための下皿球抜き機構16が備えられる。前面枠3下部右側には、ガラス枠18を施錠するための鍵25が備えられている。

The open /

また、遊技者が操作部24を回動操作することによって、打球発射装置は、上皿21から供給される遊技球を発射する。

Further, when the player turns the

また、上皿21の上縁部には、遊技者からの操作入力を受け付けるための演出ボタン17が備えられている。遊技者が演出ボタン17を操作することによって、遊技盤10に設けられた表示装置53(図2参照)における特図変動表示ゲームの演出内容を選択して、表示装置53における特図変動表示ゲームに、遊技者の操作を介入させた演出を行うことができる。

In addition, the upper edge portion of the

特図変動表示ゲームは、発射された遊技球が遊技盤10に備わる始動口36(図2参照)に入賞した場合に開始される。特図変動表示ゲームでは、表示装置53において複数の識別情報が変動表示する。そして、変動表示していた識別情報が停止し、停止した識別情報の結果態様が特定の結果態様である場合に、遊技機1の状態が遊技者に有利な状態(特典が付与される状態)である特別遊技状態に遷移する。

The special figure variation display game is started when the launched game ball wins a start opening 36 (see FIG. 2) provided in the

上皿21の右上部には、遊技者が遊技球を借りる場合に操作する球貸ボタン26、及び、図示しないカードユニットからプリペイドカードを排出させるために操作される排出ボタン27が設けられている。さらに、これらの球貸ボタン26と排出ボタン27との間には、プリペイドカードの残高を表示する残高表示部28が設けられる。

In the upper right portion of the

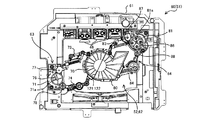

図2は、本発明の実施の形態の遊技盤10の正面図である。

FIG. 2 is a front view of the

図1に示す遊技機1は、内部の遊技領域10a内に遊技球を発射して(弾球して)遊技を行うもので、ガラス枠18のカバーガラスの奥側には、遊技領域10aを構成する遊技盤10が設置されている。

The

遊技盤10は、各種部材の取付ベースとなる平板状の遊技盤本体10b(木製又は合成樹脂製)を備え、該遊技盤本体10bの前面にガイドレール32で囲まれた遊技領域10aを有している。また、遊技盤本体10bの前面であってガイドレール32の外側には、前面構成部材33が取り付けられている。そして、このガイドレール32で囲まれた遊技領域10a内に発射装置から遊技球(打球;遊技媒体)を発射して遊技を行う。

The

遊技領域10aの略中央には、特図変動表示ゲームの表示領域となる窓部52を形成するセンターケース51が取り付けられている。センターケース51に形成された窓部52の後方には、複数の識別情報を変動表示する特図変動表示ゲームの演出を実行可能な演出表示装置としての表示装置53が配される。表示装置53は、例えば、液晶ディスプレイを備え、表示内容が変化可能な表示部53aがセンターケース51の窓部52を介して遊技盤10の前面側から視認可能となるように配されている。なお、表示装置53は、液晶ディスプレイを備えるものに限らず、EL、CRT等のディスプレイを備えるものであってもよい。

A

また、センターケース51の上部には、大当たりの可能性(信頼度)を報知する信頼度報知装置15が備えられる。信頼度報知装置15には、複数色のLED(例えば、赤、青、緑の3色のLED)が備えられており、信頼度に応じた色及び態様で発光するように制御される。

In addition, a

さらに、センターケース51の左部には、遊技球が流下可能な球導入路(ワープ流路)50が設けられ、遊技領域10aに向けて入口50aが開放した状態で開設されている。球導入路50は、センターケース51の内部に連通しており、入口50aから流入した遊技球は、センターケース51の裏側を通過して、ユニット側ステージ部49b上に排出される。さらに、ユニット側ステージ部49b上で転動した遊技球が当該ユニット側ステージ部49bの下方に配置されたベース側ステージ部49a上に流下できるように構成されている。

Further, a ball introduction path (warp flow path) 50 through which a game ball can flow down is provided on the left portion of the

センターケース51の周縁部には、複数の装飾具47が配置される。センターケース51の左下部には、装飾ランプ48が配置される、センターケース51の上部には、複数の装飾ピース46を上下動可能な状態で配置される。装飾具47、装飾ランプ48及び装飾ピース46は、後述する演出制御装置550からの命令に従って演出動作を行う。センターケース51の構成については、図3を参照しながらさらに詳細に説明する。

A plurality of

また、遊技領域10aのうちセンターケース51の下方には、遊技球を受入可能(入賞可能)な特図変動表示ゲームを始動させるための始動口36が配置される。さらに、センターケース51の側方(左側方)には、普図変動表示ゲームを始動させるための普図始動ゲート34が配置される。

Further, in the

さらに、遊技領域10aには、センターケース51の左下方及び右下方に、発光によって各種装飾表示を行うサイドランプ45が配置される。また、サイドランプ45には、一般入賞口44が備えられている。

Further, in the

さらに、始動口36の下方には大入賞口42が配置され、該大入賞口42の下方であって遊技領域10aの下縁部には、入賞せずに流下した遊技球を回収するアウト口43が開設される。大入賞口42は、上端側が手前側に倒れる方向に回動して開放可能になっているアタッカ形式の開閉扉42aを備える。特図変動表示ゲームの結果によって開閉扉42aを閉じた状態(遊技者にとって不利な状態)から開放状態(遊技者にとって有利な状態)に変換する。

Further, a big winning

また、センターケース51、始動口36やサイドランプ45等の取付部分を除いた遊技領域10a内には、この他、遊技領域10aには、打球方向変換部材としての風車(図示略)、及び多数の障害釘(図示略)などが配設されている。そして、センターケース51と、該センターケース51を挟んで普図始動ゲート34とは反対側に位置する前面構成部材33との間に縦長な円弧状の遊技球通路57が形成されている。

In addition, in the

さらに、遊技盤10には、特図変動表示ゲーム及び普図変動表示ゲームを実行する普図・特図表示器35が備えられている。普図・特図表示器35には、特図変動表示ゲームの未処理回数(特図始動記憶数)及び普図変動表示ゲームの未処理回数(普図始動記憶数)が表示される。普図・特図表示器35は、遊技状態を表す遊技状態表示LED(図示略)と併せて、セグメントLEDとして設けられている。

Further, the

普図始動ゲート34内には、該普図始動ゲート34を通過した遊技球を検出するためのゲートSW34a(図9参照)が設けられている。そして、遊技領域10a内に打ち込まれた遊技球が普図始動ゲート34内を通過すると、普図変動表示ゲームが開始される。

A

また、普図変動表示ゲームを開始できない状態で、普図始動ゲート34を遊技球が通過すると、普図始動記憶数が上限数未満であるならば、普図始動記憶数が1加算されて、当該普図変動表示ゲームが当りとなるか否かを示す乱数が普図始動記憶として一つ記憶される。

In addition, when the game ball passes through the general chart start

普図変動表示ゲームが開始できない状態とは、例えば、普図変動表示ゲームが既に行われ、その普図変動表示ゲームが終了していない状態や、普図変動表示ゲームに当選して始動口36が開状態に変換されている状態のことをいう。 The state in which the general map change display game cannot be started is, for example, a state in which the general map change display game has already been performed and the normal map change display game has not been completed, Is the state that has been converted to the open state.

なお、普図変動表示ゲームは、表示装置53の表示領域の一部で普図変動表示ゲームを表示するようにしてもよく、この場合は識別図柄として、例えば、数字、記号、キャラクタ図柄などを用い、この識別図柄を所定時間変動表示させた後、停止表示させることによって行うようにする。

It should be noted that the universal map change display game may display the universal map change display game in a part of the display area of the

普図変動表示ゲームの停止表示が特別の結果態様となった場合には、普図変動表示ゲームに当選したものとして、始動口36の開閉部材36aが所定時間(例えば、0.5秒間)開放される。これにより、始動口36に遊技球が入賞しやすくなり、特図変動表示ゲームの始動が容易となる。始動口36の開閉部材36aは、通常時は遊技球の直径程度の間隔をおいて閉じた状態(遊技者にとって不利な状態)を保持しているが、普図変動表示ゲームの結果が所定の停止表示態様となった場合(普図変動表示ゲームに当選した場合)には、ソレノイド(普電SOL36b、図9参照)によって、逆「ハ」の字状に開いて始動口36に遊技球が流入し易い状態(遊技者にとって有利な状態)に変化させられる。

When the stop display of the normal map change display game becomes a special result mode, the opening / closing

また、本発明の実施の形態の遊技機1は、特図変動表示ゲームの結果態様に基づいて、遊技状態として、表示装置53における特図変動表示ゲームの変動表示時間を短縮する時短動作状態(第2動作状態)を発生可能となっている。時短動作状態(第2動作状態)は、通常動作状態(第1動作状態)と比較して始動口36の開閉部材36aが開放状態となりやすい状態である。

In addition, the

時短動作状態においては、普図変動表示ゲームの実行時間が通常動作状態における実行時間よりも短くなるように制御され(例えば、10秒が1秒)、単位時間当りの始動口36の開放回数が実質的に多くなるように制御される。また、時短動作状態においては、普図変動表示ゲームに当選したことによって始動口36が開放される場合に、開放時間が通常動作状態の開放時間よりも長くなるように制御される(例えば、0.3秒が1.8秒)。また、時短動作状態においては、普図変動表示ゲームの1回の当選結果に対して、始動口36が1回ではなく、複数回(例えば、2回)開放される。さらに、時短動作状態においては普図変動表示ゲームの当選結果となる確率が通常動作状態よりも高くなるように制御される。すなわち、通常動作状態よりも始動口36の開放回数が増加され、始動口36に遊技球が入賞しやすくなり、特図変動表示ゲームの始動が容易となる。

In the short-time operation state, the execution time of the normal variation display game is controlled to be shorter than the execution time in the normal operation state (for example, 10 seconds is 1 second), and the number of opening of the

また、始動口36の内部には、始動口36を通過した遊技球を検出するための、始動口SW36d(図9参照)が備えられる。始動口SW36dによって遊技球を検出すると、補助遊技としての特図変動表示ゲームを開始する始動権利が発生する。このとき、特図変動表示ゲームを開始する始動権利は、所定の上限数(例えば4)の範囲内で特図始動記憶として記憶される。

In addition, a start port SW 36 d (see FIG. 9) for detecting a game ball that has passed through the

特図変動表示ゲームを直ちに開始できない状態、例えば、既に特図変動表示ゲームが行われ、その特図変動表示ゲームが終了していない状態や、特別遊技状態となっている場合に、始動口36に遊技球が入賞すると、特図始動記憶数が上限数未満(例えば、4個未満)ならば、特図始動記憶数が1加算され、始動口36に遊技球が入賞したタイミングで抽出された乱数が特図始動記憶として一つ記憶される。そして、特図変動表示ゲームが開始可能な状態となると、特図始動記憶に基づき特図変動表示ゲームが開始される。

When the special figure fluctuation display game cannot be started immediately, for example, when the special figure fluctuation display game has already been performed and the special figure fluctuation display game has not been completed, or when the special game state has been entered, the

補助遊技としての特図変動表示ゲームは、遊技盤10に設けられた普図・特図表示器35で実行され、複数の識別情報を変動表示したのち、所定の結果態様を停止表示することで行われる。また、表示装置53にて特図変動表示ゲームに対応して複数種類の識別情報(例えば、数字、記号、キャラクタ図柄など)が変動表示される。そして、特図変動表示ゲームの結果として、普図・特図表示器35の表示態様が特別結果態様となった場合には、大当たりとなって特別遊技状態(いわゆる、大当たり状態)となる。また、これに対応して表示装置53の表示態様も特別結果態様(例えば、「7,7,7」等のゾロ目数字の何れか)となる。なお、普図・特図表示器35ではなく、表示装置53のみで特図変動表示ゲームを実行するように構成してもよい。

The special figure variation display game as an auxiliary game is executed by the general figure / special

また、本発明の実施の形態の遊技機1は、特図変動表示ゲームの結果態様に基づき、遊技状態として確変状態(第2確率状態)を発生可能となっている。この確変状態(第2確率状態)は、特図変動表示ゲームでの当り結果となる確率が、通常確率状態(第1確率状態)に比べて高い状態である。なお、確変状態と上述した時短動作状態はそれぞれ独立して発生可能であり、両方を同時に発生することも可能であるし、一方のみを発生させることも可能である。

Further, the

図3は、本発明の実施の形態のセンターケース51の分解斜視図である。

FIG. 3 is an exploded perspective view of the

センターケース51は、遊技盤本体10b(遊技盤10)の表面側に前面構成部として配置される枠装飾部65と、遊技盤本体10bの裏面側に裏面構成部として配置される枠体基部60とを前後に重合して構成されている。枠装飾部65は、遊技盤本体10bの表面に止着される環状の装飾ベース66を備える。装飾ベース66の裏面側には、装飾ベース66と略同じ大きさで円形状に形成された装飾パネルユニット67を備え、枠装飾部65は、装飾ベース66と装飾パネルユニット67とを前後に重合して構成されている。

The

装飾ベース66の下部には、上面に遊技球を前後方向及び左右方向に転動可能なベース側ステージ部49aが配置され、該ベース側ステージ部49aと遊技球通路57との間には装飾ランプ48が配置されている(図2参照)。そして、ベース側ステージ部49aを挟んで装飾ランプ48とは反対側には、遊技球が流下可能な球導入路(ワープ流路)50が設けられ、球導入路50の入口50aを装飾ベース66の外方へ向けて開放した状態で開設し、球導入路50の出口50bを後述する装飾パネルユニット67の裏側へ連通している。

Under the

装飾パネルユニット67は、略円形状の透明樹脂板で形成されたカバーパネル部69を備え、該カバーパネル部69の前面側の周縁に複数の装飾具47を配置している。装飾パネルユニット67と枠装飾部65とを重合すると、装飾具47が装飾ベース66の内周縁に沿って配置されるように設定されている(図2参照)。また、カバーパネル部69の上部には、信頼度報知装置15が配置されている。

The

また、カバーパネル部69の裏面側の下部には、上面に遊技球を前後方向及び左右方向に転動可能なユニット側ステージ部49bが配置される。ユニット側ステージ部49bは、装飾ベース66のベース側ステージ部49aよりも上方に配置される。

In addition, a unit-

さらに、カバーパネル部69のうち球導入路50の出口50bに重合する箇所には球流入口68を開設し、該球流入口68を介して球導入路50とユニット側ステージ部49bとを連通している。したがって、遊技領域10aを流下する遊技球が球導入路50に流入すると、球導入路50がこの遊技球をユニット側ステージ部49b上に導入できるように構成されている。

Further, a

枠体基部60は、遊技盤10の裏面側に止着される額縁状の基部ケース61を前側が開放した状態で備え、該基部ケース61の内側(言い換えるとセンターケース51の内部)に、開口部62aが前面側に設けられた凹室62を形成している。

The

また、基部ケース61のうち凹室62の後方には矩形状の窓部52を前後方向へ貫通して開設し、基部ケース61の後方から表示装置53を装着して、表示装置53の表示部53aを窓部52及び凹室62を通してセンターケース51の前方へ臨ませている。

In addition, a

さらに、窓部52の上縁部の前側には、役物駆動ソレノイド(図示せず)によって上下動可能な複数の装飾ピース46が配置され、窓部52の左右両側の周縁には、表示部53aの前方へ移動して演出動作を行う可動演出装置58が備えられる。

Further, a plurality of

そして、枠体基部60の前方に枠装飾部65を重合すると、凹室62の開口部62a及び窓部52をカバーパネル部69で前方から被覆し、表示装置53の表示部53aを枠装飾部65の内側(カバーパネル部69が露出した箇所)からセンターケース51の前方へ臨ませるように構成されている。

Then, when the

図4及び図5は、本発明の実施の形態の可動演出装置58の構成を説明する図である。

4 and 5 are diagrams illustrating the configuration of the

可動演出装置58は、第1演出ユニット63と第2演出ユニット64とを互いに離間した位置に備えて構成され、第1演出ユニット63及び第2演出ユニット64が連動して演出動作が実行される。

The

図4は、可動演出装置58が動作する前の状態を示す図であり、図5は、可動演出装置58が動作し、第1演出ユニット63及び第2演出ユニット64が動作した結果、当接部(第1当接部121及び第2当接部122)にて当接している状態を示す図である。

FIG. 4 is a diagram illustrating a state before the

第1演出ユニット63は、センターケース51の左側、すなわち、基部ケース61の窓部52の周縁の左側に配置される。また、第2演出ユニット64は、センターケース51の右側に配置される。センターケース51の前方から見て第1演出ユニット63と第2演出ユニット64との間に凹室62及び窓部52を臨ませるように配置される。

The

第1演出ユニット63は、表示部53aの前方へ移動可能な第1演出部材70と、該第1演出部材70の駆動力を発生する第1演出駆動源としての役物駆動第1モータ(MOT)71と、役物駆動第1MOT71から発生した駆動力(回動力)を第1演出部材70へ伝達する第1演出伝達機構(第1主腕部材73及び第1副腕部材74)とを備える。

The

また、役物駆動第1MOT71の出力軸(第1出力軸)71aがセンターケース51の前後方向に延在し、第1出力軸71aには第1駆動ギア76を共回り可能に軸着している。

Further, an output shaft (first output shaft) 71a of the accessory driving

第1主腕部材73は、第1駆動ギア76と噛合される第1主腕ギア77が形成され、当該第1駆動ギア76の上方に軸着される。第1副腕部材74は、第1駆動ギア76と噛合される第1副腕ギア78が形成され、当該第1駆動ギア76の下方に軸着される。第1主腕部材73及び第1副腕部材74は、基部ケース61と軸着された端部の反対側の端部が互いに異なる位置で第1演出部材70に軸着し、第1演出部材70を支持している。

The first

第1演出ユニット63は、役物駆動第1MOT71を駆動して第1駆動ギア76をセンターケース51の正面から見て時計方向へ回動すると、役物駆動第1MOT71の駆動力(回動力)を第1駆動ギア76及び第1主腕ギア77を介して第1主腕部材73へ伝達し、この駆動力により第1主腕部材73がセンターケース51の正面から見て反時計方向へ回動する。また、役物駆動第1MOT71の駆動力を第1駆動ギア76及び第1副腕ギア78を介して第1副腕部材74へ伝達し、この駆動力により第1副腕部材74が第1主腕部材73と同じ反時計方向へ回動する。この結果、第1演出部材70が第1主腕部材73及び第1副腕部材74に支持された状態で上昇する。

When the

そして、役物駆動第1MOT71の駆動力により第1主腕部材73及び第1副腕部材74を上方へ延出して縦向き姿勢に設定すると、図4に示すように、第1演出部材70を表示部53aの前方から外れて位置させた第1演出停止状態となり、第1演出部材70が窓部52の側方に位置して、枠装飾部65の後方及び遊技盤本体10bの後方に隠れる(図2参照)。

Then, when the first

一方、第1演出停止状態から役物駆動第1MOT71を駆動して第1駆動ギア76をセンターケース51の正面から見て反時計方向へ回動すると、役物駆動第1MOT71の駆動力(回動力)を第1駆動ギア76及び第1主腕ギア77を介して第1主腕部材73へ伝達し、この駆動力により第1主腕部材73がセンターケース51の正面から見て時計方向へ回動する。

On the other hand, when the first

また、役物駆動第1MOT71の駆動力を第1駆動ギア76及び第1副腕ギア78を介して第1副腕部材74へ伝達し、この駆動力により第1副腕部材74が第1主腕部材73と同じ時計方向へ回動する。この結果、第1演出部材70が第1主腕部材73及び第1副腕部材74に支持された状態で下降する。

The driving force of the accessory driving

そして、役物駆動第1MOT71の駆動力により第1主腕部材73及び第1副腕部材74を表示部53aの前方へ延出して横向き姿勢に設定すると、図5に示すように、第1演出部材70を表示部53aの前方へ位置させた第1演出実行状態となり、第1演出部材70が表示部53aとカバーパネル部69との間の空間部のうち表示部53aの中央部分の前方に位置する。

Then, when the first

第2演出ユニット64は、表示部53aの前方へ移動可能な第2演出部材80と、該第2演出部材80の駆動力を発生する第2演出駆動源としての役物駆動第2モータ(MOT)81と、役物駆動第2MOT81から発生した駆動力(回動力)を第2演出部材80へ伝達する第2演出伝達機構(第2主腕部材83及び第2副腕部材84)とを備える。

The

また、役物駆動第2MOT81を出力軸(第2出力軸)81aがセンターケース51の前後方向に延在し、第2出力軸81aには第2駆動ギア86を共回り可能に軸着している。

Further, the accessory driving

第2主腕部材83は、第2駆動ギア86と噛合される第2主腕ギア87が形成され、当該第2駆動ギア86よりも第1演出ユニット63寄りの位置に軸着される。第2副腕部材84は、第2駆動ギア86と噛合される第2副腕ギア88が形成され、当該第2駆動ギア86の下方に軸着される。第2主腕部材83及び第2副腕部材84は、基部ケース61と軸着された端部の反対側の端部が互いに異なる位置で第2演出部材80に軸着し、第2演出部材80を支持している。

The second

第2演出ユニット64は、役物駆動第2MOT81を駆動して第2駆動ギア86をセンターケース51の正面から見て時計方向へ回動すると、役物駆動第2MOT81の駆動力(回動力)を第2駆動ギア86及び第2主腕ギア87を介して第2主腕部材83へ伝達し、この駆動力により第2主腕部材83がセンターケース51の正面から見て反時計方向へ回動する。また、役物駆動第2MOT81の駆動力を第2駆動ギア86及び第2副腕ギア88を介して第2副腕部材84へ伝達し、この駆動力により第2副腕部材84が第2主腕部材83と同じ反時計方向へ回動する。この結果、第2演出部材80が第2主腕部材83及び第2副腕部材84に支持された状態で下降する。

When the

そして、役物駆動第2MOT81の駆動力により第2主腕部材83及び第2副腕部材84を回動して第2演出部材80を下死点へ到達させ、引き続き第2主腕部材83及び第2副腕部材84を回動して斜め下方へ延出して縦向き姿勢に設定し、第2演出部材80を下死点から僅かに上昇させると、図4に示すように、第2演出部材80を表示部53aの前方から外れて位置させた第2演出停止状態となり、第2演出部材80が枠装飾部65の後方及び遊技盤本体10bの後方に隠れる(図2参照)。

Then, the second

一方、第2演出停止状態から役物駆動第2MOT81を駆動して第2駆動ギア86をセンターケース51の正面から見て反時計方向へ回動すると、役物駆動第2MOT81の駆動力(回動力)を第2駆動ギア86及び第2主腕ギア87を介して第2主腕部材83へ伝達し、この駆動力により第2主腕部材83がセンターケース51の正面から見て時計方向へ回動する。

On the other hand, when the accessory driving

また、役物駆動第2MOT81の駆動力を第2駆動ギア86及び第2副腕ギア88を介して第2副腕部材84へ伝達し、この駆動力により第2副腕部材84が第2主腕部材83と同じ時計方向へ回動する。この結果、第2演出部材80が第2主腕部材83及び第2副腕部材84に支持された状態で上昇する。

Further, the driving force of the accessory driving

そして、役物駆動第2MOT81の駆動力により第2主腕部材83及び第2副腕部材84を表示部53aの前方へ延出して横向き姿勢に設定すると、図5に示すように、第2演出部材80を表示部53aの前方へ位置させた第2演出実行状態となり、第2演出部材80が表示部53aとカバーパネル部69との間の空間部のうち表示部53aの中央部分の前方に位置する。

Then, when the second

図6は、本発明の実施の形態の第1演出部材70の分解斜視図である。

FIG. 6 is an exploded perspective view of the

第1演出部材70は、センターケース51の正面から見て略半円形状の部材であり、第1演出ユニット63側に円弧面を配置した姿勢に設定されている。

The

第1演出部材70には、基部となる第1演出ベース100が備えられる。第1演出ベース100は、透明な樹脂によって形成される。第1演出ベース100の上部には、第1主腕部材73を第1演出ベース100の前方から軸着する第1主腕軸着部101を形成し、第1演出ベース100の下部には、第1副腕部材74を第1演出ベース100の後方から軸着する第1副腕軸着部102を形成している。

The

第1演出ベース100の前面には、光を拡散しながら透過可能な第1光拡散シート103が重合される。さらに、第1光拡散シート103の前面に透明な第1保護パネル104を重合することによって、第1光拡散シート103が第1演出部材70から脱落することを阻止している。

A first

また、第1演出ベース100の後部を前方へ窪ませて第1基板収納空間部105を形成し、該第1基板収納空間部105にLEDなどの発光装置(装飾装置620、図17参照)が実装された第1発光基板106を収納する。さらに、この状態で第1基板収納空間部105を第1ベース蓋部107で閉塞し、第1発光基板106が第1演出部材70から脱落することを阻止している。

Further, the rear portion of the

そして、第1発光基板106の発光装置から光を発生すると、この光が第1演出ベース100、第1光拡散シート103、第1保護パネル104を透過してセンターケース51の前方へ照射されるように構成されている。

Then, when light is generated from the light emitting device of the first

さらに、第1当接部121の第1基板収納空間部105側には、後部が開放された第1演出磁石ホルダ124を窪ませて形成されている。第1演出磁石ホルダ124には、ボタン形状の永久磁石からなる第1磁石125を磁極が第2演出部材80側へ向いた姿勢で、第1磁石125が第1当接部121(第1演出磁石ホルダ124)から脱落しないように収納されている。

Further, a first

第1発光基板106には、装飾装置620の発光を制御するためのI2CI/Oエクスパンダ615(図17参照)が搭載され、演出制御装置550から出力された制御信号(電気信号)など送信するためのデータ線及びクロック線(信号線)が接続される。さらに、装飾装置620を発光させるために必要な電力を供給するための電源線などが接続される。これらの接続線は、ケーブル108としてまとめられて接続されている。

The first

図7は、本発明の実施の形態の第2演出部材80の分解斜視図である。

FIG. 7 is an exploded perspective view of the

第2演出部材80は、センターケース51の正面から見て上部に切欠部分がある略平行四辺形状となっている。第2演出停止状態においては第2演出部材80の上下両側面を第2演出ユニット64側から第1演出ユニット63側へ向けて下り傾斜させ(図4参照)、第2演出実行状態においては当該第2演出部材80の左右両側面を第2演出ユニット64側から第1演出ユニット63側へ向けて下り傾斜させる姿勢に設定されている(図5参照)。

The

第2演出部材80には、基部となる第2演出ベース110が備えられる。第2演出ベース110は、透明な樹脂によって形成される。第2演出ベース110の上部には、第2主腕部材83を第2演出ベース110の前方から軸着する第2主腕軸着部111を形成し、第2演出ベース110の下部には、第2副腕部材84を第2演出ベース110の後方から軸着する第2副腕軸着部112を形成している。

The

さらに、第2演出ベース110の前面には、光を拡散しながら透過可能な第2光拡散シート113を重合される。第2光拡散シート113の前面に透明な第2保護パネル114を重合することによって、第2光拡散シート113が第2演出部材80から脱落することを阻止している。

Further, a second

また、第2演出ベース110の後部を前方へ窪ませて第2基板収納空間部115を形成し、該第2基板収納空間部115にLEDなどの発光装置(装飾装置620)が実装された第2発光基板116を収納し、この状態で第2基板収納空間部115を第2ベース蓋部117で閉塞して、第2発光基板116が第2演出部材80から脱落することを阻止している。

In addition, the rear portion of the

そして、第2発光基板116の発光装置から光を発生すると、この光が第2演出ベース110、第2光拡散シート113、第2保護パネル114を透過してセンターケース51の前方へ照射されるように構成されている。

Then, when light is generated from the light emitting device of the second

さらに、第2当接部122の第2基板収納空間部115側には、後部が開放された第2演出磁石ホルダ128を窪ませて形成されている。第2演出磁石ホルダ128には、ボタン形状の永久磁石からなる第2磁石129が、第1当接部121及び第2当接部122を挟んで第1磁石125とは対称となる位置に収納されている。

Further, a second

第2発光基板116には、第1発光基板106と同様に、装飾装置620の発光を制御するためのI2CI/Oエクスパンダ615(図17参照)が搭載され、演出制御装置550から出力された制御信号などを送信するためのデータ線及びクロック線(信号線)が接続される。さらに、装飾装置620を発光させるために必要な電力を供給するための電源線などが接続される。これらの接続線は、ケーブル118としてまとめられて接続されている。

Similarly to the first

可動演出装置58は、第1演出部材70に第1当接部121を備えるとともに、第2演出部材80に第2当接部122を備える。そして、第1演出ユニット63を第1演出実行状態へ変換するとともに、第2演出ユニット64を第2演出実行状態へ変換すると、第1当接部121と第2当接部122とが当接し、第1演出部材70と第2演出部材80とで1つの装飾体を形成する。このとき、第1磁石125と第2磁石129との間で吸引力を発生するように第1磁石125及び第2磁石129が配置されている。さらに、この形成された装飾体を表示部53aの中央部の前方に位置させるように構成している。

The

図8は、本発明の実施の形態の遊技機1の配線を説明する図である。

FIG. 8 is a diagram illustrating wiring of the

図8では、遊技盤本体10bにセンターケース51が取り付けられ、表示装置53がセンターケース51に取り付けられる前の状態を示している。また、表示装置53の背面には、演出制御装置550が取り付けられている。演出制御装置550には、第1接続端子90及び第2接続端子92が備えられており、第1接続端子90及び第2接続端子92を介して制御対象となる演出装置に対し、制御信号の送信や電力の供給を行う。具体的には、第1接続端子90は後述する中継基板600にケーブル91を介して接続され、第2接続端子92は後述する簡易中継基板1600(図12参照)に接続される。

FIG. 8 shows a state before the

また、遊技盤本体10bの背面下部には、遊技制御装置500や各種制御基板を含む制御ユニット700が配置される。制御ユニット700に搭載される制御基板には、演出制御装置550から送信された制御信号を、装飾制御装置610(図11参照)に中継する中継基板600が含まれる。装飾制御装置610は、詳細については後述するが、遊技を演出するための発光装置(例えば、LED)や可動物(例えば、モータ)などの演出装置の制御を行う。また、中継基板600は、装飾制御装置610と同様に、発光装置や可動物を接続可能である。

In addition, a

中継基板600には発光装置を制御する装飾制御装置610が接続され、簡易中継基板1600には可動物を制御する装飾制御装置610が接続される。

A

中継基板600には、演出制御装置550にケーブル91を介して接続される上流コネクタ601が備えられる。ケーブル91の一方のコネクタ91aは、前述のように、演出制御装置550の第1接続端子90に接続される。ケーブル91の他方のコネクタ91bは、中継基板600の上流コネクタ601に接続される。さらに、遊技機1に備えられた各演出装置の制御を行う装飾制御装置610に接続するためのコネクタ602a〜602eを備える。

The

さらに、中継基板600には、接続されたケーブルの接続状態を示す空き端子モニタ603が備えられている。空き端子モニタ603の詳細については、図15にて説明する。

Further, the

また、図示は略するが、遊技制御装置500を構成するユニットが、中継基板600のコネクタ装着面を覆うようにして設けられている。そのため、遊技制御装置500は、中継基板600の各コネクタに必要なケーブルを装着した後に取り付けられる配置構成となっている。

Although illustration is omitted, units constituting the

遊技盤本体10bには、サイドランプ45を取り付けるための開口部45bが形成されている。サイドランプ45には、電力及び信号を送信するケーブル45aが接続され、開口部45bから遊技盤10の裏面側へ導入される。遊技盤10の裏面側へ導入されたケーブル45aは、中継基板600に接続され、例えば、コネクタ602dに接続される。

An

また、遊技盤10の下部には、図2に示したように、始動口36及び大入賞口42が配置される。始動口36が配置されている遊技盤10の裏側には、普図変動表示ゲームに当選した場合に開放される開閉部材36aを開閉するための普電ソレノイド(SOL)36bが配置される。また、特図変動表示ゲームに当選した場合に、大入賞口42を開閉するための大入賞口SOL42bも遊技盤10の裏側に配置されている。普電SOL36b及び大入賞口SOL42bには、制御信号の入力を受け付けるためのケーブル(図示略)が接続され、このケーブルは遊技制御装置500に接続されている。また、ケーブル42Cは、大入賞口42の内部に備えられる演出用のLEDを点灯させるための電力及び信号を伝達するケーブルとして中継基板600に接続され、例えば、コネクタ602fに接続される。

Further, as shown in FIG. 2, a starting

前述のように、遊技盤10の中央部には、センターケース51が取り付けられている。センターケース51の内部には、第1演出部材70及び第2演出部材80によって構成される可動演出装置58が備えられる。図8では、第1演出部材70及び第2演出部材80が当接面(121,122)で当接している状態となっている。

As described above, the

また、可動演出装置58の第1演出ユニット63及び第2演出ユニット64には、前述のように、第1演出部材70及び第2演出部材80を稼動させるためのモータ(役物駆動第1モータ71、役物駆動第2モータ81)(図12参照)が備えられている。

Further, as described above, the

また、複数の装飾ピース46を稼動させるためのソレノイド(役物駆動ソレノイド82)が備えられている。

In addition, a solenoid (operating article drive solenoid 82) for operating the plurality of

図8には図示しないが、前面枠3には簡易中継基板1600(図12参照)が配設される。また、前面枠3に配置されたスピーカ30、前面枠3の照明ユニット11の左右に配置された照明駆動モータ(13a、14a)(図12参照)、遊技盤10に設けられた役物駆動モータ(71、81)、役物駆動ソレノイド82(図12参照)などを制御するための信号を送信するケーブル3bが簡易中継基板1600に接続されている。このケーブル3bのコネクタは、演出制御装置550の第2接続端子92に接続される。

Although not shown in FIG. 8, a simple relay board 1600 (see FIG. 12) is disposed on the

そして、遊技盤10に設けられたこれらのモータ及びソレノイドを制御するための信号、並びに、遊技盤10に設けられたこれらのモータ及びソレノイドを駆動させるための電力を供給するためのケーブル652が可動演出装置58及び装飾ピース46に接続されている。ケーブル652は、センターケース51の開口部51cから遊技盤10の裏面側に延びており、簡易中継基板1600に接続されている。

A

また、可動演出装置58には、これらのモータの動作状態を検知するための役物駆動モータ位置検出センサ560a(図11参照)が備えられており、センシング結果を受信するためのケーブル651が接続されている。ケーブル651は、センターケース51の開口部51bから遊技盤10の裏面側に延びており、中継基板600に接続される。例えば、ケーブル651はコネクタ602eに接続される。

Further, the

さらに、演出制御装置550から出力された制御信号を、センターケース51の内部に配置されたLEDなどの演出装置を制御するための装飾制御装置610(図11参照)へ伝達するケーブル653が接続される。ケーブル653は、センターケース51に設けられた開口部51aから遊技盤10の裏面側の中継基板600に接続され、例えば、コネクタ602aに接続される。

Furthermore, a cable 653 is connected to transmit the control signal output from the

図9は、本発明の実施の形態の遊技機1の構成を示すブロック図である。

FIG. 9 is a block diagram showing a configuration of the

遊技機1は、遊技を統括的に制御する遊技制御装置500、各種演出を行うために表示装置53及びスピーカ30等を制御する演出制御装置550、遊技球を払い出すために図示しない払出モータを制御する払出制御装置580を備える。

The

まず、遊技制御装置500の構成について説明する。なお、演出制御装置550については、図10にて説明する。

First, the configuration of the

遊技制御装置500は、遊技用マイコン501、入力I/F(Interface)505、出力I/F(Interface)506、及び外部通信端子507を備える。

The

遊技用マイコン501は、CPU502、ROM(Read Only Memory)503及びRAM(Random Access Memory)504を備える。

The

CPU502は、遊技を統括的に制御する主制御装置であって、遊技制御を司る。ROM503は、遊技制御のための不変の情報(プログラム、データ等)を記憶している。RAM504は、遊技制御時にワークエリアとして利用される。

The CPU 502 is a main control device that controls the game in an integrated manner, and controls the game. The

外部通信端子507は、遊技制御装置500の設定情報等を検査する検査装置等の外部機器に遊技制御装置500を接続する。

The

CPU502は、入力I/F505を介して各種入力装置(始動口SW36d、一般入賞口SW44a〜44n、ゲートSW34a、カウントSW42d、ガラス枠開放SW18a、前面枠開放SW3a、球切れSW54、振動センサ55、及び磁気センサ56)からの検出信号を受けて、大当り抽選等、種々の処理を行う。

The CPU 502 receives various input devices (start opening SW36d, general winning openings SW44a to 44n, gate SW34a, count SW42d, glass frame opening SW18a, front frame opening SW3a, ball break SW54,

始動口SW36dは、始動口36に遊技球が入賞したことを検出するスイッチである。一般入賞口SW44a〜44nは、一般入賞口44に遊技球が入賞したことを検出するスイッチである。

The start port SW36d is a switch that detects that a game ball has won the

ゲートSW34aは、普図始動ゲート34を遊技球が通過したことを検出するスイッチである。カウントSW42dは、大入賞口42に遊技球が入賞したことを検出するスイッチである。

The

ガラス枠開放SW18aは、ガラス枠18が開放されたことを検出するスイッチである。前面枠開放SW3aは、前面枠3が開放されたことを検出するスイッチである。

The glass

球切れSW54は、遊技機1の内部に貯留され、払い出しに用いられる遊技球の数が所定数以下になったことを検出するスイッチである。

The ball cut

振動センサ55は、遊技機1に与えられた振動を検出するセンサであり、遊技機1を振動させるなどの不正行為を検出する。磁気センサ56は、始動口36、一般入賞口44、大入賞口42、及び普図始動ゲート34付近に設けられ、磁力を検出するセンサである。磁気センサ56は、各入賞口付近に磁石を近づけて、遊技領域10aに発射された遊技球を各入賞口に導く不正を検出する。

The

また、CPU502は、出力I/F506を介して、普図・特図表示器35、普電SOL36b、大入賞口SOL42b、払出制御装置580、及び演出制御装置550に指令信号を送信して、遊技を統括的に制御する。

In addition, the CPU 502 transmits a command signal to the ordinary / special-

普図・特図表示器35には、前述のように、特図変動表示ゲーム及び普図変動表示ゲームが実行される。さらに、特図変動表示ゲームの未処理回数(特図始動記憶数)及び普図変動表示ゲームの未処理回数(普図始動記憶数)が表示される。普図変動表示ゲームが当りとなるか否かを示す乱数を含む普図始動記憶、及び特図変動表示ゲームが当りとなるか否かを示す乱数を含む特図始動記憶が記憶されている。

As described above, the special figure change display game and the universal figure change display game are executed on the special figure / special

普電SOL36bは、普図変動表示ゲームの停止表示が特別の結果態様となった場合に、開閉部材36aを開放することによって、始動口36に遊技球が入賞しやすい状態にする。

The general

大入賞口SOL42bは、特図変動表示ゲームの結果が特別の結果態様となって、特別遊技状態(大当たり状態)となった場合に、大入賞口42の開閉扉42aを開放して、遊技球が入賞しやすい状態に変換する。

The special winning opening SOL42b opens the open /

遊技制御装置500は、図示しない外部情報端子から図示しない情報収集端末装置を介して、遊技機データを図示しない遊技場管理装置に出力する。遊技場管理装置は、遊技場に設置された遊技機1の遊技データを収集管理する計算機である。

The

払出制御装置580は、遊技球が一般入賞口44又は大入賞口42に入賞した場合に、入賞した入賞口に対応する数の遊技球の払出指令を遊技制御装置500から受信する。また、球貸ボタン26が操作された場合にも所定数の遊技球の払い出しを行う払出指令を遊技制御装置500から受信する。払出制御装置580は、受信した払出指令に基づいて、図示しない払出モータを制御し、払出指令に指定された数の遊技球を払い出す。

The

遊技制御装置500は、変動開始コマンド、客待ちデモコマンド、ファンファーレコマンド、確率情報コマンド、及びエラー指定コマンド等を、遊技の状況を示す遊技データとして、出力I/F506を介して、演出制御装置550へ送信する。

The

図10は、本発明の実施の形態の演出制御装置550の構成を示すブロック図である。

FIG. 10 is a block diagram showing a configuration of the

演出制御装置550は、遊技制御装置500から入力される遊技データに基づいて、演出内容を決定し、表示装置53を制御するとともに、遊技盤10及び前面枠3に備えられた各種演出装置を制御する。演出装置には、LEDなどの発光装置やモータ又はソレノイドなどの可動物が含まれる。

The

演出制御装置550は、CPU551、制御ROM552、RAM553、画像ROM554、音ROM555、VDP556、音LSI557、入力I/F558b、出力I/F558a、電源投入検出回路559、第1マスタIC570a、第2マスタIC570b、NORゲート回路561及び監視タイマ回路562を備える。さらに、演出制御装置550は、中継基板600に接続される第1接続端子90と簡易中継基板1600に接続される第2接続端子92を備える。

The

中継基板600は、発光装置を制御する装飾制御装置610に接続されるものであり、簡易中継基板1600は、可動物を制御する装飾制御装置610に接続されるものである。

The

なお、第1マスタIC570a及び第2マスタIC570bに共通の機能については、単に「マスタIC」として説明する。

The functions common to the

CPU551は、遊技制御装置500から送信された指令信号が通信割込としての割込信号(INT)として入力され、入力された指令信号に基づいて、各種演出を制御する。また、CPU551には、第1マスタIC570a及び第2マスタIC570bからマスタ割込としての割込信号(INT)が入力されるとともに、VDP556からも画像更新割込としての割込信号(INT)が入力される。

The

さらに、CPU551は、監視タイマ回路562からもタイムアウト割込としての割込信号(INT)が入力される。監視タイマ回路562は、複数種類の監視タイマが内蔵されており、CPU551によって設定された監視タイマ値がタイムアップすると、CPU551に割込信号を出力する。CPU551は、割込信号の入力を受け付けると、実行中の処理を中断し、入力された割込信号に対応する処理を実行する。

Further, the

制御ROM552には、演出制御のための不変の情報(プログラム、データ等)が格納されている。RAM553は、演出制御時にワークエリアとして利用される。

The

画像ROM554は、VDP556に接続され、表示装置53に表示される画像データを格納する。VDP556は、表示装置53への画像出力を制御するプロセッサである。

The image ROM 554 is connected to the

また、VDP556は、表示装置53に表示される画像を更新する周期(33ms周期)と同期する同期信号を発生させる同期信号発生手段を備える。同期信号発生手段は、同期信号を発生させるごとに、発生させた同期信号をCPU551に割込信号として入力する。

In addition, the

音ROM555は、音LSI557に接続され、前面枠3に備えられたスピーカ30から出力される音データを格納する。音LSI557は、スピーカ30からの音声出力を制御する回路である。

The

入力I/F558bは、フィルタ565a及び565bを介して外部から入力された情報を受け付けるインタフェースである。具体的には、前面枠3に備えられた演出ボタン17が操作されたことを示す信号の入力を受け付けたり、遊技盤10に備えられた役物駆動モータ位置検出センサ560a(図11参照)によって検出された各モータの位置情報などの入力を受け付けたりする。

The input I /

電源投入検出回路559は、演出制御装置550に電源が投入された場合に、第1マスタIC570a及び第2マスタIC570bのレジスタをデフォルト状態(すべて0)に初期化するリセット信号(初期化信号)を発生させ、NORゲート回路561に出力する。

The power-on

また、CPU551は、所定の条件が成立した場合に、バス563を介してリセット信号を出力I/F558aに出力する。そして、出力I/F558aは、入力されたリセット信号をNORゲート回路561に出力し、さらに、NORゲート回路561から、第1マスタIC570a及び第2マスタIC570bに当該リセット信号を出力する。所定の条件とは、例えば、すべての装飾制御装置610において、エラーフラグが「ON」になった場合などである(図32及び図33参照)。

Further, the

なお、電源投入検出回路559からNORゲート回路561に入力されるリセット信号と、CPU551から出力I/F558aを介してNORゲート回路561に入力されるリセット信号は、いずれの場合にもLOWレベルの状態のときにリセットを指令する信号として機能する。そのため、電源投入検出回路559及びCPU551の少なくとも一方からNORゲート回路561にリセット信号が出力されていれば、NORゲート回路561を介してリセット信号が第1マスタIC570a及び第2マスタIC570bに入力される。

Note that the reset signal input from the power-on

監視タイマ回路562は、演出制御装置550にて時間を計測するための回路であり、設定された時間が経過するとCPU551に割込信号を入力する。

The

図11は、本発明の実施の形態の演出制御装置550に備えられた第1マスタIC570aと演出装置の構成を示すブロック図である。

FIG. 11 is a block diagram showing the configuration of the

遊技盤10は、第1マスタIC570aに接続される中継基板600、当該中継基板600に接続される補助遊技装置ユニット12を備える。

The

中継基板600は、装飾制御装置610が遊技盤10及び前面枠3に設けられているかに拘らず、発光装置を制御する装飾制御装置610に接続される。

The

中継基板600は、第1マスタIC570aから送信された電気信号を、遊技盤10及び前面枠3に備えられた発光装置を制御する装飾制御装置610に送信(中継)する。また、中継基板600には、装飾制御装置610と同様に、演出装置を制御する機能を有し、当該中継基板600に直接接続された装飾装置基板625を制御する。

The

ここで、発光装置となる装飾装置620は、装飾制御装置610に備えられるI2CI/Oエクスパンダ615(図17参照)によって制御され、電流を流すことによって光が点滅して演出を行うものであり、例えばLEDなどである。装飾装置基板625は、サイドランプ45(図8参照)に設けられる基板であり、サイドランプ45の発光装置(LED)が搭載されている。このサイドランプ45の発光装置は、中継基板600に備えられるI2CI/Oエクスパンダ615によって、直接制御される。

Here, the

補助遊技装置ユニット12には、LEDなどの発光装置である装飾装置620、可動物である役物駆動第1モータ(MOT)71、役物駆動第2MOT81、及び役物駆動ソレノイド82が含まれるが、第1マスタIC560は、発光装置である装飾装置620を制御する装飾制御装置610に接続される。

The auxiliary

なお、補助遊技装置ユニット12に含まれる役物駆動第1MOT71、及び役物駆動第2MOT81を制御する装飾制御装置610は、簡易中継基板1600を介して、第2マスタIC570bに接続される(図12参照)。

Note that the

役物駆動第1MOT71及び役物駆動第2MOT81は、電流が流れると回転動作することによって演出動作を行う駆動装置である。

The first

本発明の実施の形態では、役物駆動第1MOT71及び役物駆動第2MOT81は、可動演出装置58に含まれ、具体的には、役物駆動第1MOT71は第1演出ユニット63、役物駆動第2MOT81は第2演出ユニット64に含まれている。

In the embodiment of the present invention, the accessory driving

演出制御装置550は、役物駆動第1MOT71及び役物駆動第2MOT81を制御することによって、第1演出ユニット63及び第2演出ユニット64が連動した演出動作を実行させる。

The

第1マスタIC570aは、制御対象となる装飾装置620を制御する装飾制御装置610に個別に割り当てられたアドレスを指定して、指定した個別アドレスの装飾制御装置610に装飾装置620の制御内容を出力する。なお、装飾制御装置610の個別アドレスは、正確には、装飾制御装置610に含まれるI2CI/Oエクスパンダ615(図17参照)の個別アドレスである。

The

第1マスタIC570aは、接続線SDA、接続線SCL、接続線GND、接続線Vcc、接続線Vled、及び接続線Vseの6種類の接続線を介して、中継基板(装飾制御装置)600に接続される。これらの接続線は、第1マスタIC570aと中継基板600とを接続するケーブル91(図8参照)により構成される。

The

接続線SDAは、演出制御装置550と装飾制御装置610との間でデータ信号を授受するための接続線であり、本発明の実施の形態におけるデータ線(データ信号線)として機能する。接続線SCLは、接続線SDAでのデータ通信に用いられるクロック信号を入出力するための接続線であり、本発明の実施の形態におけるタイミング信号線として機能する。接続線GNDは、接続線Vcc、接続線Vled、及び接続線Vseで供給される電源のグランドである。

Connection line SDA is a connection line for exchanging data signals between

接続線Vccは、中継基板600及び装飾制御装置610にロジック用の電源を供給するための接続線である。接続線Vledは、LED(装飾装置620)を発光させるための電源を供給するための接続線である。接続線Vseは、各種センサ(演出装置に含まれるモータの状態を検出する状態検出センサであって、具体的には、役物駆動モータ位置検出センサ560aが相当する)に電源を供給するための接続線である。

The connection line Vcc is a connection line for supplying logic power to the

中継基板600と補助遊技装置ユニット12との間は、演出制御装置550と中継基板600との間を接続する7種類の接続線が接続される。本発明の実施の形態では、役物駆動モータ位置検出センサ560aは、中継基板600によって直接制御されるため、前述した6種類の接続線のうち、接続線Vse以外の5種類の接続線が、補助遊技装置ユニット12の最上流に配置された装飾制御装置610に接続される。具体的には、中継基板600と装飾制御装置610との間は、接続線Vcc、接続線Vled、接続線SDA、接続線SCL及び接続線GNDが接続される。

Between the

なお、図8に示した配線(ケーブル)と各接続線を対応させると、演出制御装置550から中継基板600に引き渡される各種接続線(接続線Vcc、接続線Vled、接続線SDA、接続線SCL、接続線Vse、及び接続線GND)(図11参照)は、ケーブル91に含まれている。

When the wiring (cable) shown in FIG. 8 is associated with each connection line, various connection lines (connection line Vcc, connection line Vled, connection line SDA, connection line SCL) delivered from the

また、演出制御装置550から中継基板600に引き渡される各種接続線は、中継基板600からさらに分岐して別の基板に引き渡され、中継基板600から分岐する接続線Vcc、接続線Vled、接続線SDA、及び接続線SCLはケーブル653に、接続線Vseはケーブル651に含まれている。また、中継基板600から分岐する接続線GNDが、ケーブル651、653の全てに含まれている。

Further, the various connection lines delivered from the

演出制御装置550から簡易中継基板1600に引き渡される各種接続線(接続線Vcc、接続線Vms、接続線SDA、接続線SCL、接続線Vse、及び接続線GND)は、ケーブル3bに含まれている。

Various connection lines (connection line Vcc, connection line Vms, connection line SDA, connection line SCL, connection line Vse, and connection line GND) delivered from the

また、演出制御装置550から簡易中継基板1600に引き渡される各種接続線は、簡易中継基板1600からさらに分岐して別の基板に引き渡され、簡易中継基板1600から分岐する接続線Vcc、接続線Vms、接続線SDA、接続線Vse、接続線GND、及び接続線SCLはケーブル652に含まれている。

Further, the various connection lines delivered from the

第1マスタIC570aと装飾制御装置610とは、接続線SDA及び接続SCLによって2ライン双方向通信を行う。第1マスタIC570aは、CPU551からの指令に基づいて、装飾制御装置610との間に接続された接続線SDA及び接続線SCLの各信号レベルを制御する(第1の)信号レベル制御手段として機能する。

The

第1マスタIC570aは、中継基板600及び装飾制御装置610にデータを送信する場合には、まず、接続線SCLの信号レベルをHIGHに維持したまま、接続線SDAの信号レベルをHIGHからLOWに変化させることにより、装飾制御装置610へのデータ出力を開始するためのスタート条件を成立させる(装飾制御装置610に対してスタートコンディションを発行(出力)する)。

When transmitting data to the

この後、第1マスタIC570aは、接続線SCLの信号レベルをLOWに変更し、接続線SCLの信号レベルがLOWである間に接続線SDAの信号レベルを送信データの最初のビットのレベルに設定し、所定時間後に接続線SCLの信号レベルをLOWからHIGHに変化させる。接続線SCLの信号レベルがHIGHに変化すると、装飾制御装置610は接続線SDAの信号レベルを取得し、送信データの最初のビットとして認識する。次いで、第1マスタIC570aは、接続線SCLの信号レベルをHIGHからLOWに戻す。

Thereafter, the

この手順を1回実行すると、第1マスタIC570aから装飾制御装置610へ1ビットのデータが送信され、最終的にはこの手順が8回繰り返されることで、送信データの8ビットすべてが第1マスタIC570aから装飾制御装置610へ送信される(1バイト分のデータが送信される)。

When this procedure is executed once, 1-bit data is transmitted from the

そして、第1マスタIC570aは、最後の8ビット目のデータ送信が終了すると、接続線SCLの信号レベルをHIGHからLOWに戻した際に、接続線SDAを解放して装飾制御装置610からの返答信号を受信することを待機する受信待機状態にする。

Then, when the data transmission of the last 8 bits is completed, the

受信待機状態になると、装飾制御装置610は、接続線SDAを介して1ビットの返答信号(後述するACK又はNACK)を第1マスタIC570aに返す。次いで、第1マスタIC570aは、接続線SCLの信号レベルをLOWからHIGHに変化させて返答信号のレベルを取り込み、所定時間後に接続線SCLの信号レベルをHIGHからLOWに変化させると、装飾制御装置610は接続線SDAを解放する。

In the reception standby state, the

第1マスタIC570aは、このような1バイト分のデータ送信と1ビット分の返答信号の受信とを交互に繰り返し、装飾制御装置610へ出力すべきデータがすべて出力されるまで継続する。第1マスタIC570aは、出力すべきデータの出力が終了した場合には、接続線SCLの信号レベルをHIGHに維持したまま、接続線SDAの信号レベルをLOWからHIGHに変更させることにより、装飾制御装置610へのデータ出力を終了するためのストップ条件を成立させる(装飾制御装置610に対してストップコンディションを発行する)。

The

入力用バッファ571は、装飾制御装置610から接続線SDAを介して入力されたデータが一時的に記憶される記憶装置である。

The

具体的には、第1マスタIC570aが入力モードに設定された場合において、装飾制御装置610から第1マスタIC570aに送信されたデータが、フィルタ575aによりノイズが除去されて入力用バッファ571に一時的に記憶される。

Specifically, when the

出力用バッファ572は、装飾制御装置610に接続線SDAを介して出力するデータが一時的に記憶される。

The

リセットレジスタ(REG)573は、バス563に接続され、演出制御装置550のCPU551からの指令を受け付けてリセット信号をコントローラ574に出力する。コントローラ574は、第1マスタIC570aを統括的に制御し、各種処理を実行する。

The reset register (REG) 573 is connected to the

フィルタ575aは、接続線SDAから入力されたデータのノイズを除去する。ドライバ576aは、接続線SDAからデータを出力する場合に、トランジスタ578aが動作可能な電圧をトランジスタ578aに印加する。

The

接続線SDAは、プルアップ抵抗Rによって所定の電圧が印加され(図21参照)、フィルタ575a及びトランジスタ578aに接続されている。

A predetermined voltage is applied to the connection line SDA by a pull-up resistor R (see FIG. 21), and the connection line SDA is connected to the

トランジスタ578aは、電力消費を抑えるために電界効果トランジスタ(FET)が用いられている。トランジスタ578aのゲートはドライバ576aに接続され、ドレインはプルアップ抵抗Rにより所定の電圧が印加された接続線SDAに接続され、ソースは接地されている。

As the

トランジスタ578aのゲートに印加される電圧がトランジスタ578aを動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れないので、接続線SDAに印加された電圧は降下せず、その結果、接続線SDAはHIGHレベルとなる。一方、トランジスタ578aのゲートに印加される電圧がトランジスタ578aを動作させる所定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流が流れることによって、接続線SDAの電圧が低下し、その結果、接続線SDAはLOWレベルとなる。

If the voltage applied to the gate of the

なお、トランジスタ578aは、10ミリアンペア程度の電流をドレインからソースへ流しても破損しない仕様のものを用いている。このため、接続線SDAには、通常のI2Cバス使用で用いられる電流値よりもはるかに大きい10ミリアンペア程度の電流を流すことが可能であり、演出制御装置550と装飾制御装置610との間のデータ送信が、ノイズによる障害に耐えうる構成となっている。

Note that the

ドライバ576aは、データを接続線SDAから出力する場合に、トランジスタ578aにドレインとソースとの間に電流を流すためにトランジスタ578aのゲートにトランジスタ578aが動作可能な値の電圧を印加する。そして、ドライバ576aは、接続線SDAの電圧を、HIGHレベル又はLOWレベルに設定することによって、データを接続線SDAから出力する。

When the

また、フィルタ575bは、接続線SCLから入力されたデータのノイズを除去する。ドライバ576bは、接続線SCLからデータを出力する場合に、トランジスタ578bが動作可能な電圧をトランジスタ578bに印加する。

Further, the

接続線SCLは、プルアップ抵抗Rによって所定の電圧が印加され(図21参照)、フィルタ575b及びトランジスタ578bに接続されている。

A predetermined voltage is applied to the connection line SCL by the pull-up resistor R (see FIG. 21), and the connection line SCL is connected to the

トランジスタ578bは、電力消費を抑えるために電界効果トランジスタ(FET)が用いられている。トランジスタ578bのゲートはドライバ576bに接続され、ドレインはプルアップ抵抗Rにより所定の電圧が印加された接続線SCLに接続され、ソースは接地されている。

A field effect transistor (FET) is used as the

トランジスタ578bのゲートに印加される電圧がトランジスタ578bを動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れないので、接続線SCLに印加された電圧は降下せず、その結果、接続線SCLはHIGHレベルとなる。一方、トランジスタ578bのゲートに印加される電圧がトランジスタ578bを動作させる所定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流が流れることによって、接続線SCLの電圧が低下し、その結果、接続線SCLはLOWレベルとなる。

If the voltage applied to the gate of the

なお、トランジスタ578bは、10ミリアンペア程度の電流をドレインからソースへ流しても破損しない仕様のものを用いている。そのため、接続線SCLには、通常のI2Cバス使用で用いられる電流値よりもはるかに大きい10ミリアンペア程度の電流を流すことが可能であり、演出制御装置550と装飾制御装置610との間のデータ送信が、ノイズによる障害に耐えうる構成となっている。

Note that the

ドライバ576bは、クロック信号を接続線SCLから出力する場合に、トランジスタ578bにドレインとソースとの間に電流を流すためにトランジスタ578bのゲートにトランジスタ578bが動作可能な値の電圧を印加する。そして、ドライバ576bは、接続線SCLの電圧を、HIGHレベルとLOWレベルとに繰り返し変化させることによって、クロック信号を接続線SCLから出力する。

When the

電源投入リセット回路577は、第1マスタIC570aに電源が投入されて、電源投入リセット回路577内の電圧が所定値に達した場合に、入力用バッファ571及び出力用バッファ572などの記憶領域をデフォルト状態にするためのリセット信号をコントローラ574に出力する。なお、電源投入リセット回路577については、第1マスタIC570aの外部に設け、後述する第2マスタIC570bの共通としてもよい。

The power-on

コマンドレジスタ(REG)581は、演出制御装置550のCPU551からコマンドを受け付けるためのレジスタである。本発明の実施の形態では、コマンドレジスタ581には、STA、STO、SI、及びMODEの各ビットが予め割り当てられており、CPU551によって、各ビット毎個別に“0”又は“1”が設定可能となっている。

The command register (REG) 581 is a register for receiving a command from the

STAは、第1マスタIC570aが制御対象の装飾制御装置610に対し、スタート条件(スタートコンディション)の出力を指示するためのビットである。STAに“1”が設定されると、第1マスタIC570aは、制御対象の装飾制御装置610に対し、スタートコンディションを発行(出力)し、スタート条件を成立させる。

The STA is a bit for the

STOは、第1マスタIC570aが制御対象の装飾制御装置610に対し、ストップ条件(ストップコンディション)の出力を指示するためのビットである。STOに“1”が設定されると、第1マスタIC570aは、制御対象の装飾制御装置610に対し、ストップコンディションを発行(出力)し、ストップ条件を成立させる。

The STO is a bit for the

SIは、第1マスタIC570aから、演出制御装置550において割込みを発生させるときに設定されるビットである。第1マスタIC570aからCPU551に割込みを発生させるときには、コントローラ574によってSIに“1”が設定され、割込信号(INT)がCPU551に入力される。その後、SIに“1”が設定されている間は、第1マスタIC570aは処理を中断しているが、CPU551によってSIに“0”が設定されると、第1マスタIC570aは、割込を中断して処理を再開する。

SI is a bit that is set when an interrupt is generated in the

MODEは、データを送信するモードを指定するビットであり、“1”が設定されている場合には「バッファモード」、“0”が設定されている場合には「バイトモード」が指定される。バッファモードは、最大68バイトのデータの送信が可能である。また、バイトモードは、1バイトのデータの送信が可能であり、スタートコンディション又はストップコンディションの送信、バイト単位でのデータの送受信に利用される。 MODE is a bit for designating a mode for transmitting data, and “buffer mode” is designated when “1” is set, and “byte mode” is designated when “0” is set. . In the buffer mode, data of up to 68 bytes can be transmitted. The byte mode can transmit 1-byte data, and is used for transmission of a start condition or stop condition and transmission / reception of data in byte units.

ステータスレジスタ(REG)582は、第1マスタIC570aのステータスを示す情報が格納される。下位2ビットには常に“0”が設定され、上位5ビットにステータスコードが設定される。 The status register (REG) 582 stores information indicating the status of the first master IC 570a. “0” is always set in the lower 2 bits, and the status code is set in the upper 5 bits.

自身アドレス設定レジスタ(REG)583は、第1マスタIC570aがスレーブ(装飾制御装置)として機能する場合に設定されるレジスタである。市販されているマスタICは、通常、マスタとしての機能とスレーブとしての機能を備えており、用途に応じて使用される。自身アドレス設定REG583には、第1マスタIC570aがスレーブとして機能する場合に、自身を特定するためのアドレスが設定される。

The own address setting register (REG) 583 is a register that is set when the

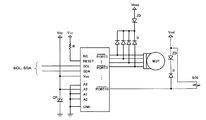

図12は、本発明の実施の形態の演出制御装置550に備えられた第2マスタIC570bと演出装置の構成を示すブロック図である。

FIG. 12 is a block diagram showing a configuration of the

前面枠3は、第2マスタIC570bに接続される簡易中継基板1600を備える。

The

簡易中継基板1600は、前面枠3及び遊技盤10に設けられた各種装置に接続される。

The

前面枠3に設けられた装置のうち簡易中継基板1600に接続される装置には、スピーカ30、照明駆動モータ位置検出センサ560b、照明駆動第1MOT13a及び照明駆動第2MOT14a(以下、照明駆動MOT13a、14a)を制御する装飾制御装置610、並びに演出ボタン17などが含まれる。

Among the devices provided on the

補助遊技装置ユニット12に設けられた装置のうち簡易中継基板1600に接続される役物駆動第1MOT71、役物駆動第2MOT81、及び役物駆動ソレノイド82を制御sるう装飾制御装置610が含まれる。

Among the devices provided in the auxiliary

簡易中継基板1600は、第2マスタIC570bから送信された電気信号を、前面枠3及び補助遊技装置ユニット12に備えられた可動物を制御する装飾制御装置610に送信(中継)する。なお、簡易中継基板1600は、中継基板600とは異なり、I2CI/Oエクスパンダ615を備えていないので、簡易中継基板1600に備えた電子部品には、演出装置を制御するための演算処理を実行する機能を有していない。

The

照明駆動第1MOT13a及び照明駆動第2MOT14aは、演出制御装置550から送信された信号に基づいて内部に備えられた発光部材を駆動させ、各種演出を実行する。

The illumination drive

また、演出制御装置550は、演出ボタン17から当該演出ボタン17が操作されたことを示す信号が簡易中継基板1600を介して入力される。さらに、照明駆動モータ位置検出センサ560bによって検出された照明駆動MOT13a、14aの位置情報が、簡易中継基板1600を介して入力される。

In addition, the

さらに、簡易中継基板1600は、演出制御装置550の音LSI557からの信号を受信し、スピーカ30から出力する。

Further, the

なお、第2マスタIC570bの構成は、第1マスタIC570aと同じ構成であるため、第2マスタIC570bの各構成には同じ符号を割り当てて説明を省略する。また、第2マスタIC570bは、第1マスタIC570aと同様に、CPU551からの指令に基づいて、装飾制御装置610との間に接続された接続線SDA及び接続線SCLの各信号レベルを制御する(第2の)信号レベル制御手段として機能する。

Since the configuration of the

なお、演出制御装置550と中継基板600及び簡易中継基板1600との接続方法、並びに、中継基板600及び簡易中継基板1600と装飾制御装置610との接続方法については、図13〜図15にて詳細を後述する。また、中継基板600及び装飾制御装置610の構成などについては、図16〜図20にて詳細を後述する。

Note that the connection method between the

前述したように、第2マスタIC570bが制御する装飾制御装置610は、可動物を可動させる可動制御装置として機能する装飾制御装置610である。可動制御装置として機能する装飾制御装置610は、センターケース51、表示装置53、及び演出制御装置550を一体化して構成される補助遊技装置ユニット12及び前面枠3に取り付けられている。前面枠3に取り付けられた装飾制御装置610は、照明駆動MOT13a、14aを制御するものである。また、補助遊技装置ユニット12に取り付けられた装飾制御装置610は、役物駆動モータ(役物駆動第1MOT71、役物駆動第2MOT81)及び役物駆動ソレノイド82を制御するものである。

に含まれている。

As described above, the

Included.

図13は、本発明の実施の形態の遊技盤10及び通常版の前面枠3に取り付けられる装飾制御装置610の接続形態の説明図である。

FIG. 13 is an explanatory diagram of a connection form of the

補助遊技装置ユニット12を構成するセンターケース51は、前述したように、枠装飾部65と枠体基部60とを組み合わせて構成される。

As described above, the

枠装飾部65には、変動表示ゲームなどの補助遊技の演出を行うための演出装置や当該演出装置を制御するための装飾制御装置610などが複数個備えられる。これらの装飾制御装置610同士を所定の信号ケーブルにより相互に接続し、さらに、この装飾制御装置610に制御される演出装置もケーブルで接続することにより、当該枠装飾部65が一体構成される。

The

また、枠体基部60にも、変動表示ゲームなどの補助遊技の演出を行うための演出装置や当該演出装置を制御するための装飾制御装置610が複数個備えられる。これらの装飾制御装置610同士を所定の信号ケーブルにより相互に接続し、さらに、この装飾制御装置610に制御される演出装置もケーブルで接続することにより、当該枠体基部60が一体構成される。

The

ゆえに、枠装飾部65や枠体基部60は、本実施形態における一体型演出ユニットを構成している。これに対し、サイドランプ45などは、一体型演出ユニットに含まれない単体の演出装置であるので、分離型演出装置を構成することになる。

Therefore, the

装飾制御装置610には、前述のように、装飾装置620を制御するためのI2CI/Oエクスパンダ615が搭載され、I2CI/Oエクスパンダ615には、個々のI2CI/Oエクスパンダ615を識別するための個別アドレスが割り当てられている。本発明の実施の形態では、前述のように、I2CI/Oエクスパンダ615の個別アドレスが、装飾制御装置610の個別アドレスとして利用される。

The

演出制御装置550は、I2CI/Oエクスパンダ615の個別アドレスを指定して制御信号を送信することによって、装飾装置620を個別に制御して演出動作を実行することが可能となる。各装飾制御装置610には、原則的に、それぞれ異なる個別アドレス(図中に「ad=」で示す)が割り当てられる。

The

また、装飾制御装置610は、接続形態によって、分岐型(分岐基板)、連結型(連結基板)及び終端型(終端基板)の三種類に分類される。分岐型、連結型及び終端型いずれの装飾制御装置610にも装飾装置620を接続可能であり、接続された装飾装置620を制御することが可能である。

Further, the

分岐型の装飾制御装置610は、下流側に複数の装飾制御装置610が直接接続され、これらの複数の装飾制御装置610に受信した制御信号を送信する。連結型の装飾制御装置610は、下流側に一つの装飾制御装置610が接続され、接続された装飾制御装置610に受信した制御信号を送信する。終端型の装飾制御装置610は、下流側に装飾制御装置610が接続されず、装飾装置620の制御のみを行う。分岐型、連結型、終端型の装飾制御装置610の詳細に関しては、図16を用いて後述する。

In the branch type

なお、上流側とは、演出制御装置550から送信された電気信号を送信する側であり、反対に、下流側とは、演出制御装置550から送信された電気信号を受信する側である。

The upstream side is the side that transmits the electrical signal transmitted from the

要するに、演出制御装置550から末端の装飾制御装置610への信号ケーブルを順に辿っていったときに、より演出制御装置550に近い側へ接続されている装飾制御装置610が上流側となり、より末端の装飾制御装置610に近い側へ接続されている装飾制御装置610が下流側となる。例えば、装飾制御装置610Aは、装飾制御装置610B、610C、610Dの上流側に配置されており、装飾制御装置610B、610C、610Dは、装飾制御装置610Aの下流側に配置されていることになる。

In short, when the signal cable from the

ここで、本発明の実施の形態では、前述のように、可動演出装置58を構成する第1演出部材70及び第2演出部材80の可動部分に装飾制御装置610が配置されている。言い換えれば、図6において、第1演出部材70の可動部(第1演出ベース100)に装飾制御装置610(第1発光基板106)が配置され、図7において、第2演出部材80の可動部(第2演出ベース110)に装飾制御装置610(第2発光基板116)が配置されている。

Here, in the embodiment of the present invention, as described above, the

このとき、従来のシフトレジスタのように、各装飾制御装置610をデイジーチェーンで配線すると、デイジーチェーンの末端となる何れか一方の装飾制御装置610だけは、入力用のケーブルのみを接続するだけで済む。しかし、デイジーチェーンの途中に接続される構成となる他方の装飾制御装置610には、入力用のケーブルと出力用のケーブルを接続する必要がある。可動部に複数のケーブルが接続されると、可動部とともに装飾制御装置610(第1発光基板106、第2発光基板116)自体が可動する構造となってケーブルも移動するため、配線の引き回しが困難になってしまうおそれがある。さらに、ケーブルの移動により、ケーブルを構成する接続線が断線する可能性が生じ、演出に影響を与えるおそれがある。

At this time, if each

本発明の実施の形態では、第1演出部材70及び第2演出部材80に配置された装飾制御装置610を終端型とし、これらの装飾制御装置610の上流に分岐型の装飾制御装置610を配置している。そのため、終端型の装飾制御装置610(第1発光基板106、第2発光基板116)には、第1演出部材70及び第2演出部材80の外部に備えた他の装飾制御装置610へ信号を伝達するケーブルが、接続されない構造となる。このように装飾制御装置610を配置すれば、可動部に配置された装飾制御装置610には入力ケーブルのみを接続すればよいことになる。したがって、デイジーチェーンで配線する場合と比較して、配線の引き回しが容易になり、断線する可能性を少なくすることができる。

In the embodiment of the present invention, the

装飾制御装置610は、受信した制御信号の宛先アドレスが自宛でない場合、下流側にさらに装飾制御装置610が接続されていれば受信した制御信号を送信する。また、送信先がなければ受信した制御信号を破棄する。

When the destination address of the received control signal is not addressed to itself, the

装飾制御装置610は、16個のポートに対応するLEDを制御することが可能であり、装飾制御装置610に搭載されたLEDと、当該装飾制御装置610に接続された外部の装飾装置基板625に搭載されたLEDとの合計数が16以下であれば、両方のLEDを制御することが可能である。すなわち、一体型の装飾制御装置610(I2CI/Oエクスパンダ615と装飾装置620がともに配置される主動型基板に相当)では、装飾装置基板625(I2CI/Oエクスパンダ615が配置されず、装飾装置620が配置される従動型基板に相当)をさらに接続することによって、内部に備えられた装飾装置620と外部に接続した装飾装置620の両方を制御することが可能である。

The

こうすることによって、離れて配置された装飾装置620を1つの装飾制御装置610で制御することが可能となり、装飾制御装置610の数を最小限にすることができる。

By doing so, it is possible to control the

第1マスタIC570aは、LEDによって構成される発光型装飾装置620に接続される発光型装飾制御装置610を制御し、第2マスタIC570bは、モータやソレノイドによって構成される可動型装飾装置620に接続される可動型装飾制御装置610を制御する。

The

第1マスタIC570aは、遊技盤10に取り付けられる中継基板600に接続され、第2マスタIC570bは、前面枠3に取り付けられる簡易中継基板1600に接続される。

The

まず、第1マスタIC570aが制御する発光型装飾制御装置610の接続形態について説明する。

First, the connection form of the light emitting

中継基板600は、上流側では演出制御装置550に搭載された第1マスタIC570aに接続し、第1マスタIC570aから送信された制御信号を受信する。また、下流側では補助遊技装置ユニット12に含まれる装飾制御装置610A(正確には一体型演出ユニットである枠体基部60に含まれる装飾制御装置610A)、及び、前面枠3に含まれる装飾制御装置610Hに接続する。さらに、中継基板600は、遊技盤10に備えられた分離型演出装置である装飾装置基板625(サイドランプ45(図8参照)に設けられた基板)に接続し、当該中継基板600に備えられたI2CI/Oエクスパンダ615によって、当該装飾装置基板625に搭載された装飾装置620を制御する。

The

補助遊技装置ユニット12には、装飾制御装置610A〜610G、及び装飾制御装置610M〜610Oが含まれる。装飾制御装置610A〜610Gは発光型装飾制御装置610であるので、第1マスタIC570aによって制御され、装飾制御装置610M〜610Oは可動型装飾制御装置610であるので、第2マスタIC570bによって制御される。

The auxiliary

装飾制御装置610Aは、分岐型の装飾制御装置であり、装飾制御装置610B及び装飾制御装置610Cに第1マスタIC570aから受信した制御信号を送信する。また、装飾制御装置610Bには、装飾装置基板625Bが接続されており、装飾装置基板625Bに配置されたLEDなどの演出装置(装飾装置620)が装飾制御装置610Bによって制御される。

The

装飾制御装置610Cは、連結型の装飾制御装置610であり、下流側の装飾制御装置610Dに受信した制御信号を送信する。装飾制御装置610Dには、分岐型の装飾制御装置610Eが接続され、さらに、装飾制御装置610Dは装飾装置基板625Dに含まれる装飾装置620Dを制御する。

The

装飾制御装置610Eには、第1演出部材70の発光態様を制御する装飾制御装置610Fと、第2演出部材80の発光態様を制御する装飾制御装置610Gとが接続される。第1演出部材70及び第2演出部材80は、連動して演出動作が実行される。装飾制御装置610Fは、第1演出部材70に含まれる第1発光基板106に配置され(図6)、また、装飾制御装置610Gは、第2演出部材80に含まれる第2発光基板116に配置されている(図7)。

The

前面枠3には、装飾制御装置610H〜610L、610P、及び610Qが含まれる。装飾制御装置610H〜610Lは発光型装飾制御装置610であるので、第1マスタIC570aによって制御され、装飾制御装置610P、及び610Qは可動型装飾制御装置610であるので、第2マスタIC570bによって制御される。

The

中継基板600に直接接続される装飾制御装置610Hは、分岐型の装飾制御装置610であり、装飾制御装置610I及び装飾制御装置610Kに第1マスタIC570aから受信した制御信号を送信する。装飾制御装置610Hは、照明ユニット11内に配置され、装飾装置基板625Hに備えられた装飾装置620Hを制御する。具体的には、照明ユニット11に含まれるLEDや異常報知LED29などが制御される。

The

装飾制御装置610I及び装飾制御装置610Iの下流側の装飾制御装置610Jは、前面枠3の左側部分の装飾部材9aを制御する。また、装飾制御装置610K及び装飾制御装置610Lは、前面枠3の右側部分の装飾部材9bを制御する。

The

前面枠3の左側部分の装飾部材9aは、装飾制御装置610I及び610Jを含む。

The

装飾制御装置610Iは、連結型の装飾制御装置610であり、下流側の装飾制御装置610Jに受信した制御信号を送信する。装飾制御装置610Iは装飾装置基板625Iに含まれる装飾装置620Iを制御する。

The

装飾制御装置610Jは、終端型の装飾制御装置610であり、下流側の装飾制御装置に接続されない。装飾制御装置610Jは装飾装置基板625Jに含まれる装飾装置620Jを制御する。

The

前面枠3の右側部分の装飾部材9bは、装飾制御装置610K及び610Lを含む。

The

装飾制御装置610Kは、連結型の装飾制御装置610であり、下流側の装飾制御装置610Lに受信した制御信号を送信する。さらに、装飾制御装置610Kは装飾装置基板625Kに含まれる装飾装置620Kを制御する。

The

装飾制御装置610Lは、終端型の装飾制御装置610であり、下流側の装飾制御装置に接続されない。装飾制御装置610Lは装飾装置基板625Lに含まれる装飾装置620Lを制御する。

The

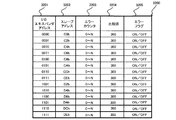

第1マスタIC570aに接続される中継基板600及び装飾制御装置610A〜610Lには、それぞれ異なる個別アドレスが割り当てられており、第1マスタIC570aから送信された制御信号に基づいて、それぞれ別々の演出動作を実行させることができる。

Different individual addresses are assigned to the

まず、中継基板600の個別アドレスには、「0000」が割り当てられている。補助遊技装置ユニット12に含まれる装飾制御装置610A、610B、610C、610D、610E、610F、及び610Gの個別アドレスには、「0001」、「0010」、「0011」、「0100」、「0101」、「0110」、及び「0111」が割り当てられている。

First, “0000” is assigned to the individual address of the

また、照明ユニット11に含まれる装飾制御装置610Hの個別アドレスには、「1001」が割り当てられている。また、装飾部材9a及び装飾部材9bに含まれる装飾制御装置610I、610J、610K、及び610Lの個別アドレスには、「1010」、「1100」、「1101」、及び「1110」が割り当てられている。

Further, “1001” is assigned to the individual address of the

また、第1マスタIC570aは、第1演出部材70に含まれるLEDなどの発光装置を制御する制御信号を、第1演出部材70を制御する装飾制御装置610Fの個別アドレス(「0110」)を指定して送信する。同様に、第1マスタIC570aは、第2演出部材80に含まれるLEDなどの発光装置を制御する制御信号を、第2演出部材80を制御する装飾制御装置610Gの個別アドレス(「0111」)を指定して送信する。

Further, the

装飾制御装置610Cは、連結型の装飾制御装置610であり、さらに、連結型の装飾制御装置610Dが接続される。

The

本発明の実施の形態では、装飾制御装置610C及び装飾制御装置610Dは、信頼度報知装置15に含まれる演出装置(LED)を制御する。所定の条件を満たした場合には、演出制御装置550の第1マスタIC570aから所定の態様を示すようにするための制御信号が送信され、指定された態様で演出を行う。

In the embodiment of the present invention, the

なお、第1マスタIC570aが制御する発光制御装置に関して、第1発光基板106自体が装飾制御装置610Fとして機能し、第2発光基板116自体が装飾制御装置610Gとして機能していてもよい。

Regarding the light emission control device controlled by the

次に、第2マスタIC570bが制御する発光型装飾制御装置610の接続形態について説明する。

Next, a connection form of the light emitting

簡易中継基板1600は、上流側では演出制御装置550に搭載された第2マスタIC570bに接続し、第2マスタIC570bから送信された制御信号を受信する。また、下流側では補助遊技装置ユニット12に含まれる装飾制御装置610M、及び、前面枠3に含まれる装飾制御装置610Pに接続する。

The

なお、簡易中継基板1600は、I2CI/Oエクスパンダ615を備えないので、中継基板600のように、直接接続された装飾装置基板625に搭載された装飾装置620を制御するものではない。

Since the

装飾制御装置610Mは、連結型の装飾制御装置であり、装飾制御装置610Nに第1マスタIC570aから受信した制御信号を送信する。また、装飾制御装置610Mには、役物駆動ソレノイド82が接続されており、装飾制御装置610Mは、役物駆動ソレノイド82へ通電させるか否かを制御することによって装飾ピース46(図2参照)の上下動を制御する。

The

装飾制御装置610Nは、連結型の装飾制御装置610であり、下流側の装飾制御装置610Oに受信した制御信号を送信する。また、装飾制御装置610Nには、役物駆動第1MOT71が接続され、装飾制御装置610Nは、役物駆動第1MOT71を制御することによって、第1演出部材70の可動(駆動)を制御する。

The

装飾制御装置610Oは、終端型の装飾制御装置610であり、下流側には装飾制御装置610は接続されない。また、装飾制御装置610Oには、役物駆動第2MOT81が接続され、装飾制御装置610Oは、役物駆動第2MOT81を制御することによって、第2演出部材80の可動(駆動)を制御する。

The decoration control device 610O is a terminal-type

簡易中継基板1600に直接接続され、前面枠3に取り付けられる装飾制御装置610Pは、連結型の装飾制御装置610であり、装飾制御装置610Qに第2マスタIC570bから受信した制御信号を送信する。装飾制御装置610Pは、照明駆動第1MOT13aに接続され、照明駆動第1MOT13aを制御することによって、第1可動式照明13の可動(駆動)を制御する。

The

装飾制御装置610Qは、終端型の装飾制御装置610であり、下流側には装飾制御装置610は接続されない。装飾制御装置610Qは、照明駆動第2MOT14aに接続され、照明駆動第2MOT14aを制御することによって、第2可動式照明14の可動(駆動)を制御する。

The

第2マスタIC570bに接続される装飾制御装置610M〜610Qには、それぞれ異なる個別アドレスが割り当てられており、第2マスタIC570bから送信された制御信号に基づいて、それぞれ別々の演出動作を実行させることができる。

Different decoration addresses are assigned to the

補助遊技装置ユニット12に含まれる装飾制御装置610M、610N、及び610Oの個別アドレスには、「0000」、「0001」、及び「0010」が割り当てられている。

“0000”, “0001”, and “0010” are assigned to the individual addresses of the

また、前面枠3に含まれる装飾制御装置610P、及び610Qの個別アドレスには、「0011」、及び「0100」が割り当てられている。

Further, “0011” and “0100” are assigned to the individual addresses of the

演出制御装置550は、変動表示ゲーム実行時など、所定の条件を満たすと、第1演出ユニット63(第1演出部材70)及び第2演出ユニット64(第2演出部材80)を制御して演出動作を実行する。

The

例えば、第2マスタIC570bは、第1演出ユニット63に含まれる役物駆動第1MOT71を制御するために、装飾制御装置610Nの個別アドレス(「0001」)を指定して役物駆動第1MOT71を動作させるための制御信号を送信し、役物駆動第1MOT71を制御する。また、第2演出ユニット64に含まれる役物駆動第2MOT81を制御するために、第2マスタIC570bは、装飾制御装置610Oの個別アドレス(「0010」)を指定して役物駆動第2MOT81を動作させるための制御信号を送信し、役物駆動第2MOT81を制御する。

For example, the

図13では、遊技機に通常版前面枠3が取り付けられる場合について説明したが、通常版前面枠3よりも廉価なコストで構成された装飾部材を備えている前面枠(廉価版前面枠)3が取り付けられる場合がある。廉価版前面枠3’が遊技機1に取り付けられる場合については、図21で詳細を説明する。

Although the case where the normal

図14は、本発明の実施の形態の演出制御装置550に搭載される第1マスタIC570aと遊技盤10に含まれる中継基板600及び当該中継基板600に接続される装飾制御装置610の接続状態を説明する図である。

FIG. 14 shows the connection state of the

図14では、演出制御装置550、中継基板600、装飾制御装置610A、610C、610H、及び610Iの接続について説明する。また、説明の都合上、装飾制御装置610として、装飾制御装置610Cから分岐した装飾制御装置610B、610Cよりも下流に接続されている各装飾制御装置(610D〜610G)、装飾制御装置610Hから分岐した装飾制御装置610K、及び装飾制御装置610Kの下流に接続されている装飾制御装置610Lについては記載を省略する。なお、各装飾制御装置610間の接続はそれぞれ同じである。

In FIG. 14, connection of the

演出制御装置550は、接続線Vcc、接続線Vled、接続線SDA、接続線SCL、接続線GND、接続線SE1〜3、及び接続線Vseによって中継基板600と接続される。

The

接続線Vcc、接続線Vled、接続線SDA、接続線SCL、接続線GND、及び接続線Vseについては、図11にて説明した通りである。 The connection line Vcc, the connection line Vled, the connection line SDA, the connection line SCL, the connection line GND, and the connection line Vse are as described in FIG.

中継基板600には、図11に示すように、役物駆動モータ(役物駆動第1MOT71、役物駆動第2MOT81)の回転位置を検出するための役物駆動モータ位置検出センサ560aが接続される。接続線SE1〜3は、役物駆動モータ位置検出センサ560aによる検出結果を受信するための接続線であり、中継基板600は、役物モータ位置検出センサ560aによって検出された役物駆動モータの回転位置を、接続線SE1〜3を介して演出制御装置550に送信する。

As shown in FIG. 11, the

中継基板600を含む装飾制御装置610は、接続線Vcc、接続線Vled、接続線SDA、接続線SCL、及び接続線GND(以下、この5本の接続線を一つのハーネスという)を介して互いに接続される。

The

中継基板600には2本のハーネスが接続されており、一方のハーネスは、中継基板600を遊技盤10の補助遊技装置ユニット12に含まれる最上流の装飾制御装置610Aに接続するためのハーネスであり、他方のハーネスは、中継基板600を前面枠3に含まれる最上流の装飾制御装置610Hに接続するためのハーネスである。

Two harnesses are connected to the

また、装飾制御装置610Aにはハーネスを介して図示しない装飾制御装置610B及び装飾制御装置610Cが接続され、装飾制御装置610Cにはハーネスを介して図示しない装飾制御装置610Dが接続される。

Also, a

また、装飾制御装置610Hにはハーネスを介して装飾制御装置610I及び図示しない装飾制御装置610Kが接続され、装飾制御装置610Iにはハーネスを介して図示しない装飾制御装置610Jが接続され、装飾制御装置610Kにはハーネスを介して図示しない装飾制御装置610Lが接続される。

In addition, a

各装飾制御装置610は、ハーネスを自身に接続するための取付口となるコネクタを備える。このコネクタは各装飾制御装置610で共通であるため、各接続線の接続順が共通となっており、誤配線を防止することができる。

Each

図15は、本発明の実施の形態の演出制御装置550と、前面枠3に含まれる簡易中継基板1600及び当該簡易中継基板1600に接続される装飾制御装置610の接続状態を説明する図である。

FIG. 15 is a diagram illustrating a connection state of the

図15では、演出制御装置550、簡易中継基板1600、装飾制御装置610M、610N、610P、及び610Qの接続について説明する。また、説明の都合上、装飾制御装置610として、装飾制御装置610Nよりも下流に接続されている装飾制御装置610Oについては記載を省略する。

FIG. 15 illustrates connection of the

演出制御装置550は、接続線Vcc、接続線Vms、接続線SDA、接続線SCL、接続線GND、接続線SE1〜3、及び接続線Vseに加え、演出ボタン17からのボタン信号を受信する接続線及び音信号をスピーカ30に送信する接続線によって簡易中継基板1600と接続される。

The

接続線Vcc、接続線Vms、接続線SDA、接続線SCL、接続線GND、及び接続線Vseについては、図14にて説明したように、下流側に配置されている各装飾制御装置610に各種信号を送受信する。

Regarding the connection line Vcc, the connection line Vms, the connection line SDA, the connection line SCL, the connection line GND, and the connection line Vse, as described with reference to FIG. 14, there are various types of

照明駆動MOT(照明駆動第1MOT13a、照明駆動第2MOT14a)、役物駆動モータ(役物駆動第1MOT71、役物駆動第2MOT81)、及び役物駆動ソレノイド82を駆動するために、接続線Vmsから供給された電力を各モータなどに供給する。

Supplied from the connection line Vms to drive the illumination drive MOT (illumination drive

また、簡易中継基板1600には、照明駆動MOTの回転位置を検出するための照明駆動MOT位置検出センサ560bが接続される。簡易中継基板1600は、照明駆動MOT位置検出センサ560bによって検出された照明駆動MOT(照明駆動第1MOT13a、照明駆動第2MOT14a)の回転位置を、接続線SE1〜3を介して演出制御装置550に送信する。

The

簡易中継基板1600に接続される装飾制御装置610は、接続線Vcc、接続線Vms、接続線SDA、接続線SCL、及び接続線GND(以下、この5本の接続線を一つのハーネスという)を介して互いに接続される。

The

簡易中継基板1600には2本のハーネスが接続されており、一方のハーネスは、簡易中継基板1600を遊技盤10の補助遊技装置ユニット12に含まれる最上流の装飾制御装置610Mに接続するためのハーネスであり、他方のハーネスは、簡易中継基板1600を前面枠3に含まれる最上流の装飾制御装置610Pに接続するためのハーネスである。

Two harnesses are connected to the

また、装飾制御装置610Mにはハーネスを介して装飾制御装置610Nが接続され、装飾制御装置610Nにはハーネスを介して図示しない装飾制御装置610Oが接続される。

In addition, a

また、装飾制御装置610Pにはハーネスを介して装飾制御装置610Qが接続される。

In addition, a

各装飾制御装置610は、ハーネスを自身に接続するための取付口となるコネクタを備える。このコネクタは各装飾制御装置610で共通であるため、各接続線の接続順が共通となっており、誤配線を防止することができる。

Each

なお、遊技機1の構成として、通常版前面枠3の代わりに廉価版前面枠3’を設けた場合でも、廉価版前面枠3’に含まれる各種基板の接続状態は、図15とほぼ同等の構成となる。

Note that, even when a low-priced

但し、廉価版前面枠3’には、照明駆動MOT(照明駆動第1MOT13a、照明駆動第2MOT14a)が設けられていないので、簡易中継基板1600’と装飾制御装置610P、及び装飾制御装置610Qを接続するケーブルが存在しない。

However, since the low

ここで、装飾制御装置610に設けられたI2CI/Oエクスパンダ615(図17で後述)が装飾装置620を制御する方法について説明する。

Here, a method in which the I 2 CI / O expander 615 (described later in FIG. 17) provided in the

演出制御装置550は、遊技制御装置500から入力された遊技データに基づいて、演出装置(装飾装置620)の出力態様を決定する。そして、演出制御装置550は、決定された出力態様となるように、制御対象となる装飾制御装置610の個別アドレス(I2CI/Oエクスパンダ615の個別アドレス)を含む演出制御データ(演出制御情報)を中継基板600又は簡易中継基板1600に出力する。このとき、演出制御データは、中継基板600から接続線SDAを介してすべての制御対象の装飾制御装置610に出力される。

The

第1マスタIC570aが制御する装飾制御装置610によって制御される演出装置はLED等の発光装置であるため、LEDの発光態様が演出装置の出力態様に相当する。この場合、演出制御データによって、LEDの点灯/点滅/消灯が指示され、さらに、LEDの点滅周期や点灯輝度も指示される。

Since the rendering device controlled by the

また、第2マスタIC570bが制御する装飾制御装置610によって制御される演出装置はモータやソレノイドなどの可動装置であるため、モータやソレノイドの動作態様が演出装置の出力態様に相当する。

In addition, since the rendering device controlled by the

各装飾制御装置610には、前述のようにあらかじめ一意な個別アドレスが設定されており、演出制御データが入力されると、入力された演出制御データに含まれるアドレスと設定されている個別アドレスとが一致するか否かを判定する。そして、入力された演出制御データに含まれるアドレスと設定されている個別アドレスとが一致すると判定された場合には、装飾制御装置610のI2CI/Oエクスパンダ615は、演出制御データを取り込んで、対応する装飾装置620の出力態様を制御するとともに、8ビット目のデータが入力された直後に返答信号をマスタIC(第1マスタIC570a、第2マスタIC570b)に出力する。

Each

以上のように、マスタICは、当該マスタICに接続されるすべての装飾制御装置610に演出制御データを送信し、当該演出制御データに含まれる個別アドレスに対応する装飾制御装置610において、要求した出力態様となるように演出装置を制御することができる。

As described above, the master IC transmits the effect control data to all the

なお、各装飾制御装置610には、個別アドレス以外にも、装飾制御装置610のI2CI/Oエクスパンダ615を初期化するためのリセット用アドレスが設定されている。このリセットアドレスは、すべてのI2CI/Oエクスパンダ615に対して共通に設けられたアドレスであり、個別アドレスとして使用することはできない。また、このリセットアドレスの値を変更することもできないように構成されている(詳細は後述する)。

Each

演出制御装置550は、装飾制御装置610(正確には、装飾制御装置610のI2CI/Oエクスパンダ615)を初期化する場合に、このリセット用の共通アドレスを含んだ初期化指示データを、中継基板600又は簡易中継基板1600に出力する。このとき、初期化指示データ及び演出制御データは、中継基板600又は簡易中継基板1600を介して、演出制御装置550に接続されるすべての装飾制御装置610に対して接続線SDAから出力される。

When the

各装飾制御装置610には、リセット用の共通アドレスがあらかじめ設定されているので、入力されたデータに含まれるアドレスと、リセット用の共通アドレスとが一致するか否かを判定する。一致すると判定された場合には、装飾制御装置610のI2CI/Oエクスパンダ615は、返答信号をマスタICに出力するとともに、入力データを初期化指示データとして取り込み、I2CI/Oエクスパンダ615自身を初期化する。

Since a common address for reset is set in advance in each

なお、I2CI/Oエクスパンダ615が初期化されると、当該初期化されたI2CI/Oエクスパンダ615によって制御される演出装置はオフ状態となる。

When the I 2 CI /

このように、装飾制御装置610は、演出制御装置550からの指令に基づく制御を行うので、演出制御装置550と装飾制御装置610との関係は、演出制御装置550の第1マスタIC570a及び第2マスタIC570bがマスタであり、各装飾制御装置610のI2CI/Oエクスパンダ615がスレーブとなる。

As described above, the

図16は、本発明の実施の形態の装飾制御装置610のブロック図である。

FIG. 16 is a block diagram of the

本発明の実施の形態の装飾制御装置610は、前述のように、接続形態に基づいて、分岐型、連結型、及び終端型の3種類に分類される。図16には、分岐型の装飾制御装置610Xに終端型の装飾制御装置610Yが接続されている例を示している。さらに、装飾制御装置610Yには、装飾装置基板625が接続されている。

As described above, the

分岐型の装飾制御装置610Xとは、I2CI/Oエクスパンダ615と、I2CI/Oエクスパンダ615が受信する信号を受け入れるためのコネクタ(上流コネクタ)と、上流コネクタから受け入れた信号を、複数の装飾制御装置610に伝達するコネクタ(下流コネクタ)を備えたものである。例えば、図中の装飾制御装置610Xのように、内部にI2CI/Oエクスパンダ615及びLED(装飾装置620)を備え、さらに、一つの上流コネクタ611と二つの下流コネクタ612A、612Bを備える。

The branch type

接続線SDA及び接続線SCLは、装飾制御装置610内で二つに分岐し、一方は、そのまま次の装飾制御装置610Yに出力するための下流コネクタ612Bに接続される。他方は、さらに分岐し、一方はI2CI/Oエクスパンダ615に接続され、他方は別の下流コネクタ612Aに接続される。

The connection line SDA and the connection line SCL are branched into two in the

また、装飾制御装置610XのI2CI/Oエクスパンダ615の出力側には、制御対象となる装飾装置620が接続される。I2CI/Oエクスパンダ615の出力側は、図18及び図19で説明するポート0〜15によって構成される。さらに、装飾制御装置610のすべてのポートが、図18で後述する電流制限抵抗R0〜R15を介して、内部のLEDに接続されている。なお、この電流制限抵抗R0〜R15も、装飾制御装置610に備えられている。

Further, a

前述したように、I2CI/Oエクスパンダ615は、演出制御装置550から入力された演出制御データに含まれるアドレスと、当該I2CI/Oエクスパンダ615に設定されている個別アドレスとが一致する場合にのみ、演出制御データに含まれる装飾データに基づいて、I2CI/Oエクスパンダ615に接続されている装飾装置620を制御する。

As described above, the I 2 CI /

なお、下流コネクタを1個しか備えないために、上流コネクタから受け入れた信号が、一つの装飾制御装置610にのみ伝達可能となっている装飾制御装置610は、連結型の装飾制御装置となる。例えば、前述した装飾制御装置610Xにて、下流コネクタ612Bのみが備えられ、下流コネクタ612Aが存在しないようなものが該当する。

Since only one downstream connector is provided, the

また、終端型の装飾制御装置とは、I2CI/Oエクスパンダ615と、I2CI/Oエクスパンダ615が受信する信号を受け入れるためのコネクタ(上流コネクタ)を有するが、上流コネクタから受け入れた信号を、他の装飾制御装置610に伝達しないものである。例えば、図中の装飾制御装置610Yは、I2CI/Oエクスパンダ615及びLED(装飾装置620)を備え、装飾制御装置610Yの外部に接続される装飾装置基板625に備わるLEDに電流を流すための接続線、装飾装置基板625のLEDに電源電圧を供給する接続線、及び、グランドに接地する接続線を介して、装飾制御装置610と装飾装置基板625とが接続される。

The terminal-type decoration control device has an I 2 CI /

装飾装置基板625は、I2CI/Oエクスパンダ615を備えておらず、LEDなどの発光装置のみを備えた基板である。この場合、装飾装置基板625に備えたLEDに接続される電流制限抵抗を、装飾装置基板625に設けることになるが、I2CI/Oエクスパンダ615が備えられた装飾制御装置610に設けてもよい。

The

なお、装飾装置基板625に設けたLEDの数に対応して、装飾制御装置610から装飾装置基板625へ渡されることになる、これらのLEDに電流を流すための接続線の数が決定される。例えば、装飾装置基板625に二つのLEDを備えた場合には、I2CI/Oエクスパンダ615のポートと対応するLEDとを接続するための2本の制御線と、Vledから供給された電力を供給する電源線1本とが、少なくとも必要となる。

It should be noted that the number of connection lines for passing current to these LEDs to be passed from the

そして、装飾制御装置610Yに設けられたI2CI/Oエクスパンダ615も、演出制御装置550から入力された演出制御データに含まれるアドレスと、当該I2CI/Oエクスパンダ615に設定されているアドレスとが一致する場合にのみ、演出制御データに含まれる装飾データに基づいて、I2CI/Oエクスパンダ615に接続されている装飾装置620を制御する。この場合、中央の装飾制御装置610に設けられた装飾装置620と、装飾装置基板625に設けられた装飾装置620の両方が、I2CI/Oエクスパンダ615によって制御される。

The I 2 CI /

このように、装飾装置基板625を設けて、装飾制御装置610から一部の装飾装置(LED)を分離させることで、離れた箇所に配置されたLEDであっても、共通のI2CI/Oエクスパンダ615により制御することができる。

In this way, by providing the

なお、第2マスタIC570bによって制御される装飾制御装置610は、前述したように、ソレノイドやモータなどの可動物を制御するものであり、具体的な構成は、図19にて後述する。

The

図17は、本発明の実施の形態のI2CI/Oエクスパンダ615の構成を示すブロック図である。

FIG. 17 is a block diagram illustrating a configuration of the I 2 CI /

I2CI/Oエクスパンダ615は、接続線SDAに接続されるトランジスタ630、接続線SDAに接続されるフィルタ631、接続線SDAに接続されるドライバ632、接続線SCLに接続されるフィルタ633、バスコントローラ634、出力設定レジスタ635、出力コントローラ636、I2CI/Oエクスパンダ615の出力側の各ポート0〜15に接続されるドライバ637、各ポート0〜15に接続されるトランジスタ638A〜638P、及びリセット信号発生回路639を備える。

The I 2 CI /

フィルタ631は、接続線SDAに接続され、接続線SDAから入力されたデータのノイズを除去し、ノイズが除去されたデータをバスコントローラ634に出力する。ドライバ632は、返答信号を接続線SDAから出力する場合に、トランジスタ630が動作可能な電圧をトランジスタ630に印加する。

The

ドライバ632は、接続線SDAからデータ(返答信号)を出力する場合に、トランジスタ630が動作可能な電圧をトランジスタ630に印加する。

When the

トランジスタ630は、電力消費を抑えるために電界効果トランジスタ(FET)が用いられており、トランジスタ630のゲートはドライバ632に接続され、ドレインはプルアップ抵抗Rにより所定の電圧が印加された接続線SDAに接続され、ソースは接地されている。

The

トランジスタ630のゲートに印加される電圧がトランジスタ630を動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れない。一方、トランジスタ630のゲートに印加される電圧がトランジスタ630を動作させる所定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流が流れることによって、接続線SDAの電圧が低下する。なお、トランジスタ630は、10ミリアンペア程度の電流をドレインからソースへ流しても破損しない仕様のものを用いている。

If the voltage applied to the gate of the

ドライバ632は、データ(返答信号)を接続線SDAから出力する場合に、トランジスタ630にドレインとソースとの間に電流を流すためにトランジスタ630のゲートにトランジスタ630が動作可能な値の電圧を印加する。そして、ドライバ632は、接続線SDAの電圧をHIGHからLOWへ繰り返し変化させることによって、データを接続線SDAから出力する。

When the

フィルタ633は、接続線SCLに接続され、接続線SCLから入力されたデータのノイズを除去し、ノイズが除去されたデータをバスコントローラ634に出力する。

The

また、I2CI/Oエクスパンダ615には、当該I2CI/Oエクスパンダ615に備わるアドレス設定用端子A0〜A3によって固有のアドレスが設定されており、バスコントローラ634に入力されている。さらに、I2CI/Oエクスパンダ615をリセットするためのアドレスも、あらかじめ設定されている。

In addition, the I 2 CI /

バスコントローラ634は、接続線SDAから入力されたデータのアドレスがI2CI/Oエクスパンダ615に設定された固有のアドレスと一致するか否かを判定し、一致している場合に当該データを演出制御データとして取り込む。

The

また、バスコントローラ634は、接続線SDAから入力されたデータのアドレスがI2CI/Oエクスパンダ615に設定されたリセット用のアドレスと一致するか否かを判定し、一致している場合に当該データを初期化指示データとして取り込み、当該I2CI/Oエクスパンダ615を初期化する。

The

また、バスコントローラ634は、接続線SCLの信号レベルのLOWからHIGHへの変化回数が8回に達し、8ビット目のデータを取り込んだ後、接続線SCLの信号レベルがHIGHからLOWへ変化すると、返答信号を接続線SDAから第1マスタIC570aに出力する。さらに、接続線SCLの信号レベルがLOWからHIGHへ変化することが確認され、再度接続線SCLの信号レベルがHIGHからLOWへ変化すると、接続線SDAを開放する。つまり、接続線SCLの信号レベルのLOWからHIGHへの変化回数が9回になるタイミングで返答信号を出力する。

In addition, the

出力設定レジスタ635には、当該I2CI/Oエクスパンダ615の動作モードやポート0〜15の出力状態が設定される。バスコントローラ634が接続線SDAから初期化指示データを取り込んで、当該I2CI/Oエクスパンダ615が初期化された場合には、出力設定レジスタ635は、すべてのポート0〜15に電流が流れないように初期状態に設定される。

In the

出力コントローラ636は、出力設定レジスタ635に設定されたデータに基づいて、ポートドライバ637を介して、各ポート0〜15に接続された演出装置に電流を流すことによって、演出装置の出力状態を実際に制御する。この出力状態は、バスコントローラ634が接続線SDAから演出制御データを取り込むと、演出制御データに指定されている内容に更新される。

Based on the data set in the

すなわち、第1マスタIC570a又は第2マスタIC570bから受信した演出制御データに基づいて、出力設定レジスタ635に設定し、ストップコンディションを受信した時点で、各ポート0〜15の出力状態を更新して演出装置に反映させる。したがって、シフトレジスタのように、LAT信号を受信する必要もなく、すなわち、LAT信号を受信するための配線を必要とすることなく、演出制御を行うことができる。特に、ポート出力状態を、複数のI2CI/Oエクスパンダ615で同時に更新する必要がある場合に有効であり、異なるI2CI/Oエクスパンダ615に制御される演出装置であっても、同時に演出動作を実行するように制御できるため、より演出効果を高めることが可能となる。

That is, based on the production control data received from the

ドライバ637は、ポートに電流を流す場合に、電流を流すポートに接続されるトランジスタ638A〜638Pが動作可能な電圧を当該トランジスタに印加する。

When a current flows through a port, the

トランジスタ638A〜638Pのゲートはドライバ637に接続され、ドレインは図19及び図20に示すように演出装置を動作させるための電圧が印加された接続線に接続するポート端子に接続され、ソースは接地されている。

The gates of the

トランジスタ638A〜638Pのゲートに印加される電圧がトランジスタ638A〜638Pを動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れない。一方、638A〜638Pのゲートに印加される電圧がトランジスタ638を動作させる所定値以上であれば、図18に示す電源Vled、又は図19に示す電源Vmotや電源Vsolからゲートに印加されている所定の電圧が、トランジスタ638のドレインを介して接地されているソースへ電流が流れることによって、ポート端子に接続された演出装置の出力状態を制御できる。

If the voltage applied to the gates of the

また、装飾制御装置610のI2CI/Oエクスパンダ615は、I2CI/Oエクスパンダ615のポート端子に接続されたすべての演出装置を同時に制御することが可能であるので、I2CI/Oエクスパンダ615のポート端子に接続された一つの演出装置を一つのグループとして制御することができる。

Also, I 2 CI /

そして、各装飾制御装置610に備わるI2CI/Oエクスパンダ615同士は、互いに異なる個別アドレスが割り当てられているので、演出装置が複数のグループに分割された形態となっている。すなわち、各装飾制御装置610に備わるI2CI/Oエクスパンダ615は、演出装置をグループ単位で制御可能なグループ単位制御手段として構成されているものである。

Since the I 2 CI /

したがって、各装飾制御装置610を統括する演出制御装置550は、グループ単位制御手段を統括して制御するグループ統括制御手段として機能している。

Therefore, the

リセット信号発生回路639には、I2CI/Oエクスパンダ615に電源を供給する接続線Vccに接続されるVcc端子、及び外部からのリセット信号を受け付けるRESET端子が接続されている。

The reset

リセット信号発生回路639は、I2CI/Oエクスパンダ615に電源が投入され、電圧が所定値まで立ち上がると、リセット信号を発生させ、発生させたリセット信号をバスコントローラ634、出力設定レジスタ635、及び出力コントローラ636に入力することによって初期化する。

The reset

なお、外部からLOWレベルのリセット信号が入力された場合には、リセット信号発生回路639はリセット信号を出力するので、演出制御装置550のCPU551から、NORゲート回路561を経由して、RESET端子からリセット信号を入力するようにしてもよい。RESET端子を使用しない場合には、図18及び図19に示すようにRESET端子はHIGHにプルアップされていてもよい。

Note that when a LOW level reset signal is input from the outside, the reset

図18は、本発明の実施の形態の第1マスタIC570aに接続される装飾装置620を制御する装飾制御装置610のI2CI/Oエクスパンダ615周辺の回路図である。

FIG. 18 is a circuit diagram around the I 2 CI /

I2CI/Oエクスパンダ615は、入力端子としてNC端子、RESET端子、SCL端子、SDA端子、Vcc端子、A0〜A3端子、及びGND端子を備え、出力端子として、PORT0〜PORT15を備える。

The I 2 CI /

RESET端子には、プルアップ抵抗Rを介してI2CI/Oエクスパンダ615に供給される電源が接続されている。このため、リセット端子に印加される電圧は常にHIGHに維持されている。

A power source supplied to the I 2 CI /

SCL端子は接続線SCLに接続され、SDA端子は接続線SDAに接続される。 The SCL terminal is connected to the connection line SCL, and the SDA terminal is connected to the connection line SDA.

Vcc端子には、I2CI/Oエクスパンダ615に供給される電源が接続される。さらに、Vcc端子には、電源ノイズを除去するコンデンサCPが接続される。

A power supply supplied to the I 2 CI /

A0端子〜A3端子は、I2CI/Oエクスパンダ615に個別アドレスを設定するための端子である。なお、I2CI/Oエクスパンダ615の個別アドレスは、通常、4ビットで表現され、この端子にI2CI/Oエクスパンダ615の電源が印加されている場合にはバスコントローラ634に「1」が設定され、この端子がグランドに接続されている場合にはバスコントローラ634に「0」が設定される。

The A0 to A3 terminals are terminals for setting individual addresses in the I 2 CI /

したがって、図18に示すI2CI/Oエクスパンダ615の個別アドレスは「0100」となる。GND端子は、電圧をグランドするための端子である。

Therefore, the individual address of the I 2 CI /

PORT0端子〜PORT15端子は、電流制限抵抗R0〜R15を介してLED0〜LED15からなる装飾装置620に接続される。なお、PORT0にように、ポート1個に対して1個のLEDを接続してもよいが、PORT1〜15のように、ポート1個に対して複数個のLEDを接続してもよい。

The PORT0 terminal to the PORT15 terminal are connected to a

すべてのポートにLEDを1個ずつ設ける場合は、1個のI2CI/Oエクスパンダ615によって、最大で16個のLEDを制御できることになる。また、各ポートに接続されるLEDの個数が異なる場合は、1個のポートに直列に接続されたすべてのLEDを1種類のLEDということにすれば、1個のI2CI/Oエクスパンダ615によって、最大で16種類のLEDを制御できることになる。

When one LED is provided for every port, a maximum of 16 LEDs can be controlled by one I 2 CI /

PORT0端子〜PORT15端子に接続されるトランジスタ638A〜638P(図17参照)のゲートに対してドライバ637から電圧が印加されると、電圧が印加されたトランジスタ638A〜638Pのドレインからソースへ電流が流れることが可能になり、PORT0端子〜PORT15端子に接続されるLED0〜LED15に電流が流れ、各LED0〜LED15は点灯する。

When a voltage is applied from the

一方、ドライバ637がトランジスタ638A〜638Pのゲートに電圧を印加しなければ、各LED0〜LED15に電流が流れない状態になり、各LED0〜LED15は点灯しない。

On the other hand, if the

図19は、本発明の実施の形態の第2マスタIC570bに接続される装飾制御装置610のI2CI/Oエクスパンダ615周辺の回路図であり、モータやソレノイドを制御する場合を示す図である。

FIG. 19 is a circuit diagram around the I 2 CI /

図19では、説明の都合上、I2CI/Oエクスパンダ615にモータとソレノイドとが接続されているが、図13に示すように、一つのI2CI/Oエクスパンダ615(つまり一つの装飾制御装置610)に一つのモータ又は一つのソレノイドが接続されるものである。このような構成により、同一グループに属する演出装置を同じタイミングで制御することが可能となるので、高速処理が必要な演出装置だけをグループ化して効率よく制御することも可能となる。

In Figure 19, for convenience of explanation, although the motor and the solenoid in I 2 CI /

ここで使用されるモータはステッピングモータにより構成され、ステッピングモータを駆動する各相の信号端子に、所定の電圧を順次印加することで回動する。本発明の実施の形態では、モータの各相の信号端子がPORT0端子〜PORT3端子に接続される。 The motor used here is constituted by a stepping motor, and rotates by sequentially applying a predetermined voltage to signal terminals of each phase that drive the stepping motor. In the embodiment of the present invention, the signal terminals of the respective phases of the motor are connected to the PORT0 terminal to the PORT3 terminal.

モータに接続されているPORT0端子〜PORT3端子に接続されるトランジスタ638A〜638Dのいずれかのゲートに対してドライバ637から電圧が印加されると、電圧が印加されたトランジスタ638A〜638Dのドレインからソースへ電流が流れることが可能になり、PORT0端子〜PORT3端子に接続されるモータに電流が流れ、役物駆動用のモータが駆動する。

When a voltage is applied from the

なお、各PORT0端子〜PORT3端子とモータとを接続する接続線は分岐し、分岐した一方の接続線は、モータに供給される電源にダイオードD及びツェナダイオードZDを介して接続される。 The connection lines connecting the PORT0 to PORT3 terminals and the motor are branched, and one of the branched connection lines is connected to a power source supplied to the motor via a diode D and a Zener diode ZD.

また、PORT端子15は、使用されるソレノイドに接続される。ソレノイドに接続されているPORT15端子に接続されるトランジスタ638Pのゲートに対してドライバ637から電圧が印加されると、電圧が印加されたトランジスタ638Pのドレインからソースへ電流が流れることが可能になり、PORT15端子に接続されるソレノイドに電流が流れ、ソレノイドによって駆動される図示しない演出装置が駆動する。

The

なお、図19では、I2CI/Oエクスパンダ615にモータ及びソレノイドの双方が接続されているが、一つのI2CI/Oエクスパンダ615に対して、モータ及びソレノイドを接続した構成でもよい。

In FIG 19, although both the motors and solenoids to I 2 CI /

図20は、本発明の実施の形態の装飾制御装置610、中継基板600及び簡易中継基板1600の回路構成を説明するための図であり、特に、信号線や電源線の入出力に関する接続状態を説明するための図である。

FIG. 20 is a diagram for explaining circuit configurations of the

本図においては、装飾制御装置610、中継基板600及び簡易中継基板1600のうち、分岐型の装飾制御装置610(例えば、装飾制御装置610Aなど)について説明を行うこととし、最後に、連結型の装飾制御装置610、終端型の装飾制御装置610、中継基板600、簡易中継基板1600との相違点の説明を行うことにする。

In this figure, among the

なお、本図においては、図16に示す分岐型の装飾制御装置610Xに備えられる部品と、同一の付番を付けて説明を行う。

In the drawing, the same reference numerals are assigned to the parts provided in the branch type

分岐型の装飾制御装置610は、上流コネクタ611、下流コネクタ612(612A、612B)、及びI2CI/Oエクスパンダ615を備える。

The branch type

上流コネクタ611は、当該装飾制御装置610よりも上流の装飾制御装置610に接続されるコネクタである。下流コネクタ612A及び612Bは、当該装飾制御装置610よりも下流側の装飾制御装置610に接続される。

The

二つの下流コネクタ612A、612Bに接続線SDAを接続するために、上流コネクタ611から延びる内部接続線SDA2011は分岐2001で第1接続線SDA2021と第2接続線SDA2031とに分岐する。第1接続線SDA2021は下流コネクタ612Aに接続され、第2接続線SDA2031は下流コネクタ612Bに接続される。

In order to connect the connection line SDA to the two

同じく、上流コネクタ611から延びる内部接続線SCL2012は分岐2002で第1接続線SCL2022と第2接続線SCL2032とに分岐する。第1接続線SCL2022は下流コネクタ612Aに接続され、第2接続線SCL2032は下流コネクタ612Bに接続される。

Similarly, the internal connection line SCL2012 extending from the

さらに、接続線SDAをI2CI/Oエクスパンダ615に接続するために、第2接続線SDA2031は分岐2003で分岐し、分岐した第2接続線SDA2031はI2CI/Oエクスパンダ615の図18及び図19に示すSDA端子に接続される。また、接続線SCLをI2CI/Oエクスパンダ615に接続するために、第2接続線SCL2032は分岐2004で分岐し、分岐した第2接続線SCL2032はI2CI/Oエクスパンダ615の図18及び図19に示すSCL端子に接続される。以下、I2CI/Oエクスパンダ615、分岐2003からI2CI/Oエクスパンダ615に接続される接続線SDA、及び分岐2004からI2CI/Oエクスパンダ615に接続される接続線SCLを含む構成をI2CI/Oエクスパンダ部2081とする。

Further, in order to connect the connection line SDA to the I 2 CI /

なお、I2CI/Oエクスパンダ615には、I2CI/Oエクスパンダ615の電源電圧となる電圧Vccが供給されている。また、図20では図示されていないが、I2CI/Oエクスパンダ615からは、装飾制御装置610に設けられたLEDなど(装飾装置620)を駆動する各ポート0〜15の信号線(図18、19参照)が出力されている。

Note that the I 2 CI /

さらに、当該装飾制御装置610のI2CI/Oエクスパンダ615が上流の装飾制御装置610に接続線SDAを介して出力する信号、及び上流の装飾制御装置610から、当該装飾制御装置610のI2CI/Oエクスパンダ615に接続線SDAを介して入力される信号のノイズを除去するために、内部接続線SDA2011にはツェナダイオードZD2041が接続されている。

Further, a signal output from the I 2 CI /

具体的には、内部接続線SDA2011は分岐2005で分岐し、分岐した内部接続線SDA2011はツェナダイオードZD2041のカソード側に接続され、ツェナダイオードZD2041のアノード側は接地されている。 Specifically, the internal connection line SDA2011 branches at a branch 2005, the branched internal connection line SDA2011 is connected to the cathode side of the Zener diode ZD2041, and the anode side of the Zener diode ZD2041 is grounded.

このため、内部接続線SDA2011に印加された所定以上の電圧(例えば、パルス性のノイズ信号)は、ツェナダイオードZD2041によって逃がされる。 For this reason, a voltage (for example, a pulsed noise signal) higher than a predetermined voltage applied to the internal connection line SDA2011 is released by the Zener diode ZD2041.

また、上流の装飾制御装置610から、当該装飾制御装置610のI2CI/Oエクスパンダ615へ接続線SCLを介して入力される信号のノイズを除去するために、内部接続線SCL2012にはツェナダイオードZD2042が接続されている。

Further, in order to remove noise of a signal input from the upstream

具体的には、内部接続線SCL2012は分岐2006で分岐し、分岐した内部接続線SCL2012はツェナダイオードZD2042のカソード側に接続され、ツェナダイオードZD2042のアノード側は接地されている。

Specifically, the internal connection line SCL2012 branches at the

このため、内部接続線SCL2012に印加された所定以上の電圧(例えば、パルス性のノイズ信号)は、ツェナダイオードZD2042によって逃がされる。 For this reason, a voltage (for example, a pulsed noise signal) higher than a predetermined voltage applied to the internal connection line SCL2012 is released by the Zener diode ZD2042.

また、当該装飾制御装置610のI2CI/Oエクスパンダ615が、下流コネクタ612Aに接続された装飾制御装置610に接続線SDAを介して出力する信号、及び下流コネクタ612Aに接続された装飾制御装置610から装飾制御装置610のI2CI/Oエクスパンダ615へ接続線SDAを介して入力される信号のノイズを除去するために、第1接続線SDA2021にはツェナダイオードZD2043が接続されている。

Further, the I 2 CI /

具体的には、第1接続線SDA2021は分岐2007で分岐し、分岐した第1接続線SDA2021はツェナダイオードZD2043のカソード側に接続され、ツェナダイオードZD2043のアノード側は接地されている。

Specifically, the first connection line SDA2021 branches at a

このため、第1接続線SDA2021に印加された所定以上の電圧(例えば、パルス性のノイズ信号)は、ツェナダイオードZD2043によって逃がされる。 For this reason, a voltage (for example, a pulsed noise signal) higher than a predetermined voltage applied to the first connection line SDA2021 is released by the Zener diode ZD2043.

また、第1接続線SDA2021に接続されるツェナダイオードZD2043と同じく、第2接続線SDA2031にもツェナダイオードZD2045が接続される。 Similarly to the Zener diode ZD2043 connected to the first connection line SDA2021, the Zener diode ZD2045 is also connected to the second connection line SDA2031.

また、装飾制御装置610のI2CI/Oエクスパンダ615から下流コネクタ612Aに接続された装飾制御装置610へ接続線SCLを介して入力される信号のノイズを除去するために、第1接続線SCL2022にはツェナダイオードZD2044が接続されている。

Further, in order to remove noise of a signal input from the I 2 CI /

具体的には、第1接続線SCL2022は分岐2008で分岐し、分岐した第1接続線SCL2022はツェナダイオードZD2044のカソード側に接続され、ツェナダイオードZD2044のアノード側は接地されている。

Specifically, the first connection line SCL2022 branches at a

このため、第1接続線SCL2022に印加された所定以上の電圧(例えば、パルス性のノイズ信号)は、ツェナダイオードZD2044によって逃がされる。 For this reason, a voltage (for example, a pulse noise signal) higher than a predetermined voltage applied to the first connection line SCL2022 is released by the Zener diode ZD2044.

また、第1接続線SCL2022に接続されるツェナダイオードZD2044と同じく、第2接続線SCL2032にもツェナダイオードZD2046が接続される。 Similarly to the Zener diode ZD2044 connected to the first connection line SCL2022, the Zener diode ZD2046 is also connected to the second connection line SCL2032.

さらに、当該装飾制御装置610のI2CI/Oエクスパンダ615に電源電圧を供給する接続線Vccに接続される上流コネクタ601のVcc端子から延びる内部接続線Vcc2071と、上流コネクタ601のGND端子から延び、接地されている内部接続線GND2072とは、平滑コンデンサC2061及びバイパスコンデンサCP2062を介して接続されている。

Further, from the internal

平滑コンデンサC2061は、電源の電圧波形を滑らかにするためのコンデンサであり、バイパスコンデンサCP2062は、電源の電圧のノイズを除去するためのコンデンサである。 The smoothing capacitor C2061 is a capacitor for smoothing the voltage waveform of the power supply, and the bypass capacitor CP2062 is a capacitor for removing noise of the power supply voltage.

このため、装飾制御装置610のI2CI/Oエクスパンダ615に供給される電源電圧は、平滑コンデンサC2061により電圧が平滑化され、バイパスコンデンサCP2062によりノイズが除去されて、I2CI/Oエクスパンダ615に供給される。

Therefore, the power supply voltage supplied to the I 2 CI /

同じく、下流コネクタ612A、612BのVcc端子から延びる内部接続線Vcc2073と、GND端子から延びる内部接続線GND2074とは、平滑コンデンサC2061及びバイパスコンデンサCP2062を介して接続されている。これによって、平滑化され、ノイズが除去された電圧が下流の装飾制御装置610に接続される接続線Vccに印加される。

Similarly, the internal

以上、分岐型の装飾制御装置610について説明を行ったが、次に、連結型の装飾制御装置610について説明する。

The branch type

なお、下流コネクタ612Aに加え、接続線SDAに接続されるツェナダイオードZD2043、及び接続線SCLに接続されるツェナダイオードZD2044、内部接続線Vcc2073、内部接続線GND2074、平滑コンデンサC2061及びバイパスコンデンサCP2062を備える構成を第1の下流コネクタ部2082とする。

In addition to the

また、下流コネクタ612Bに加え、接続線SDAに接続されるツェナダイオードZD2045、及び接続線SCLに接続されるツェナダイオードZD2046、内部接続線Vcc2073、内部接続線GND2074、平滑コンデンサC2061及びバイパスコンデンサCP2062を備える構成を第2の下流コネクタ部2083とする。

In addition to the

装飾制御装置610が連結型の場合には、基板内に一つの下流コネクタのみを備える構成となるので、下流コネクタ612Aは存在するが下流コネクタ612Bが存在しない。

In the case where the

そのため、内部接続線SDA2011及び内部接続線SCL2012は、分岐2003、2004では分岐しない構成となり、第2接続線SDA2031及び第2接続線SCL2032は存在しない点が、分岐型の装飾制御装置610とは異なる構成となる。

Therefore, the internal connection line SDA2011 and the internal connection line SCL2012 are configured not to branch at the

また、連結型の装飾制御装置610は、第2の下流コネクタ部2083を構成する電子部品が存在しない点も、分岐型の装飾制御装置610と異なる構成となる。他の構成は分岐型の装飾制御装置610と同様の構成となる。

Further, the connection type

次に、終端型の装飾制御装置610について説明する。

Next, the terminal type

装飾制御装置610が終端型の場合には、基板内に下流コネクタを備えない構成となるので、下流コネクタ612A、612Bがともに存在しない。

In the case where the