JP5775289B2 - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP5775289B2 JP5775289B2 JP2010260837A JP2010260837A JP5775289B2 JP 5775289 B2 JP5775289 B2 JP 5775289B2 JP 2010260837 A JP2010260837 A JP 2010260837A JP 2010260837 A JP2010260837 A JP 2010260837A JP 5775289 B2 JP5775289 B2 JP 5775289B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- liquid crystal

- electrode layer

- substrate

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 559

- 239000000758 substrate Substances 0.000 claims description 338

- 239000004065 semiconductor Substances 0.000 claims description 291

- 239000000463 material Substances 0.000 claims description 115

- 239000011347 resin Substances 0.000 claims description 81

- 229920005989 resin Polymers 0.000 claims description 81

- 230000001747 exhibiting effect Effects 0.000 claims description 43

- UWCWUCKPEYNDNV-LBPRGKRZSA-N 2,6-dimethyl-n-[[(2s)-pyrrolidin-2-yl]methyl]aniline Chemical compound CC1=CC=CC(C)=C1NC[C@H]1NCCC1 UWCWUCKPEYNDNV-LBPRGKRZSA-N 0.000 claims description 14

- 239000003999 initiator Substances 0.000 claims description 14

- 239000010410 layer Substances 0.000 description 1542

- 239000010408 film Substances 0.000 description 434

- 238000000034 method Methods 0.000 description 149

- 238000010438 heat treatment Methods 0.000 description 81

- 238000004544 sputter deposition Methods 0.000 description 70

- 239000007789 gas Substances 0.000 description 65

- 230000002829 reductive effect Effects 0.000 description 63

- 238000002834 transmittance Methods 0.000 description 61

- 230000005684 electric field Effects 0.000 description 55

- 239000001257 hydrogen Substances 0.000 description 53

- 229910052739 hydrogen Inorganic materials 0.000 description 53

- 239000012535 impurity Substances 0.000 description 52

- 230000001681 protective effect Effects 0.000 description 50

- 239000011229 interlayer Substances 0.000 description 47

- 230000008569 process Effects 0.000 description 47

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 44

- 239000010936 titanium Substances 0.000 description 44

- 238000005530 etching Methods 0.000 description 41

- 230000006870 function Effects 0.000 description 40

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 38

- 229910052814 silicon oxide Inorganic materials 0.000 description 38

- 229910007541 Zn O Inorganic materials 0.000 description 37

- 229910052581 Si3N4 Inorganic materials 0.000 description 35

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 35

- 229910052782 aluminium Inorganic materials 0.000 description 34

- 238000004519 manufacturing process Methods 0.000 description 34

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 33

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 31

- 229910052760 oxygen Inorganic materials 0.000 description 31

- 229910052710 silicon Inorganic materials 0.000 description 31

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 30

- 230000015572 biosynthetic process Effects 0.000 description 30

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 29

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 29

- 239000001301 oxygen Substances 0.000 description 29

- 239000010703 silicon Substances 0.000 description 29

- 229910052719 titanium Inorganic materials 0.000 description 29

- 239000011521 glass Substances 0.000 description 27

- 150000004767 nitrides Chemical class 0.000 description 26

- 229910052721 tungsten Inorganic materials 0.000 description 26

- 239000012298 atmosphere Substances 0.000 description 25

- 239000010949 copper Substances 0.000 description 25

- 229910052750 molybdenum Inorganic materials 0.000 description 25

- 229920000642 polymer Polymers 0.000 description 25

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 22

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 22

- 238000000206 photolithography Methods 0.000 description 22

- 230000006641 stabilisation Effects 0.000 description 22

- 238000011105 stabilization Methods 0.000 description 22

- 229910052751 metal Inorganic materials 0.000 description 21

- 229910044991 metal oxide Inorganic materials 0.000 description 21

- 150000004706 metal oxides Chemical group 0.000 description 21

- 239000011651 chromium Substances 0.000 description 20

- 239000002184 metal Substances 0.000 description 20

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 20

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 19

- 239000000956 alloy Substances 0.000 description 19

- 229910052786 argon Inorganic materials 0.000 description 19

- 229910052802 copper Inorganic materials 0.000 description 19

- 150000002431 hydrogen Chemical class 0.000 description 19

- 239000010937 tungsten Substances 0.000 description 19

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 18

- 239000011733 molybdenum Substances 0.000 description 18

- 239000011159 matrix material Substances 0.000 description 17

- 229910045601 alloy Inorganic materials 0.000 description 16

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 16

- 239000000203 mixture Substances 0.000 description 16

- -1 Ag) Chemical class 0.000 description 15

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 15

- 229910052804 chromium Inorganic materials 0.000 description 15

- 238000002425 crystallisation Methods 0.000 description 15

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 15

- 230000004044 response Effects 0.000 description 15

- 229910052715 tantalum Inorganic materials 0.000 description 15

- 239000010409 thin film Substances 0.000 description 14

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 14

- 239000011787 zinc oxide Substances 0.000 description 14

- 230000008025 crystallization Effects 0.000 description 13

- 150000004678 hydrides Chemical class 0.000 description 13

- 229910003437 indium oxide Inorganic materials 0.000 description 13

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 13

- 229910052757 nitrogen Inorganic materials 0.000 description 13

- 239000003566 sealing material Substances 0.000 description 13

- 239000003990 capacitor Substances 0.000 description 12

- 238000004891 communication Methods 0.000 description 12

- 239000004020 conductor Substances 0.000 description 12

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 12

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 12

- 239000011701 zinc Substances 0.000 description 12

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 11

- 238000000151 deposition Methods 0.000 description 11

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 11

- 238000012545 processing Methods 0.000 description 11

- 239000000565 sealant Substances 0.000 description 11

- 230000007704 transition Effects 0.000 description 11

- 150000001875 compounds Chemical class 0.000 description 10

- 238000001312 dry etching Methods 0.000 description 10

- 239000011368 organic material Substances 0.000 description 10

- 239000002356 single layer Substances 0.000 description 10

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 9

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 9

- 229910019092 Mg-O Inorganic materials 0.000 description 9

- 229910019395 Mg—O Inorganic materials 0.000 description 9

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 9

- 125000004429 atom Chemical group 0.000 description 9

- 230000008021 deposition Effects 0.000 description 9

- 229910052738 indium Inorganic materials 0.000 description 9

- 230000001678 irradiating effect Effects 0.000 description 9

- 125000006850 spacer group Chemical group 0.000 description 9

- 239000004990 Smectic liquid crystal Substances 0.000 description 8

- 229910021417 amorphous silicon Inorganic materials 0.000 description 8

- 230000003098 cholesteric effect Effects 0.000 description 8

- 230000018044 dehydration Effects 0.000 description 8

- 238000006297 dehydration reaction Methods 0.000 description 8

- 238000006356 dehydrogenation reaction Methods 0.000 description 8

- 229910052734 helium Inorganic materials 0.000 description 8

- 239000001307 helium Substances 0.000 description 8

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 8

- 239000010955 niobium Substances 0.000 description 8

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 8

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 8

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 8

- 229910001930 tungsten oxide Inorganic materials 0.000 description 8

- 238000001039 wet etching Methods 0.000 description 8

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 8

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 7

- 238000010586 diagram Methods 0.000 description 7

- 229910052733 gallium Inorganic materials 0.000 description 7

- 229910052759 nickel Inorganic materials 0.000 description 7

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 7

- 229920005591 polysilicon Polymers 0.000 description 7

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 7

- 239000004925 Acrylic resin Substances 0.000 description 6

- 229920000178 Acrylic resin Polymers 0.000 description 6

- 229910000838 Al alloy Inorganic materials 0.000 description 6

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 6

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 6

- 108010083687 Ion Pumps Proteins 0.000 description 6

- 229910052779 Neodymium Inorganic materials 0.000 description 6

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 6

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 6

- 230000000052 comparative effect Effects 0.000 description 6

- 229910001882 dioxygen Inorganic materials 0.000 description 6

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 6

- 239000011261 inert gas Substances 0.000 description 6

- 229910010272 inorganic material Inorganic materials 0.000 description 6

- 239000011147 inorganic material Substances 0.000 description 6

- 239000007769 metal material Substances 0.000 description 6

- 239000012299 nitrogen atmosphere Substances 0.000 description 6

- 238000009832 plasma treatment Methods 0.000 description 6

- 239000010453 quartz Substances 0.000 description 6

- 229910052706 scandium Inorganic materials 0.000 description 6

- 239000000243 solution Substances 0.000 description 6

- 238000004528 spin coating Methods 0.000 description 6

- 238000000859 sublimation Methods 0.000 description 6

- 230000008022 sublimation Effects 0.000 description 6

- 239000000126 substance Substances 0.000 description 6

- 239000004642 Polyimide Substances 0.000 description 5

- 229910004298 SiO 2 Inorganic materials 0.000 description 5

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 5

- 239000005407 aluminoborosilicate glass Substances 0.000 description 5

- 229910052788 barium Inorganic materials 0.000 description 5

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 5

- 239000005388 borosilicate glass Substances 0.000 description 5

- 239000000460 chlorine Substances 0.000 description 5

- 229910017052 cobalt Inorganic materials 0.000 description 5

- 239000010941 cobalt Substances 0.000 description 5

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 5

- 229920001940 conductive polymer Polymers 0.000 description 5

- 239000013078 crystal Substances 0.000 description 5

- 238000009792 diffusion process Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 238000009616 inductively coupled plasma Methods 0.000 description 5

- 239000012212 insulator Substances 0.000 description 5

- 238000002156 mixing Methods 0.000 description 5

- 229910052754 neon Inorganic materials 0.000 description 5

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 5

- 238000000016 photochemical curing Methods 0.000 description 5

- 229910052697 platinum Inorganic materials 0.000 description 5

- 229920001721 polyimide Polymers 0.000 description 5

- 230000005855 radiation Effects 0.000 description 5

- 238000001552 radio frequency sputter deposition Methods 0.000 description 5

- 238000007650 screen-printing Methods 0.000 description 5

- 238000005507 spraying Methods 0.000 description 5

- 229920001187 thermosetting polymer Polymers 0.000 description 5

- SYTBZMRGLBWNTM-SNVBAGLBSA-N (R)-flurbiprofen Chemical compound FC1=CC([C@H](C(O)=O)C)=CC=C1C1=CC=CC=C1 SYTBZMRGLBWNTM-SNVBAGLBSA-N 0.000 description 4

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 4

- 229910006404 SnO 2 Inorganic materials 0.000 description 4

- 150000001412 amines Chemical class 0.000 description 4

- 229910052799 carbon Inorganic materials 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 230000007547 defect Effects 0.000 description 4

- 239000000428 dust Substances 0.000 description 4

- 239000003822 epoxy resin Substances 0.000 description 4

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 4

- 238000011049 filling Methods 0.000 description 4

- 238000007667 floating Methods 0.000 description 4

- 229910052735 hafnium Inorganic materials 0.000 description 4

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 4

- 238000003780 insertion Methods 0.000 description 4

- 230000037431 insertion Effects 0.000 description 4

- 239000007788 liquid Substances 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 150000002739 metals Chemical class 0.000 description 4

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 4

- 229910052758 niobium Inorganic materials 0.000 description 4

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 4

- 238000007645 offset printing Methods 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 4

- 238000001020 plasma etching Methods 0.000 description 4

- 239000004033 plastic Substances 0.000 description 4

- 229920003023 plastic Polymers 0.000 description 4

- 229920000647 polyepoxide Polymers 0.000 description 4

- 238000004151 rapid thermal annealing Methods 0.000 description 4

- 230000002441 reversible effect Effects 0.000 description 4

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 4

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 4

- 229910052709 silver Inorganic materials 0.000 description 4

- 239000004332 silver Substances 0.000 description 4

- 238000009751 slip forming Methods 0.000 description 4

- LEONUFNNVUYDNQ-UHFFFAOYSA-N vanadium atom Chemical compound [V] LEONUFNNVUYDNQ-UHFFFAOYSA-N 0.000 description 4

- 229910052725 zinc Inorganic materials 0.000 description 4

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 3

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 229910000676 Si alloy Inorganic materials 0.000 description 3

- 229910020923 Sn-O Inorganic materials 0.000 description 3

- 229910001069 Ti alloy Inorganic materials 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 3

- 239000012300 argon atmosphere Substances 0.000 description 3

- 230000001413 cellular effect Effects 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 238000007598 dipping method Methods 0.000 description 3

- 208000037265 diseases, disorders, signs and symptoms Diseases 0.000 description 3

- 229910000449 hafnium oxide Inorganic materials 0.000 description 3

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 3

- 229910052736 halogen Inorganic materials 0.000 description 3

- 150000002367 halogens Chemical class 0.000 description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 3

- 238000002347 injection Methods 0.000 description 3

- 239000007924 injection Substances 0.000 description 3

- 239000011810 insulating material Substances 0.000 description 3

- 229910052743 krypton Inorganic materials 0.000 description 3

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 3

- 230000007774 longterm Effects 0.000 description 3

- 229910017604 nitric acid Inorganic materials 0.000 description 3

- 239000012788 optical film Substances 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- 238000007639 printing Methods 0.000 description 3

- 229910052990 silicon hydride Inorganic materials 0.000 description 3

- 230000000087 stabilizing effect Effects 0.000 description 3

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- 229910052724 xenon Inorganic materials 0.000 description 3

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 3

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical compound C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 description 2

- KWOLFJPFCHCOCG-UHFFFAOYSA-N Acetophenone Chemical compound CC(=O)C1=CC=CC=C1 KWOLFJPFCHCOCG-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 2

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 2

- XPDWGBQVDMORPB-UHFFFAOYSA-N Fluoroform Chemical compound FC(F)F XPDWGBQVDMORPB-UHFFFAOYSA-N 0.000 description 2

- 230000005355 Hall effect Effects 0.000 description 2

- 239000005264 High molar mass liquid crystal Substances 0.000 description 2

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- 238000001237 Raman spectrum Methods 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 239000004974 Thermotropic liquid crystal Substances 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- GDFCWFBWQUEQIJ-UHFFFAOYSA-N [B].[P] Chemical compound [B].[P] GDFCWFBWQUEQIJ-UHFFFAOYSA-N 0.000 description 2

- AZWHFTKIBIQKCA-UHFFFAOYSA-N [Sn+2]=O.[O-2].[In+3] Chemical compound [Sn+2]=O.[O-2].[In+3] AZWHFTKIBIQKCA-UHFFFAOYSA-N 0.000 description 2

- 230000001133 acceleration Effects 0.000 description 2

- 239000002253 acid Substances 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 239000000654 additive Substances 0.000 description 2

- 230000000996 additive effect Effects 0.000 description 2

- 239000005354 aluminosilicate glass Substances 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 229910052810 boron oxide Inorganic materials 0.000 description 2

- 239000005380 borophosphosilicate glass Substances 0.000 description 2

- 150000001721 carbon Chemical group 0.000 description 2

- 239000006229 carbon black Substances 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 230000000994 depressogenic effect Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- JKWMSGQKBLHBQQ-UHFFFAOYSA-N diboron trioxide Chemical compound O=BOB=O JKWMSGQKBLHBQQ-UHFFFAOYSA-N 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- 238000005247 gettering Methods 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-M hydroxide Chemical compound [OH-] XLYOFNOQVPJJNP-UHFFFAOYSA-M 0.000 description 2

- 230000001771 impaired effect Effects 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 2

- 229910052753 mercury Inorganic materials 0.000 description 2

- 229910001507 metal halide Inorganic materials 0.000 description 2

- 150000005309 metal halides Chemical class 0.000 description 2

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 239000000178 monomer Substances 0.000 description 2

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 description 2

- 125000000962 organic group Chemical group 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 239000000049 pigment Substances 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920006267 polyester film Polymers 0.000 description 2

- 239000003870 refractory metal Substances 0.000 description 2

- 239000010948 rhodium Substances 0.000 description 2

- 229910052594 sapphire Inorganic materials 0.000 description 2

- 239000010980 sapphire Substances 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 239000011734 sodium Substances 0.000 description 2

- 229910052708 sodium Inorganic materials 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- VZGDMQKNWNREIO-UHFFFAOYSA-N tetrachloromethane Chemical compound ClC(Cl)(Cl)Cl VZGDMQKNWNREIO-UHFFFAOYSA-N 0.000 description 2

- CZDYPVPMEAXLPK-UHFFFAOYSA-N tetramethylsilane Chemical compound C[Si](C)(C)C CZDYPVPMEAXLPK-UHFFFAOYSA-N 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 210000003462 vein Anatomy 0.000 description 2

- 239000002699 waste material Substances 0.000 description 2

- 229910052727 yttrium Inorganic materials 0.000 description 2

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 description 2

- GOXQRTZXKQZDDN-UHFFFAOYSA-N 2-Ethylhexyl acrylate Chemical compound CCCCC(CC)COC(=O)C=C GOXQRTZXKQZDDN-UHFFFAOYSA-N 0.000 description 1

- 239000005212 4-Cyano-4'-pentylbiphenyl Substances 0.000 description 1

- HHPCNRKYVYWYAU-UHFFFAOYSA-N 4-cyano-4'-pentylbiphenyl Chemical group C1=CC(CCCCC)=CC=C1C1=CC=C(C#N)C=C1 HHPCNRKYVYWYAU-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-M Acrylate Chemical compound [O-]C(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-M 0.000 description 1

- CPELXLSAUQHCOX-UHFFFAOYSA-M Bromide Chemical compound [Br-] CPELXLSAUQHCOX-UHFFFAOYSA-M 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 244000126211 Hericium coralloides Species 0.000 description 1

- CPELXLSAUQHCOX-UHFFFAOYSA-N Hydrogen bromide Chemical compound Br CPELXLSAUQHCOX-UHFFFAOYSA-N 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- CERQOIWHTDAKMF-UHFFFAOYSA-M Methacrylate Chemical compound CC(=C)C([O-])=O CERQOIWHTDAKMF-UHFFFAOYSA-M 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- 206010034960 Photophobia Diseases 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910018503 SF6 Inorganic materials 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- DAKWPKUUDNSNPN-UHFFFAOYSA-N Trimethylolpropane triacrylate Chemical compound C=CC(=O)OCC(CC)(COC(=O)C=C)COC(=O)C=C DAKWPKUUDNSNPN-UHFFFAOYSA-N 0.000 description 1

- 206010047571 Visual impairment Diseases 0.000 description 1

- GLMQLIQWKQLVMB-UHFFFAOYSA-N [O-2].[In+3].[O-2].[Ti+4] Chemical compound [O-2].[In+3].[O-2].[Ti+4] GLMQLIQWKQLVMB-UHFFFAOYSA-N 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 125000003118 aryl group Chemical group 0.000 description 1

- 230000002457 bidirectional effect Effects 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 239000003054 catalyst Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 239000007822 coupling agent Substances 0.000 description 1

- 238000001723 curing Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 125000004386 diacrylate group Chemical group 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 238000007306 functionalization reaction Methods 0.000 description 1

- 229910000078 germane Inorganic materials 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 1

- 150000002483 hydrogen compounds Chemical class 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 208000013469 light sensitivity Diseases 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- 238000001755 magnetron sputter deposition Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 239000013081 microcrystal Substances 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- QKCGXXHCELUCKW-UHFFFAOYSA-N n-[4-[4-(dinaphthalen-2-ylamino)phenyl]phenyl]-n-naphthalen-2-ylnaphthalen-2-amine Chemical compound C1=CC=CC2=CC(N(C=3C=CC(=CC=3)C=3C=CC(=CC=3)N(C=3C=C4C=CC=CC4=CC=3)C=3C=C4C=CC=CC4=CC=3)C3=CC4=CC=CC=C4C=C3)=CC=C21 QKCGXXHCELUCKW-UHFFFAOYSA-N 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- 150000001282 organosilanes Chemical class 0.000 description 1

- 229910052762 osmium Inorganic materials 0.000 description 1

- SYQBFIAQOQZEGI-UHFFFAOYSA-N osmium atom Chemical compound [Os] SYQBFIAQOQZEGI-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 239000003505 polymerization initiator Substances 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000001737 promoting effect Effects 0.000 description 1

- 238000000746 purification Methods 0.000 description 1

- 239000007870 radical polymerization initiator Substances 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 239000012266 salt solution Substances 0.000 description 1

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 1

- SBIBMFFZSBJNJF-UHFFFAOYSA-N selenium;zinc Chemical compound [Se]=[Zn] SBIBMFFZSBJNJF-UHFFFAOYSA-N 0.000 description 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 125000001424 substituent group Chemical group 0.000 description 1

- SFZCNBIFKDRMGX-UHFFFAOYSA-N sulfur hexafluoride Chemical compound FS(F)(F)(F)(F)F SFZCNBIFKDRMGX-UHFFFAOYSA-N 0.000 description 1

- 229960000909 sulfur hexafluoride Drugs 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- 239000013077 target material Substances 0.000 description 1

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 1

- 230000008646 thermal stress Effects 0.000 description 1

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 1

- QQQSFSZALRVCSZ-UHFFFAOYSA-N triethoxysilane Chemical compound CCO[SiH](OCC)OCC QQQSFSZALRVCSZ-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/133345—Insulating layers

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1337—Surface-induced orientation of the liquid crystal molecules, e.g. by alignment layers

- G02F1/133707—Structures for producing distorted electric fields, e.g. bumps, protrusions, recesses, slits in pixel electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134336—Matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134363—Electrodes characterised by their geometrical arrangement for applying an electric field parallel to the substrate, i.e. in-plane switching [IPS]

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134381—Hybrid switching mode, i.e. for applying an electric field with components parallel and orthogonal to the substrates

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/137—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells characterised by the electro-optical or magneto-optical effect, e.g. field-induced phase transition, orientation effect, guest-host interaction or dynamic scattering

- G02F1/13793—Blue phases

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Mathematical Physics (AREA)

- Geometry (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Liquid Crystal (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

Description

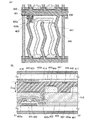

液晶表示装置を、図1、図19を用いて説明する。

本明細書に開示する発明は、パッシブマトリクス型の液晶表示装置でもアクティブマトリクス型の液晶表示装置にも適用することができる。アクティブマトリクス型の液晶表示装置の例を、図2、図8及び図18を用いて説明する。

実施の形態2において、カラーフィルタを液晶層を挟持する基板の外側に設ける例を図4に示す。なお、実施の形態1及び実施の形態2と同様なものに関しては同様の材料及び作製方法を適用することができ、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

遮光層(ブラックマトリクス)を有する液晶表示装置を、図5を用いて説明する。

遮光層(ブラックマトリクス)を有する液晶表示装置を、図6を用いて説明する。

実施の形態1乃至5において、液晶表示装置に適用できるトランジスタの他の例を示す。なお、実施の形態1乃至5と同様なものに関しては同様の材料及び作製方法を適用することができ、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

実施の形態1乃至5において、液晶表示装置に適用できるトランジスタの他の例を、図9を用いて説明する。

上記実施の形態1乃至7において、トランジスタ420、421、422の半導体層に用いることのできる材料として酸化物半導体を説明する。具体的には、半導体層として酸化物半導体層を用いたトランジスタ1420、1450を説明する。

本実施の形態は、実施の形態8で示した酸化物半導体層を含むトランジスタ、及び作製方法の一例を図26を用いて詳細に説明する。本実施の形態で示すトランジスタ390は、上記実施の形態における、チャネル形成領域を含む酸化物半導体層を用いるトランジスタ1420、1450として適用することができる。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

本実施の形態は、実施の形態8で示した酸化物半導体層を含むトランジスタ、及び作製方法の一例を図27を用いて詳細に説明する。本実施の形態で示すトランジスタ310は、上記実施の形態における、チャネル形成領域を含む酸化物半導体層を用いるトランジスタ1420、1450として適用することができる。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

本実施の形態は、実施の形態8で示した酸化物半導体層を含むトランジスタ、及び作製方法の一例を図25を用いて詳細に説明する。本実施の形態で示すトランジスタ380は、上記実施の形態における、チャネル形成領域を含む酸化物半導体層を用いるトランジスタ1420、1450として適用することができる。

上記実施の形態2乃至11において、トランジスタの半導体層に用いることのできる他の材料の例を説明する。

本明細書に開示する発明は、パッシブマトリクス型の液晶表示装置でもアクティブマトリクス型の液晶表示装置にも適用することができる。パッシブマトリクス型の液晶表示装置の例を、図3を用いて説明する。液晶表示装置の上面図を図3(A)に、図3(A)における線G−Hの断面図を図3(B)に示す。また、図3(A)には、液晶層1703、対向基板である基板1710、偏光板1714a、1714bなどは省略され図示されていないが、図3(B)で示すようにそれぞれ設けられている。

本実施の形態では、液晶表示装置の一形態を図23のブロック図及び図24のタイミングチャートを用いて説明する。

トランジスタを作製し、該トランジスタを画素部、さらには駆動回路に用いて表示機能を有する液晶表示装置を作製することができる。また、トランジスタを駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

本明細書に開示する液晶表示装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

11 基板

20 画素電極層

21a 共通電極層

21b 共通電極層

22a 共通電極層

22b 共通電極層

23 構造体

24 液晶層

200 基板

201 基板

202a 矢印

202b 矢印

202c 矢印

202d 矢印

208 液晶層

230a 画素電極層

230b 画素電極層

231a 共通電極層

231b 共通電極層

231c 共通電極層

232a 共通電極層

232b 共通電極層

232c 共通電極層

233a 構造体

233b 構造体

234a 構造体

234b 構造体

234c 構造体

235a 構造体

235b 構造体

235c 構造体

240a 画素電極層

240b 画素電極層

241a 構造体

241b 構造体

242a 画素電極層

242b 画素電極層

243a 構造体

243b 構造体

305 基板

306 保護絶縁層

307 ゲート絶縁層

310 トランジスタ

311 ゲート電極層

312 酸化物半導体層

315a ソース電極層

315b ドレイン電極層

316 酸化物絶縁層

330 酸化物半導体膜

331 酸化物半導体層

370 基板

372a ゲート絶縁層

372b ゲート絶縁層

373 保護絶縁層

380 トランジスタ

381 ゲート電極層

382 酸化物半導体層

385a ソース電極層

385b ドレイン電極層

386 酸化物絶縁層

390 トランジスタ

391 ゲート電極層

392 酸化物半導体層

393 酸化物半導体膜

394 基板

395a ソース電極層

395b ドレイン電極層

396 酸化物絶縁層

397 ゲート絶縁層

398 保護絶縁層

399 酸化物半導体層

401 ゲート電極層

402 ゲート絶縁層

403 半導体層

404a ドレイン領域

405a 配線層

405b 配線層

407 絶縁膜

408 容量配線層

409 絶縁層

413 層間膜

414 遮光層

415 絶縁層

416 絶縁膜

417 透光性樹脂層

420 トランジスタ

421 トランジスタ

422 トランジスタ

441 基板

442 基板

443a 偏光板

443b 偏光板

444 液晶層

446 電極層

446a 電極層

446b 電極層

446c 電極層

446d 電極層

447 電極層

447a 電極層

447b 電極層

447c 電極層

447d 電極層

448 電極層

448a 電極層

448b 電極層

448c 電極層

449 構造体

450 カラーフィルタ

451 素子層

454a 透光性樹脂層

455a 遮光層

456a シール材

457 光

458 液晶層

459a 基板

459b 基板

1000 携帯電話機

1001 筐体

1002 表示部

1003a 操作ボタン

1004 外部接続ポート

1005 スピーカ

1006 マイク

1301 表示部

1302 駆動部

1303 信号線駆動回路

1304 走査線駆動回路

1305 画素

1306 走査線

1308 信号線

1400 基板

1401 ゲート電極層

1402 ゲート絶縁層

1403 酸化物半導体層

1405a ソース電極層

1405b ドレイン電極層

1407 酸化物絶縁層

1409 保護絶縁層

1420 トランジスタ

1432a ゲート絶縁層

1432b ゲート絶縁層

1437 酸化物絶縁層

1439 保護絶縁層

1450 トランジスタ

1700 基板

1701a 画素電極層

1701b 画素電極層

1701c 画素電極層

1703 液晶層

1705a 共通電極層

1706a 共通電極層

1707a 構造体

1707b 構造体

1707c 構造体

1714a 偏光板

1714b 偏光板

1710 基板

1713 液晶素子

1714 偏光板

2600 素子基板

2601 対向基板

2602 シール材

2603 素子層

2604 表示素子

2605 層間膜

2606 偏光板

2607 偏光板

2608 配線回路部

2609 フレキシブル配線基板

2610 冷陰極管

2611 反射板

2612 回路基板

2613 拡散板

4001 基板

4002 画素部

4003 信号線駆動回路

4003a 信号線駆動回路

4003b 信号線駆動回路

4004 走査線駆動回路

4005 シール材

4006 基板

4008 液晶層

4010 トランジスタ

4011 トランジスタ

4013 液晶素子

4015 接続端子電極

4016 端子電極

4018 FPC

4019 異方性導電膜

4020 絶縁層

4021 層間膜

4030 画素電極層

4031 共通電極層

4032 偏光板

4034 遮光層

4036 共通電極層

4037 構造体

4038 構造体

8310 比抵抗/ホール測定システムResiTest

9400 通信装置

9401 筐体

9402 操作ボタン

9403 外部入力端子

9404 マイク

9405 スピーカ

9406 発光部

9410 表示装置

9411 筐体

9412 表示部

9413 操作ボタン

9600 テレビジョン装置

9601 筐体

9603 表示部

9605 スタンド

9607 表示部

9609 操作キー

9610 リモコン操作機

9700 デジタルフォトフレーム

9701 筐体

9703 表示部

9881 筐体

9882 表示部

9883 表示部

9884 スピーカ部

9885 入力手段(操作キー

9886 記録媒体挿入部

9887 接続端子

9888 センサ

9889 マイクロフォン

9890 LEDランプ

9891 筐体

9893 連結部

9900 スロットマシン

9901 筐体

9903 表示部

Claims (9)

- 第1の基板と第2の基板との間に、ブルー相を示す液晶材料を含む液晶層を有し、

前記第2の基板と前記液晶層との間に設けられた第2の電極層と、

前記第2の電極層と重畳し、前記第1の基板と前記液晶層との間に設けられた第3の電極層と、

前記第1の基板の前記液晶層側の面から前記液晶層中に突出する構造体と、

前記構造体の上部に設けられた第1の電極層と、

を有し、

前記第2の電極層は、開口パターンを有し、

前記第3の電極層は、開口パターンを有し、

前記構造体は、前記第3の電極層の開口パターンの間に設けられ、

前記第1の電極層は、開口パターンを有し、

前記第1の電極層は、前記液晶層中において、前記第2の電極層と前記第3の電極層との間に配置され、

前記構造体は、錐形の先端が丸いドーム状であり、

前記構造体の側面は、前記液晶層と接し、

セルギャップは5μm未満であることを特徴とする液晶表示装置。 - 第1の基板と第2の基板との間に、ブルー相を示す液晶材料を含む液晶層を有し、

前記第2の基板の前記液晶層側の面から前記液晶層中に突出する第2の構造体と、

前記第2の構造体の上部に設けられた第2の電極層と、

前記第2の電極層と重畳し、前記第1の基板と前記液晶層との間に設けられた第3の電極層と、

前記第1の基板の前記液晶層側の面から前記液晶層中に突出する第1の構造体と、

前記第1の構造体の上部に設けられた第1の電極層と、

を有し、

前記第2の電極層は、開口パターンを有し、

前記第3の電極層は、開口パターンを有し、

前記構造体は、前記第3の電極層の開口パターンの間に設けられ、

前記第1の電極層は、前記液晶層中において、前記第2の電極層と前記第3の電極層との間に配置され、

前記第1の構造体は、錐形の先端が丸いドーム状であり、

前記第1の構造体の側面は、前記液晶層と接し、

前記第2の構造体は、錐形の先端が丸いドーム状であり、

前記第2の構造体の側面は、前記液晶層と接し、

セルギャップは5μm未満であることを特徴とする液晶表示装置。 - 第1の基板と第2の基板との間に、ブルー相を示す液晶材料を含む液晶層を有し、

前記第2の基板の前記液晶層側の面から前記液晶層中に突出する第2の構造体と、

前記第2の構造体の上部に設けられた第2の電極層と、

前記第1の基板の前記液晶層側の面から前記液晶層中に突出する第3の構造体と、

前記第2の電極層と重畳し、前記第3の構造体の上部に設けられた第3の電極層と、

前記第1の基板の前記液晶層側の面から前記液晶層中に突出する第1の構造体と、

前記第1の構造体の上部に設けられた第1の電極層と、

を有し、

前記第2の電極層は、開口パターンを有し、

前記第3の電極層は、開口パターンを有し、

前記構造体は、前記第3の電極層の開口パターンの間に設けられ、

前記第1の電極層は、前記液晶層中において、前記第2の電極層と前記第3の電極層との間に配置され、

前記第1の構造体は、錐形の先端が丸いドーム状であり、

前記第1の構造体の側面は、前記液晶層と接し、

前記第2の構造体は、錐形の先端が丸いドーム状であり、

前記第2の構造体の側面は、前記液晶層と接し、

前記第3の構造体は、錐形の先端が丸いドーム状であり、

前記第3の構造体の側面は、前記液晶層と接し、

セルギャップは5μm未満であることを特徴とする液晶表示装置。 - 請求項1乃至3のいずれか一項において、

前記第1の電極層と前記第2の電極層との間の距離と、前記第1の電極層と前記第3の電極層との間の距離は等しいことを特徴とする液晶表示装置。 - 請求項1乃至4のいずれか一項において、

前記第1の電極層、前記第2の電極層、及び前記第3の電極層は、それぞれ前記液晶層に接していることを特徴とする液晶表示装置。 - 請求項1乃至5のいずれか一項において、

前記第1の電極層、前記第2の電極層、及び前記第3の電極層は櫛歯状であることを特徴とする液晶表示装置。 - 請求項1乃至6のいずれか一項において、

前記液晶層は、カイラル剤を含むことを特徴とする液晶表示装置。 - 請求項1乃至7のいずれか一項において、

前記液晶層は、光硬化樹脂及び光重合開始剤を有することを特徴とする液晶表示装置。 - 請求項1乃至8のいずれか一項において、

前記第1の基板と、前記第1の電極層及び前記第3の電極層との間にトランジスタを有し、

前記第1の電極層は前記トランジスタと電気的に接続されており、

前記トランジスタは酸化物半導体層を含むことを特徴とする液晶表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010260837A JP5775289B2 (ja) | 2009-11-24 | 2010-11-24 | 液晶表示装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009266231 | 2009-11-24 | ||

| JP2009266231 | 2009-11-24 | ||

| JP2010260837A JP5775289B2 (ja) | 2009-11-24 | 2010-11-24 | 液晶表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011133874A JP2011133874A (ja) | 2011-07-07 |

| JP2011133874A5 JP2011133874A5 (ja) | 2014-01-23 |

| JP5775289B2 true JP5775289B2 (ja) | 2015-09-09 |

Family

ID=44061843

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010260837A Active JP5775289B2 (ja) | 2009-11-24 | 2010-11-24 | 液晶表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8355109B2 (ja) |

| JP (1) | JP5775289B2 (ja) |

| KR (1) | KR20110058693A (ja) |

| CN (1) | CN102162955B (ja) |

| TW (1) | TWI529465B (ja) |

Families Citing this family (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20100165280A1 (en) * | 2008-12-25 | 2010-07-01 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| WO2011065259A1 (en) * | 2009-11-27 | 2011-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| JP5744366B2 (ja) * | 2010-04-12 | 2015-07-08 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| US8928846B2 (en) | 2010-05-21 | 2015-01-06 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device having dielectric film over and in contact with wall-like structures |

| JP5836846B2 (ja) | 2011-03-11 | 2015-12-24 | 株式会社半導体エネルギー研究所 | 液晶表示装置の作製方法 |

| CN103290371B (zh) * | 2011-06-08 | 2015-02-25 | 株式会社半导体能源研究所 | 溅射靶材、溅射靶材的制造方法及薄膜形成方法 |

| WO2013058157A1 (ja) * | 2011-10-18 | 2013-04-25 | シャープ株式会社 | 液晶表示パネル及び液晶表示装置 |

| US9116397B2 (en) * | 2011-11-23 | 2015-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and method for manufacturing the same |

| CN103959158B (zh) * | 2011-11-28 | 2017-08-01 | 株式会社半导体能源研究所 | 液晶显示装置 |

| JP5865149B2 (ja) * | 2012-03-23 | 2016-02-17 | 株式会社ジャパンディスプレイ | 表示装置、電子装置 |

| KR20130112628A (ko) | 2012-04-04 | 2013-10-14 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| JP5944752B2 (ja) * | 2012-06-12 | 2016-07-05 | 株式会社ジャパンディスプレイ | 液晶表示装置及びその製造方法 |

| CN102749767B (zh) * | 2012-06-19 | 2015-05-13 | 京东方科技集团股份有限公司 | 一种蓝相液晶显示面板及蓝相液晶显示装置 |

| CN107564967B (zh) | 2012-07-20 | 2020-10-23 | 株式会社半导体能源研究所 | 显示装置 |

| TWI489184B (zh) | 2012-07-26 | 2015-06-21 | Au Optronics Corp | 液晶顯示面板 |

| TWI494670B (zh) * | 2012-08-10 | 2015-08-01 | Innocom Tech Shenzhen Co Ltd | 藍相液晶顯示面板之電極製造方法 |

| US9140937B2 (en) * | 2012-12-20 | 2015-09-22 | Industrial Technology Research Institute | Display panel |

| KR101990115B1 (ko) | 2012-12-21 | 2019-10-01 | 삼성디스플레이 주식회사 | 표시 장치 |

| TWI491967B (zh) * | 2013-06-20 | 2015-07-11 | Au Optronics Corp | 畫素結構及顯示面板 |

| KR102095027B1 (ko) * | 2013-07-12 | 2020-04-16 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| CN103676356B (zh) * | 2013-12-10 | 2016-04-27 | 京东方科技集团股份有限公司 | 显示装置 |

| CN104076424A (zh) * | 2014-07-28 | 2014-10-01 | 上海交通大学 | 全息聚合物分散液晶光栅及其制备方法 |

| US20170343869A1 (en) * | 2014-12-04 | 2017-11-30 | Sharp Kabushiki Kaisha | Liquid crystal display device |

| US10429704B2 (en) | 2015-03-26 | 2019-10-01 | Semiconductor Energy Laboratory Co., Ltd. | Display device, display module including the display device, and electronic device including the display device or the display module |

| CN104880883A (zh) * | 2015-06-12 | 2015-09-02 | 武汉华星光电技术有限公司 | 一种蓝相液晶显示面板及其制作方法 |

| CN104965357B (zh) * | 2015-06-30 | 2019-08-30 | 武汉华星光电技术有限公司 | 蓝相液晶面板 |

| CN104977769B (zh) * | 2015-08-04 | 2019-03-15 | 武汉华星光电技术有限公司 | 蓝相液晶面板和蓝相液晶显示器 |

| CN105116639A (zh) * | 2015-09-17 | 2015-12-02 | 武汉华星光电技术有限公司 | 蓝相液晶显示器、蓝相液晶显示模组及其制作方法 |

| CN105204209B (zh) * | 2015-10-23 | 2019-03-15 | 武汉华星光电技术有限公司 | 一种蓝相液晶显示面板 |

| US9927666B2 (en) * | 2016-04-20 | 2018-03-27 | a.u. Vista Inc. | Liquid crystal display systems and related methods |

| KR20200089294A (ko) * | 2017-12-28 | 2020-07-24 | 커넥텍 재팬 가부시키가이샤 | 지문 센서 및 표시장치 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09105953A (ja) | 1995-10-12 | 1997-04-22 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

| US6449024B1 (en) * | 1996-01-26 | 2002-09-10 | Semiconductor Energy Laboratory Co., Inc. | Liquid crystal electro-optical device utilizing a polymer with an anisotropic refractive index |

| JP3708620B2 (ja) | 1996-03-01 | 2005-10-19 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型液晶電気光学装置 |

| JPH10104644A (ja) * | 1996-10-01 | 1998-04-24 | Citizen Watch Co Ltd | 液晶表示装置用基板 |

| US6791757B2 (en) * | 1999-07-12 | 2004-09-14 | Coho Holdings, Llc | Optical device for filtering and sensing |

| TW573190B (en) * | 2000-08-14 | 2004-01-21 | Samsung Electronics Co Ltd | Liquid crystal display and fabricating method thereof |

| JP4081643B2 (ja) * | 2001-08-01 | 2008-04-30 | 株式会社日立製作所 | 液晶表示装置 |

| TW594234B (en) * | 2002-12-02 | 2004-06-21 | Ind Tech Res Inst | Wide viewing angle LCD device with laterally driven electric field and its manufacturing method |

| DE602004023641D1 (de) | 2003-11-27 | 2009-11-26 | Asahi Glass Co Ltd | Optisches element mit einem flüssigkristall mit optischer isotropie |

| US7327433B2 (en) | 2004-01-15 | 2008-02-05 | Sharp Kabushiki Kaisha | Display element, display device, and manufacturing method of display element |

| JP4027941B2 (ja) | 2004-01-16 | 2007-12-26 | シャープ株式会社 | 表示素子および表示装置 |

| KR100781819B1 (ko) | 2004-03-19 | 2007-12-03 | 도꾸리쯔교세이호징 가가꾸 기쥬쯔 신꼬 기꼬 | 액정표시 소자 |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP4476137B2 (ja) | 2005-02-28 | 2010-06-09 | セイコーエプソン株式会社 | 液晶装置および電子機器 |

| JP2007086205A (ja) | 2005-09-20 | 2007-04-05 | Sharp Corp | 表示パネルおよび表示装置 |

| JP5064747B2 (ja) * | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| EP2270583B1 (en) | 2005-12-05 | 2017-05-10 | Semiconductor Energy Laboratory Co., Ltd. | Transflective Liquid Crystal Display with a Horizontal Electric Field Configuration |

| US7713596B2 (en) | 2006-06-07 | 2010-05-11 | Chunghwa Picture Tubes, Ltd. | Light shading structure, and color filter substrate, active device array substrate, liquid crystal display panel thereof |

| JP5019848B2 (ja) | 2006-10-31 | 2012-09-05 | ソニーモバイルディスプレイ株式会社 | 液晶装置及び電子機器 |

| KR20080050851A (ko) * | 2006-12-04 | 2008-06-10 | 삼성전자주식회사 | 액정표시패널 |

| KR20090063761A (ko) * | 2007-12-14 | 2009-06-18 | 삼성전자주식회사 | 표시 장치 |

| US20100165280A1 (en) | 2008-12-25 | 2010-07-01 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| US8395740B2 (en) | 2009-01-30 | 2013-03-12 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device having blue phase liquid crystal and particular electrode arrangement |

| KR101662998B1 (ko) | 2009-03-26 | 2016-10-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 표시 장치 및 액정 표시 장치의 제작 방법 |

| WO2011065259A1 (en) | 2009-11-27 | 2011-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

-

2010

- 2010-11-11 US US12/944,097 patent/US8355109B2/en active Active

- 2010-11-18 TW TW099139771A patent/TWI529465B/zh not_active IP Right Cessation

- 2010-11-23 KR KR1020100116777A patent/KR20110058693A/ko not_active Application Discontinuation

- 2010-11-24 JP JP2010260837A patent/JP5775289B2/ja active Active

- 2010-11-24 CN CN201010576044.0A patent/CN102162955B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20110122332A1 (en) | 2011-05-26 |

| CN102162955B (zh) | 2015-05-20 |

| CN102162955A (zh) | 2011-08-24 |

| US8355109B2 (en) | 2013-01-15 |

| JP2011133874A (ja) | 2011-07-07 |

| TW201207519A (en) | 2012-02-16 |

| TWI529465B (zh) | 2016-04-11 |

| KR20110058693A (ko) | 2011-06-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5775289B2 (ja) | 液晶表示装置 | |

| JP5759704B2 (ja) | 液晶表示装置 | |

| JP6983209B2 (ja) | 液晶表示装置 | |

| JP5546236B2 (ja) | 液晶表示装置の作製方法 | |

| JP5336397B2 (ja) | 液晶表示装置 | |

| JP5987083B2 (ja) | 液晶表示装置 | |

| JP5468376B2 (ja) | 液晶表示装置 | |

| JP5444121B2 (ja) | 液晶表示装置 | |

| JP5587031B2 (ja) | 液晶表示装置 | |

| JP2020042314A (ja) | 液晶表示装置 | |

| JP5987082B2 (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20131018 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131128 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140307 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140422 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140619 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20141118 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150114 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150616 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150703 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5775289 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |