JP5676273B2 - パンチスルー効果を利用した半導体発光デバイス - Google Patents

パンチスルー効果を利用した半導体発光デバイス Download PDFInfo

- Publication number

- JP5676273B2 JP5676273B2 JP2010543598A JP2010543598A JP5676273B2 JP 5676273 B2 JP5676273 B2 JP 5676273B2 JP 2010543598 A JP2010543598 A JP 2010543598A JP 2010543598 A JP2010543598 A JP 2010543598A JP 5676273 B2 JP5676273 B2 JP 5676273B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- junction

- junction region

- emitting device

- light emitting

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 22

- 230000000694 effects Effects 0.000 title claims description 8

- 239000000463 material Substances 0.000 claims description 24

- 239000000969 carrier Substances 0.000 claims description 19

- 230000007704 transition Effects 0.000 claims description 16

- 238000000034 method Methods 0.000 claims description 13

- 230000004888 barrier function Effects 0.000 claims description 11

- 230000015556 catabolic process Effects 0.000 claims description 8

- 229910052710 silicon Inorganic materials 0.000 claims description 7

- 238000005401 electroluminescence Methods 0.000 claims description 6

- 239000010703 silicon Substances 0.000 claims description 6

- 239000013078 crystal Substances 0.000 claims description 3

- 238000002347 injection Methods 0.000 description 16

- 239000007924 injection Substances 0.000 description 16

- 238000010586 diagram Methods 0.000 description 13

- 238000005215 recombination Methods 0.000 description 8

- 230000006798 recombination Effects 0.000 description 8

- 230000008569 process Effects 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 230000005684 electric field Effects 0.000 description 5

- 108091006149 Electron carriers Proteins 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000005284 excitation Effects 0.000 description 2

- 230000003993 interaction Effects 0.000 description 2

- 230000007935 neutral effect Effects 0.000 description 2

- 230000002285 radioactive effect Effects 0.000 description 2

- 229910008310 Si—Ge Inorganic materials 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- 239000003031 high energy carrier Substances 0.000 description 1

- 230000005693 optoelectronics Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 238000004080 punching Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/0004—Devices characterised by their operation

- H01L33/0008—Devices characterised by their operation having p-n or hi-lo junctions

- H01L33/0016—Devices characterised by their operation having p-n or hi-lo junctions having at least two p-n junctions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/34—Materials of the light emitting region containing only elements of Group IV of the Periodic Table

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Led Devices (AREA)

Description

−半導体からなるボディと、

−ボディ内の、第1のドーピング・タイプをもつボディの第1の領域と第2のドーピング・タイプをもつボディの第2の領域との間に形成された、第1の接合領域と、

−ボディ内の、ボディの第2の領域と第1のドーピング・タイプをもつボディの第3の領域との間に形成された、第2の接合領域と、

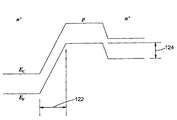

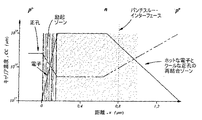

−使用の際に、第1の接合領域に逆バイアスをかけて降伏モードにし、また第2の接合領域の少なくとも一部に順バイアスをかけて、第1の接合領域に向かってキャリアを注入するために、ボディに接続された端子構成と

を備え、

−逆バイアスがかけられた第1の接合領域に関連する第1の空乏領域が、第2の領域をパンチスルーして、第2の接合領域の順バイアスがかけられた少なくとも一部に関連する第2の空乏領域に至るように構成された

発光デバイスが提供される。

−半導体材料からなるボディを利用するステップと、

−第1のドーピング・タイプをもつボディの第1の領域と第2のドーピング・タイプをもつボディの第2の領域との間に、第1の接合領域が形成されるようにし、ボディ内の、ボディの第2の領域と第1のドーピング・タイプをもつボディの第3の領域との間に、第2の接合領域が形成されるようにするステップと、

−第1の接合領域に逆バイアスをかけて降伏モードにするステップと、

−第2の接合領域の少なくとも一部に順バイアスをかけて、第1の接合領域に向かってキャリアが注入されるようにするステップと、

−逆バイアスがかけられた第1の接合領域に関連する第1の空乏領域に、ボディの第2の領域をパンチスルーさせて、順バイアスがかけられた第2の接合領域に関連する第2の空乏領域に至らせるステップと

を含む方法を、本発明の範囲内に含む。

Claims (15)

- 半導体材料からなるボディと、

前記ボディ内の、第1のドーピング・タイプをもつ前記ボディの第1の領域と第2のドーピング・タイプをもつ前記ボディの第2の領域との間に形成された、第1の接合領域と、

前記ボディ内の、前記ボディの前記第2の領域と前記第1のドーピング・タイプをもつ前記ボディの第3の領域との間に形成された、第2の接合領域と、

前記ボディに接続され、第2の接合領域の少なくとも一部に順バイアスをかけ、前記第1の接合領域が降伏モードとなるように第1の接合領域へと逆バイアスを印加するように構成された端子構成と

を備え、

前記逆バイアスがかけられた第1の接合領域に関連する第1の空乏領域が、前記第2の接合領域の少なくとも一部のエネルギー障壁を低くするために、前記第2の接合領域の前記順バイアスがかけられた少なくとも一部に関連する第2の空乏領域にパンチスルーするように構成されるとともに、キャリアを前記第2の接合領域の少なくとも一部から第1の空乏領域へと注入し、これによりデバイスにおけるエレクトロルミネセンス効果を向上させるように構成された

発光デバイス。

- 前記第2の接合領域の前記少なくとも一部は前記第1の接合領域および前記第1の接合領域の表面から横方向に離隔され、前記第2の接合領域の他の領域は逆バイアスがかけられる請求項1に記載の発光デバイス。

- 前記半導体材料が単結晶間接遷移型半導体材料である、請求項1または2に記載の発光デバイス。

- 前記半導体材料がシリコンを含む、請求項3に記載の発光デバイス。

- 記半導体材料が直接遷移型半導体材料である、請求項1または2に記載の発光デバイス。

- 前記第1のドーピング・タイプがnであり、前記第2のドーピング・タイプがpである、請求項1乃至5のいずれか1項に記載の発光デバイス。

- 前記第1のドーピング・タイプがpであり、前記第2のドーピング・タイプがnである、請求項1乃至5のいずれか1項に記載の発光デバイス。

- 降伏モードが、アバランシェ・モード、電界放出モード、およびアバランシェ・モードと電界放出モードの組合せのうちの1つである、請求項1乃至6のいずれか1項に記載の発光デバイス。

- 前記第1の空乏領域が前記第2の接合領域にパンチスルーする、請求項1乃至8のいずれか1項に記載の発光デバイス。

- 前記端子構成が、前記ボディの前記第1の領域に接続された、第1の極性の電圧を前記第1の領域に印加するための第1の端子と、前記ボディの前記第3の領域に接続された、反対極性の電圧を前記第3の領域に印加するための第2の端子との2つの端子を備える、請求項1乃至9のいずれか1項に記載の発光デバイス。

- 前記端子構成が、前記ボディの前記第1の領域に接続されている、第1の極性の電圧を前記ボディの前記第1の領域に印加するための第1の端子と、前記ボディの前記第3の領域に接続されている、反対極性の電圧を前記第3の領域に印加するための第2の端子と、前記ボディの前記第2の領域に接続されている第3の端子との3つの端子を備える、請求項1乃至10のいずれか1項に記載の発光デバイス。

- 発光デバイスを動作させる方法であって、

第1のドーピング・タイプをもつ前記ボディの第1の領域と第2のドーピング・タイプをもつ前記ボディの第2の領域との間に形成された第1の接合領域と、前記ボディの前記第2の領域と前記第1のドーピング・タイプをもつ前記ボディの第3の領域との間のボディ内部に形成された第2の接合領域とを備える半導体材料のボディを供給するステップと、

前記第1の接合領域に逆バイアスをかけて降伏モードにするステップと、

前記第2の接合領域の少なくとも第1の部分に順バイアスをかけるステップと、

前記逆バイアスがかけられた第1の接合領域に関連する第1の空乏領域に、前記ボディの前記第2の領域を前記第2の接合領域の少なくとも一部のエネルギー障壁を低くするために、前記第2の接合領域の前記少なくとも第1の部分と関連する第2の空乏領域へとパンチスルーさせるとともに、キャリアを前記第2の接合領域の少なくとも第1の部分から第1の空乏領域へと注入させ、これによりデバイスにおけるエレクトロルミネセンス効果を向上させるステップと

を含む方法。

- 前記第2の接合領域には逆バイアスがかけられ、前記パンチスルーさせた第1の空乏領域によって、前記第2の接合領域の前記第1の部分に順バイアスがかけられる、請求項12に記載の方法。

- 前記半導体材料が単結晶間接遷移型半導体材料である、請求項12または13に記載の方法。

- 前記半導体材料が直接遷移型半導体材料である、請求項13または14に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| ZA200800593 | 2008-01-21 | ||

| ZA2008/00593 | 2008-01-21 | ||

| PCT/IB2009/050209 WO2009093177A1 (en) | 2008-01-21 | 2009-01-21 | Semiconductor light emitting device utilising punch-through effects |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011510511A JP2011510511A (ja) | 2011-03-31 |

| JP2011510511A5 JP2011510511A5 (ja) | 2011-05-12 |

| JP5676273B2 true JP5676273B2 (ja) | 2015-02-25 |

Family

ID=40586889

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010543598A Expired - Fee Related JP5676273B2 (ja) | 2008-01-21 | 2009-01-21 | パンチスルー効果を利用した半導体発光デバイス |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8759845B2 (ja) |

| EP (1) | EP2245676A1 (ja) |

| JP (1) | JP5676273B2 (ja) |

| WO (1) | WO2009093177A1 (ja) |

| ZA (1) | ZA201004753B (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8729582B2 (en) * | 2007-11-01 | 2014-05-20 | Insiava (Pty) Limited | Optoelectronic device with light directing arrangement and method of forming the arrangement |

| JP5676273B2 (ja) | 2008-01-21 | 2015-02-25 | インシアヴァ (ピーテーワイ) リミテッド | パンチスルー効果を利用した半導体発光デバイス |

| ATE523900T1 (de) * | 2008-02-01 | 2011-09-15 | Insiava Pty Ltd | Lichtemittierendes halbleiterbauelement mit heteroübergängen |

| CN102292834A (zh) | 2008-12-15 | 2011-12-21 | 因西亚瓦(控股)有限公司 | 利用穿通效应的硅发光器件 |

| JP6008742B2 (ja) | 2010-01-22 | 2016-10-19 | インシアヴァ (ピーテーワイ) リミテッド | シリコン発光デバイス及び該デバイスを製造する方法 |

| JP5665504B2 (ja) * | 2010-11-24 | 2015-02-04 | キヤノン株式会社 | 垂直共振器型面発光レーザおよび垂直共振器型面発光レーザアレイ |

| EP2756527B1 (en) | 2011-09-16 | 2015-11-18 | Insiava (Pty) Limited | Near infrared light source in bulk silicon |

| WO2018049434A2 (en) | 2016-09-06 | 2018-03-15 | University Of South Africa | Optimised 650 nm silicon avalanche led |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60167390A (ja) | 1984-02-09 | 1985-08-30 | Matsushita Electric Ind Co Ltd | 半導体発光素子 |

| JPS63181486A (ja) | 1987-01-23 | 1988-07-26 | Hiroshima Univ | 半導体発光装置 |

| US5136353A (en) * | 1990-05-10 | 1992-08-04 | The University Of Colorado Foundation, Inc. | Optical switch |

| US5510627A (en) * | 1994-06-29 | 1996-04-23 | The United States Of America As Represented By The Secretary Of The Navy | Infrared-to-visible converter |

| US5994720A (en) | 1996-03-04 | 1999-11-30 | University Of Pretoria | Indirect bandgap semiconductor optoelectronic device |

| US6111271A (en) * | 1996-03-28 | 2000-08-29 | University Of Pretoria | Optoelectronic device with separately controllable carrier injection means |

| JP4024431B2 (ja) * | 1999-07-23 | 2007-12-19 | 株式会社東芝 | 双方向半導体発光素子及び光伝送装置 |

| JP2002246639A (ja) * | 2001-02-20 | 2002-08-30 | Fujitsu Ltd | 半導体発光装置 |

| EP1656701A4 (en) * | 2003-08-22 | 2007-10-10 | Univ Illinois | SEMICONDUCTOR DEVICE AND ASSOCIATED METHOD |

| CN101855736B (zh) | 2007-10-08 | 2011-12-21 | 因西亚瓦(控股)有限公司 | 具有载流子注入的硅发光器件 |

| US8729582B2 (en) | 2007-11-01 | 2014-05-20 | Insiava (Pty) Limited | Optoelectronic device with light directing arrangement and method of forming the arrangement |

| JP5676273B2 (ja) | 2008-01-21 | 2015-02-25 | インシアヴァ (ピーテーワイ) リミテッド | パンチスルー効果を利用した半導体発光デバイス |

| ATE523900T1 (de) | 2008-02-01 | 2011-09-15 | Insiava Pty Ltd | Lichtemittierendes halbleiterbauelement mit heteroübergängen |

| CN102292834A (zh) | 2008-12-15 | 2011-12-21 | 因西亚瓦(控股)有限公司 | 利用穿通效应的硅发光器件 |

| US8395226B2 (en) | 2009-01-27 | 2013-03-12 | Insiava (Pty) Limited | Microchip-based MOEMS and waveguide device |

| JP6008742B2 (ja) | 2010-01-22 | 2016-10-19 | インシアヴァ (ピーテーワイ) リミテッド | シリコン発光デバイス及び該デバイスを製造する方法 |

-

2009

- 2009-01-21 JP JP2010543598A patent/JP5676273B2/ja not_active Expired - Fee Related

- 2009-01-21 EP EP09703175A patent/EP2245676A1/en not_active Ceased

- 2009-01-21 US US12/863,743 patent/US8759845B2/en not_active Expired - Fee Related

- 2009-01-21 WO PCT/IB2009/050209 patent/WO2009093177A1/en active Application Filing

-

2010

- 2010-07-06 ZA ZA2010/04753A patent/ZA201004753B/en unknown

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011510511A (ja) | 2011-03-31 |

| EP2245676A1 (en) | 2010-11-03 |

| ZA201004753B (en) | 2011-08-31 |

| WO2009093177A1 (en) | 2009-07-30 |

| US20110031893A1 (en) | 2011-02-10 |

| US8759845B2 (en) | 2014-06-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5676273B2 (ja) | パンチスルー効果を利用した半導体発光デバイス | |

| KR102357920B1 (ko) | 전계 효과에 의해 도펀트들을 이온화하기 위한 p-n 접합 광전 소자 | |

| US9306113B2 (en) | Silicon light emitting device utilising reach-through effects | |

| US8362679B2 (en) | Silicon light emitting device with carrier injection | |

| US20140225059A1 (en) | LED with Improved Injection Efficiency | |

| US8674382B2 (en) | Semiconductor light emitting device comprising heterojunction | |

| TW200618430A (en) | Semiconductor heterostructure | |

| EP2919282B1 (en) | Nitride semiconductor stacked body and semiconductor light emitting device comprising the same | |

| CN112466954B (zh) | 一种半导体器件及其制造方法 | |

| US11631780B2 (en) | Light-emitting metal-oxide-semiconductor devices and associated systems, devices, and methods | |

| CN108701729A (zh) | 包括钉扎光电二极管结构的半导体装置 | |

| Ali et al. | Design Analysis of Linear Graded Quantum barriers in Ultavoilet-C Laser Diodes | |

| JP2015163693A (ja) | 発光材料、発光材料の製造方法、発光素子、及び発光デバイス | |

| WO2009093170A1 (en) | Silicon light emitting device utilising reach-through effects | |

| Kim et al. | P–N Junction Diode: I–V Behavior and Applications | |

| WO2009150628A1 (en) | Silicon light emitting device utilizing radiative carrier recombination in oxide |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111208 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20120710 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130306 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130402 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130702 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130709 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131002 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140304 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140603 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141202 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141225 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5676273 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |