JP5636720B2 - Semiconductor device manufacturing method and joining jig - Google Patents

Semiconductor device manufacturing method and joining jig Download PDFInfo

- Publication number

- JP5636720B2 JP5636720B2 JP2010085210A JP2010085210A JP5636720B2 JP 5636720 B2 JP5636720 B2 JP 5636720B2 JP 2010085210 A JP2010085210 A JP 2010085210A JP 2010085210 A JP2010085210 A JP 2010085210A JP 5636720 B2 JP5636720 B2 JP 5636720B2

- Authority

- JP

- Japan

- Prior art keywords

- bonding material

- semiconductor element

- opening

- bonding

- thickness

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8338—Bonding interfaces outside the semiconductor or solid-state body

- H01L2224/83385—Shape, e.g. interlocking features

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/838—Bonding techniques

- H01L2224/8384—Sintering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Die Bonding (AREA)

Description

この発明は、パワーモジュールなどの半導体装置の製造方法およびそれに用いられる治具に関するものである。 The present invention relates to a method of manufacturing a semiconductor device such as a power module and a jig used therefor.

近年、電子モジュールに対する信頼性の要求は益々高まり、とくに熱膨張係数差の大きい半導体素子と基板との接合部に対する耐ヒートサイクル特性の向上が強く求められている。また、次世代省エネルギーデバイスや高性能デバイスの実現も要請されており、とくにシリコンと比較して高温動作が可能なSiCデバイスの開発が活発になっている。そのため、確保すべきヒートサイクルの温度範囲の拡大、および確保すべき熱伝導性と高耐熱性の確保に優れた接合部の開発が熱望されている。 In recent years, there has been an increasing demand for reliability of electronic modules, and in particular, there has been a strong demand for improvement in heat cycle resistance of a junction between a semiconductor element having a large difference in thermal expansion coefficient and a substrate. In addition, the realization of next-generation energy-saving devices and high-performance devices is also demanded, and development of SiC devices capable of operating at a higher temperature than silicon is particularly active. Therefore, there is an eager desire to expand the temperature range of the heat cycle to be ensured and to develop a joint excellent in ensuring heat conductivity and high heat resistance to be ensured.

このような要求に対して、粒径が1nm〜20nmの極めて微細な金属微粒子を含むペーストを200℃〜400℃の比較的低温の接合温度で加圧接合することにより、その金属微粒子の融点(700℃以上)まで加熱しなくても金属微粒子が互いに結合することを応用した半導体装置の製造方法が開示されている(例えば、特許文献1参照)。このような金属微粒子を用いた加圧接合による半導体装置の製造方法においては、加圧接合時に余分な金属微粒子を含むペーストの一部が、半導体素子の外側にはみ出して、各部の配線部等に付着してショートする場合がある。このような問題を解決するために、接合材にはんだを用いる場合に、余剰はんだ吸収手段として溝を設け、この溝に余剰なはんだが流れ込むようにした半導体装置の製造方法が開示されている(例えば、特許文献2参照)。 In response to such a demand, a paste containing extremely fine metal fine particles having a particle diameter of 1 nm to 20 nm is subjected to pressure bonding at a relatively low bonding temperature of 200 ° C. to 400 ° C., whereby the melting point of the metal fine particles ( A manufacturing method of a semiconductor device is disclosed that applies that metal fine particles are bonded to each other without heating to 700 ° C. or higher (see, for example, Patent Document 1). In such a method of manufacturing a semiconductor device by pressure bonding using fine metal particles, a part of the paste containing excessive metal fine particles protrudes outside the semiconductor element during pressure bonding, and enters the wiring portion of each part. It may adhere and short circuit. In order to solve such a problem, a method of manufacturing a semiconductor device is disclosed in which, when solder is used as a bonding material, a groove is provided as excess solder absorbing means, and excess solder flows into the groove ( For example, see Patent Document 2).

従来の溝構造の余剰はんだ吸収手段は、接合材の全てが溶融して基板との濡れ性が高いはんだに対しては、余剰はんだを吸収する効果を奏する。しかしながら、加圧接合工程においてほとんど溶融せず、基板との濡れ性も低い金属粒子を含むペーストに対しては、余剰のペーストを吸収する効果は低く、半導体素子の横にはみ出た状態となる。このような状態となった金属粒子を含むペーストは、加圧接合工程において焼結反応を生じると、収縮割れが発生する場合がある。このような収縮割れが生じた半導体装置においては、ヒートサイクル試験において、この収縮割れを起点として基板と半導体素子との間の接合材に亀裂が発生し、耐ヒートサイクル特性が著しく低下するという問題があった。 The surplus solder absorbing means of the conventional groove structure has an effect of absorbing surplus solder with respect to the solder where all of the bonding material is melted and has high wettability with the substrate. However, the paste containing metal particles that are hardly melted in the pressure bonding process and have low wettability with the substrate has a low effect of absorbing the excess paste, and protrudes to the side of the semiconductor element. When the paste containing the metal particles in such a state undergoes a sintering reaction in the pressure bonding process, shrinkage cracking may occur. In a semiconductor device in which such shrinkage cracking has occurred, in the heat cycle test, cracks occur in the bonding material between the substrate and the semiconductor element starting from this shrinkage cracking, and the heat cycle resistance is significantly reduced. was there.

この発明は上述のような課題を解決するためになされたもので、金属粒子を含有した接合材で半導体素子と基板とを加圧接合するときに、はみ出した接合材の収縮割れを抑制し、耐ヒートサイクル特性に優れた半導体装置の製造方法を提供するものである。 This invention was made in order to solve the above-described problems, and when the semiconductor element and the substrate are pressure bonded with a bonding material containing metal particles, the shrinkage cracking of the protruding bonding material is suppressed, A method for manufacturing a semiconductor device having excellent heat cycle resistance is provided.

この発明に係る半導体装置の製造方法は、半導体素子が緩挿可能な開口部と、この開口部の開口縁に開口部の開口断面積より大きい開口断面積を有する接合材逃がし部とを有する接合治具を用いる半導体装置の製造方法であって、基板と半導体素子との間に金属粒子を含有した接合材を狭持する工程と、半導体素子が開口部に緩挿されるように接合治具を配置する工程と、接合治具を介して半導体素子と基板との間を200℃以上500℃以下の温度環境下において加圧する工程とを備えたものである。 A manufacturing method of a semiconductor device according to the present invention includes an opening having an opening in which a semiconductor element can be loosely inserted, and a bonding material relief portion having an opening cross-sectional area larger than the opening cross-sectional area of the opening at the opening edge of the opening. A method of manufacturing a semiconductor device using a jig, the step of sandwiching a bonding material containing metal particles between a substrate and a semiconductor element, and a bonding jig so that the semiconductor element is loosely inserted into the opening. And a step of applying pressure between the semiconductor element and the substrate through a bonding jig in a temperature environment of 200 ° C. or higher and 500 ° C. or lower.

この発明は、半導体素子が緩挿可能な開口部と、この開口部の開口縁に開口部の開口断面積より大きい開口断面積を有する接合材逃がし部とを有する接合治具を用いて、金属粒子を含有した接合材で半導体素子と基板とを加圧接合しているので、半導体素子からはみ出ている接合材の厚さを、半導体素子と基板とに狭持された部分の接合材の厚さより小さくすることができる。その結果、はみ出した接合材の収縮割れを抑制し、耐ヒートサイクル特性に優れた半導体装置の製造方法を提供することができる。 The present invention uses a joining jig having an opening part into which a semiconductor element can be loosely inserted and a joining material relief part having an opening cross-sectional area larger than the opening cross-sectional area of the opening part at the opening edge of the opening part. Since the semiconductor element and the substrate are pressure-bonded with a bonding material containing particles, the thickness of the bonding material protruding from the semiconductor element is set to the thickness of the bonding material in the portion sandwiched between the semiconductor element and the substrate. It can be made smaller. As a result, it is possible to provide a method for manufacturing a semiconductor device that suppresses shrinkage cracking of the protruding bonding material and has excellent heat cycle resistance.

実施の形態1.

図1は、この発明を実施するための実施の形態1における、半導体装置の製造方法の工程を説明する工程図である。半導体素子1として、Siチップを用意する。このSiチップは、次のようにして作製する。φ5インチで厚さ500μmのSiウェハを用意し、裏面(鏡面研磨されていない面)に、例えばスパッタリング法を用いて、Siウェハ側から順にTi層を約100nm厚、Ni層を約300nm厚およびAu層を約50nm厚で成膜する。この金属膜が成膜されたSiウェハを縦横7mmの正方形に切断して本実施の形態のSiチップとした。

FIG. 1 is a process diagram for explaining a process of a semiconductor device manufacturing method according to the first embodiment for carrying out the present invention. A Si chip is prepared as the

次に、基板2として、Cuブロックを用意する。このCuブロックは次のようにして作製する。縦横10mmで厚さ1mmの無酸素銅板の一方の面に、電解めっきを用いて、厚さ約4μmのNiめっき層を形成してCuブロックとした。

Next, a Cu block is prepared as the

図1(a)に示すように、基板2の表面に金属粒子含有ペーストを用いて、スクリーン印刷で接合材3を形成する。金属粒子含有ペーストとしては、例えばクックソンエレクトロニクス社製の焼結タイプのAgナノペースト(クックソンエレクトロニクス社製:SP2000)を用いることができる。このペーストは、電子顕微鏡観察結果からは平均粒径が30nmのAg微粒子を主成分とするもので、このようなサイズのAg微粒子は200℃〜500℃の範囲で焼結するものである。スクリーン印刷に用いた印刷マスクはステンレスメッシュ製で乳剤の厚さが100μm、印刷パターンの開口は縦横8mmのものを用いた。印刷後の接合材3の形状は、縦横8mmの正方形で厚さは約0.1mmである。

As shown in FIG. 1A, a

次に、図1(b)に示すように、接合材3の上に中心を合わせて半導体素子1を載置し、さらに半導体素子1の上からステンレス製の治具4を配置する。治具4の形状などについては後述する。次に、図1(c)に示すように、例えば、アスリートFA(株)社製の加圧と加熱を同時に行なう接合装置(CB505)を用いて、温度350℃、加圧圧力10MPaの条件で半導体素子1と基板2とを接合した。20分間加圧と加熱とを継続後、加圧と加熱とを停止して空冷によって冷却し、図1(d)に示したような、半導体装置5を完成した。

Next, as shown in FIG. 1B, the

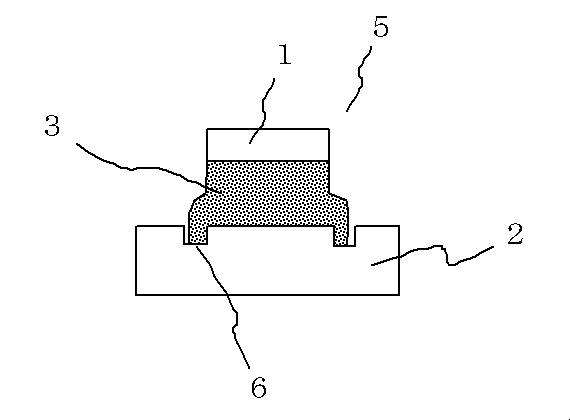

図2は、本実施の形態に用いた治具4を示す模式図である。図2において、治具4の中央部には、半導体素子が緩挿可能な開口部6が形成されている。また、この開口部6の開口縁には、開口部の開口断面積より大きい開口断面積を有する接合材逃がし部7が形成されている。開口部6の開口断面は、半導体素子(縦横7mm)よりも少し大きい縦横(x)7.2mmであり、接合材逃がし部7の開口断面は、縦横(y)9mmである。開口部6の高さ(h)は、560μmであり、接合材逃がし部7の高さ(a)は、30μmである。なお、開口部6の高さ(h)は、接合材逃がし部7の高さ(a)を含んでいる。

FIG. 2 is a schematic diagram showing the jig 4 used in the present embodiment. In FIG. 2, an

このような治具を用いて半導体装置を作製した場合、治具が半導体素子横にはみ出たペーストを押し下げて半導体素子から遠い位置に押し出す作用により、半導体素子と基板とに狭持された接合材の外側にはみ出している接合材の高さを抑制することができる。その結果、図1(d)に示したように、半導体素子からはみ出ている接合材の厚さ(d)を、半導体素子と基板とに狭持された部分の接合材の厚さ(t)より小さくすることができる。その結果、はみ出した接合材の収縮割れを抑制し、耐ヒートサイクル特性に優れた半導体装置の製造方法を提供することができる。 When a semiconductor device is manufactured using such a jig, the bonding material sandwiched between the semiconductor element and the substrate by the jig pushing down the paste protruding from the side of the semiconductor element and pushing it away from the semiconductor element. It is possible to suppress the height of the bonding material that protrudes to the outside. As a result, as shown in FIG. 1D, the thickness (d) of the bonding material protruding from the semiconductor element is set to the thickness (t) of the bonding material in the portion sandwiched between the semiconductor element and the substrate. It can be made smaller. As a result, it is possible to provide a method for manufacturing a semiconductor device that suppresses shrinkage cracking of the protruding bonding material and has excellent heat cycle resistance.

半導体素子からはみ出ている接合材の厚さを、半導体素子と基板とに狭持された部分の接合材の厚さより小さくすることによって、はみ出した接合材の収縮割れを抑制でき、耐ヒートサイクル特性が向上する理由は、次のように考えられる。 By making the thickness of the bonding material protruding from the semiconductor element smaller than the thickness of the bonding material sandwiched between the semiconductor element and the substrate, shrinkage cracking of the protruding bonding material can be suppressed, and heat cycle resistance The reason for the improvement is considered as follows.

焼結タイプのAgナノペーストは、一般に保護膜で覆われたAg微粒子と、分散剤と、溶剤とからなり、加熱により溶剤、分散剤、保護膜が蒸発、分解することによって、Ag微粒子の清浄面が露出し、これらAg微粒子の清浄な清浄面同士や、半導体素子および基板表面に成膜されたAu、Ag、Cuなどの清浄な表面とを加圧により接触させ、熱拡散させることにより、焼結、接合される。10nm以下の粒径の小さいAg微粒子は、溶融するとも考えられている。 Sintered Ag nanopaste is generally composed of Ag fine particles covered with a protective film, a dispersant, and a solvent. The solvent, dispersant, and protective film are evaporated and decomposed by heating, so that the Ag fine particles are cleaned. The surfaces are exposed, and the clean surfaces of these Ag fine particles and the clean surfaces of Au, Ag, Cu, etc. formed on the semiconductor element and the substrate surface are brought into contact by pressure and thermally diffused, Sintered and joined. Ag fine particles having a particle diameter of 10 nm or less are considered to melt.

この際、ペーストから蒸発、分解する溶剤、分散剤の量は非常に多く、焼結により体積比で、印刷時と比較して1/2〜1/4も収縮する。しかし、半導体素子や基板表面のAu、Ag、Cuなどを接合された部分は、収縮することができず、厚さ方向のAg微粒子のみで構成される部分が主に収縮する。しかし、半導体素子からはみ出た部分は、基板と接合されている(拘束されている)が、半導体素子からはみ出た部分はAg微粒子表面が拘束されていないために、大きく収縮して割れる。本実施の形態の治具を用いて加圧することにより、半導体素子と接合された部分同様に加圧され、収縮と合わせてAgペーストを加圧しつづけられるため、焼結収縮割れを著しく低減することができる。 At this time, the amount of solvent and dispersant that evaporates and decomposes from the paste is very large, and the volume ratio is reduced by sintering by 1/2 to 1/4 as compared with printing. However, the portion of the semiconductor element or the substrate surface where Au, Ag, Cu, or the like is bonded cannot be shrunk, and the portion composed only of Ag fine particles in the thickness direction mainly shrinks. However, the portion that protrudes from the semiconductor element is bonded (restrained) to the substrate, but the portion that protrudes from the semiconductor element is cracked due to large shrinkage because the Ag fine particle surface is not constrained. By applying pressure using the jig of the present embodiment, pressure is applied in the same manner as the portion joined to the semiconductor element, and the Ag paste is continuously pressed together with the shrinkage, so that the sintering shrinkage crack is significantly reduced. Can do.

また、半導体素子とAg微粒子との接合界面は、熱膨張係数差が大きく、熱応力が最もかかりやすい部分であり、半導体素子と基板とをAgペーストで接合した場合、ヒートサイクルによるクラックが最も発生しやすい部分である。このため、半導体素子横の大きなクラックは、ヒートサイクルによるクラック発生を助長することが懸念される。本実施の形態の治具を用いて加圧することによる焼結割れ抑制は、耐ヒートサイクル性を著しく向上させる。 Also, the bonding interface between the semiconductor element and the Ag fine particle has a large difference in coefficient of thermal expansion and is the portion where the thermal stress is most easily applied. When the semiconductor element and the substrate are bonded with Ag paste, cracks due to heat cycles are most generated. It is a part that is easy to do. For this reason, there is a concern that a large crack beside the semiconductor element promotes the generation of cracks due to heat cycles. Sintering crack suppression by applying pressure using the jig of the present embodiment significantly improves heat cycle resistance.

なお、本実施の形態においては、金属粒子を含有する接合材の材料として、焼結タイプのAgナノペーストを用いたが、加圧接合時の温度条件である200℃〜500℃の範囲で焼結する金属粒子を用いることができ、平均粒径が30nmのAg微粒子以外に、平均粒径が2nm〜500nmの範囲で、所定比率で混合させたものや、例えば平均粒径が2nm〜500nmのCu微粒子、Ni微粒子などを主成分とするナノペーストを用いることができる。加圧接合時の温度が、200℃より低い場合は、ボイドが多くなるという不具合があり、500℃より高い場合は、被接合部材が酸化や熱劣化するという不具合がある。 In this embodiment, a sintered type Ag nanopaste is used as a material for the bonding material containing metal particles. However, the sintering is performed in a temperature range of 200 ° C. to 500 ° C., which is a temperature condition during pressure bonding. In addition to the Ag fine particles having an average particle size of 30 nm, those mixed at a predetermined ratio in the range of 2 nm to 500 nm, for example, the average particle size of 2 nm to 500 nm A nanopaste mainly composed of Cu fine particles, Ni fine particles and the like can be used. When the temperature during pressure bonding is lower than 200 ° C., there is a problem that the number of voids increases. When the temperature is higher than 500 ° C., there is a problem that the member to be bonded is oxidized or thermally deteriorated.

また、本実施の形態において、治具の材料としてステンレスを用いたが、加圧接合時の温度条件である200℃〜500℃の範囲で、接合材の金属粒子と反応せず安定な材料であれば用いることができ、例えばアルミニウム、銅、ジルコニア、アルミナなどのセラミックや、炭素などの材料を用いることができる。さらに、治具と接合材とが接触する開口部や接合材逃がし部の内壁に、接合材との離型性を容易にするように、離型剤として、Niめっきやジルコニア粉末、カーボンなどを塗布してもよい。 In this embodiment, stainless steel is used as the material of the jig, but it is a stable material that does not react with the metal particles of the bonding material in the range of 200 ° C. to 500 ° C., which is the temperature condition during pressure bonding. For example, a ceramic such as aluminum, copper, zirconia, or alumina, or a material such as carbon can be used. Furthermore, Ni plating, zirconia powder, carbon, etc. are used as a release agent on the inner wall of the opening where the jig and the bonding material are in contact and the inner wall of the bonding material relief part, in order to facilitate releasability from the bonding material. It may be applied.

実施の形態2.

実施の形態2においては、実施の形態1で用いた治具の形状を変化させた場合に、製造される半導体装置の特性の変化を調べたものである。半導体素子の形状は、実施の形態1と同様に、縦横7mmの正方形で厚さ500μmである。

In the second embodiment, the change in characteristics of the manufactured semiconductor device is examined when the shape of the jig used in the first embodiment is changed. As in the first embodiment, the shape of the semiconductor element is a square of 7 mm in length and width and 500 μm in thickness.

表1は、本実施の形態における治具の各部のサイズに対する、完成した半導体装置における接合材のはみ出し率および製造工程終了後の収縮割れの有無を示したものである。ここで、x、y、aおよびhは、それぞれ実施の形態1の図1に示したように、xは開口部の開口断面の縦横、yは接合材逃がし部の開口断面の縦横、aは接合材逃がし部の高さ、およびhは開口部の高さである。 Table 1 shows the protruding rate of the bonding material in the completed semiconductor device and the presence or absence of shrinkage cracks after the manufacturing process with respect to the size of each part of the jig in the present embodiment. Here, x, y, a, and h are respectively the vertical and horizontal dimensions of the opening cross section of the opening, y is the vertical and horizontal dimensions of the opening section of the bonding material escape portion, and a is as shown in FIG. The height of the bonding material escape portion, and h is the height of the opening.

ここで、はみ出し率は、図1(d)に示したように、半導体素子からはみ出ている接合材の厚さ(d)と導体素子と基板とに狭持された部分の接合材の厚さ(t)との比として定義し、はみ出し率(%)=(d/t)×100とした。これらの接合材の厚さ(d、t)は、レーザー変位計で形状測定した図から等間隔でd、tを5点平均で算出した。収縮割れの有無に関しては、半導体素子からはみ出ている接合材の表面を光学顕微鏡を用いて100倍の倍率で観察し、2mm以上の長さの亀裂が観測された場合を×、そうでない場合を○として判定した。なお、表1には、比較として開口部の開口断面が大きすぎるもの(比較例1)、開口部および接合材逃がし部がないもの(比較例2)も合わせて示している。 Here, as shown in FIG. 1 (d), the protrusion ratio is the thickness (d) of the bonding material protruding from the semiconductor element and the thickness of the bonding material sandwiched between the conductor element and the substrate. The ratio was defined as the ratio to (t), and the protrusion rate (%) = (d / t) × 100. The thicknesses (d, t) of these bonding materials were calculated by averaging five points at d and t at equal intervals from the figure of the shape measured with a laser displacement meter. Regarding the presence or absence of shrinkage cracks, the surface of the bonding material protruding from the semiconductor element is observed at a magnification of 100 times using an optical microscope, and when cracks of 2 mm or longer are observed, × Judged as ○. Table 1 also shows a comparative example in which the opening cross-section of the opening is too large (Comparative Example 1) and that does not have the opening and the bonding material escape part (Comparative Example 2).

表1において、まず比較例2は治具が単なる直方体であり、半導体素子を単に上から平面で加圧接合しているだけである。この場合、金属粒子を含んだ接合材は半導体素子の側面に盛り上がった状態となり、はみ出し率が100%を越えた状態、つまり半導体素子からはみ出ている接合材の厚さ(d)が半導体素子と基板とに狭持された部分の接合材の厚さ(t)より大きくなる。このような状態になると、はみ出たAgペースト量が過多となって収縮割れが発生する。 In Table 1, first, in Comparative Example 2, the jig is a simple rectangular parallelepiped, and the semiconductor element is simply press-bonded in a plane from above. In this case, the bonding material including the metal particles is raised on the side surface of the semiconductor element, and the protruding rate exceeds 100%, that is, the thickness (d) of the bonding material protruding from the semiconductor element is the same as that of the semiconductor element. It becomes larger than the thickness (t) of the bonding material in the portion sandwiched between the substrates. In such a state, the amount of protruding Ag paste becomes excessive and shrinkage cracking occurs.

また、表1の比較例1においては、開口部の開口断面の縦横(x)が10mmと、半導体素子の縦横の7mmよりも両サイドが1.5mmずつ大きい。このようなサイズの関係では、開口部に半導体素子は緩挿されているとはいえない。また、接合材逃がし部の開口断面の縦横(y)も12mmと大きいため、このような治具で加圧接合した場合、半導体素子の周辺部にはみ出した接合材は、接合材逃がし部および開口部の内壁と半導体素子との間が広いため、接合材は半導体素子の側面に盛り上がった状態となり、はみ出し率が100%を越えてしまう。その結果、収縮割れが発生し、比較例2と同様に、耐ヒートサイクル特性が低下する。 Further, in Comparative Example 1 of Table 1, the vertical and horizontal (x) of the opening cross section of the opening is 10 mm, and both sides are larger by 1.5 mm than the vertical and horizontal 7 mm of the semiconductor element. With such a size relationship, it cannot be said that the semiconductor element is loosely inserted into the opening. In addition, since the vertical and horizontal dimensions (y) of the opening cross section of the bonding material relief portion are as large as 12 mm, when pressure bonding is performed with such a jig, the bonding material that protrudes to the periphery of the semiconductor element is the bonding material relief portion and the opening. Since the space between the inner wall of the part and the semiconductor element is wide, the bonding material is raised on the side surface of the semiconductor element, and the protrusion rate exceeds 100%. As a result, shrinkage cracks are generated, and the heat cycle resistance is reduced as in Comparative Example 2.

一方、実施例1〜6においては、はみ出し率が100%以下であるため、収縮割れが発生せず、耐ヒートサイクル特性に優れた半導体装置が得られる。 On the other hand, in Examples 1-6, since a protrusion rate is 100% or less, a shrinkage crack does not generate | occur | produce and the semiconductor device excellent in the heat cycle-proof characteristic is obtained.

実施の形態3.

実施の形態3においては、実施の形態1の半導体装置の製造方法において、基板に溝構造の余剰接合材吸収部を備えたものである。

In the third embodiment, in the method of manufacturing the semiconductor device of the first embodiment, the substrate is provided with an excess bonding material absorbing portion having a groove structure.

図3は、本実施の形態における半導体装置の模式図である。本実施の形態においては、基板2の表面の半導体素子1が接合材3を介して接合される領域の外周部に、溝状の余剰接合材吸収部6を備えたものである。それ以外は実施の形態1と同様な方法で、半導体装置が製造される。

FIG. 3 is a schematic diagram of the semiconductor device in this embodiment. In the present embodiment, a groove-like surplus bonding

このような基板2の接合領域の外周部に溝を備えたことにより、半導体素子の外周部にはみ出した接合材は、接合材3が治具で加圧接合される際に基板2の方向に押し出され、余剰接合材吸収部6の溝に押し込まれる。その結果、余剰な接合材の量が多い場合でも、確実に半導体素子からはみ出ている接合材の厚さが半導体素子と基板とに狭持された部分の接合材の厚さより薄くなる。その結果、実施の形態1と同様に、はみ出した接合材の収縮割れを抑制し、耐ヒートサイクル特性に優れた半導体装置の製造方法を提供することができる。溝状の余剰接合材吸収部を備えた基板に対して、単に平板の治具で加圧接合をしただけでは、接合材は溶剤が多く、これが溝に大量に入ってしまうため、簡単に溝に入らない。しかしながら、本実施の形態のような開口部および接合材逃がし部を備えた治具を用いることにより、

接合材は、余剰接合材吸収溝内で、接合材逃がし穴7を境界面として下向きから上向きに流動し、はみ出した接合材は確実に溝状の余剰接合材吸収部に吸収される。

By providing a groove in the outer peripheral portion of the bonding region of the

The joining material flows from the downward direction to the upward direction in the surplus joining material absorption groove with the joining material escape hole 7 as a boundary surface, and the protruding joining material is reliably absorbed by the groove-like surplus joining material absorbing portion.

また、余剰な接合材が余剰接合材吸収部である溝より外側にはみ出すことを抑制できるので、はみ出した接合材が横方向に広がることを防ぐことができ、各部の配線部等に付着

してショートする不具合を防ぐ効果もある。

Moreover, since it can suppress that an excess joining material protrudes outside the groove | channel which is an excess joining material absorption part, it can prevent the joining material which protruded spreading to a horizontal direction, and adheres to the wiring part etc. of each part. It also has the effect of preventing short circuit failures.

1 半導体素子

2 基板

3 接合材

4 治具

5 半導体装置

6 余剰接合材吸収部

DESCRIPTION OF

Claims (7)

この開口部の開口縁に前記開口部の開口断面積より大きい開口断面積を有する接合材逃がし部とを有する接合治具を用いる半導体装置の製造方法であって、

基板と前記半導体素子との間に、200℃以上500℃以下の範囲で焼結する金属粒子を含有した焼結タイプの接合材を狭持する工程と、

前記半導体素子が前記開口部に緩挿されるように前記接合治具を配置する工程と、

前記接合治具を介して前記半導体素子と前記基板との間を200℃以上500℃以下の温度環境下において加圧する工程とを備え、

前記加圧工程は、前記接合材逃がし部によって前記半導体素子横にはみ出た接合材を押し下げて前記半導体素子から遠い位置に押し出し、前記半導体素子からはみ出ている接合材の厚さを前記半導体素子と前記基板とに狭持された部分の接合材の厚さより小さくすることにより、段形状の接合材を形成する工程を有することを特徴とする半導体装置の製造方法。 An opening in which a semiconductor element can be loosely inserted;

A manufacturing method of a semiconductor device using a bonding jig having a bonding material relief portion having an opening cross-sectional area larger than an opening cross-sectional area of the opening at an opening edge of the opening,

Between the substrate and the semiconductor element, sandwiching a sintered type bonding material containing metal particles sintered in a range of 200 ° C. or more and 500 ° C. or less ;

Arranging the joining jig so that the semiconductor element is loosely inserted into the opening;

And pressurizing between the semiconductor element and the substrate through the joining jig in a temperature environment of 200 ° C. or more and 500 ° C. or less,

In the pressurizing step, the bonding material protruding from the side of the semiconductor element is pushed down by the bonding material relief portion to be pushed away from the semiconductor element, and the thickness of the bonding material protruding from the semiconductor element is determined with the semiconductor element. A method of manufacturing a semiconductor device, comprising: forming a step- shaped bonding material by making the thickness smaller than a thickness of a bonding material in a portion held between the substrates.

前記金属粒子は、平均粒径が2nm〜500nmのAg、Cu、Niのいずれかを主成分とし、

前記溶剤と分散剤とは、前記加圧工程における加熱温度が200℃〜500℃以下で蒸発、分解する成分であることを特徴とする請求項1〜3いずれか1項記載の半導体装置の製造方法。 The bonding material is a paste material composed of metal particles, a solvent, and a dispersant,

The metal particles are mainly composed of any one of Ag, Cu, and Ni having an average particle diameter of 2 nm to 500 nm,

The said solvent and a dispersing agent are components which evaporate and decompose when the heating temperature in the said pressurization process is 200 to 500 degreeC or less, The manufacturing of the semiconductor device of any one of Claims 1-3 characterized by the above-mentioned. Method.

この開口部の開口縁に前記開口部の開口断面積より大きい開口断面積を有する接合材逃がし部とを有する接合治具であって、

前記開口部の開口断面の幅は、前記半導体素子の幅よりも0.2mm以上1mm以下の範囲で大きく、

前記接合材逃がし部の開口断面の幅は、前記半導体素子の幅よりも2mm以上3mm以下の範囲で大きく、

前記接合材逃がし部の高さは、30μm以上60μm以下の範囲であり、

前記接合材逃がし部によって前記半導体素子横にはみ出た接合材を押し下げて前記半導体素子から遠い位置に押し出し、前記半導体素子からはみ出ている接合材の厚さを前記半導体素子と前記基板とに狭持された部分の接合材の厚さより小さくすることにより、段形状の接合材を形成することを特徴とする接合治具。 An opening in which a semiconductor element can be loosely inserted;

A bonding jig having a bonding material escape portion having an opening cross-sectional area larger than the opening cross-sectional area of the opening at the opening edge of the opening,

The width of the opening cross section of the opening is larger than the width of the semiconductor element in a range of 0.2 mm to 1 mm,

The width of the opening cross section of the bonding material escape portion is larger than the width of the semiconductor element in a range of 2 mm to 3 mm,

The height of the bonding material escaping portion is Ri 60μm following ranges der than 30 [mu] m,

The bonding material protruding from the side of the semiconductor element is pushed down by the bonding material relief portion and pushed out to a position far from the semiconductor element, and the thickness of the bonding material protruding from the semiconductor element is held between the semiconductor element and the substrate. by less than the thickness of the bonding material portion, the joining jig characterized that you form a bonding material stage shape.

前記接合治具と接合材とが接触する開口部や接合材逃がし部の内壁に離型剤としてNiめっきやジルコニア粉末、カーボンのいずれかが塗布していることを特徴とする請求項6に記載の接合治具。 The material of the joining jig is mainly composed of stainless steel or aluminum, copper, zirconia, alumina or other ceramic or carbon,

The plating apparatus according to claim 6, wherein any one of Ni plating, zirconia powder, and carbon is applied as a release agent to an opening portion where the bonding jig and the bonding material are in contact with each other and an inner wall of the bonding material relief portion. Joining jig.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010085210A JP5636720B2 (en) | 2010-04-01 | 2010-04-01 | Semiconductor device manufacturing method and joining jig |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010085210A JP5636720B2 (en) | 2010-04-01 | 2010-04-01 | Semiconductor device manufacturing method and joining jig |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011216772A JP2011216772A (en) | 2011-10-27 |

| JP5636720B2 true JP5636720B2 (en) | 2014-12-10 |

Family

ID=44946198

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010085210A Expired - Fee Related JP5636720B2 (en) | 2010-04-01 | 2010-04-01 | Semiconductor device manufacturing method and joining jig |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5636720B2 (en) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5659171B2 (en) * | 2012-02-23 | 2015-01-28 | 株式会社 日立パワーデバイス | Semiconductor device and inverter device using the same |

| JP2014127537A (en) * | 2012-12-26 | 2014-07-07 | Hitachi Power Semiconductor Device Ltd | Semiconductor device using conductive bonding material and method of manufacturing semiconductor device |

| JP6176590B2 (en) * | 2013-10-07 | 2017-08-09 | 日産自動車株式会社 | Semiconductor device manufacturing apparatus and manufacturing method |

| JP6119553B2 (en) * | 2013-10-23 | 2017-04-26 | 三菱電機株式会社 | Power semiconductor device and manufacturing method thereof |

| JP6228490B2 (en) | 2014-03-04 | 2017-11-08 | ローム株式会社 | Semiconductor device and manufacturing method of semiconductor device |

| JP6358423B2 (en) * | 2014-03-24 | 2018-07-18 | 日産自動車株式会社 | Semiconductor mounting method and semiconductor component manufacturing apparatus |

| CN106463415B (en) * | 2015-03-31 | 2019-01-01 | 新电元工业株式会社 | The manufacturing method of conjugant |

| JP6610102B2 (en) * | 2015-09-08 | 2019-11-27 | 株式会社村田製作所 | Semiconductor module |

| JP6726821B2 (en) * | 2017-01-10 | 2020-07-22 | 株式会社デンソー | Method of manufacturing semiconductor device |

| JP7355709B2 (en) * | 2020-05-29 | 2023-10-03 | 株式会社 日立パワーデバイス | Bonding jig and semiconductor device manufacturing method |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07326636A (en) * | 1994-05-31 | 1995-12-12 | Mitsubishi Electric Corp | Method and device for chip bonding |

-

2010

- 2010-04-01 JP JP2010085210A patent/JP5636720B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011216772A (en) | 2011-10-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5636720B2 (en) | Semiconductor device manufacturing method and joining jig | |

| KR102097177B1 (en) | Power module substrate, power module substrate with heat sink, and power module | |

| KR102224535B1 (en) | Method for manufacturing power-module substrate | |

| JP6056432B2 (en) | Power module substrate, power module substrate with heat sink, power module, power module substrate manufacturing method | |

| JP2016208010A (en) | Bonded body, substrate for power module with heat sink, heat sink, method for producing bonded body, method for producing substrate for power module with heat sink, and method for producing heat sink | |

| JP2007110001A (en) | Semiconductor device | |

| US11257735B2 (en) | Heat sink-equipped power module substrate and manufacturing method for heat sink-equipped power module substrate | |

| KR102336484B1 (en) | Assembly, power-module substrate provided with heat sink, heat sink, method for manufacturing assembly, method for manufacturing power-module substrate provided with heat sink, and method for manufacturing heat sink | |

| JP6048541B2 (en) | Power module substrate, power module substrate with heat sink, power module, power module substrate manufacturing method, and copper member bonding paste | |

| JP2013211546A (en) | Ceramic-copper assembly and manufacturing method of the same | |

| JP5642336B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP2021150455A (en) | Temporary fixing method for metal member, manufacturing method for joint, and manufacturing method for insulated circuit board | |

| JP5261263B2 (en) | Brazing material and joining method of brazing material | |

| JP6677886B2 (en) | Semiconductor device | |

| JP3981090B2 (en) | Manufacturing method of electronic device | |

| JP2010165807A (en) | Method of manufacturing insulating circuit board, insulating circuit board, and substrate for power module | |

| JP2014175492A (en) | Metal composite body, circuit board, semiconductor device, and method of manufacturing metal composite body | |

| JP6170045B2 (en) | Bonding substrate and manufacturing method thereof, semiconductor module using bonding substrate, and manufacturing method thereof | |

| JP2008300792A (en) | Semiconductor device, and manufacturing method thereof | |

| JP2006351988A (en) | Ceramic substrate, ceramic circuit board and power control component using same | |

| JP6269116B2 (en) | Metal member with underlayer, insulated circuit board, semiconductor device, insulated circuit board with heat sink, and method for producing metal member with underlayer | |

| JP6213204B2 (en) | Ag base layer forming paste | |

| JP6171912B2 (en) | Ag base layer-attached metal member, insulated circuit board, semiconductor device, heat sink-equipped insulating circuit board, and method for manufacturing Ag base layer-attached metal member | |

| JP7267522B1 (en) | Bonding materials and semiconductor devices | |

| Zheng | Processing and Properties of Die-attachment on Copper Surface by Low-temperature Sintering of Nanosilver Paste |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121019 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130909 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130917 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20140326 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140701 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140820 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20140901 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140924 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141007 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5636720 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |