JP5569321B2 - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP5569321B2 JP5569321B2 JP2010227850A JP2010227850A JP5569321B2 JP 5569321 B2 JP5569321 B2 JP 5569321B2 JP 2010227850 A JP2010227850 A JP 2010227850A JP 2010227850 A JP2010227850 A JP 2010227850A JP 5569321 B2 JP5569321 B2 JP 5569321B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- gan

- type gan

- regrowth

- opening

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Electrodes Of Semiconductors (AREA)

- Junction Field-Effect Transistors (AREA)

Description

しかし、半導体積層体の成膜方法によっては、期待した耐圧性能を得られない場合がある。

水素がp型バリア層に高濃度で滞留すると、マグネシウム(Mg)がアクセプタまたはp型不純物として機能しにくくなり、p型バリア層として期待通りの機能を発揮しなくなる。この結果、(1)耐圧性能が低下し、(2)ピンチオフ特性が劣化する。このような、高濃度の水素のp型バリア層への集積による、耐圧性能およびピンチオフ特性の劣化は、npn構造の帰結といえる。

さらに、ソース電極はp型バリア層に接触することで、この半導体装置のオフ動作のアバランシェ破壊によって生成される正孔を引き抜く。しかし、p型バリア層のアクセプタ濃度が低いとソース電極とp型バリア層との接触抵抗は増大して、円滑に正孔を引き抜くことができない。長期間、正孔が引き抜かれず堆積すると、この正孔の堆積によって耐圧性能が不安定になり耐圧性能が劣化する。

本発明の構成によれば、GaN系積層体のトップ側は、従来表層をなしていたn型コンタクト層を無くして、n−型ドリフト層/p型バリア層、という、np構造にする。すなわちnp構造で終端する。このため、高濃度の水素が終端部におけるpn接合の障壁でp型バリア層内に閉じこめられることがなくなる。この結果、p型バリア層に期待される本来の作用である、耐圧性能、ピンチオフ特性、およびソース電極との協働による正孔の円滑な引き抜き、を確実に得ることができる。

その他、高濃度水素の集積に伴う多くの不都合を除くことができる。

これによってn型コンタクト層を設けることなく簡単な構造により、ソース電極から再成長層のチャネルにいたるアクセス抵抗を低くすることができる。すなわち簡単な構造でオン抵抗を低くすることができる。

水素によって不活性化されるMgの量は減少して、Mgの利用率は向上する。上記の濃度範囲のうち適当なMg濃度を用いて、低いオン抵抗と、高い耐圧性能およびピンチオフ特性とを兼ね備えた半導体装置を得ることができる。

ゲート電極下に絶縁層を配置することで、ゲートに正電圧を印加したときのゲートリーク電流を抑制できるため、大電流動作がしやすくなる。また、しきい値電圧をより正方向にシフトできるため、ノーマリーオフを得やすくなる。

再成長層はアンドープなので、pn接合の障壁は形成されないため、水素は容易に離脱できる。この結果、耐圧性能およびピンチオフ特性を向上させる、本来のp型バリア層の性能を発揮することができる。

ソース電極は、開口部の周囲を覆って大きい面積比率で配置されるので、p型バリア層上を大きな蓋のように被覆する。このため脱水素アニールの妨げになる。また、再成長層上であってゲート電極下に絶縁膜を配置する場合には、脱水素アニールは、その絶縁膜の形成工程よりも前に行うのがよい。

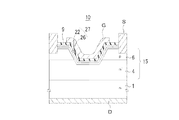

p型GaNバリア層6の表面からn−型GaNドリフト層4に届く開口部28が設けられている。開口部28に露出する上記GaN系半導体層15を覆うように、電子走行層(チャネル層)22および電子供給層(キャリア供給層)26を含む再成長層27が形成されている。再成長層27上には絶縁膜9を介在させてゲート電極Gが配置される。

p型GaNバリア層は、本実施の形態ではp型GaNバリア層6としているが、p型AlGaN層を用いてもよい。積層体15を構成するその他の層についても、場合に応じて、上記に示したGaN層を他のGaN系半導体層としてよい。

GaN系積層体15上にソース電極Sが形成され、このソース電極Sと対面するように、当該ソース電極Sと、n−型GaNドリフト層4等を挟んで、ドレイン電極Dが設けられている。電子走行層(チャネル層)22はアンドープGaN層により、また電子供給層(キャリア供給層)26はアンドープAlGaN層で形成される。電子走行層22と電子供給層26の界面に、二次元電子ガス(2DEG:2 Dimensional Electron Gas)が形成され、この2DEGが、ソース電極Sとドレイン電極Dとの間の縦方向電流のチャネルを構成し、かつ低いオン抵抗を実現する。ソース電極Sは、その側面で再成長層27に接して、p型GaNバリア層6内に延びており、再成長層27およびp型GaNバリア層6の両方に導電接続している。

(a1)耐圧性能の向上

(a2)バンドの正方向へのシフトによるピンチオフ特性の向上

しかし、p型GaNバリア層6については、次の理由によりアクセプタ濃度を十分高くできない。

(b1)p型GaNバリア層6は、チャネルに面しており、アクセプタの混入はチャネル特性の劣化を生じる。すなわちアクセプタが電子走行層22/電子供給層26に混入すると、オン抵抗が増大する。

(b2)p型GaNバリア層6は、直下のn−型GaN系ドリフト層4とpn接合を形成し、チャネルOFF時に、良好な逆方向I(電流)−V(電圧)特性(耐圧性能)を得る。しかし、アクセプタ濃度が高いと、逆方向特性が劣化する。

上記(b1)および(b2)によって、p型GaNバリア層6のアクセプタ濃度を十分高くできない。

従来のnpn構造をもつ半導体装置の場合、アクセプタ濃度を十分高くできないということに加えて、高濃度水素の集積という大きな因子が加わる。半導体装置は、量産段階に入ると、高い成長能率とくに大面積基板への成膜が可能、良好な結晶品質などを得られることから、MOVPE(Metal Organic Vapor Phase Epitaxy)法で成長される。この種の半導体装置が実用レベルに入って量産される場合、上記の理由でほとんど例外なくMOVPE法で成長されることになる。MOVPE法では、トリメチルガリウム(TMG)などの有機金属ガスが、アンモニアおよび水素などに搬送されて成長室に入り、膜を形成する。成膜に寄与した後、多量の水素等は排気されるが、水素はイオン状態ではサイズが小さいため半導体積層構造内に必ず侵入する。従来のnpn構造をもつ半導体装置では、水素は熱履歴を受けても半導体装置から離脱せずに残留する傾向が強かった。とくにGaN系半導体においてnpn構造内のp型層に高濃度の水素の集積が顕著に生じることが、本発明者らによって確認された。本発明者らは、npn構造内のp型GaNバリア層に集積した高濃度の水素は、表面のn+型コンタクト層との間に形成されるpn接合の障壁によって表面側への移動を妨げられる結果と推測している。p型GaNバリア層内に集積した高濃度の水素は、同層内のアクセプタを不活性化させる、すなわちp型不純物として機能させにくくする。このため、上記の(b1)および(b2)の理由によりアクセプタ濃度を十分高くできないことに加えて、高濃度の水素によってアクセプタ濃度がさらに実質的に低下する。

(n+型GaNコンタクト層/p型GaNバリア層内で[H]=2E18cm−3/n−型GaNドリフト層内で[H]=1E16cm−3)

n+型GaNコンタクト層では、p型GaNバリア層との界面における[H]=2E18cm−3から表面側へと急峻に低下して、低下した底で[H]=3E16cm−3程度になる。表面では表面特有の立ち上がりを示すが、これは実質的に問題にならない。問題は、p型GaNバリア層内での[H]=2E18cm−3という異常に高い水素濃度である。

上記の水素濃度は、SIMS(Secondary Ion Mass Spectroscopy)を用いて、n+型コンタクト層が積層された従来の半導体装置の表面から内部へと分析した結果である。従来の半導体装置は、上記のように、図1に示す開口部が設けられた縦型半導体装置に対して、表層にn+型コンタクト層が追加されただけで、他の構成は図1の装置と同じである。

さらに、上記のような高濃度の水素の集積は、上記の他に、半導体装置の作動に対して多くの不都合な影響を及ぼす。たとえば、アクセプタ濃度が低くなると、ソース電極とp型GaNバリア層を接触させて正孔を引き抜くことが、接触抵抗が増大するため円滑に作動しなくなる。すなわち、半導体装置のオフ動作時にp型GaNバリア層とn−型GaNドリフト層とのpn接合でアバランシェ破壊によって生成される正孔は、堆積すると耐圧性能が不安定になる。ソース電極をp型GaNバリア層に低抵抗で接触させると、正孔はソース電極(グランド)へと引き抜くことができる。

その他、高濃度の水素の集積は好ましくない影響を及ぼす。

(a1)耐圧性能の向上

(a2)バンドの正方向へのシフトによるピンチオフ特性の向上

(a3)オフ動作時にp型GaNバリア層とn−型GaNドリフト層とのpn接合でアバランシェ破壊によって生成される正孔を、ソース電極Sと協働して除くことができる。

上記の六角形のハニカム構造は、畝状にして、畝状の開口部を密に配置することでも、上記の面積当たりの開口部周囲長を大きくでき、この結果、電流密度を向上させることができる。

GaN基板1は、いわゆる一体物の厚手のGaN基板でも、または支持基体上のGaN膜でもよい。さらに、GaN系積層体の成長時にGaN基板等の上に形成して、その後の工程で、GaN基板等の所定厚み部分を除いて、製品の状態では薄いGaN層下地のみが残っているものであってもよい。これら、GaN基板、支持基体上にオーミック接触するGaN層を有する基板、製品に薄く残された下地のGaN層などを、単にGaN基板と略称する場合もある。

その薄い下地のGaN層は、導電性でも非導電性でもよく、ドレイン電極は、製造工程および製品の構造によるが、薄いGaN層の表面または裏面に設けることができる。GaN基板または支持基体等が製品に残る場合、当該支持基体または基板は、導電性でも、非導電性でもよい。導電性の場合は、ドレイン電極は、その支持基体または基板の裏面(下)またはおもて面(上)に直接設けることができる。また、非導電性の場合は、非導電性基板の上であって、上記半導体層中の下層側に位置する導電層の上に、ドレイン電極を設けることができる。

上記の層の形成は、MOCVD(有機金属化学気相成長)法を用いるのがよい。MOCVD法で成長することで、結晶性の良好な積層体15を能率良く形成できる。GaN基板1の形成において、導電性基板上に窒化ガリウム膜をMOCVD法によって成長させる場合、ガリウム原料として、トリメチルガリウムを用いる。窒素原料としては高純度アンモニアを用いる。キャリアガスとしては純化水素を用いる。高純度アンモニアの純度は99.999%以上、純化水素の純度は99.999995%以上である。n型ドーパント(ドナー)のSi原料には水素ベースのシランを用い、p型ドーパント(アクセプタ)のMg原料にはビスシクロペンタジエニルマグネシウムを用いるのがよい。

導電性基板としては、直径2インチの導電性窒化ガリウム基板を用いる。1030℃、100Torrで、アンモニアおよび水素の雰囲気中で、基板クリーニングを実施する。その後、1050℃に昇温して、200Torr、V/III比=1500で窒化ガリウム層を成長させる。上記の導電性基板上のGaN層の形成は、GaN基板1の形成だけでなく、GaN基板1上の積層体15の成長においても共通する方法である。

上記の方法で、GaN基板1上に、n−型GaN層ドリフト層4/p型GaNバリア層6、の順にnp構造を成長する。GaN系積層体15の積層が終了した時点でp型GaNバリア層6内には高濃度の水素が集積している。

上記の再成長層27の成長時に、水素は確実にGaN系積層体15内に侵入する。とくにp型GaNバリア層6内への集積濃度を増大させる。したがって、脱水素処理は、少なくとも再成長層27の成長を終了した後に必ず行う必要がある。

脱水素アニールの温度は、600℃〜800℃程度にするのがよい。本実施の形態においては、表面側がpn構造なので水素は抜けやすい。このため、p型GaNバリア層6への高濃度の水素の集積はなくなる。この結果、上記(a1)〜(a3)の作用を安定して得ることができる。

p型GaNバリア層6の電位を固定し、かつ正孔を引き抜くため、当該p型GaNバリア層6に対するp側電極(オーミック電極)を形成することが望ましい。このp側電極は、ソース電極Sが兼ねてもよいし、またはソース電極Sとは別に設けてもよい。図1に示す半導体装置10のソース電極Sは、このp側電極を兼ねる形態をとっている。ここでは、ソース電極Sとは別に、ソース電極Sに接触(短絡)するp側電極を設ける場合について説明する。

フォトリソグラフィを用いて、再成長膜27および絶縁膜9に、ドライエッチングにより溝(孔)を形成し、p型GaNバリア層6を露出しておき、p型GaNバリア層6と低い接触抵抗で接触する金属、例えばNi/Auなどをリフトオフ法により堆積し、パターニングしてp側電極を形成する。その後、上記方法にて形成したp側電極を覆い、かつ再成長膜27と低い接触抵抗で接触する材料、例えばTi/Alでソース電極をリフトオフ法により堆積し、パターニングすることでソース電極Sを形成するのがよい。これにより、p側電極はp型GaNバリア層6に、またソース電極Sは電子走行層22と低い抵抗で接触しながら、p側電極とソース電極Sとを接触(短絡)させることで接地の共通電極として機能する。この結果、デバイス面積を小さくすることができる。

Claims (6)

- 表層からn−型GaN系半導体層まで届く開口部が設けられたGaN系積層体を備える縦型の半導体装置であって、

前記開口部の壁面および該開口部周縁の前記GaN系積層体を覆うように位置するチャネルを含む再成長層と、

前記n−型GaN系半導体層上に接して位置し、前記開口部の壁面で前記再成長層にその端面が被覆されるp型GaN系半導体層と、

前記開口部において前記再成長層の上に位置するゲート電極と、

前記開口部の周囲の前記GaN系積層体上に位置するソース電極とを備え、

前記再成長層は電子走行層および電子供給層を含み、前記チャネルが前記電子走行層内の前記電子供給層との界面に生じる二次元電子ガスにより形成され、前記電子走行層および電子供給層はともにアンドープであり、

前記p型GaN系半導体層が前記GaN系積層体の表層をなし、かつ前記ソース電極が前記再成長層およびp型GaN系半導体層に接して位置し、

前記p型GaN系半導体層の上層にある半導体層はアンドープのGaN系半導体層に限られることを特徴とする、半導体装置。 - 前記再成長層は前記ソース電極の側面まで延在しており、該ソース電極は、該再成長層に側面で接しながら前記p型GaN系半導体層内に延びていることを特徴とする、請求項1に記載の半導体装置。

- 前記p型GaN系半導体層のマグネシウム濃度を1E17cm−3以上1E19cm−3以下とすることを特徴とする、請求項1または2に記載の半導体装置。

- 前記再成長層上であって、前記ゲート電極の下に、絶縁層を備えることを特徴とする、請求項1〜3のいずれか1項に記載の半導体装置。

- GaN系積層体をMOCVD法によって成長する、縦型の半導体装置の製造方法であって、

n−型GaN系半導体層上に、前記GaN系積層体の表層をなすp型GaN系半導体層を形成する工程と、

エッチングにより、前記表層から前記n−型GaN系半導体層にまで届く開口部を形成する工程と、

前記開口部および該開口部周縁に、電子走行層および電子供給層を含む再成長層を成長する工程と、

前記開口部周囲の前記GaN系積層体の表層に、前記再成長層および前記p型GaN系半導体層の両方に接触するようにソース電極を形成する工程と、

前記再成長層を形成した後、真空雰囲気または不活性気体雰囲気において加熱する脱水素アニールを行う工程とを備え、

前記再成長層における前記電子走行層および電子供給層をアンドープとし、前記p型GaN系半導体層の上層にある半導体層はアンドープのGaN系半導体層に限られることを特徴とする、半導体装置の製造方法。 - 前記脱水素アニールは、前記ソース電極を形成する工程よりも前に行うことを特徴とする、請求項5に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010227850A JP5569321B2 (ja) | 2010-10-07 | 2010-10-07 | 半導体装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010227850A JP5569321B2 (ja) | 2010-10-07 | 2010-10-07 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012084617A JP2012084617A (ja) | 2012-04-26 |

| JP5569321B2 true JP5569321B2 (ja) | 2014-08-13 |

Family

ID=46243212

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010227850A Expired - Fee Related JP5569321B2 (ja) | 2010-10-07 | 2010-10-07 | 半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5569321B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12087762B2 (en) | 2018-07-17 | 2024-09-10 | Panasonic Holdings Corporation | Nitride semiconductor device |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2998709B1 (fr) * | 2012-11-26 | 2015-01-16 | Commissariat Energie Atomique | Procede de fabrication d'un transistor a heterojonction de type normalement bloque |

| JP6070526B2 (ja) | 2013-12-11 | 2017-02-01 | 豊田合成株式会社 | 半導体装置の製造方法 |

| JP6754782B2 (ja) | 2016-02-12 | 2020-09-16 | パナソニック株式会社 | 半導体装置 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7919791B2 (en) * | 2002-03-25 | 2011-04-05 | Cree, Inc. | Doped group III-V nitride materials, and microelectronic devices and device precursor structures comprising same |

| JP4645034B2 (ja) * | 2003-02-06 | 2011-03-09 | 株式会社豊田中央研究所 | Iii族窒化物半導体を有する半導体素子 |

| JP4916671B2 (ja) * | 2005-03-31 | 2012-04-18 | 住友電工デバイス・イノベーション株式会社 | 半導体装置 |

| JP5252813B2 (ja) * | 2007-03-15 | 2013-07-31 | 株式会社豊田中央研究所 | 半導体装置の製造方法 |

| JP2008270310A (ja) * | 2007-04-17 | 2008-11-06 | Toyota Central R&D Labs Inc | Iii族窒化物系化合物半導体縦型トランジスタ及びその製造方法 |

| JP2009094337A (ja) * | 2007-10-10 | 2009-04-30 | Toyota Central R&D Labs Inc | 半導体素子の製造方法 |

| EP2405467A1 (en) * | 2009-03-02 | 2012-01-11 | Toyota Jidosha Kabushiki Kaisha | Nitride semiconductor device and method for manufacturing the same |

-

2010

- 2010-10-07 JP JP2010227850A patent/JP5569321B2/ja not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12087762B2 (en) | 2018-07-17 | 2024-09-10 | Panasonic Holdings Corporation | Nitride semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012084617A (ja) | 2012-04-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101211969B (zh) | 高速大功率氮化物半导体器件及其制造方法 | |

| JP5110153B2 (ja) | 半導体装置およびその製造方法 | |

| JP4737471B2 (ja) | 半導体装置およびその製造方法 | |

| JP5003813B2 (ja) | 半導体装置およびその製造方法 | |

| JP5742072B2 (ja) | 半導体装置およびその製造方法 | |

| US9478632B2 (en) | Method of manufacturing a semiconductor device | |

| US11502170B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP5353735B2 (ja) | 半導体装置およびその製造方法 | |

| JP2012084739A (ja) | 半導体装置およびその製造方法 | |

| JP2012094688A (ja) | 半導体装置およびその製造方法 | |

| JP2007103451A (ja) | 半導体装置及びその製造方法 | |

| CN113380623A (zh) | 通过p型钝化实现增强型HEMT的方法 | |

| JP2007165431A (ja) | 電界効果型トランジスタおよびその製造方法 | |

| US20130240900A1 (en) | Semiconductor device and method for producing the same | |

| JP2010199597A (ja) | 化合物半導体装置の製造方法 | |

| CN115000168A (zh) | 一种p型氮化物增强型hemt器件及其制备方法 | |

| CN114744039A (zh) | 一种高耐压增强型的双异质结栅极hemt及其制备方法 | |

| JP5569321B2 (ja) | 半導体装置およびその製造方法 | |

| US20140110758A1 (en) | Semiconductor device and method for producing same | |

| KR101943356B1 (ko) | 선택 성장을 이용한 질화물 반도체 소자 및 그 제조 방법 | |

| JP2008226907A (ja) | 窒化物半導体積層構造およびその形成方法、ならびに窒化物半導体素子およびその製造方法 | |

| US20250364246A1 (en) | Methods of selectively forming group iii nitride semiconductor regions on epitaxially grown group iii nitride semiconductor layer structures and related semiconductor devices | |

| JP5429012B2 (ja) | 半導体装置およびその製造方法 | |

| US20250287681A1 (en) | Nitride semiconductor device and method for manufacturing the nitride semiconductor device | |

| JP5134797B2 (ja) | GaN系半導体素子及びその製造方法並びにGaN系半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130417 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130514 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131105 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131224 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140527 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140609 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5569321 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |