JP5551663B2 - 直接rf変調送信器 - Google Patents

直接rf変調送信器 Download PDFInfo

- Publication number

- JP5551663B2 JP5551663B2 JP2011187410A JP2011187410A JP5551663B2 JP 5551663 B2 JP5551663 B2 JP 5551663B2 JP 2011187410 A JP2011187410 A JP 2011187410A JP 2011187410 A JP2011187410 A JP 2011187410A JP 5551663 B2 JP5551663 B2 JP 5551663B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- transistor

- voltage

- gate

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000005096 rolling process Methods 0.000 claims 1

- 230000005540 biological transmission Effects 0.000 description 17

- 238000010586 diagram Methods 0.000 description 14

- 238000006243 chemical reaction Methods 0.000 description 11

- 230000008859 change Effects 0.000 description 8

- 238000000034 method Methods 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 230000000694 effects Effects 0.000 description 5

- 238000005070 sampling Methods 0.000 description 3

- 230000007704 transition Effects 0.000 description 3

- 238000004891 communication Methods 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 230000003321 amplification Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000000052 comparative effect Effects 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

Images

Landscapes

- Transmitters (AREA)

Description

このようなマルチモードマルチバンド対応端末の送信に係る構成として、デジタルベースバンド信号をアナログ信号に変換(デジタル/アナログ変換)する際に、同時にRF送信キャリア周波数への周波数変換も行い、デジタル信号から直接RF周波数に変調する送信器が近年知られている。このような送信器は、例えば、特許文献1に記載されている。

2分周器3には、周波数掛算用のRF信号(以下、送信ローカルRF信号と記す)Loin+、送信ローカルRF信号Loin+の位相が反転された送信ローカルRF信号Loin−が外部から供給されている。2分周器3は、送信ローカルRF信号Loin+、Loin−を入力し、90度位相の異なる二対の差動ローカル信号TxLoI+、TxLoI−、TxLoQ+、TxLoQ−を生成し、デジタル/RF変換器1、2に各々出力する。

ここで入力信号LO+、LO−が入力される差動対を構成するMOSトランジスタ145、146のゲート幅Wについて説明する。

次に、図14に示したユニットブロックで必要な電源電圧Vddについて説明する。この説明では、差動入力信号LO+、LO−のうち、入力信号LO+は正、入力信号LO−は負の状態であるとする。また、デジタルベースバンド信号VLN+、VLN−のうち、デジタルベースバンド信号VLN+は正、デジタルベースバンド信号VLN−は負の状態であるとする。すなわち、以下の説明では、MOSトランジスタ147で発生した定電流が、MOSトランジスタ145、141を経由して出力に流れる場合を想定している。

Vdd´ > Vo+Vov1´+Vov5´+Vov7´ …式(1)

ここで、出力電圧は電源電圧Vdd´を中心として電源電圧Vdd´+V0からVdd´−V0の間で変化すると想定している。定電流源用のMOSトランジスタ147の電流値をI0とすると、このユニットブロックで消費される消費電力はVdd´×I0となる。携帯型の送信器等では、その消費電力が蓄電池の放電時間に影響を与えるため、小さいほど好ましい。図14に示したユニットブロックの消費電力は、MOSトランジスタ141、145、157のオーバードライブ電圧を小さくすることによって数式上は削減可能である。

本発明は、以上の点に鑑みてなされたものであり、消費電力をより省力化することができる直接RF変調送信器を提供することを目的とする。

また、本発明の直接RF変調送信器は、上記した発明において、前記第1トランジスタ、前記第2トランジスタ、前記第3トランジスタ、前記第4トランジスタが、N型MOSトランジスタで構成されることが望ましい。

以上のことから、本発明によれば、消費電力をいっそう省力化することができる直接RF変調送信器を提供することができる。

以下、本発明の直接RF変調送信器の第1実施形態、第2実施形態、第3実施形態を説明する。

・回路構成

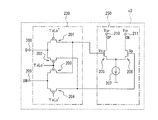

図1は、第1実施形態の直接RF変調送信器の回路構成を説明するための図であって、直接RF変調送信器に含まれるデジタル/RF変換器の1つのユニットブロックu1を示している。なお、ユニットブロックとは、直接RF変調送信器に含まれるデジタル/RF変換器を構成する1つの電流源と、この電流源に対応して設けられた複数のスイッチとを含むユニットを指す。

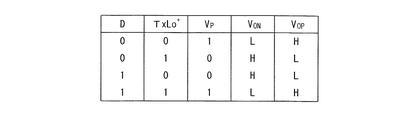

また、受動ミキサ回路100のMOSトランジスタ101、104のゲートには、差動ローカル信号TxLoI+が入力される。MOSトランジスタ102、103のゲートには、差動ローカル信号TxLoI−が入力される。差動ローカル信号TxLoI+、TxLoI−は、送信キャリア波の周波数で振動する。

MOSトランジスタ105、106は、MOSトランジスタ107から供給された一定の電流を、出力端子110、111に振り分ける。出力端子110、111に振り分けられた電流は、ユニットブロックu1の外部で電流負荷回路に入力され、電圧に変換される。この結果、MOSトランジスタ105のドレインと接続する出力端子110には出力電圧Vonがかかる。また、MOSトランジスタ106のドレインと接続する出力端子111には出力電圧Vopがかかる。

第1実施形態の直接RF変調送信器において、電流出力回路150を構成する全てのMOSトランジスタが飽和領域で動作するための必要最低限の電源電圧Vddは、数式(2)で表される。

Vdd >Vo+Vov5+Vov7 …式(2)

式(2)において、Vov5はMOSトランジスタ105のオーバードライブ電圧を指す。また、Vov7は、MOSトランジスタ107のオーバードライブ電圧を指す。また、受動ミキサ回路100の出力電圧Vpの極性がハイであり、Vnの極性がローであり、ユニットブロックの出力においてシングルエンドのゼロ−ピーク電圧振幅V0が必要であるものとした。

さらに、第1実施形態では、受動ミキサ回路100の電源、グランド間に電流が流れる経路が無いため、受動ミキサ回路100では電流が消費されない。このため、図1に示したユニットブロックを含む第1実施形態の直接RF変調送信器は、従来の直接RF変調送信器と比較していっそうの低電源電圧化による低消費電力化が可能である。

次に、ユニットブロックを含むデジタル/RF変換器の前段回路(例えば2分周器)に対する、第1実施形態の影響について説明する。

図1に示した受動ミキサ回路100を構成するMOSトランジスタ101〜104は、そのゲート、ソース間電圧が十分高くなってオーバードライブ電圧が正になると、ソース、ドレイン間が電気的に接続される。そして、ソース、ドレイン間の電圧が等しくするように動作する。このような動作は、受動ミキサ回路100を構成するMOSトランジスタ101〜104が、正のオーバードライブ電圧のときに、基本的に三極管領域において動作することを意味する。

W/L=2・π・CL・f/(μ・Cox・Vds) …式(3)

CL=Cox・W・L 式(4)

次に、図1の差動対を構成するMOSトランジスタ105が、図14のトランジスタ145と同一サイズ、同じ単位面積当たりのゲート容量Coxを有し、MOSトランジスタ105と図14に示したMOSトランジスタ145とはゲート容量CLが等しいとする。さらに、図1に示したMOSトランジスタ107と図14に示したMOSトランジスタ147は同一値の定電流を生成するものとする。

以上のことから、第1実施形態の直接RF変調送信器は、そのユニットブロックの前段回路が駆動すべき容量が、従来技術よりも小さくなる。このため、第1実施形態の直接RF変調送信器は、従来よりも低い消費電力で駆動することができるようになる。

・回路構成

図3は、本発明の第2実施形態の直接RF変調送信器の、ユニットブロックu2を説明するための図である。ユニットブロックu2は、MOSトランジスタ201、202、203、204、205、206を含んでいる。MOSトランジスタ201〜204は、P型MOSトランジスタであって、受動ミキサ回路200を構成する。MOSトランジスタ205、206は、NMOSトランジスタである。

MOSトランジスタ201、202のソースは、端子208に接続されている。また、MOSトランジスタ203、204のソースは端子209に接続されている。端子208は、受動ミキサ回路200に1ビットベースバンドデータDを入力する。端子209は、受動ミキサ回路200に1ビットベースバンドデータDの反転データDNを入力する。

出力端子210、211に振り分けられた電流は、ユニットブロックu2の外部で電流負荷回路に入力され、電圧に変換される。

第2実施形態の直接RF変調送信器の電流出力回路250は、図1に示したMOSトランジスタ107に代えて、定電流源207を設けた点でのみ第1実施形態と相違する。電流出力回路250は第1実施形態の電流出力回路150と同様に動作するため、その説明を省くものとする。

次に、ユニットブロックを含むデジタル/RF変換器の前段回路(例えば2分周器)に対する、第2実施形態の影響について説明する。

先ず、図3に示したMOSトランジスタ201のゲート幅Wとゲート長LのW/L比を、式(3)を使って計算する。差動対を構成するMOSトランジスタ205、206は、図1に示したMOSトランジスタ105、106と同一の設計条件、プロセス条件によって製造されているものとする。また、受動ミキサ回路200を構成するMOSトランジスタ201のVds=−0.1[V]、キャリア移動度μ=−40[uA/V2]とする。この他の条件は、第1実施形態のMOSトランジスタ101のW/L比を計算するにあたって式(3)に入力されたものと同じであるものとする。

次に、受動ミキサ回路200の出力電圧変化の挙動が、受動ミキサ回路200と接続される電流出力回路250に与える影響を説明する。

(1)第1実施形態について(比較例)

第2実施形態と比較するため、先ず、受動ミキサ回路100を構成するMOSトランジスタに、NMOSトランジスタを使った第1実施形態における定電流源への影響について説明する。

NMOSトランジスタがスイッチとしてオン状態となる条件は、式(5)によって表される。

Vgs−Vtn>0 式(5)

出力電圧Vpは、MOSトランジスタ101がオン、MOSトランジスタ103がオフの場合、1ビットベースバンドデータDにしたがう電圧となる。また、MOSトランジスタ101がオフ、MOSトランジスタ103がオンの場合、反転データDNにしたがう電圧となる。また、MOSトランジスタ101がオン、MOSトランジスタ103がオンの場合、1ビットベースバンド信号にしたがう電圧と、反転データDNにしたがう電圧の中間電圧となる。さらに、MOSトランジスタ101がオフ、MOSトランジスタ103がオフになる状態は、差動ローカル信号TxLo+、TxLo−の動作点を適切にバイアスすることによって回避される。

次に、図3に示した受動ミキサ回路200の出力の電圧変化の挙動が、電流出力回路250のMOSトランジスタ205、206と定電流源207に与える影響を説明する。

受動ミキサ回路200を構成するMOSトランジスタ201〜204は、PMOSトランジスタである。PMOSトランジスタがスイッチとしてオン状態となる条件は、式(6)によって与えられる。式(6)において、Vgsはトランジスタのゲート、ソース間電圧であり、VtpはPMOSトランジスタの閾値電圧である。

Vgs−Vtp <0 …式(6)

出力電圧Vpは、MOSトランジスタ201がオン、MOSトランジスタ203がオフの場合、1ビットベースバンドデータDにしたがう電圧となる。また、MOSトランジスタ201がオフ、MOSトランジスタ203がオンの場合、反転データDNにしたがう電圧となる。また、MOSトランジスタ201がオン、MOSトランジスタ203がオンの場合、1ビットベースバンド信号にしたがう電圧と、反転データDNにしたがう電圧の中間電圧となる。さらに、MOSトランジスタ201がオフ、MOSトランジスタ203がオフになる状態は、差動ローカル信号TxLo+、TxLo−の動作点を適切にバイアスすることによって回避される。

・回路構成

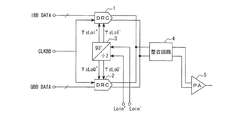

図10は、本発明の第3実施形態を説明するための図であって、実施形態3の直接RF変調送信器に含まれる、デジタル/RF変換器(図中、DRCと記す)の回路図である。デジタル/RF変換器は、LSB(Least Significant Bit)側の信号を処理するブロックと、MSB(Most Significant Bit)側の信号を処理するブロックとを備えている。LSB側のブロックは、ユニットブロックがバイナリで重み付けされた電流源300、301、…30kと、NMOSトランジスタで構成された差動対340、341、…34kと、ローカル信号用とデータ信号を周波数掛算するためのNMOSトランジスタで構成されたミキサ回路320、321、…32kと、で構成されている。

また、ミキサ回路320、321、…32k、ミキサ回路320を第2実施形態で説明した、PMOSトランジスタで構成された受動ミキサ回路に置き換えたデジタル/RF変換器回路を有した直接RF変調送信器においても、デジタル/アナログ変換と周波数掛算とを同時に行うことができる。

図10に示した第1実施形態、第2実施形態のユニットブロックに相当する構成から得られた電流は、図10に示すように、加算されて外部に出力される。

図10に示した実施形態3のデジタル/RF変換器回路は、第1実施形態もしくは第2実施形態に記載のユニットブロックにより構成される。このため、第1実施形態、第2の実施形態において説明した通り、従来技術と比較し、低電圧化による低消費化に加え、前段回路の消費電流低減による低消費電力化が可能である。

受動ミキサ回路 100、200

端子 108、109、208、209

出力端子 110、111、210、211

電流出力回路 150、250

定電流源 207、300〜30K、310

ミキサ回路 320〜32K、330

差動対 340〜34K、350

デジタル/RF変換器(DRC)1、2

2分周器 3

整合回路 4

パワーアンプ(PA) 5

ローカル信号用スイッチ 220〜22k、230

データ信号用スイッチ 240〜24k、260

定電流源 280〜28K、290

MOSトランジスタ 141〜147

Claims (5)

- 1ビットのデジタルベースバンドデータの正転データと当該正転データの反転データとを入力し、第1RF信号と当該第1RF信号と位相が180度異なる第2RF信号とを入力し、前記正転データおよび前記反転データが前記第1RF信号および前記第2RF信号によって周波数変換された第1電圧信号と当該第1電圧信号の差動信号である第2電圧信号とを出力する受動ミキサ回路と、

定電流源と、

前記定電流源によって生成された定電流を、前記受動ミキサ回路から出力された前記第1電圧信号、第2電圧信号に応じて第1出力信号と、当該第1電圧信号の差動信号である第2出力信号とに変換する差動対素子と、

を有するユニットブロックを複数個含み、

複数ビットの前記デジタルベースバンドデータからなるデジタルベースバンド信号によって前記第1RF信号及び前記第2RF信号を変調し、前記各ユニットブロックからの出力信号を加算すること特徴とする直接RF変調送信器。 - 前記受動ミキサ回路は、

ソースに前記1ビットのデジタルベースバンドデータの正転データが入力され、ゲートに前記第1RF信号が入力され、ドレインが前記差動対を構成する第5トランジスタのゲートに接続される第1トランジスタと、

ソースに前記1ビットのデジタルベースバンドデータの正転データが入力され、ゲートに前記第2RF信号が入力され、ドレインが前記差動対を構成する第6トランジスタのゲートに接続される第2トランジスタと、

ソースに前記1ビットのデジタルベースバンドデータの反転データが入力され、ゲートに前記第2RF信号が入力され、ドレインが前記第5トランジスタのゲートに接続される第3トランジスタと、

ソースに前記1ビットのデジタルベースバンドデータの反転データが入力され、ゲートに前記第1RF信号が入力され、ドレインが前記第6トランジスタのゲートに接続される第4トランジスタと、

を含むこと特徴とする請求項1に記載の直接RF変調送信器。 - 前記定電流源は、前記第5トランジスタのソースと前記第6トランジスタのソースの共通接点に接続されることを特徴とする請求項2に記載の直接RF変調送信器。

- 前記第1トランジスタ、前記第2トランジスタ、前記第3トランジスタ、前記第4トランジスタは、N型MOSトランジスタで構成されることを特徴とする請求項2から3のいずれかに1項に記載の直接RF変調送信器。

- 前記第1トランジスタ、前記第2トランジスタ、前記第3トランジスタ、前記第4トランジスタは、P型MOSトランジスタで構成されることを特徴とする請求項2から3のいずれかに1項に記載の直接RF変調送信器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011187410A JP5551663B2 (ja) | 2011-08-30 | 2011-08-30 | 直接rf変調送信器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011187410A JP5551663B2 (ja) | 2011-08-30 | 2011-08-30 | 直接rf変調送信器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013051494A JP2013051494A (ja) | 2013-03-14 |

| JP5551663B2 true JP5551663B2 (ja) | 2014-07-16 |

Family

ID=48013255

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011187410A Expired - Fee Related JP5551663B2 (ja) | 2011-08-30 | 2011-08-30 | 直接rf変調送信器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5551663B2 (ja) |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6980779B2 (en) * | 2003-11-20 | 2005-12-27 | Nokia Corporation | RF transmitter using digital-to-RF conversion |

| JP2009049585A (ja) * | 2007-08-16 | 2009-03-05 | Renesas Technology Corp | 差動増幅回路、ミキサ回路および受信装置 |

| US8615205B2 (en) * | 2007-12-18 | 2013-12-24 | Qualcomm Incorporated | I-Q mismatch calibration and method |

-

2011

- 2011-08-30 JP JP2011187410A patent/JP5551663B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013051494A (ja) | 2013-03-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10008984B2 (en) | Apparatus and method for dynamically biased baseband current amplifier | |

| JPWO2012176250A1 (ja) | 差動スイッチ駆動回路及び電流ステアリング型デジタル・アナログ変換器 | |

| US9503022B2 (en) | Balanced up-conversion mixer | |

| US20120256676A1 (en) | Mixer circuit | |

| US7463869B2 (en) | Low noise high isolation transmit buffer gain control mechanism | |

| US7868695B2 (en) | Differential amplifier | |

| US8847662B2 (en) | Mixer and associated signal circuit | |

| CN103684267B (zh) | 信号混频电路 | |

| JP6446192B2 (ja) | 送信装置及び送信方法 | |

| JP5551663B2 (ja) | 直接rf変調送信器 | |

| KR100799227B1 (ko) | 진폭 변조를 위한 캐스코드 구조의 전력 증폭기 | |

| Zimmermann et al. | Design of an RF-DAC in 65nm CMOS for multistandard, multimode transmitters | |

| CN105720923A (zh) | 切换电路、集成电路、主动混频器电路及相关方法 | |

| JP4580882B2 (ja) | 半導体集積回路 | |

| US20080242253A1 (en) | Frequency converter and radio receiver using the same | |

| US9197174B2 (en) | Analog baseband filter for radio transceiver | |

| JP2012114610A (ja) | 電子回路 | |

| JP5204902B2 (ja) | トランスファーゲート回路ならびにそれを用いた電力合成回路,電力増幅回路,送信装置および通信装置 | |

| JP2006074380A (ja) | 周波数混合器 | |

| JP4909862B2 (ja) | 周波数変換回路および受信機 | |

| CN110120785B (zh) | 一种低功耗混频器 | |

| US10382036B2 (en) | High voltage switch | |

| JP2013223118A (ja) | ミキサ回路 | |

| JP5602791B2 (ja) | 送信器 | |

| JP5524913B2 (ja) | 送信器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130328 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131111 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131126 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140127 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140520 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140522 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5551663 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |