JP5425585B2 - マルチ・モード増幅器 - Google Patents

マルチ・モード増幅器 Download PDFInfo

- Publication number

- JP5425585B2 JP5425585B2 JP2009240433A JP2009240433A JP5425585B2 JP 5425585 B2 JP5425585 B2 JP 5425585B2 JP 2009240433 A JP2009240433 A JP 2009240433A JP 2009240433 A JP2009240433 A JP 2009240433A JP 5425585 B2 JP5425585 B2 JP 5425585B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- amplifier

- output

- current

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000002457 bidirectional effect Effects 0.000 claims 12

- 230000008901 benefit Effects 0.000 description 3

- 230000003321 amplification Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000014509 gene expression Effects 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 239000000969 carrier Substances 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 230000003362 replicative effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/45179—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using MOSFET transistors as the active amplifying circuit

- H03F3/45183—Long tailed pairs

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/45475—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using IC blocks as the active amplifying circuit

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F3/00—Non-retroactive systems for regulating electric variables by using an uncontrolled element, or an uncontrolled combination of elements, such element or such combination having self-regulating properties

- G05F3/02—Regulating voltage or current

- G05F3/08—Regulating voltage or current wherein the variable is dc

- G05F3/10—Regulating voltage or current wherein the variable is dc using uncontrolled devices with non-linear characteristics

- G05F3/16—Regulating voltage or current wherein the variable is dc using uncontrolled devices with non-linear characteristics being semiconductor devices

- G05F3/20—Regulating voltage or current wherein the variable is dc using uncontrolled devices with non-linear characteristics being semiconductor devices using diode- transistor combinations

- G05F3/30—Regulators using the difference between the base-emitter voltages of two bipolar transistors operating at different current densities

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Amplifiers (AREA)

Description

なお、米国政府が、空軍調査研究所との契約番号FA8650−05−C−5707に遵守する本発明の確実性権利を獲得している。

文脈により明示されない限りにおいて、本発明の異なる実施例は一緒に用いることができる。

更なる実施例では、第1の電流出力と第2の電流出力はそれぞれ、高インピーダンスである。更なる実施例では、第1の電流出力と第2の電流出力はそれぞれ、第1の電圧入力と第2の電圧入力間の差分の増幅形態である。

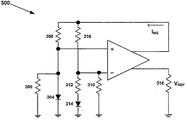

本明細書に開示される例示的な増幅器は多種多様な形態で動作可能な増幅器である。図面を参照すると、図2(a)は例示的な増幅器を示すものであって、増幅器は、(a)第1及び第2の入力と(b)第1及び第2の出力を含む。(ただし、図2の(a)は、第1の例示的な増幅器を示し、オペアンプ(“op−amp)に共通な三角記号を用いて示しており、第1の例示的な増幅器は、タイプ2の電流搬送器(”CCII”(Second Generation Current Conveyor:第2世代電流搬送器)についての記号を用いて示しても良い。図示しないが、第1の例示的な増幅器はまた第1と第2の電力入力を含んでいる。

(1)VP−VN=0

(2)IP=IN=0

(1)VN=VOUT=VP

(2)IOUT1=IOUT2=IN

(3)IP=0

である。

本発明の例示的な実施の形態を説明した。しかし、当業者は変更と修正が、特許請求の範囲で定義される本発明の範囲と技術的思想から逸脱することなく、上述の実施の形態に対してなされることを理解できるであろう。

Claims (2)

- マルチ・モードで動作可能な増幅器において、

第1及び第2の電圧入力と、

第1及び第2の双方向性の電流出力であって、実質的に同じ振幅と実質的に同じ極性を有する双方向性の第1及び第2の電流出力と、

第3の双方向性の電流出力を備え、

該第3の双方向性の電流出力は、実質的に第1及び第2の電流出力の振幅と同じ振幅を有し、該第3の双方向性の電流出力は、第1及び第2の双方向性の電流出力の極性と実質的に反対の極性を有し、

前記増幅器が、前記第1の双方向性の電流出力、及び、前記第2の双方向性の電流出力が、一緒に結合されるときに、第1のモードで動作し、

前記増幅器が、前記第1の双方向性の電流出力と前記第2の双方向性の電流出力の1つが、前記第2の電圧入力に結合されるときに、第2のモードで動作する、

ことを特徴とする増幅器。 - 請求項1記載の増幅器において、前記増幅器が、

前記第1の双方向性の電流出力と、前記第2の双方向性の電流出力の1つが、フローティング(浮遊)状態であるときに、第1のモードで動作する、

ことを特徴とする増幅器。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/339,572 US8081030B2 (en) | 2008-12-19 | 2008-12-19 | Multi-mode amplifier |

| US12/339,572 | 2008-12-19 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010148094A JP2010148094A (ja) | 2010-07-01 |

| JP2010148094A5 JP2010148094A5 (ja) | 2012-10-25 |

| JP5425585B2 true JP5425585B2 (ja) | 2014-02-26 |

Family

ID=41668392

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009240433A Active JP5425585B2 (ja) | 2008-12-19 | 2009-10-19 | マルチ・モード増幅器 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8081030B2 (ja) |

| EP (2) | EP2595314B1 (ja) |

| JP (1) | JP5425585B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013140740A1 (ja) | 2012-03-19 | 2013-09-26 | パナソニック株式会社 | Iv変換器およびこのiv変換器を用いた慣性力センサ |

| US8692700B2 (en) | 2012-05-02 | 2014-04-08 | Honeywell International Inc. | Sigma-delta digital-to-analog converter |

| US8823450B2 (en) * | 2012-07-19 | 2014-09-02 | Honeywell International Inc. | Multiple-output transconductance amplifier based instrumentation amplifier |

| US9112462B2 (en) | 2013-05-15 | 2015-08-18 | Honeywell International Inc. | Variable-gain dual-output transconductance amplifier-based instrumentation amplifiers |

| DE102015204021B4 (de) * | 2015-03-05 | 2017-04-06 | Dialog Semiconductor (Uk) Limited | Dynamische Strombegrenzungsschaltung |

| US9882473B2 (en) | 2016-05-13 | 2018-01-30 | Silanna Asia Pte Ltd | Power converter with robust stable feedback |

| US10958169B2 (en) | 2016-05-13 | 2021-03-23 | Silanna Asia Pte Ltd | Power converter with robust stable feedback |

| CN106877821B (zh) * | 2017-02-21 | 2019-11-22 | 湖南师范大学 | 一种基于电流模有源器件的宽带射频混频器 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3582689A (en) | 1968-10-23 | 1971-06-01 | Canadian Patents Dev | Current conveyor with virtual input reference potential |

| GB1496782A (en) | 1974-02-20 | 1978-01-05 | Hamilton T | Generalized current amplifier |

| NL9000518A (nl) | 1990-03-07 | 1991-10-01 | Philips Nv | Breedband signaalversterker. |

| US5061902A (en) * | 1990-10-03 | 1991-10-29 | International Business Machines Corp. | Linear amplifier |

| US5124666A (en) * | 1991-03-04 | 1992-06-23 | Industrial Technology Research Institute | CMOS current convevor and its filter applications |

| FR2712127B1 (fr) | 1993-11-02 | 1995-12-01 | Alcatel Radiotelephone | Elément d'amplification à structure différentielle en mode de courant. |

| KR970063903A (ko) | 1996-02-15 | 1997-09-12 | 모리시다 요이치 | 연산증폭기 |

| JP2953383B2 (ja) | 1996-07-03 | 1999-09-27 | 日本電気株式会社 | 電圧電流変換回路 |

| DE69834329D1 (de) * | 1998-11-13 | 2006-06-01 | St Microelectronics Srl | Treiberschaltung zur Steurung eines piezoelektrischen Aktors in Ladungsmodus |

| US6583671B2 (en) | 2000-12-01 | 2003-06-24 | Sony Corporation | Stable AGC transimpedance amplifier with expanded dynamic range |

| US6538503B2 (en) | 2001-02-22 | 2003-03-25 | Texas Instruments Incorporated | Instrumentation amplifier and method for obtaining high common mode rejection |

| US6710655B2 (en) | 2001-05-23 | 2004-03-23 | Texas Instruments Incorporated | Bipolar emitter couple pair transconductor for high speed operational amplifiers |

| US6842067B2 (en) | 2002-04-30 | 2005-01-11 | Skyworks Solutions, Inc. | Integrated bias reference |

| US6847569B2 (en) | 2002-12-30 | 2005-01-25 | Intel Corporation | Differential current sense amplifier |

| KR20030053492A (ko) | 2003-06-05 | 2003-06-28 | 차형우 | 유니버셜 계측 증폭기 |

| US7030690B2 (en) | 2004-02-12 | 2006-04-18 | Honeywell International, Inc. | Operational amplifier with selectable performance characteristics |

| US7183851B2 (en) | 2004-06-30 | 2007-02-27 | Intel Corporation | Differential dual port current conveyor circuit |

| US7215197B2 (en) | 2004-08-17 | 2007-05-08 | National Instruments Corporation | Programmable gain instrumentation amplifier with improved gain multiplexers |

| US7327189B2 (en) | 2004-08-17 | 2008-02-05 | National Instruments Corporation | Differential structure programmable gain instrumentation amplifier |

| US20070057721A1 (en) | 2005-08-31 | 2007-03-15 | Texas Instruments Incorporated | System for amplifiers with low distortion and low output impedance |

| JP2008117215A (ja) * | 2006-11-06 | 2008-05-22 | Toshiba Corp | 基準電位発生回路 |

| US7893759B1 (en) | 2009-03-18 | 2011-02-22 | Honeywell International Inc. | Current conveyor based instrumentation amplifier |

-

2008

- 2008-12-19 US US12/339,572 patent/US8081030B2/en active Active

-

2009

- 2009-10-15 EP EP13155343.0A patent/EP2595314B1/en active Active

- 2009-10-15 EP EP09173160.4A patent/EP2200177B1/en active Active

- 2009-10-19 JP JP2009240433A patent/JP5425585B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8081030B2 (en) | 2011-12-20 |

| EP2200177A3 (en) | 2011-03-16 |

| EP2200177B1 (en) | 2020-01-15 |

| EP2595314A2 (en) | 2013-05-22 |

| EP2595314A3 (en) | 2014-10-08 |

| JP2010148094A (ja) | 2010-07-01 |

| EP2200177A2 (en) | 2010-06-23 |

| EP2595314B1 (en) | 2015-07-22 |

| US20100156385A1 (en) | 2010-06-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5425585B2 (ja) | マルチ・モード増幅器 | |

| US7956597B2 (en) | Reference buffer circuits for providing reference voltages | |

| Callewaert et al. | Class AB CMOS amplifiers with high efficiency | |

| US8063668B2 (en) | Output stage, amplifier control loop and use of the output stage | |

| US10637418B2 (en) | Stacked power amplifiers using core devices | |

| KR20080097680A (ko) | 클래스 ab 증폭기 및 이를 위한 입력 스테이지 회로 | |

| US8823450B2 (en) | Multiple-output transconductance amplifier based instrumentation amplifier | |

| US9136806B2 (en) | Amplifier circuit | |

| US7545214B2 (en) | Class AB rail-to-rail input and output operational amplifier | |

| JP2009171548A (ja) | 差動増幅回路 | |

| Palmisano et al. | A 1.5-V high drive capability CMOS op-amp | |

| US9654092B1 (en) | High speed gain stage with analog input and determinable digital output using regenerative feedback | |

| CN103023442B (zh) | 限幅放大器及其方法 | |

| CN101834575A (zh) | 运算放大器 | |

| US8035448B1 (en) | Differential amplifier that compensates for process variations | |

| US6710660B1 (en) | Class B power buffer with rail to rail output swing and small deadband | |

| US6831501B1 (en) | Common-mode controlled differential gain boosting | |

| JP5320503B2 (ja) | 増幅回路 | |

| JP2005328464A (ja) | 増幅器及びこれを用いた液晶ディスプレイ装置 | |

| JP2008011051A (ja) | 差動演算増幅器 | |

| TWI774512B (zh) | 功率放大器電路 | |

| JP2008042487A (ja) | 演算増幅器 | |

| JP2008048039A (ja) | 演算増幅回路およびそれを用いた半導体装置 | |

| JP2006148775A (ja) | 平衡型差動増幅器および平衡型演算増幅器 | |

| Edbib et al. | Current Conveyor Classifiacation and Application |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120907 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120907 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130709 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130719 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131011 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131029 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131127 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5425585 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |