JP5259784B2 - 情報処理装置およびプログラム実行制御方法 - Google Patents

情報処理装置およびプログラム実行制御方法 Download PDFInfo

- Publication number

- JP5259784B2 JP5259784B2 JP2011161936A JP2011161936A JP5259784B2 JP 5259784 B2 JP5259784 B2 JP 5259784B2 JP 2011161936 A JP2011161936 A JP 2011161936A JP 2011161936 A JP2011161936 A JP 2011161936A JP 5259784 B2 JP5259784 B2 JP 5259784B2

- Authority

- JP

- Japan

- Prior art keywords

- processor

- program module

- information processing

- execute

- processing apparatus

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Compression Or Coding Systems Of Tv Signals (AREA)

Description

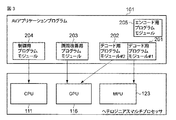

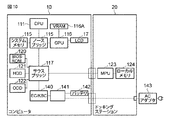

まず、図1および図2を参照して、本発明の一実施形態に係る情報処理装置の構成について説明する。この情報処理装置は、例えば、バッテリ駆動可能なノートブック型の携帯型パーソナルコンピュータ10として実現されている。

Claims (9)

- 第1の命令セットを有し、圧縮符号化された動画像データをデコードするデコード処理を実行可能な第1のプロセッサと、

前記第1の命令セットとは異なる第2の命令セットを有し、前記第1のプロセッサよりも前記デコード処理を高速に実行するように構成される第2のプロセッサと、

前記第2の命令セットを用いて記述され前記デコード処理を前記第2のプロセッサに実行させるための第1のプログラムモジュール、および前記第1の命令セットを用いて記述され前記デコード処理を前記第1のプロセッサに実行させるための第2のプログラムモジュールを含み、圧縮符号化された動画像データを再生する動画再生処理を実行するためのプログラムを格納する記憶部と、

前記プログラムによって前記動画再生処理を実行する場合、情報処理装置が前記情報処理装置内に設けられたバッテリまたは外部電源のどちらによって駆動されているかを判別する手段と、

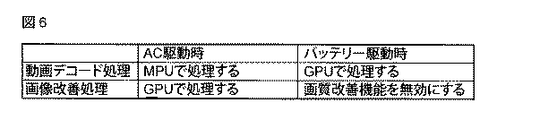

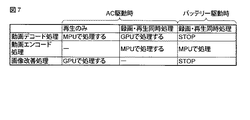

前記情報処理装置が前記外部電源によって駆動されている場合、前記第1のプログラムモジュールを前記第2のプロセッサに割り当てることによって前記デコード処理を前記第2のプロセッサに実行させ、前記情報処理装置が前記バッテリによって駆動されている場合、前記第2のプログラムモジュールを前記第1のプロセッサに割り当てることによって前記デコード処理を前記第1のプロセッサに実行させる制御手段とを具備することを特徴とする情報処理装置。 - 前記制御手段は、前記情報処理装置が前記バッテリによって駆動されている場合、前記第2のプロセッサを動作状態から前記動作状態よりも電力消費の少ない状態に移行させることを特徴とする請求項1記載の情報処理装置。

- 前記プログラムは、前記第1の命令セットを用いて記述され、前記デコード処理によってデコードされた動画像データに対して施すべき所定の映像処理を前記第1のプロセッサに実行させる第3のプログラムモジュールをさらに含み、

前記制御手段は、前記情報処理装置が前記外部電源によって駆動されている場合、前記第1のプログラムモジュールを前記第2のプロセッサに割り当てることによって前記デコード処理を前記第2のプロセッサに実行させると共に前記第3のプログラムモジュールを前記第1のプロセッサに割り当てることによって前記映像処理を前記第1のプロセッサに実行させ、前記情報処理装置が前記バッテリによって駆動されている場合、前記第2のプログラムモジュールを前記第1のプロセッサに割り当てることによって前記デコード処理を前記第1のプロセッサに実行させると共に前記第1のプロセッサによって実行すべき前記映像処理の中の少なくとも一部の処理を省略することを特徴とする請求項1記載の情報処理装置。 - 前記第1のプロセッサは、表示装置に表示されるべき画面を形成する映像信号を生成するグラフィクス処理プロセッサであり、

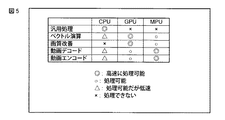

前記第2のプロセッサは、動画像データストリームを処理するように構成されたメディア処理プロセッサであることを特徴とする請求項1記載の情報処理装置。 - 第1の命令セットを有し、汎用処理、ベクトル演算を含むグラフィクス演算処理、および圧縮符号化された動画像データをデコードするデコード処理を実行可能なメインプロセッサと、

第2の命令セットを有し、前記グラフィクス演算処理および前記デコード処理を実行可能であり、且つ前記メインプロセッサよりも前記グラフィクス演算処理および前記デコード処理を高速に実行するように構成された第1のサブプロセッサと、

第3の命令セットを有し、前記グラフィクス演算処理および前記デコード処理を実行可能であり、且つ前記第1のサブプロセッサよりも前記デコード処理を高速に実行するように構成され、且つ前記第1のサブプロセッサよりも前記グラフィクス演算処理の処理性能が低い第2のサブプロセッサと、

前記第3の命令セットを用いて記述され圧縮符号化された動画像データをデコードするためのデコード処理を前記第2のサブプロセッサに実行させるための第1のプログラムモジュールと、前記第2の命令セットを用いて記述され前記デコード処理を前記第1のサブプロセッサに実行させるための第2のプログラムモジュールと、前記第2の命令セットを用いて記述され前記デコード処理によってデコードされた動画像データに対して施すべき所定の映像処理を前記第1のサブプロセッサに実行させる第3のプログラムモジュールと、前記第1の命令セットを用いて記述された制御用プログラムモジュールとを含み、圧縮符号化された動画像データを再生する動画再生処理を実行するためのプログラムを格納する記憶部と、

前記プログラムによって前記動画再生処理を実行する場合、情報処理装置が前記情報処理装置内に設けられたバッテリまたは外部電源のどちらによって駆動されているかを判別する手段と、

前記制御用プログラムモジュールを前記メインプロセッサに実行させることによって前記第1乃至第3のプログラムモジュールの実行を制御する制御手段であって、前記情報処理装置が前記外部電源によって駆動されている場合には、前記第1のプログラムモジュールを前記第2のサブプロセッサに割り当てると共に、前記第3のプログラムモジュールを前記第1のサブプロセッサに割り当て、前記情報処理装置が前記バッテリによって駆動されている場合には、前記第2のプログラムモジュールを前記第1のサブプロセッサに割り当てると共に、前記第2および第3のプログラムモジュールを前記第1のサブプロセッサに割り当て、且つ前記第2のサブプロセッサを動作状態から前記動作状態よりも電力消費の少ない状態に移行させる制御手段とを具備することを特徴とする情報処理装置。 - 前記制御手段は、前記情報処理装置が前記バッテリによって駆動されている場合には、前記第1のサブプロセッサによって実行すべき前記映像処理の中の少なくとも一部の処理を省略することを特徴とする請求項5記載の情報処理装置。

- 第1の命令セットを有し、圧縮符号化された動画像データをデコードするデコード処理を実行可能な第1のプロセッサと、前記第1の命令セットとは異なる第2の命令セットを有し、前記第1のプロセッサよりも前記デコード処理を高速に実行するように構成される第2のプロセッサとを有する情報処理装置におけるプログラムの実行を制御するプログラム実行制御方法であって、

前記第2の命令セットを用いて記述され前記デコード処理を前記第2のプロセッサに実行させるための第1のプログラムモジュール、および前記第1の命令セットを用いて記述され前記デコード処理を前記第1のプロセッサに実行させるための第2のプログラムモジュールを含み、圧縮符号化された動画像データを再生する動画再生処理を実行するためのプログラムを入力するステップと、

前記プログラムによって前記動画再生処理を実行する場合、情報処理装置が前記情報処理装置内に設けられたバッテリまたは外部電源のどちらによって駆動されているかを判別するステップと、

前記情報処理装置が前記外部電源によって駆動されている場合、前記第1のプログラムモジュールを前記第2のプロセッサに割り当てることによって前記デコード処理を前記第2のプロセッサに実行させ、前記情報処理装置が前記バッテリによって駆動されている場合、前記第2のプログラムモジュールを前記第1のプロセッサに割り当てることによって前記デコード処理を前記第1のプロセッサに実行させる制御ステップとを具備することを特徴とするプログラム実行制御方法。 - 前記制御ステップは、前記情報処理装置が前記バッテリによって駆動されている場合、前記第2のプロセッサを動作状態から前記動作状態よりも電力消費の少ない状態に移行させることを特徴とする請求項7記載のプログラム実行制御方法。

- 前記プログラムは、前記第1の命令セットを用いて記述され、前記デコード処理によってデコードされた動画像データに対して施すべき所定の映像処理を前記第1のプロセッサに実行させる第3のプログラムモジュールをさらに含み、

前記制御ステップは、前記情報処理装置が前記外部電源によって駆動されている場合、前記第1のプログラムモジュールを前記第2のプロセッサに割り当てることによって前記デコード処理を前記第2のプロセッサに実行させると共に前記第3のプログラムモジュールを前記第1のプロセッサに割り当てることによって前記映像処理を前記第1のプロセッサに実行させ、前記情報処理装置が前記バッテリによって駆動されている場合、前記第2のプログラムモジュールを前記第1のプロセッサに割り当てることによって前記デコード処理を前記第1のプロセッサに実行させると共に前記第1のプロセッサによって実行すべき前記映像処理の中の少なくとも一部の処理を省略することを特徴とする請求項8記載のプログラム実行制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011161936A JP5259784B2 (ja) | 2011-07-25 | 2011-07-25 | 情報処理装置およびプログラム実行制御方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011161936A JP5259784B2 (ja) | 2011-07-25 | 2011-07-25 | 情報処理装置およびプログラム実行制御方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007117382A Division JP2008276395A (ja) | 2007-04-26 | 2007-04-26 | 情報処理装置およびプログラム実行制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011210282A JP2011210282A (ja) | 2011-10-20 |

| JP5259784B2 true JP5259784B2 (ja) | 2013-08-07 |

Family

ID=44941184

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011161936A Active JP5259784B2 (ja) | 2011-07-25 | 2011-07-25 | 情報処理装置およびプログラム実行制御方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5259784B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7278067B2 (ja) * | 2018-12-20 | 2023-05-19 | キヤノン株式会社 | データ処理装置及びその制御方法及びプログラム |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09138716A (ja) * | 1995-11-14 | 1997-05-27 | Toshiba Corp | 電子計算機 |

| JP3826859B2 (ja) * | 2002-08-19 | 2006-09-27 | ソニー株式会社 | 情報処理方法とその方法を実現するプログラム及び記録媒体 |

| JP2004171234A (ja) * | 2002-11-19 | 2004-06-17 | Toshiba Corp | マルチプロセッサシステムにおけるタスク割り付け方法、タスク割り付けプログラム及びマルチプロセッサシステム |

| JP2006155187A (ja) * | 2004-11-29 | 2006-06-15 | Sony Corp | 情報処理システム、情報処理装置および方法、記録媒体、並びにプログラム。 |

| JP2007013315A (ja) * | 2005-06-28 | 2007-01-18 | Toshiba Corp | 情報処理装置および動画像再生方法 |

-

2011

- 2011-07-25 JP JP2011161936A patent/JP5259784B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011210282A (ja) | 2011-10-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2008276395A (ja) | 情報処理装置およびプログラム実行制御方法 | |

| US9069553B2 (en) | Switching tasks between heterogeneous cores | |

| US9529646B2 (en) | Power-efficient interaction between multiple processors | |

| TWI452514B (zh) | 電腦系統及組態該電腦系統之方法 | |

| US7917784B2 (en) | Methods and systems for power management in a data processing system | |

| TWI544322B (zh) | 管理電源使用的技術 | |

| TWI431532B (zh) | 用於經由一虛擬圖形裝置驅動程式於一顯示器上顯示一影像之方法、系統及儲存媒體 | |

| US20130125126A1 (en) | Information processing apparatus and method for controlling information processing apparatus | |

| US9632563B2 (en) | Methods and systems for time keeping in a data processing system | |

| JP7787163B2 (ja) | マルチプレクサでのgpuのブランキングやアーチファクトが発生しない(グリッチレス)切り替え | |

| US9395803B2 (en) | Multi-core processor system implementing migration of a task from a group of cores to another group of cores | |

| US9176570B2 (en) | System and method for providing universal serial bus link power management policies in a processor environment | |

| CN100373301C (zh) | 信息处理设备和该设备中的节电控制方法 | |

| JP2007264953A (ja) | 情報処理装置および動作制御方法 | |

| JP5259784B2 (ja) | 情報処理装置およびプログラム実行制御方法 | |

| WO2020197725A1 (en) | System, apparatus and method for adaptive interconnect routing | |

| JP2008243049A (ja) | 情報処理装置および同装置のメモリ制御方法 | |

| KR101441684B1 (ko) | 동영상 플레이 모드를 구비한 컴퓨터 및 이의 동영상플레이시 시스템의 모드 설정방법 | |

| WO2020068319A1 (en) | System, apparatus and method for collective power control of multiple intellectual property agents and a shared power rail | |

| JP4703757B2 (ja) | 情報処理装置 | |

| JP2006163643A (ja) | 電源制御装置、データ読出装置および電源制御方法 | |

| TWI772438B (zh) | 用於計算設備中的動態緩衝器大小設定的系統和方法 | |

| JP2011013853A (ja) | 情報処理装置 | |

| HK1152777B (en) | Virtual graphics device driver |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110801 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130115 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130308 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130424 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160502 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5259784 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313121 Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |