JP5259082B2 - 一致検証方法及び装置 - Google Patents

一致検証方法及び装置 Download PDFInfo

- Publication number

- JP5259082B2 JP5259082B2 JP2006344975A JP2006344975A JP5259082B2 JP 5259082 B2 JP5259082 B2 JP 5259082B2 JP 2006344975 A JP2006344975 A JP 2006344975A JP 2006344975 A JP2006344975 A JP 2006344975A JP 5259082 B2 JP5259082 B2 JP 5259082B2

- Authority

- JP

- Japan

- Prior art keywords

- result

- verification

- assertion

- fpga

- assertion check

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Tests Of Electronic Circuits (AREA)

- Test And Diagnosis Of Digital Computers (AREA)

- Devices For Executing Special Programs (AREA)

Description

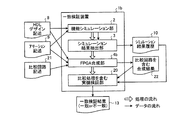

図1は、この発明の実施の形態1による一致検証方法を実施する一致検証装置の構成を示すブロック図である。図1において、HDL機能シミュレーション結果とFPGA上での実機動作結果との間での一致検証を行う一致検証装置1aは、機能シミュレーション部2と、シミュレーション結果抽出部3と、FPGA合成部4aと、実機検証部5と、実機検証結果抽出部6と、実行結果比較部7と、これらの各構成要素での処理データの入出力や保持に用いる記憶部8〜13とを備えている。

図3は、この発明の実施の形態2による一致検証方法を実施する一致検証装置の構成を示すブロック図である。なお、図3では、図1(実施の形態1)に示した構成要素と同一ないしは同等である構成要素には同一の符号が付されている。ここでは、この実施の形態2に関わる部分を中心に説明する。

2 機能シミュレーション部

3 シミュレーション結果抽出部

4a,4b FPGA合成部

5 実機検証部

6 実機検証結果抽出部

7 実行結果比較部

8 HDLデザイン記述の記憶部

9 アサーション記述の記憶部

10 シミュレーション結果履歴の記憶部

11 合成結果の記憶部

12 実機検証結果履歴の記憶部

13 一致検証結果の記憶部

20 比較処理を含む実機検証部

21 比較回路記述の記憶部

22 比較回路を含む合成結果の記憶部

Claims (10)

- 設計した半導体集積回路のHDLモデルの機能シミュレーションでの動作結果と前記HDLモデルを搭載したFPGAの実機検証での動作結果との一致を検証する一致検証方法であって、

(a)前記機能シミュレーションでのシミュレーション動作が前記半導体集積回路の仕様通りであるか否かをアサーションチェック機能を用いて検証する工程と、

(b)前記(a)の工程でのアサーションチェック機能によるアサーションチェックの結果履歴を抽出する工程と、

(c)前記HDLモデルとともに前記アサーションチェック機能を前記FPGA上に搭載するための論理合成処理及びマッピング処理を実施する工程と、

(d)前記(c)の工程にてHDLモデルを搭載した当該FPGAの実機検証での実機動作が仕様通りであるか否かを前記(c)の工程にて当該FPGA上に搭載した前記アサーションチェック機能を用いて検証する工程と、

(e)前記(d)の工程での実機検証における前記アサーションチェック機能によるアサーションチェックの結果履歴を抽出する工程と、

(f)前記(b)の工程で得られたアサーションチェック結果履歴と前記(e)の工程で得られたアサーションチェック結果履歴とを比較処理し、得られた差異を一致検証結果としてレポート出力する工程と

を含むことを特徴とする一致検証方法。 - 設計した半導体集積回路のHDLモデルの機能シミュレーションでの動作結果と前記HDLモデルを搭載したFPGAの実機検証での動作結果との一致を検証する一致検証方法であって、

(a)前記機能シミュレーションでのシミュレーション動作が前記半導体集積回路の仕様通りであるか否かをアサーションチェック機能を用いて検証する工程と、

(b)前記(a)の工程でのアサーションチェック機能によるアサーションチェックの結果履歴を抽出する工程と、

(c)前記HDLモデルとともに、前記アサーションチェック機能、前記アサーションチェック機能によるアサーションチェック結果履歴を抽出する機能、及び比較機能を当該FPGA上に搭載するための論理合成処理及びマッピング処理を実施する工程と、

(d)前記(c)の工程にてHDLモデルを搭載した当該FPGAの実機検証において前記のアサーションチェック機能及びアサーションチェック結果履歴を抽出する機能を用いて実機動作が仕様通りであるか否かについてのアサーションチェック結果履歴を取得し、得られたアサーションチェック結果履歴と前記(b)の工程にて得られたアサーションチェック結果履歴との差異を前記(c)の工程にて搭載された前記の比較機能を用いて検出し、得られた前記差異を一致検証結果としてレポート出力する工程と

を含むことを特徴とする一致検証方法。 - 前記アサーションチェック結果履歴には、合格したアサーションに関する情報と不合格したアサーションに関する情報との一方または双方が含まれていることを特徴とする請求項1または2に記載の一致検証方法。

- 前記レポート出力する差異には、当該差異が発生した時刻に関する情報及び発生回数が含まれていることを特徴とする請求項1または2に記載の一致検証方法。

- 前記レポート出力する差異は、比較結果を特定の条件によってフィルタリングし条件に合致したケースのみでの差異であることを特徴とする請求項4に記載の一致検証方法。

- 設計した半導体集積回路のHDLモデルの機能シミュレーションでの動作結果と前記HDLモデルを搭載したFPGAの実機検証での動作結果との一致を検証する一致検証装置であって、

前記機能シミュレーションでのシミュレーション動作が前記半導体集積回路の仕様通りであるか否かをアサーションチェック回路によって検証する機能シミュレーション部と、

前記機能シミュレーション部での前記アサーションチェック回路によるアサーションチェックの結果履歴を抽出するシミュレーション結果抽出部と、

前記HDLモデルとともに前記アサーションチェック回路を前記FPGA上に搭載するための論理合成処理及びマッピング処理を実施するFPGA合成部と、

前記FPGA合成部にてHDLモデルを搭載した前記FPGAの実機検証での実機動作が仕様通りであるか否かを前記FPGA合成部にて当該FPGA上に搭載した前記アサーションチェック回路を用いて検証する実機検証部と、

前記実機検証部での前記アサーションチェック回路によるアサーションチェックの結果履歴を抽出する実機検証結果抽出部と、

前記シミュレーション結果抽出部でのアサーションチェック結果履歴と前記実機検証結果抽出部でのアサーションチェック結果履歴とを比較処理し、得られた差異を一致検証結果としてレポート出力する実行結果比較部と

を備えていることを特徴とする一致検証装置。 - 設計した半導体集積回路のHDLモデルの機能シミュレーションでの動作結果と前記HDLモデルを搭載したFPGAの実機検証での動作結果との一致を検証する一致検証装置であって、

前記機能シミュレーションでのシミュレーション動作が前記半導体集積回路の仕様通りであるか否かをアサーションチェック回路によって検証する機能シミュレーション部と、

前記機能シミュレーション部での前記アサーションチェック回路によるアサーションチェックの結果履歴を抽出するシミュレーション結果抽出部と、

前記HDLモデルとともに、前記アサーションチェック回路、前記アサーションチェック回路による検証の結果履歴を抽出する回路、及び比較回路を当該FPGA上に搭載するための論理合成処理及びマッピング処理を実施するFPGA合成部と、

前記FPGA合成部によってHDLモデルを搭載した当該FPGAの実機検証において前記FPGA合成部によって搭載された前記のアサーションチェック機能及びアサーションチェック結果履歴を抽出する機能を用いて実機動作が仕様通りであるか否かについてのアサーションチェック結果履歴を取得し、得られたアサーションチェック結果履歴と前記シミュレーション結果抽出部によるアサーションチェック結果履歴との差異を前記FPGA合成部によって搭載された前記の比較回路を用いて検出し、得られた前記差異を一致検証結果としてレポート出力する実機検証部と

を備えていることを特徴とする一致検証装置。 - 前記アサーションチェック結果履歴には、合格したアサーションに関する情報と不合格したアサーションに関する情報との一方または双方が含まれていることを特徴とする請求項6または7に記載の一致検証装置。

- 前記レポート出力する差異には、当該差異が発生した時刻に関する情報及び発生回数が含まれていることを特徴とする請求項6または7に記載の一致検証装置。

- 前記レポート出力する差異は、比較結果を特定の条件によってフィルタリングし条件に合致したケースのみでの差異であることを特徴とする請求項9に記載の一致検証装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006344975A JP5259082B2 (ja) | 2006-12-21 | 2006-12-21 | 一致検証方法及び装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006344975A JP5259082B2 (ja) | 2006-12-21 | 2006-12-21 | 一致検証方法及び装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008158696A JP2008158696A (ja) | 2008-07-10 |

| JP5259082B2 true JP5259082B2 (ja) | 2013-08-07 |

Family

ID=39659546

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006344975A Expired - Fee Related JP5259082B2 (ja) | 2006-12-21 | 2006-12-21 | 一致検証方法及び装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5259082B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8088633B2 (en) | 2009-12-02 | 2012-01-03 | Ultratech, Inc. | Optical alignment methods for forming LEDs having a rough surface |

| JP5807452B2 (ja) * | 2011-08-29 | 2015-11-10 | 富士通株式会社 | 修正プログラム、修正装置、および修正方法 |

| JP5818762B2 (ja) * | 2012-09-14 | 2015-11-18 | 株式会社東芝 | プログラマブルロジックデバイス及びその検証方法 |

| US8856708B1 (en) * | 2013-07-12 | 2014-10-07 | Hamilton Sundstrand Corporation | Multi-tier field-programmable gate array hardware requirements assessment and verification for airborne electronic systems |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005346517A (ja) * | 2004-06-04 | 2005-12-15 | Renesas Technology Corp | 検証装置および検証方法 |

| JP2008107872A (ja) * | 2006-10-23 | 2008-05-08 | Oki Electric Ind Co Ltd | 半導体集積回路 |

-

2006

- 2006-12-21 JP JP2006344975A patent/JP5259082B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008158696A (ja) | 2008-07-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9824243B2 (en) | Model-based runtime detection of insecure behavior for system on chip with security requirements | |

| Huang et al. | Formal equivalence checking and design debugging | |

| JP5570701B2 (ja) | 集積回路の故障モード・影響分析を実行するための方法、およびそのためのコンピュータプログラム製品 | |

| Ahmad et al. | CirFix: Automatically repairing defects in hardware design code | |

| JP2006244073A (ja) | 半導体設計装置 | |

| US9286180B1 (en) | Final result checking for system with pre-verified cores | |

| US20170161403A1 (en) | Assertion statement check and debug | |

| CN118940687A (zh) | 芯片的安全设计方法、电子设备及存储介质 | |

| Zhang et al. | Automatic assertion generation for simulation, formal verification and emulation | |

| US10460060B2 (en) | Checking equivalence between changes made in a circuit definition language and changes in post-synthesis nets | |

| JP5259082B2 (ja) | 一致検証方法及び装置 | |

| US12197840B2 (en) | Techniques for modeling and verification of convergence for hierarchical domain crossings | |

| JP4492803B2 (ja) | 動作合成装置及びプログラム | |

| US20070074137A1 (en) | Database and method of verifying function of LSI using the same | |

| US20180121584A1 (en) | Verification support program medium, verification support method, and information processing device | |

| TWI488063B (zh) | 最佳化並驗證第一電路的設備,方法及電腦可讀取儲存媒體 | |

| US8751988B1 (en) | Computer-implemented methods and systems for automatic generation of layout versus schematic (LVS) rule files and regression test data suites | |

| CN103399982A (zh) | 一种数字硬件电路逻辑错误诊断机制 | |

| JP4899927B2 (ja) | テストパターン自動生成方法およびテストパターン自動生成プログラム | |

| CN110750956B (zh) | 逻辑闸阶层验证方法以及验证系统 | |

| JP2011203962A (ja) | 半導体集積回路の検証装置及び検証方法 | |

| JP5568779B2 (ja) | 論理検証方法及び論理検証システム | |

| JP2012073148A (ja) | 故障診断装置、故障診断方法、及び故障診断プログラム | |

| JP2011034517A (ja) | 等価性検証装置、そのデータ処理方法、およびプログラム | |

| US20060004557A1 (en) | System and method for reducing size of simulation value change files |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090807 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110201 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110401 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110607 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130424 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160502 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |