JP5232018B2 - エラー処理方法およびエラー処理装置 - Google Patents

エラー処理方法およびエラー処理装置 Download PDFInfo

- Publication number

- JP5232018B2 JP5232018B2 JP2008555429A JP2008555429A JP5232018B2 JP 5232018 B2 JP5232018 B2 JP 5232018B2 JP 2008555429 A JP2008555429 A JP 2008555429A JP 2008555429 A JP2008555429 A JP 2008555429A JP 5232018 B2 JP5232018 B2 JP 5232018B2

- Authority

- JP

- Japan

- Prior art keywords

- error

- memory

- write request

- storage area

- error correction

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000012545 processing Methods 0.000 title claims description 53

- 238000003672 processing method Methods 0.000 title claims description 9

- 238000012937 correction Methods 0.000 claims description 106

- 238000001514 detection method Methods 0.000 claims description 50

- 230000004044 response Effects 0.000 claims description 22

- 230000001737 promoting effect Effects 0.000 claims description 11

- 238000000034 method Methods 0.000 description 35

- 238000004891 communication Methods 0.000 description 18

- 208000011580 syndromic disease Diseases 0.000 description 10

- 230000006870 function Effects 0.000 description 6

- 238000012508 change request Methods 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 230000008859 change Effects 0.000 description 3

- 230000009471 action Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000001131 transforming effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1048—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices using arrangements adapted for a specific error detection or correction feature

- G06F11/1052—Bypassing or disabling error detection or correction

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/16—Error detection or correction of the data by redundancy in hardware

- G06F11/20—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Quality & Reliability (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

Description

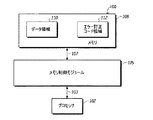

開示された装置は、第1記憶領域を有するメモリを備える。第1記憶領域は、データ領域とエラー訂正領域を備える。本装置は、第1記憶領域に関連する第1状態指標と、メモリに接続されるエラー訂正モジュールとを更に備える。エラー訂正を行なうエラー訂正モジュールは、第1記憶領域に関連する。本装置はアクセス制御モジュールを更に備える。アクセス制御モジュールは、第1状態指標に接続される第1入力と、エラー訂正モジュールに接続される出力とを有する。アクセス制御モジュールは、第1状態指標が第1状態になるのに応答して、第1記憶領域に対するエラー訂正、エラー検出、または任意のそれらの組合せのうちの1つを無効にする。

別の特定態様では、アクセス制御モジュールは、リセット信号を受信する第2入力を更に備える。アクセス制御モジュールは、第1状態指標を、リセット信号の受信に応答して第1状態にする。

特定態様では、第1状態指標は、第1記憶領域に関連する状態フラグビットである。

別の特定態様では、本方法は、リセット指示を受信することと、リセット指示の受信に応答して、エラー訂正状態指標を第1状態にすることとを含む。

特定態様では、本方法は、第1部分書込動作を第1全体書込動作に昇格後に、第1エラー訂正状態指標を第2状態に変更することを含む。

異なる図面中の同一の参照符号の使用は、同様または同一の要素を示す。

本発明の原理は、特定の装置に関して上述されるが、この記述が例示としてのみなされ、本発明の範囲に対する限定としてなされていないことが明白に理解されるべきである。

Claims (4)

- 第1記憶領域に関連する第1エラー訂正状態指標の状態を判定することであって、前記第1記憶領域には第1アクセス要求が行われることと;

前記第1エラー訂正状態指標が第1状態であるとの判定に応答して、前記第1アクセス要求に対するエラー処理を実行しないことと

を含むエラー処理方法であって、

前記エラー処理は、エラー検出とエラー訂正のうち少なくともエラー検出を含み、

前記第1アクセス要求が部分書込要求である場合、

前記第1エラー訂正状態指標が第1状態であるとの判定に応答して、前記第1アクセス要求に対するエラー処理を実行せずに、前記部分書込要求を全体書込要求に昇格させることと;

前記第1エラー訂正状態指標が第1状態でないとの判定に応答して、前記第1アクセス要求に対するエラー処理を実行し、前記部分書込要求を前記全体書込要求に昇格させないこととを含むことを特徴とする、エラー処理方法。 - 前記エラー処理方法は更に、前記全体書込要求に対するエラー訂正情報を算出することを含む、請求項1記載のエラー処理方法。

- 前記全体書込要求に基づく全体書込動作は、前記第1記憶領域に関連するエラー訂正データ単位の幅全体に亘って行なわれる、請求項1記載のエラー処理方法。

- データ領域とエラー訂正領域を含む記憶領域を備えるメモリと;

前記記憶領域に関連する状態指標と;

前記メモリに接続されるエラー処理モジュールであって、前記エラー処理モジュールは前記記憶領域に関連するエラー処理を行なうことと;

アクセス制御モジュールと

を備えるエラー処理装置であって、

前記アクセス制御モジュールは、前記状態指標に接続される第1入力と、前記エラー処理モジュールに接続される出力とを有し、

前記記憶領域に対して部分書込要求が行われた場合、前記アクセス制御モジュールは、

前記状態指標が所定状態であるとの判定に応答して、前記記憶領域に対するエラー処理を前記エラー処理モジュールに実行させないようにし、前記部分書込要求を全体書込要求に昇格させ、

前記状態指標が前記所定状態でないとの判定に応答して、前記記憶領域に対するエラー処理を前記エラー処理モジュールに実行させ、前記部分書込要求を全体書込要求に昇格させ、

前記エラー処理は、エラー検出とエラー訂正のうち少なくともエラー検出を含むことを特徴とする、エラー処理装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/359,329 US7617437B2 (en) | 2006-02-21 | 2006-02-21 | Error correction device and method thereof |

| US11/359,329 | 2006-02-21 | ||

| PCT/US2007/060659 WO2007103590A2 (en) | 2006-02-21 | 2007-01-18 | Error correction device and method thereof |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009527820A JP2009527820A (ja) | 2009-07-30 |

| JP2009527820A5 JP2009527820A5 (ja) | 2010-02-18 |

| JP5232018B2 true JP5232018B2 (ja) | 2013-07-10 |

Family

ID=38475622

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008555429A Expired - Fee Related JP5232018B2 (ja) | 2006-02-21 | 2007-01-18 | エラー処理方法およびエラー処理装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7617437B2 (ja) |

| JP (1) | JP5232018B2 (ja) |

| KR (1) | KR101291525B1 (ja) |

| TW (1) | TWI421679B (ja) |

| WO (1) | WO2007103590A2 (ja) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7783955B2 (en) * | 2006-01-18 | 2010-08-24 | Sandisk Il Ltd. | Method for implementing error-correction codes in flash memory |

| KR100972807B1 (ko) * | 2006-01-31 | 2010-07-29 | 후지쯔 가부시끼가이샤 | 에러 정정 코드 생성 방법 및 메모리 관리 장치 |

| US8725975B2 (en) * | 2007-01-03 | 2014-05-13 | Freescale Semiconductor, Inc. | Progressive memory initialization with waitpoints |

| JP4764945B2 (ja) * | 2007-06-20 | 2011-09-07 | 富士通株式会社 | キャッシュ制御装置、キャッシュ制御方法およびキャッシュ制御プログラム |

| US8239732B2 (en) * | 2007-10-30 | 2012-08-07 | Spansion Llc | Error correction coding in flash memory devices |

| FR2928769B1 (fr) * | 2008-03-14 | 2012-07-13 | Airbus France | Dispositif permettant l'utilisation d'un composant programmable dans un environnement radiatif naturel |

| US8122308B2 (en) * | 2008-06-25 | 2012-02-21 | Intel Corporation | Securely clearing an error indicator |

| US8112649B2 (en) * | 2009-03-17 | 2012-02-07 | Empire Technology Development Llc | Energy optimization through intentional errors |

| JP4905510B2 (ja) * | 2009-06-29 | 2012-03-28 | 富士通株式会社 | ストレージ制御装置及びストレージ装置のデータ回復方法 |

| WO2011031260A1 (en) * | 2009-09-10 | 2011-03-17 | Hewlett-Packard Development Company, L.P. | Memory subsystem having a first portion to store data with error correction code information and a second portion to store data without error correction code information |

| JP4837121B1 (ja) * | 2010-06-23 | 2011-12-14 | 株式会社東芝 | データ記憶装置及びデータ書き込み方法 |

| US8990660B2 (en) | 2010-09-13 | 2015-03-24 | Freescale Semiconductor, Inc. | Data processing system having end-to-end error correction and method therefor |

| US8549379B2 (en) * | 2010-11-19 | 2013-10-01 | Xilinx, Inc. | Classifying a criticality of a soft error and mitigating the soft error based on the criticality |

| US8738993B2 (en) * | 2010-12-06 | 2014-05-27 | Intel Corporation | Memory device on the fly CRC mode |

| US8560892B2 (en) * | 2010-12-14 | 2013-10-15 | Medtronic, Inc. | Memory with selectively writable error correction codes and validity bits |

| US8566672B2 (en) | 2011-03-22 | 2013-10-22 | Freescale Semiconductor, Inc. | Selective checkbit modification for error correction |

| US8607121B2 (en) * | 2011-04-29 | 2013-12-10 | Freescale Semiconductor, Inc. | Selective error detection and error correction for a memory interface |

| US8990657B2 (en) | 2011-06-14 | 2015-03-24 | Freescale Semiconductor, Inc. | Selective masking for error correction |

| US8522091B1 (en) | 2011-11-18 | 2013-08-27 | Xilinx, Inc. | Prioritized detection of memory corruption |

| US9612901B2 (en) * | 2012-03-30 | 2017-04-04 | Intel Corporation | Memories utilizing hybrid error correcting code techniques |

| US9411678B1 (en) * | 2012-08-01 | 2016-08-09 | Rambus Inc. | DRAM retention monitoring method for dynamic error correction |

| MY180992A (en) | 2013-03-13 | 2020-12-15 | Intel Corp | Memory latency management |

| US9696920B2 (en) * | 2014-06-02 | 2017-07-04 | Micron Technology, Inc. | Systems and methods for improving efficiencies of a memory system |

| US9852811B2 (en) * | 2014-11-13 | 2017-12-26 | Macronix International Co., Ltd. | Device and method for detecting controller signal errors in flash memory |

| US9423972B2 (en) * | 2014-11-17 | 2016-08-23 | Freescale Semiconductor, Inc. | Error recovery in a data processing system which implements partial writes |

| CN105607726B (zh) * | 2015-12-24 | 2018-11-23 | 浪潮(北京)电子信息产业有限公司 | 一种降低高性能计算集群内存功耗的方法及装置 |

| US11990199B2 (en) * | 2021-01-21 | 2024-05-21 | Micron Technology, Inc. | Centralized error correction circuit |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6384647U (ja) * | 1986-11-21 | 1988-06-03 | ||

| JPH04364552A (ja) * | 1991-06-12 | 1992-12-16 | Nec Corp | パリティ監視回路付きメモリ回路 |

| JPH10289164A (ja) * | 1997-04-16 | 1998-10-27 | Mitsubishi Electric Corp | メモリ制御方法およびメモリ制御装置 |

| US6119248A (en) * | 1998-01-26 | 2000-09-12 | Dell Usa L.P. | Operating system notification of correctable error in computer information |

| TW200517836A (en) * | 2003-11-18 | 2005-06-01 | Jtek Technology Corp | Buffer control framework and method between different memories |

| US6980873B2 (en) * | 2004-04-23 | 2005-12-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | System and method for real-time fault detection, classification, and correction in a semiconductor manufacturing environment |

| US7334179B2 (en) * | 2004-06-04 | 2008-02-19 | Broadcom Corporation | Method and system for detecting and correcting errors while accessing memory devices in microprocessor systems |

| TWI294126B (en) * | 2004-06-30 | 2008-03-01 | Hon Hai Prec Ind Co Ltd | System and method for testing memory |

| US20060143551A1 (en) * | 2004-12-29 | 2006-06-29 | Intel Corporation | Localizing error detection and recovery |

-

2006

- 2006-02-21 US US11/359,329 patent/US7617437B2/en active Active

-

2007

- 2007-01-18 WO PCT/US2007/060659 patent/WO2007103590A2/en active Application Filing

- 2007-01-18 JP JP2008555429A patent/JP5232018B2/ja not_active Expired - Fee Related

- 2007-01-18 KR KR1020087020334A patent/KR101291525B1/ko not_active IP Right Cessation

- 2007-01-30 TW TW096103282A patent/TWI421679B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| WO2007103590A2 (en) | 2007-09-13 |

| WO2007103590A3 (en) | 2008-12-04 |

| US20070220354A1 (en) | 2007-09-20 |

| TW200801932A (en) | 2008-01-01 |

| US7617437B2 (en) | 2009-11-10 |

| KR101291525B1 (ko) | 2013-08-08 |

| JP2009527820A (ja) | 2009-07-30 |

| TWI421679B (zh) | 2014-01-01 |

| KR20080098613A (ko) | 2008-11-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5232018B2 (ja) | エラー処理方法およびエラー処理装置 | |

| US5912906A (en) | Method and apparatus for recovering from correctable ECC errors | |

| US8261140B2 (en) | Uninitialized memory detection using error correction codes and built-in self test | |

| US6216247B1 (en) | 32-bit mode for a 64-bit ECC capable memory subsystem | |

| US8689041B2 (en) | Method for protecting data in damaged memory cells by dynamically switching memory mode | |

| JP5202130B2 (ja) | キャッシュメモリ、コンピュータシステム、及びメモリアクセス方法 | |

| US20080177938A1 (en) | Hybrid hard disk drive, computer system including the same, and flash memory DMA circuit for hybrid HDD | |

| US20070268905A1 (en) | Non-volatile memory error correction system and method | |

| US20130191705A1 (en) | Semiconductor storage device | |

| EP2870539B1 (en) | Using slow response memory device on a fast response interface | |

| US11157357B2 (en) | Operation methods of memory system and host, and computing system | |

| US9384091B2 (en) | Error code management in systems permitting partial writes | |

| CN103137215A (zh) | 向存储器提供低延时错误纠正码能力 | |

| US8555050B2 (en) | Apparatus and method thereof for reliable booting from NAND flash memory | |

| US7689895B2 (en) | On-the fly error checking and correction CODEC system and method for supporting non-volatile memory | |

| US20120324321A1 (en) | Co-hosted cyclical redundancy check calculation | |

| WO2007088597A1 (ja) | エラー訂正コード生成方法及びメモリ管理装置 | |

| US20030217325A1 (en) | Method and apparatus for providing error correction within a register file of a CPU | |

| US6901551B1 (en) | Method and apparatus for protection of data utilizing CRC | |

| US11269715B2 (en) | Systems and methods for adaptive proactive failure analysis for memories | |

| US8667325B2 (en) | Method, apparatus and system for providing memory sparing information | |

| US20110107143A1 (en) | Cache system | |

| CN114333968A (zh) | 存储器的控制方法、存储器控制器及电子装置 | |

| JPH01194046A (ja) | メモリアクセス方式 | |

| CN113515405A (zh) | 地址管理方法和装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091222 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091222 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120607 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120612 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120912 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20121010 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130131 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130207 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130305 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130322 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160329 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |