JP5154907B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5154907B2 JP5154907B2 JP2007329780A JP2007329780A JP5154907B2 JP 5154907 B2 JP5154907 B2 JP 5154907B2 JP 2007329780 A JP2007329780 A JP 2007329780A JP 2007329780 A JP2007329780 A JP 2007329780A JP 5154907 B2 JP5154907 B2 JP 5154907B2

- Authority

- JP

- Japan

- Prior art keywords

- interlayer insulating

- insulating film

- semiconductor device

- manufacturing

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Formation Of Insulating Films (AREA)

Description

そこで、シラノール基を低減させる方法として、層間絶縁膜にシリル化などの処理を行うことが提案されていた。例えば、層間絶縁膜の形成プロセス中に、三フッ化窒素(NF3)ガスに曝露する方法(例えば、特許文献1,2参照)や、層間絶縁膜の形成プロセス後にシリル化剤処理を行う方法(例えば、特許文献3参照)などを用いれば、層間絶縁膜中のシラノール基を低減させることができ、特性の劣化を抑えることができる。

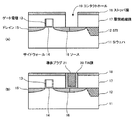

まず、本実施形態の概要について図面を参照して説明する。

基板上の層間絶縁膜の製造方法を時系列的に4つの製造工程(図1(A)〜図1(D))に分けて、各工程を模式的に示している。以下、各製造工程に沿って説明する。

半導体基板1上に、のちに形成される層間絶縁膜2の組成材料2aを塗布する(図1(B))。

疎水化処理剤3と反応した組成材料2aを固化して、層間絶縁膜2を形成する(図1(D))。

以上のように、半導体基板1上に塗布された組成材料2aを固化しながら、層間絶縁膜2を疎水化する疎水化処理剤3を組成材料2aに導入して形成される層間絶縁膜2を備える半導体装置では、疎水化処理剤3と組成材料2aとが反応して、特性の劣化を招き信頼性の低下の一因であった親水性を示す層間絶縁膜2中のシラノール基などを脱離させて、疎水化し、リーク電流を低減でき、消費電力を抑え、信頼性を向上させることが可能となる。

次に、上記概要に基づいた本実施の形態を詳細に説明する。

実施例1に対して、層間絶縁膜の組成材料の塗布後、疎水化処理剤を導入する場合を、同様に実施例2とする。なお、実施例2の場合、疎水化処理剤導入後に、層間絶縁膜の組成材料を固化して、層間絶縁膜を形成することになる。

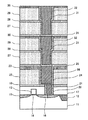

図2〜図5は、本実施の形態における半導体装置の製造方法の要部断面模式図である。

(実施例1)

実施例1では、層間絶縁膜前駆体塗布溶液を乾燥および焼成して固化する工程中に、層間絶縁膜22を疎水化させる疎水化処理剤(不図示)を導入する。

[ステップ1]:ストッパ膜18、TiN膜20および導体プラグ21上に、層間絶縁膜前駆体塗布溶液をスピン塗布法によって塗布する。

[ステップA]:層間絶縁膜前駆体塗布溶液上に、ベーパー法によって、疎水化処理剤を導入する。

(実施例2)

実施例2では、実施例1と異なり、層間絶縁膜前駆体塗布溶液を塗布した後に、[ステップA]が行われる。すなわち、実施例2における層間絶縁膜22の製造工程は以下のような順序で行われる。

[ステップA]:層間絶縁膜前駆体塗布溶液上に、ベーパー法によって、疎水化処理剤を導入する。

[ステップ3]:N2雰囲気中にて、30分間、400℃で焼成を行う。そして、層間絶縁膜22が形成される。

なお、疎水化処理剤には、シリル化剤が用いられ、特に、酸素原子(O)、炭素原子(C)、水素原子(H)および窒素原子(N)のうち少なくとも1種とSi原子とから構成される化合物が用いられる。これらの原子は比較的小さいため、余計な反応が無く、十分な反応性を有する。

以上の工程によって、配線幅が0.1μm以下であって、多層配線の櫛歯パターン構造を備える半導体装置が形成される。

図6は、本実施の形態で用いる疎水化処理剤の表である。

また、TDDB試験においては、電界強度を3.3MV/cm、SM試験においては、温度を150℃、時間を1024時間の試験条件で行った。

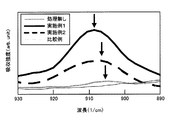

図8は、本実施の形態におけるSiH基の吸収強度を示すグラフである。

半導体基板を形成する第1工程と、

前記半導体基板上に、前記層間絶縁膜の組成材料を塗布する第2工程と、

前記組成材料を固化して、前記層間絶縁膜を形成する第3工程とともに、前記組成材料に前記層間絶縁膜を疎水化する疎水化処理剤を導入する第4工程と、

を有することを特徴とする半導体装置の製造方法。

(付記3) 前記疎水化処理剤は、含まれるシリコン原子のうち少なくとも1つが反応性官能基を2以上有したシリル化剤であること特徴とする付記1または2記載の半導体装置の製造方法。

(付記6) 前記層間絶縁膜の誘電率が2.7以下、であることを特徴とする付記1乃至5のいずれか1項に記載の半導体装置の製造方法。

前記半導体基板上に形成された層間絶縁膜と、

を有し、

前記層間絶縁膜は、

前記層間絶縁膜の組成材料と、前記組成材料に導入された、前記層間絶縁膜を疎水化する疎水化処理剤とを含むことを特徴とする半導体装置。

2 層間絶縁膜

2a 組成材料

3 疎水化処理剤

Claims (3)

- 層間絶縁膜を備える半導体装置の製造方法において、

半導体基板を形成する第1工程と、

前記半導体基板上に、前記層間絶縁膜の組成材料を塗布する第2工程と、

前記組成材料を第1の温度で加熱し前記組成材料の固化を開始する第3工程と、

前記第3工程後に、前記半導体基板を第2の温度で加熱した状態で前記組成材料に前記層間絶縁膜を疎水化する疎水化処理剤をベーパー法によって導入する第4工程と、

前記第4工程後に、第3の温度で、前記疎水化処理剤を導入した前記組成材料を加熱し、前記組成材料の固化を終える第5工程と、

を有することを特徴とする半導体装置の製造方法。 - 前記疎水化処理剤は、含まれるシリコン原子のうち少なくとも1つが反応性官能基を2以上有したシリル化剤であること特徴とする請求項1記載の半導体装置の製造方法。

- 前記疎水化処理剤は、ジメチルエトキシシラン、ヘキサメチルジシラザン、テトラメチルジシラザン、ジメチルアミノトリメチルシラン、ジメチルアミノジメチルシラン、ビス(ジメチルアミノ)ジメチルシラン、ビス(ジエチルアミノ)ジメチルシランまたはトリス(ジメチルアミノ)メチルシランであることを特徴とする請求項1または2記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007329780A JP5154907B2 (ja) | 2007-06-29 | 2007-12-21 | 半導体装置の製造方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007172213 | 2007-06-29 | ||

| JP2007172213 | 2007-06-29 | ||

| JP2007329780A JP5154907B2 (ja) | 2007-06-29 | 2007-12-21 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009033089A JP2009033089A (ja) | 2009-02-12 |

| JP5154907B2 true JP5154907B2 (ja) | 2013-02-27 |

Family

ID=40403235

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007329780A Active JP5154907B2 (ja) | 2007-06-29 | 2007-12-21 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5154907B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011040634A (ja) * | 2009-08-13 | 2011-02-24 | Ulvac Japan Ltd | 多孔質膜の前駆体組成物、多孔質膜及びその作製方法、並びに半導体装置 |

| JP2012059958A (ja) * | 2010-09-09 | 2012-03-22 | Rohm Co Ltd | 半導体装置およびその製造方法 |

| JP7446097B2 (ja) * | 2019-12-06 | 2024-03-08 | 東京応化工業株式会社 | 表面処理剤及び表面処理方法 |

| JP2024519069A (ja) * | 2021-05-19 | 2024-05-08 | バーサム マテリアルズ ユーエス,リミティド ライアビリティ カンパニー | 高弾性率を有する膜を堆積させるための新規な前駆体 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6042994A (en) * | 1998-01-20 | 2000-03-28 | Alliedsignal Inc. | Nanoporous silica dielectric films modified by electron beam exposure and having low dielectric constant and low water content |

| US6770572B1 (en) * | 1999-01-26 | 2004-08-03 | Alliedsignal Inc. | Use of multifunctional si-based oligomer/polymer for the surface modification of nanoporous silica films |

-

2007

- 2007-12-21 JP JP2007329780A patent/JP5154907B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009033089A (ja) | 2009-02-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7968451B2 (en) | Method for forming self-assembled mono-layer liner for Cu/porous low-k interconnections | |

| US20090258487A1 (en) | Method for Improving the Reliability of Low-k Dielectric Materials | |

| US7655576B2 (en) | Insulator film, manufacturing method of multilayer wiring device and multilayer wiring device | |

| KR100887225B1 (ko) | 반도체 디바이스의 제조 방법 | |

| DE102014118991B4 (de) | Verfahren zum Bilden einer integrierten Schaltkreisstruktur | |

| US20080124919A1 (en) | Cleaning processes in the formation of integrated circuit interconnect structures | |

| JP2004241776A (ja) | 低k誘電体フイルムの化学的処理 | |

| CN1832128A (zh) | 制造互连结构的方法及由其制造的互连结构 | |

| JP2008117903A (ja) | 半導体装置の製造方法 | |

| CN102646666A (zh) | 作为化学-机械抛光停止层的介电保护层 | |

| US9059259B2 (en) | Hard mask for back-end-of-line (BEOL) interconnect structure | |

| US20060220251A1 (en) | Reducing internal film stress in dielectric film | |

| JP2004088047A (ja) | 半導体装置の製造方法 | |

| JP2006128543A (ja) | 電子デバイスの製造方法 | |

| JP2001223269A (ja) | 半導体装置およびその製造方法 | |

| JP5154907B2 (ja) | 半導体装置の製造方法 | |

| US20080188074A1 (en) | Peeling-free porous capping material | |

| US8390135B2 (en) | Semiconductor device | |

| JP4675258B2 (ja) | 半導体装置の製造方法および半導体装置 | |

| JP2013143392A (ja) | 多孔質膜の製造方法及び半導体装置の製造方法 | |

| JP4567587B2 (ja) | 半導体装置の製造方法 | |

| JP2000273176A (ja) | 絶縁膜形成方法及び半導体装置 | |

| JP4684866B2 (ja) | 半導体装置の製造方法 | |

| US20160190002A1 (en) | High Boiling Temperature Solvent Additives for Semiconductor Processing | |

| JP5304033B2 (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100820 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110825 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110830 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111026 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120117 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120413 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20120420 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20120525 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121031 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121206 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151214 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5154907 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |