JP5148029B2 - 構成可能な機能ユニットを備えるデータプロセッサ及びそのようなデータプロセッサを使用する方法 - Google Patents

構成可能な機能ユニットを備えるデータプロセッサ及びそのようなデータプロセッサを使用する方法 Download PDFInfo

- Publication number

- JP5148029B2 JP5148029B2 JP2000600174A JP2000600174A JP5148029B2 JP 5148029 B2 JP5148029 B2 JP 5148029B2 JP 2000600174 A JP2000600174 A JP 2000600174A JP 2000600174 A JP2000600174 A JP 2000600174A JP 5148029 B2 JP5148029 B2 JP 5148029B2

- Authority

- JP

- Japan

- Prior art keywords

- instruction

- instructions

- reconfigurable

- bits

- functional unit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30181—Instruction operation extension or modification

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/78—Architectures of general purpose stored program computers comprising a single central processing unit

- G06F15/7867—Architectures of general purpose stored program computers comprising a single central processing unit with reconfigurable architecture

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3885—Concurrent instruction execution, e.g. pipeline, look ahead using a plurality of independent parallel functional units

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3885—Concurrent instruction execution, e.g. pipeline, look ahead using a plurality of independent parallel functional units

- G06F9/3893—Concurrent instruction execution, e.g. pipeline, look ahead using a plurality of independent parallel functional units controlled in tandem, e.g. multiplier-accumulator

- G06F9/3895—Concurrent instruction execution, e.g. pipeline, look ahead using a plurality of independent parallel functional units controlled in tandem, e.g. multiplier-accumulator for complex operations, e.g. multidimensional or interleaved address generators, macros

- G06F9/3897—Concurrent instruction execution, e.g. pipeline, look ahead using a plurality of independent parallel functional units controlled in tandem, e.g. multiplier-accumulator for complex operations, e.g. multidimensional or interleaved address generators, macros with adaptable data path

Description

【技術分野】

本発明は、その効果を実行時に再定義することが可能な、再構成可能な命令(reconfigurable instructions)を実行することができる構成可能な(configurable)機能ユニットを含むプロセッサを用いてコンピュータプログラムを実行する方法に関する。また、本発明は斯様な方法を使用するデータプロセッサにも関する。

【0002】

【背景技術】

構成可能な機能ユニットを含むプロセッサを用いてコンピュータプログラムを実行する方法は、John Schewelにより編集された1995年の“会議録、高速回路基板開発及び再構成可能なコンピューティング用のFPGA”(SPIE2607会議録)の第92〜103頁に公開されたMichael J. Wirthlin及びBrad L. Hutchingsによる“DISC:ダイナミック命令セットコンピュータ”なる題名の文献から既知である。

【0003】

この文献は、フィールドプログラマブルゲートアレイ(FPGA)を含む機能ユニットを備えるようなデータプロセッサを記載している。FPGAは、出力信号を入力信号の関数として生成するような回路である。FPGAは、構成可能な回路素子の行及び列のマトリクスからなる。入力と出力との関係は、該FPGAの異なる回路素子間の接続及びこれら回路素子の機能を制御するメモリセルに情報をロードすることにより構成(configure)することができる。

【0004】

構成プログラム(configuration program)の使用は、マイクロプログラムからは区別されるべきである。周知のように、マイクロプログラムは、機能回路を制御するために使用される個々の制御信号を規定する。異なる制御信号が、マイクロコードの実行の異なる段階に対して、且つ、異なる命令に対して規定される。対照的に、構成プログラムのビットを記憶する該当メモリセルは、入出力関係に対して不変的制御を有する。即ち、これらメモリセルは、実行されている命令及び如何なる実行段階とも無関係に回路素子を不変的に制御する。通常、制御される入出力関係は、時間的に連続した回路特性である。

【0005】

構成プログラムは、異なる構成可能な命令を実行するために導出される。Whirthlin他による上記文献によれば、FPGAマトリクスは回路素子の行の多数のバンド(bands)に分割される。各構成プログラムは、1以下のバンドしか占めることはなく、如何なるバンドにも配置することができる。実行時において、或る構成可能な命令に遭遇した場合は、この命令用の構成プログラムが上記バンドのうちの何れかに既にロードされているかが判断される。もしそうなら、この命令は該構成プログラムを使用して実行される。もしそうでない場合は、上記命令用の構成プログラムがロードされ、次いで、この構成プログラムを使用して該命令が実行される。

【0006】

同時には、限られた数の構成プログラムしかロードすることができない。新たな構成プログラムをロードする余裕がない場合は、他の構成可能な命令用の構成プログラムが当該バンドから削除され、該新たな構成プログラム用の余裕を作る。

【0007】

構成プログラムがロードされる毎に、かなりのオーバーヘッドが存在する。前記文献によれば、このオーバーヘッドは、ロードされている構成プログラムを、他の構成プログラムをロードするために削除するまで、可能な限り長く維持することにより最小化される。このようにして、構成プログラムの一種のキャッシュが実現され、これが、構成プログラムが繰り返し使用される場合はオーバーヘッドを最小化する。しかしながら、依然として、構成プログラムをロードするためのかなりのオーバーヘッドが存在する。

【0008】

【発明の開示】

本発明の一つの目的は、なかでも、構成プログラムをロードするために必要とされるオーバーヘッドを低減することにある。本発明の他の目的は、一緒にロードされた状態に維持することができる構成プログラムの数を増加させ、これにより構成プログラムが少ない回数しかロードする必要がないようにすることにある。また、本発明の他の目的は、コンピュータプログラム用に必要とされる全ての構成プログラムを記憶するのに要するメモリの量を低減することにある。

【0009】

本発明によるコンピュータプログラムを実行する方法の一実施例が請求項1に記載されている。この実施例によれば、構成可能な命令の組み合わせが定義され、個別にではなく、組み合わせとしてロードされる。当該プログラムを実行する前に、各々が少なくとも2つの構成可能な命令からなる1以上の組み合わせが選択される。典型的には、各組み合わせは、当該コンピュータプログラムの1以上の連続した命令の領域に関連付けられる。当該プログラムの該特定の領域が実行される場合、該領域に関連する組み合わせの全ての構成可能な命令用の構成プログラムがロードされる。

【0010】

上記命令の組み合わせ及びそれらに関連する領域は、当該プログラムを実行する前に、構成プログラムをロードするためのオーバーヘッドが最小となるように、即ち、当該組み合わせのために選択される構成可能な命令が該組み合わせに属さない他の構成可能な命令により中断されることなく連続的に発生するように(もし、これらの他の構成可能な命令が他の組み合わせをロードする必要性を生じるであろうようなら)、選択することができる。このように、オーバーヘッドを最小化するためになされる作業は、実行時というよりはコンパイル時になされる。

【0011】

更に、多くのコンピュータプログラムに関して、命令サイクルカウントは、オペランドにおける同一位置からのビットの使用又は類似しているが僅かに異なる論理関数の計算のような強い類似性を持つ命令の組み合わせを用いて最小化することができる。これらの命令は、当該組み合わせにおける全ての命令により共通に使用されるハードウェア資源と、個々の命令(又は、これら命令の部分集合)に特有の幾つかのハードウェア資源とをプラスしたものを用いて実現することができる。このように、上記組み合わせにおいてロードすることができる命令の数が増加される。

【0012】

本発明による方法の他の実施例によれば、上記命令の組み合わせ用の構成プログラムは、該プログラムが再構成可能な機能ユニットにおける上記組み合わせ内の異なる命令の再構成可能なハードウェア資源の使用を相互最小化(cross-minimize)するように選択される。幾つかの機能に対する資源使用の相互最小化とは、資源使用が各機能に関して独立に最小化されるのではなく、全ての機能を実行する全ての構成プログラムの設計空間において極小が追求されることを意味する。上記組み合わせにおける異なる命令の間の相互最小化の結果として、資源使用が各命令個別に対して最小化された場合に上記組み合わせに対して必要とされたであろうよりも、少ないハードウェア資源しか必要とされない。

【0013】

構成可能な機能ユニットにおけるハードウェア資源の例は、回路素子及びプログラム可能な接続部である。典型的な構成可能な機能ユニットは、オン又はオフとなるように構成することができると共に回路素子を互いに、他の回路型式の回路素子に又は当該機能ユニットの入力端子若しくは出力端子に接続するような接続部を備える多数の同一の回路素子を含んでいる。典型的には、限られた数の斯様な接続部のみを構成することが可能である。例えば、幾つかの回路素子のみが、直接に入力端子若しくは出力端子、又は所与の他の回路素子に接続することができる。

【0014】

構成プログラムが異なる命令に対して独立に選択されるとすると、或る組み合わせにおける或る命令用の各構成プログラムは、それらハードウェア資源がたとえ実際に使用されないであろう場合でも、該組み合わせ内の他の命令用の他の構成プログラムにより使用するために、これらハードウェア資源を空き状態にしておかなければならない。相互最小化により、1つの命令用の構成プログラムは、他の命令のために使用されない如何なるハードウェアも使用することができる。

【0015】

更に悪いことに、当該組み合わせにおける他の命令を考慮しない、或る命令用の構成プログラムに使用するための回路素子の選択は、この選択が当該接続部を入力端子又は出力端子に固定するような場合、追加の資源使用の原因となる。これは、他の命令用の入力端子/出力端子接続部を最適に選択することによるハードウェア資源使用を最小化する可能性を取り除くことになる。

【0016】

同一の組み合わせにおける異なる命令のハードウェア資源の使用を相互最小化することにより、斯様なハードウェア資源の浪費を防止することができる。更に、異なる命令の間で、共通のハードウェア資源を共用することが可能になる。ハードウェア使用を相互最小化することにより、共通のハードウェア資源が当該命令の組み合わせに対して2回以上割り付けられねばならないということが防止される。

【0017】

本発明による方法の他の実施例によれば、当該組み合わせ内の異なる命令を選択するための、及び上記異なる命令によるオペランドデータを処理するためのハードウェア資源使用が、相互最小化される。通常、命令選択は、演算コードのオペランドデータ処理回路を可能化する信号への解読を含んでいる。該実施例においては、命令及びオペランドデータ処理用の構成プログラムのハードウェア資源使用が互いに独立に最小化された場合よりも、少ない数のハードウェア資源しか命令選択及びオペランドデータ処理用として必要とされない。

【0018】

好ましくは、当該プロセッサはパイルライン化される。このことは、命令処理が、命令解読とオペランドフェッチとをプラスした段階、命令実行段階及び結果の書き戻し段階等の順次の段階に分割されることを意味する。パイプライン化されたプロセッサにおいては、順次の命令の命令処理の異なる段階が互いに並列に実行される。命令処理の構成可能な部分は、上記実行段階で生じる。本発明の一実施例によれば、オペランドデータ処理と、異なる命令の間を区別する命令選択ビットの使用との両方が、該構成可能な命令の処理の実行段階で生じる。

【0019】

本発明による方法の他の実施例によれば、上記の再構成可能な機能ユニットは再構成可能な交点スイッチ(cross-point switch)を、オペランドデータ用の入力端子と、該交点スイッチの各出力端子を異なる論理合成回路へ接続する接続ラインとの間に含む。

【0020】

本発明の、これら及び他の特徴は添付図面を参照して説明されるであろう。

【0021】

【発明を実施するための最良の形態】

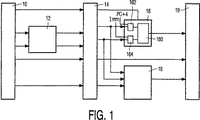

図1は、構成可能な命令をサポートするプロセッサのアーキテクチャを示している。本発明に影響を与えない該プロセッサアーキテクチャの種々の特徴は、明瞭化のために図1から削除されていることに注意されたい。例示として、パイプライン化されたRISCアーキテクチャが考察されるが、本発明は斯様なアーキテクチャに限定されるものではない。例えば、代わりにCISCアーキテクチャ又はDSPアーキテクチャを使用することもできる。該実施例は、異なるパイプライン段を分離する3つのレジスタ10、14及び19を備えるパイプライン化されたプロセッサを示している。命令レジスタ10は、当該パイプラインの源に位置する。この命令レジスタ10のオペランド参照フィールド出力端子は、レジスタファイル12の入力端子に接続されている(例として、これらのフィールドは5ビット幅とする)。このレジスタファイル12の出力端子(例えば、ビット幅w=32)は、上記命令レジスタ10の他の出力端子と共に、実行段レジスタ14に結合されている。上記他の出力端子は、結果アドレス出力端子(例として、5ビット幅)及び構成可能な命令の選択コード用出力端子(例として、11ビット幅)を含んでいる。

【0022】

レジスタファイル12からのデータを通過させる実行段レジスタ14の出力端子は、ALU機能ユニット16と構成可能な機能ユニット18とに並列に結合されている。ALU機能ユニット16はALU160を含み、該ALUの入力端子はマルチプレクサ162及び164に各々結合されている。各マルチプレクサ162、164は実行段レジスタ14の出力端子に接続されている。マルチプレクサ162及び164は、プログラムカウンタ値及び上記命令レジスタからの中間値を各々入力する入力端子を更に有している(これらの入力端子用の接続は図示されていない)。

【0023】

上記実行段レジスタ14の他の出力端子は前記の構成可能な命令の選択コードを構成可能な機能ユニット18に受け渡し、結果アドレスは書き戻し段レジスタ19に渡される。ALU機能ユニット16及び構成可能な機能ユニット18の出力端子は、書き戻し段レジスタ19に接続されている。上記実行段レジスタはレジスタファイル12に対し、ALU機能ユニット16又は構成可能な機能ユニット18の結果をレジスタファイル12における結果オペランドアドレスにより示されるロケーションに書き込むための接続部(図示略)を有している。

【0024】

他の機能ユニット(例えば、メモリアクセスユニット)、制御ライン、分岐回路、命令解読回路及びレジスタ14、19等に対する入力を選択するためのマルチプレクサのような種々の回路は、明瞭化のために図1から削除されている。

【0025】

動作時に、図1のアーキテクチャは、パイプライン化された実行機構を達成する。順次の命令は、順次のクロックサイクルにおいて命令レジスタ10にロードされる。或る命令がロードされた後のクロックサイクルにおいて、そのオペランド参照が、レジスタファイル12からオペランドをロードするために使用される。このクロックサイクルは、例えば機能ユニット16、18(又は図示せぬ他のもの)の何れが当該命令を実行するかの選択のような、命令解読を含むことができる。このサイクルの終了時に、オペランド、結果オペランドアドレス及び構成可能な命令の選択コードが、実行に要する全ての他のデータ(図示略)と共に、実行段レジスタ14にロードされる。次のクロックサイクルにおいては、この情報は機能ユニット16、18(及び/又は図示せぬ他の機能ユニット)に渡され、結果を得るために処理される。このクロックサイクルの終了時に、選択された機能ユニット16、18からの結果及び結果オペランドアドレスが、書き戻し段レジスタ19にロードされる。この次のサイクルの後のクロックサイクルにおいて、上記結果がレジスタファイル12に書き戻される。

【0026】

当該命令の演算コードフィールドが構成可能な命令を選択した場合は、構成可能な機能実行ユニット18が該命令を実行して結果を生成するために選択される。この場合、当該命令における構成可能な命令の選択コードは、どの特定の構成可能な命令が実行されるかを決定するために使用される。

【0027】

勿論、本発明から逸脱することなく、各々が異なる命令の組み合わせを用いて構成された2以上の構成可能な機能ユニットを並列に設け、所要の構成プログラムの交換のためのオーバーヘッドなしで、2以上の組み合わせを同時に利用可能にすることもできる。

【0028】

図2は、構成可能な機能ユニットの一実施例を示している。これは、基本的にそれ自体既知のCPLD(複合プログラマブル論理装置)コアである。該構成可能な機能ユニットは、前記オペランドの各々のwビット及び上記構成可能な命令の選択コードのNビット(例として、N=4)を入力するための入力ポート20a、20b及び22を有している。これら入力ポートは交点スイッチ24の入力端子に接続されている。この交点スイッチ24は多数の出力端子を有している。該交点スイッチ24は、その2*w+N個の入力端子の各々が、当該構成可能な機能ユニットにロードされる構成プログラムの制御の下で上記出力端子のうちの何れかに接続することができるように設計されている。

【0029】

交点スイッチ24の出力端子は論理ブロック26a及び26bの各々に接続されている。これら論理ブロック26a及び26bの出力端子は、当該構成可能な機能ユニットの出力ポート28に結合されている。例示として、各々が36個の入力端子とw/2(例えば、16)個の出力端子を備える2つの論理ブロック26a及び26bが示されている。2つの論理ブロック26a、26bのw/2ビットの出力は一緒にwビットの結果出力を形成する。

【0030】

該構成可能な機能ユニットは、再構成制御回路23を含んでいる。この再構成制御回路23は、前記構成可能な命令の選択コードのうちの交点スイッチ24に供給されなかったビットを入力する入力端子を含んでいる。該再構成制御回路23は、交点スイッチ24及び論理ブロック26a、26bに接続された出力端子を有している。

【0031】

動作時において、制御回路23は、上記命令選択コードの入力されたビットを、当該構成可能な機能ユニットが現在実行するようにプログラムされている再構成可能な命令の組み合わせの対応するビットと比較する。好ましくは、上記命令選択コードのビットの部分集合が当該組み合わせを示すために使用され、残りのビットが該組み合わせ内の構成可能な命令を示すようにする。上記選択コードが、異なる組み合わせからの命令が実行されるべきであることを示している場合は、上記再構成制御回路23は、メモリ(図示略)から該新たな組み合わせの全命令用の構成プログラムをロードし、交点スイッチ24及び論理ブロック26a、26bを該新たな組み合わせが要するように再プログラムする。その後、該新たな組み合わせからの命令は実行することができる。

【0032】

新たな組み合わせが一旦ロードされるか、又は既にロードされていた組み合わせからの命令が選択されると、該構成可能な機能ユニットは該命令を処理する。この場合、前記交点スイッチに供給されるN個の命令ビットが、どの命令(当該構成可能な機能ユニットにロードされた命令の組み合わせからの)に従いオペランドが処理されるかを決定する。

【0033】

構成プログラムのロードの最も容易な実施は、該構成プログラムがロードされるまで当該プロセッサによる更なる命令の実行を停止(stall)させることである。しかしながら、もっと少ない命令サイクルオーバーヘッドしか要さない他の構成を使用することもできる。例えば、当該構成プログラムのロードを起動するために、先駆(precursor)命令を使用することもできる。該先駆命令は、上記組み合わせからの構成可能な命令が使用されるであろうことを示す。該先駆命令自体は構成プログラムを必要としないが、指示された構成プログラムのロードを起動する。

【0034】

他の例では、当該プロセッサは通常の(例えば、ALU)命令のサブルーチンに跳び、構成プログラムがロードされなければならない又はロードされつつある場合は、これら命令が上記構成可能な命令を実行する。これは、アドレス指定されたオペランドレジスタの内容をサブルーチン呼び出しスタックに配置し、該サブルーチンを呼び出し、該サブルーチンからの帰還後に上記の構成可能な命令のアドレス指定された結果レジスタに上記呼び出しスタックからの結果を戻すことにより達成することができる。

【0035】

図3は、図2の構成可能な機能ユニットに使用する論理ブロックの一例の実施例を示している(それ自体は、CPLDから既知である)。この論理ブロックはPALアレイ30とPLAアレイ32とを含み、両者は前記交点スイッチ24の全出力端子に結合されている。アレイ30及び32の出力端子には、アンドゲート34a〜34b及び35a〜35cが記号的に図示されている。例示として、PALアレイ30に対しては64個のアンドゲート34a〜34bが存在し、PLAアレイ32に対しては32個のアンドゲート35a〜35cが存在する。

【0036】

アレイ30、32は列導体及び行導体(図示略)から構成され、各列は交点スイッチ24の各出力端子に対応し(好ましくは、各列は各信号と、それらの否定の両者に対して存在するようにする)、各行は当該論理ブロックのアンドゲート34a〜34b及び35a〜35cに対応している。行と列との交点には、トランジスタとメモリセルとが存在する(図示略)。メモリセルはトランジスタが駆動されるか否かを制御する。トランジスタは、駆動されると、アンドゲート34a〜34b及び35a〜35bの入力を形成し、これらアンドゲート34a〜34b及び35a〜25cは、それらのトランジスタが駆動された列導体の論理レベルのアンドを出力する。

【0037】

上記PLAアレイのアンドゲート35a〜35cの出力端子は、マトリクス33の行導体に接続されている。このマトリクスの列導体はオアゲート36a〜36cに接続されるように図示されている。行及びの交点には、トランジスタとメモリセル(図示略)が存在する。メモリセルはトランジスタが駆動されるか否かを制御する。トランジスタは、駆動されると、オアゲート36a〜36cの入力を形成し、これらオアゲート36a〜36cは、それらのトランジスタが駆動された行導体の論理レベルのオアを出力する。

【0038】

PALアレイ30の出力端子は、4つの群毎に、更なるオアゲート38a〜38bに接続されている。各オアゲート36a〜36cは、上記更なるオアゲート38a〜38bの各々の入力端子に結合された出力端子を有している。例示として、16個のオアゲート36a〜36cと、16個の更なるオアゲート38a〜38bが存在する。更なるオアゲート38a〜38bの各々は、プログラム可能なインバータ/非インバータ39a〜39bを介して当該論理ブロックの出力ビットラインに接続されている。各インバータ/非インバータ39a〜39bに対してメモリセル(図示略)が設けられ、これらメモリセルの内容が、これらインバータ/非インバータ39a〜39bが反転するか否かを制御する。

【0039】

上記論理ブロックの論理機能は、PALマトリクス30、PLAマトリクス32、マトリクス33及びインバータ/非インバータ39a〜39b内の各交点におけるトランジスタの駆動を制御するメモリセルに、構成プログラムのビットをロードすることによりプログラムすることができる。

【0040】

命令選択コードのNビットは、前記交点スイッチ24に供給される。これらNビットは、前記オペランドのビットと同様の方法で供給される。当該構成可能な機能ユニットの構成プログラムは、これらNビットをオペランドビットの何れかのように扱う自由度を有している。上記Nビットが命令の特定の1つを検出するために最初に合成され、データがどの様に処理されるかを制御するために該検出結果が使用される必要はない。反対に、上記Nビットの個々のビットは、当該Nビットの他のビットとは独立に、オペランドビットと共に論理機能に引数として参加することができる。

【0041】

図5は、命令の或る組み合わせからの命令を実行するようにプログラムされた場合の、上記機能ユニットのハードウェア機能記述のモデルを示している。この記述に示される構造は機能的のみのものであって、物理的なものではないことに注意されたい。異なる機能ブロックへの分割は、当該構成可能な機能ユニットにおいて実施化される回路の構造の如何なる分割にも対応する必要はなく、異なるブロックが当該構成可能な機能ユニットにおける同一の物理的回路素子を共用することもできる。

【0042】

該モデルは、2つのソースオペランド用の入力部50a及び50bと、構成可能な命令の各々を実行するための多数のブロック52a〜52cと、これら命令の結果用のポート54a〜54cと、上記結果の1つを出力部58に通過させるマルチプレクサ56とを示している。マルチプレクサ56は、前記命令選択コードのNビットにより制御される。

【0043】

このモデルは、その機能を果たすためになされなければならない接続のリストに変換される。この変換の間に、図5の種々のブロックの間で資源使用が相互最小化される。即ち、マルチプレクサ56の機能はブロック52a〜52cのものと(部分的に)併合することができ、これらブロック52a〜52cの機能は互いに併合することができる。

【0044】

構成可能な命令及び一緒にロードされる命令の組み合わせは、好ましくは、当該プロセッサ上で走る特定の各プログラムに対して独立に選択されるものとする。以下においては、これらの命令及び組み合わせは、各々、“カスタム命令”及び“クラスタ”とも呼ぶ。カスタム命令及びクラスタの選択は、好ましくは、コンピュータプログラムのコンパイルを用いて、即ち上記プロセッサが該コンピュータプログラムを実行する前に、なされる。

【0045】

図4はコンパイルされたプログラムを発生するためのフローチャートを示している。図4のフローチャートは以下のステップを実行する。

41:ソースコード(典型的には、Cで書かれる)がコンパイラ前置部により処理され、データフローグラフとして表された中間コードを発生する。

42:上記中間コードはクラスタ検出/選択モジュールにより読み取られ、該モジュールはハードウェア合成に潜在的に適したデータフローセグメント(候補)を探す。各“候補”はカスタム命令を定義する。好ましくは、当該アプリケーションの臨界的経路内で純粋に算術的又は論理的演算からなるセグメントのみが考慮されるものとする。上記検索を案内するためにプロファイルデータが使用される。候補は、或る評価規準に従いカスタム命令のクラスタにグループ化される(以下の説明を参照)。

43:上記クラスタはトランスレータにより処理され、該トランスレータはデータフローセグメントの算術演算をHDL(標準ハードウェア定義言語)でのハードウェア記述に変換する。異なるカスタム命令が独立に実行することができるように、このハードウェア記述には解読ロジックが付加される。図5は、この段階で生成された回路記述のモデルの一例を示している。

44:結果としての回路記述はハードウェア合成ツールにより処理され、そこでは、タイミング及び適合性レポート(所要の処理時間量及びハードウェアを記述している)が、回路ネットリストと共に発生される。この段階で、当該回路記述内のマルチプレクサの機能を、図5の機能ブロックの資源使用とで相互最小化することができる。この資源の相互最小化それ自体は、通常、機能を備えるプログラマブルロジックをプログラムするためとして既知である。

45:タイミング及び適合性情報は前記クラスタ検出/選択モジュールに送り返され、そこでは、クラスタが再配置若しくは廃棄されるか、又は新たなクラスタが形成される。該サイクルは最終的なクラスタの集合が選択されるまで繰り返される。

46:最終的なクラスタの集合が選択されたら、該最終的に選択されたクラスタで構成された中間コードのデータフローセグメントは、それらの等価なカスタム命令ラベルにより置換される。

47:次いで、結果としてのコードは後置部により後処理(レジスタの割り付け、アセンブリコードの出力、命令のスケジューリング及び/又は当てはまる何らかの他の後処理のために)される。

48:結果としてのアセンブリは、新たに合成されたカスタム命令ラベルを認識する修正されたアセンブラに送られる。前記ハードウェア合成ツールにより発生されたネットリストは、該アセンブリと組み合わされて、最終的な実行可能なものを生成する。

【0046】

上記のハードウェア合成ステップは、人のプログラマからは完全に隠すことができる。他の例として、好ましくは上述した指針を用いて前記候補及び/又はクラスタを選択する人のプログラマを必要とするかもしれない。

【0047】

プログラムのデータフローグラフから候補の構成可能な命令を選択すること自体は既知である。基本的に、これは、上記プログラムのデータフローグラフからサブグラフを選択することを含み、その場合、これらサブグラフは2以下の変数オペランド入力しか有さない。(これは、上記の構成可能な機能ユニットが2つのオペランド入力を有する場合である。該構成可能な機能ユニットが小さな数の又は大きな数のオペランド入力を有している場合は、対応して大きな又は小さな入力を有するサブグラフを選択することができる。)

【0048】

好ましくは、候補は、当該プログラムにおける上記候補が発生する連続した命令の領域に基づいてクラスタにグループ化されるようにする。或る領域に対しては、同時にロードすることが可能な構成プログラムの数よりも多くのクラスタが定義されるべきではない(例えば、1つのみの構成可能な機能ユニットしか存在せず、該ユニットが一度に1つのみの構成プログラムを用いてしか構成することができない場合は、1つのみのクラスタ)。上記プログラム領域のサイズ及び該領域用に選択される候補の数は、全ての候補を同時にロードされる最大数のクラスタにおいてプログラムすることができるように、選択されねばならない。

【0049】

原理的には、候補命令の選択及びそれらのクラスタへの合成の両者は、厄介な最適化問題である。多数の構成可能な命令の可能な組み合わせの集合が存在する。狙いは、プログラムの典型的な実行(実行プロファイルにより定義される)に必要とされる命令サイクルの数を最小化するような集合を見付けることである。命令サイクルのカウントの最小化は、或るクラスタに関する全ての選択された候補が構成プログラムに適合するという拘束を受ける。

【0050】

この目的のため、通常の命令のみが使用されたとしたら一層多数の命令サイクルを必要としたであろうような、各々が1命令サイクルにおいて効果を生成する構成可能な命令を考慮する。当該プロファイルにおいてカスタム命令により置換されるべき全ての通常の命令を実行するのに要する追加の命令サイクルの数は、構成プログラムをロードするためのオーバーヘッドサイクルよりも大きくなくてはならない。さもなければ、何の組み合わせも選択されるべきでない。オーバーヘッドサイクルの数は、組み合わせをロードする場合の方が、同数の命令を個々にロードする場合よりも小さいことに注意すべきである。何故なら、ローディングは、上記組み合わせにおける全ての命令に対しては1回しか行う必要がなく、平均して、相互最小化により命令当たり少ない構成プログラム空間しか占めないからである。

【0051】

クラスタに合成することができる候補の数は、構成可能な機能ユニットにおける資源使用の最小化に依存する。構成可能な命令が“小さい”程、又は一層高度に類似している程、より多くの構成可能な命令を1つのクラスタに組み合わせることができる。

【0052】

クラスタを選択するアルゴリズムの一例は、

1)当該プログラムの範囲から領域を、コンパイラにより生成された中間コードにおける領域の開始命令及び終了命令に関して選択する。好ましくは、領域として、頻繁に実行されるループ又は頻繁に実行されるサブルーチンにおける命令を選択するものとするが、非常に頻繁には実行されないが類似の命令の繰り返しを含む領域も良好な候補である。

2)上記の選択された領域における命令に対するデータフローセグメントに関して多数の候補のカスタム命令を選択する。

3)上記の選択されたカスタム命令が全て当該構成可能な機能ユニットに一緒に納まり、且つ、完了するのにパイプラインサイクル未満しか掛からないような形で、これら選択されたカスタム命令を組み合わせるクラスタに対する構成プログラムを発生することができるか判断する。もしそうなら、通常の命令の組み合わせを選択された候補のカスタム命令により置換することにより当該プロファイルにおいて得られる命令サイクルの数を決定する。

4)ステップ1ないし3を、一層大きな大きな及び一層小さな領域に対して、且つ、別の選択された命令に対して繰り返し、選択された領域及び選択された命令を保持し、及び最も多い命令サイクルを得るクラスタを保持する。このステップは、或る領域に対して見つかった最も有利なクラスタから始めて、同一の領域から又は該領域の拡張からの何れかから、上記クラスタを更なるカスタム命令を用いて拡張することにより発見的に高速化することができる。

5)上記ステップ1ないし4を、当該プログラムの異なる、重ならない領域に対して、これら全ての異なる領域に関する各クラスタを保持しながら繰り返す。

【0053】

上記の最小化は、当該プログラムの上記領域に局部化された局部的処理であり、当該プログラム全体に対するものでないことに注意すべきである。重要な点は、クラスタが特定の領域に対する命令サイクルカウントを減少させることである。他の領域で何が起きるかは問題ではない。何故なら、当該クラスタは、それら領域に関してはロードする必要はないからである。事実、異なる領域用の異なるクラスタは同一の効果を伴う幾つかのカスタム命令を含むかもしれない。これらの同一の効果を持つカスタム命令の1つが実行されると、実行された領域が、上記クラスタの何れがロードされたかを決定する。従って、ロードされる構成プログラムは、実行されねばならない如何なる特定の命令によるというよりも、実行されている領域により決定される。

【0054】

クラスタ及び領域の選択は、これらの点を選択するための多数の発見的評価規準を用いて単純化することができる。種々の評価規準を、候補をクラスタにグループ化するために使用することができる。例えば、

− 共通のループ内の候補は、同一のクラスタにグループ化される(これは、ループ内の再構成オーバーヘッドを防止する)。

− サブルーチン内で発生する候補は、当該サブルーチン用のクラスタ又は複数のクラスタにグループ化される。

− 低い論理的複雑さの候補は、大きなクラスタ(一層多くの候補を持つ)にグループ化される。

− 高い論理的複雑さの候補は、小さなクラスタ(一層少ない候補を持つ)にグループ化される。

− 一層良好に論理的相互最小化の機会を利用するために、類似の候補(論理の点で)の同一のクラスタへの合成が好まれる。

【0055】

実際に効果的に働くことが分かったクラスタ選択用の評価規準は、カスタム命令を、該カスタム命令の結果に影響を与えるような、それらのオペランドの入力ビットの類似性に依存してクラスタに配置することである。或るカスタム命令が与えられた場合、その入力オペランドのどのビットが、該命令の結果に影響を与えるか、及びどのビットが該結果に影響を与えないかを決定するのは回りくどくない。この場合、カスタム命令の非類似性は、共用されない入力ビットの数により測ることができる。従って、カスタム命令のクラスタは、好ましくは、各命令の入力のどのビットが該命令の結果に影響するかを計算し(これらは“関連ビット”と呼ばれる)、命令間の非類似性の目安を共用されない関連ビットの数に関して計算し、且つ、設定された量より少ない非類似性を持つカスタム命令のクラスタを選択することにより選択される。

【0056】

CPLDコアの規則的な予測可能なタイミングモデルは、クラスタの形成に有利である。複数候補の単一構成へのグループ化は、典型的なFPGA構造における導入遅延をかなり変化させ得、自動的なクラスタ形成用のアルゴリズムをかなり困難にする。何故なら、その場合には、相互最小化を、該最小化が過度に多い遅延を導入しないという制限の下で実施しなければならないからである。CPLDの場合は、或る構成への一層多くのカスタム命令の追加は、前記PAL又はPLAからの一層多くの積項(PT)を単に必要とする。回路が当該コアに適合する限り、上記遅延は前記交点スイッチ及びPLAを介しての時間遅延(Tpd_pla)に限定され、当該アルゴリズムはクラスタを形成する際に遅延変動の問題を考慮する必要がない。

【0057】

図2の機能ユニットにおいては、交点スイッチ24が特に有効である。何故なら、該交点スイッチは、オペランドの異なるビットに関する信号を、これら異なるビットが該オペランド内の非常に異なる位置に不規則に広がっている場合でさえも、1つの論理ブロック26a、26bに一緒にもたらすことを可能にするからである。これは、同一の効果がALU16を用いて実現されなければならなかった場合に、非常に多くの通常の命令を必要としたであろう構成可能な命令を実施化することを可能にするからである。

【0058】

また、交点スイッチ24は、命令選択ビットを異なるブロック26a、26bにおいてオペランドデータビットと自由に混合することを可能にする。このようにして、命令の区別をオペランドの処理と統合することにより、ハードウェア資源使用の一層良好な相互最小化が可能となる。

【図面の簡単な説明】

【図1】 図1は、構成可能な命令をサポートするプロセッサのアーキテクチャを示す。

【図2】 図2は、構成可能な機能ユニットを示す。

【図3】 図3は、構成可能な論理ブロックを示す。

【図4】 図4は、コンパイルされたプログラムを発生させるためのフローチャートを示す。

【図5】 図5は、命令の組み合わせを実行する機能ユニットのモデルを示す。

【符号の説明】

14…実行段レジスタ

16…ALU機能ユニット

18…構成可能な機能ユニット

20a、20b、22…入力ポート

23…再構成制御回路

24…交点スイッチ

26a、26b…論理ブロック

28…出力ポート

Claims (9)

- 構成プログラムをロードすることにより実行時に効果を再定義することが可能な、再構成可能な命令を実行することができる構成可能な機能ユニットを含むプロセッサを用いてコンピュータプログラムを実行する方法において、

コンパイラが、再構成可能な命令の組み合わせを選択するステップであって、各再構成可能な命令について入力オペランドのどのビットが当該命令の結果に影響を与えるかを決定し、該影響を与えるビットのうち各再構成可能な命令間で共用されない入力オペランドのビットの数に応じて前記再構成可能な命令間の非類似性を決定し、前記決定された非類似性に基づいて、相対的に少ない非類似性を持つ前記再構成可能な命令をグループ化することを含み、前記共用されない入力オペランドのビットは、当該再構成可能な命令の結果に影響を与えると決定された前記ビットである、ステップと、

前記コンパイラが、前記再構成可能な命令の各組み合わせに対して構成プログラムを各々発生するステップと、

前記プロセッサが、前記コンピュータプログラムの実行の間に、前記組み合わせのうちの1つの組み合わせからの命令が必要とされ、且つ、前記構成可能な機能ユニットが前記1つの組み合わせ用の構成プログラムを用いて構成されていない都度に、前記1つの組み合わせの全命令に対する構成プログラムを前記構成可能な機能ユニットにロードするステップと、

を有していることを特徴とする方法。 - 請求項1に記載の方法において、前記構成プログラムを発生するステップが、当該構成プログラムに関連する前記再構成可能な命令の前記1つの組み合わせに対してハードウェア資源使用を最小化するステップを有していることを特徴とする方法。

- 請求項2に記載の方法において、前記コンピュータプログラム実行の間に前記組み合わせから複数の命令を選択し、且つ、これら複数の命令によりオペランドデータを処理するためのハードウェア資源使用が最小化されることを特徴とする方法。

- 請求項2に記載の方法において、前記構成可能な機能ユニットは、交点スイッチを、オペランドデータ用の入力端子と、該交点スイッチの出力端子を異なる論理合成回路に接続する接続ラインとの間に含み、前記交点スイッチは前記構成プログラムにより制御され、前記交点スイッチ内の接続のプログラミングが前記構成可能な機能ユニットにおけるハードウェア資源使用を最小化するために使用されることを特徴とする方法。

- 請求項4に記載の方法において、前記組み合わせから前記再構成可能な命令を選択するためのビットの少なくとも一部が、前記オペランドデータと交換可能に前記交点スイッチに供給されることを特徴とする方法。

- 構成プログラムをロードすることにより効果を実行時に再定義することが可能な、再構成可能な命令を実行することができる構成可能な機能ユニットを有するようなプロセッサであって、前記構成可能な機能ユニットが、再構成可能な命令を実行するために必要とされる際に前記構成プログラムが未だロードされていない場合に該構成プログラムのロードを起動するロード起動回路を有するようなプロセッサにおいて、前記構成プログラムは少なくとも2つの組み合わされた再構成可能な命令の効果を定義し、前記ロード起動回路は前記組み合わされた再構成可能な命令のうちの少なくとも1つが必要とされる場合に該組み合わされた命令の全てに対する前記構成プログラムのロードを起動することを特徴とするプロセッサであって、

前記組み合わされた再構成可能な命令は、コンパイラが、各再構成可能な命令について入力オペランドのどのビットが当該命令の結果に影響を与えるかを決定し、該影響を与えるビットのうち各再構成可能な命令間で共用されない入力オペランドのビットの数に応じて前記再構成可能な命令間の非類似性を決定し、前記決定された非類似性に基づいて、相対的に少ない非類似性を持つ前記再構成可能な命令をグループ化して組み合わされるものであり、前記共用されない入力オペランドのビットは、当該再構成可能な命令の結果に影響を与えると決定された前記ビットである、プロセッサ。 - 請求項6に記載のプロセッサにおいて、前記構成可能な機能ユニットは前記組み合わせから命令を選択するための命令選択入力端子と、オペランドデータ入力端子と、合成ロジックと、結果出力端子とを有し、前記オペランドデータ入力端子及び前記命令選択入力端子は、共に、命令選択ビット及びオペランドデータビットが交換可能に使用することができるように、前記合成ロジックを介して前記結果出力端子に結合されていることを特徴とするプロセッサ。

- 請求項7に記載のプロセッサにおいて、前記構成可能な機能ユニットは、前記合成ロジックと、前記オペランドデータ入力端子及び前記命令選択入力端子との間に交点スイッチを有し、該交点スイッチは前記命令選択ビット及び前記オペランドデータビットを前記合成ロジックに機能的に交換可能に接続することができることを特徴とするプロセッサ。

- 請求項6に記載のプロセッサにおいて、前記構成可能な機能ユニットが、前記構成可能な機能ユニット内に交点スイッチ及び論理部を有し、前記組み合わせの構成可能な命令を構成する可能な接続の部類の何れが前記構成プログラムの制御の下で接続されるかに無関係に、前記交点スイッチ及び前記論理部を介しての、オペランドの演算結果の略一定の遅延を与えることを特徴とするプロセッサ。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP99200431.7 | 1999-02-15 | ||

| EP99200431 | 1999-02-15 | ||

| PCT/EP2000/000590 WO2000049496A1 (en) | 1999-02-15 | 2000-01-26 | Data processor with a configurable functional unit and method using such a data processor |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002537599A JP2002537599A (ja) | 2002-11-05 |

| JP2002537599A5 JP2002537599A5 (ja) | 2007-03-29 |

| JP5148029B2 true JP5148029B2 (ja) | 2013-02-20 |

Family

ID=8239894

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000600174A Expired - Lifetime JP5148029B2 (ja) | 1999-02-15 | 2000-01-26 | 構成可能な機能ユニットを備えるデータプロセッサ及びそのようなデータプロセッサを使用する方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6721884B1 (ja) |

| EP (1) | EP1073951A1 (ja) |

| JP (1) | JP5148029B2 (ja) |

| KR (1) | KR100731371B1 (ja) |

| WO (1) | WO2000049496A1 (ja) |

Families Citing this family (65)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6542998B1 (en) | 1997-02-08 | 2003-04-01 | Pact Gmbh | Method of self-synchronization of configurable elements of a programmable module |

| US6076152A (en) * | 1997-12-17 | 2000-06-13 | Src Computers, Inc. | Multiprocessor computer architecture incorporating a plurality of memory algorithm processors in the memory subsystem |

| US7373440B2 (en) | 1997-12-17 | 2008-05-13 | Src Computers, Inc. | Switch/network adapter port for clustered computers employing a chain of multi-adaptive processors in a dual in-line memory module format |

| US7565461B2 (en) | 1997-12-17 | 2009-07-21 | Src Computers, Inc. | Switch/network adapter port coupling a reconfigurable processing element to one or more microprocessors for use with interleaved memory controllers |

| US7003660B2 (en) | 2000-06-13 | 2006-02-21 | Pact Xpp Technologies Ag | Pipeline configuration unit protocols and communication |

| US8058899B2 (en) | 2000-10-06 | 2011-11-15 | Martin Vorbach | Logic cell array and bus system |

| DE60144022D1 (de) | 2000-11-06 | 2011-03-24 | Broadcom Corp | Umkonfigurierbares verarbeitungssystem und -verfahren |

| GB0028079D0 (en) * | 2000-11-17 | 2001-01-03 | Imperial College | System and method |

| JP3636986B2 (ja) | 2000-12-06 | 2005-04-06 | 松下電器産業株式会社 | 半導体集積回路 |

| JP4022147B2 (ja) | 2000-12-20 | 2007-12-12 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 設定可能な機能ユニットを備えるデータ処理装置 |

| US9037807B2 (en) | 2001-03-05 | 2015-05-19 | Pact Xpp Technologies Ag | Processor arrangement on a chip including data processing, memory, and interface elements |

| US7444531B2 (en) | 2001-03-05 | 2008-10-28 | Pact Xpp Technologies Ag | Methods and devices for treating and processing data |

| US7249242B2 (en) | 2002-10-28 | 2007-07-24 | Nvidia Corporation | Input pipeline registers for a node in an adaptive computing engine |

| US7752419B1 (en) | 2001-03-22 | 2010-07-06 | Qst Holdings, Llc | Method and system for managing hardware resources to implement system functions using an adaptive computing architecture |

| US7962716B2 (en) | 2001-03-22 | 2011-06-14 | Qst Holdings, Inc. | Adaptive integrated circuitry with heterogeneous and reconfigurable matrices of diverse and adaptive computational units having fixed, application specific computational elements |

| US6836839B2 (en) | 2001-03-22 | 2004-12-28 | Quicksilver Technology, Inc. | Adaptive integrated circuitry with heterogeneous and reconfigurable matrices of diverse and adaptive computational units having fixed, application specific computational elements |

| US7653710B2 (en) | 2002-06-25 | 2010-01-26 | Qst Holdings, Llc. | Hardware task manager |

| US6577678B2 (en) | 2001-05-08 | 2003-06-10 | Quicksilver Technology | Method and system for reconfigurable channel coding |

| US7657877B2 (en) | 2001-06-20 | 2010-02-02 | Pact Xpp Technologies Ag | Method for processing data |

| US7996827B2 (en) | 2001-08-16 | 2011-08-09 | Martin Vorbach | Method for the translation of programs for reconfigurable architectures |

| DE10249204A1 (de) * | 2001-10-29 | 2003-05-28 | Siemens Ag | Rekonfigurierbare digitale Logikeinheit |

| GB2382175A (en) * | 2001-11-20 | 2003-05-21 | Hewlett Packard Co | Reconfigurable processor |

| US7046635B2 (en) | 2001-11-28 | 2006-05-16 | Quicksilver Technology, Inc. | System for authorizing functionality in adaptable hardware devices |

| US6986021B2 (en) | 2001-11-30 | 2006-01-10 | Quick Silver Technology, Inc. | Apparatus, method, system and executable module for configuration and operation of adaptive integrated circuitry having fixed, application specific computational elements |

| US8412915B2 (en) | 2001-11-30 | 2013-04-02 | Altera Corporation | Apparatus, system and method for configuration of adaptive integrated circuitry having heterogeneous computational elements |

| US7215701B2 (en) | 2001-12-12 | 2007-05-08 | Sharad Sambhwani | Low I/O bandwidth method and system for implementing detection and identification of scrambling codes |

| US7403981B2 (en) | 2002-01-04 | 2008-07-22 | Quicksilver Technology, Inc. | Apparatus and method for adaptive multimedia reception and transmission in communication environments |

| JP3723775B2 (ja) * | 2002-01-10 | 2005-12-07 | 松下電器産業株式会社 | データ処理装置 |

| AU2003214046A1 (en) * | 2002-01-18 | 2003-09-09 | Pact Xpp Technologies Ag | Method and device for partitioning large computer programs |

| US8914590B2 (en) | 2002-08-07 | 2014-12-16 | Pact Xpp Technologies Ag | Data processing method and device |

| US7328414B1 (en) | 2003-05-13 | 2008-02-05 | Qst Holdings, Llc | Method and system for creating and programming an adaptive computing engine |

| US7660984B1 (en) | 2003-05-13 | 2010-02-09 | Quicksilver Technology | Method and system for achieving individualized protected space in an operating system |

| JP3934493B2 (ja) | 2002-06-28 | 2007-06-20 | 富士通株式会社 | 集積回路及びシステム開発方法 |

| US8108656B2 (en) | 2002-08-29 | 2012-01-31 | Qst Holdings, Llc | Task definition for specifying resource requirements |

| US7937591B1 (en) | 2002-10-25 | 2011-05-03 | Qst Holdings, Llc | Method and system for providing a device which can be adapted on an ongoing basis |

| US7225324B2 (en) | 2002-10-31 | 2007-05-29 | Src Computers, Inc. | Multi-adaptive processing systems and techniques for enhancing parallelism and performance of computational functions |

| US8276135B2 (en) | 2002-11-07 | 2012-09-25 | Qst Holdings Llc | Profiling of software and circuit designs utilizing data operation analyses |

| US7225301B2 (en) | 2002-11-22 | 2007-05-29 | Quicksilver Technologies | External memory controller node |

| US7020746B2 (en) * | 2003-01-28 | 2006-03-28 | Microsoft Corporation | Method and system for an atomically updated, central cache memory |

| US7581081B2 (en) | 2003-03-31 | 2009-08-25 | Stretch, Inc. | Systems and methods for software extensible multi-processing |

| US7590829B2 (en) * | 2003-03-31 | 2009-09-15 | Stretch, Inc. | Extension adapter |

| US7613900B2 (en) | 2003-03-31 | 2009-11-03 | Stretch, Inc. | Systems and methods for selecting input/output configuration in an integrated circuit |

| US8001266B1 (en) | 2003-03-31 | 2011-08-16 | Stretch, Inc. | Configuring a multi-processor system |

| US7373642B2 (en) * | 2003-07-29 | 2008-05-13 | Stretch, Inc. | Defining instruction extensions in a standard programming language |

| US7418575B2 (en) * | 2003-07-29 | 2008-08-26 | Stretch, Inc. | Long instruction word processing with instruction extensions |

| US7237055B1 (en) * | 2003-10-22 | 2007-06-26 | Stretch, Inc. | System, apparatus and method for data path routing configurable to perform dynamic bit permutations |

| US7526632B1 (en) * | 2003-10-22 | 2009-04-28 | Stretch, Inc. | System, apparatus and method for implementing multifunctional memory in reconfigurable data path processing |

| US7584345B2 (en) | 2003-10-30 | 2009-09-01 | International Business Machines Corporation | System for using FPGA technology with a microprocessor for reconfigurable, instruction level hardware acceleration |

| US9047094B2 (en) * | 2004-03-31 | 2015-06-02 | Icera Inc. | Apparatus and method for separate asymmetric control processing and data path processing in a dual path processor |

| US7949856B2 (en) * | 2004-03-31 | 2011-05-24 | Icera Inc. | Method and apparatus for separate control processing and data path processing in a dual path processor with a shared load/store unit |

| US8484441B2 (en) | 2004-03-31 | 2013-07-09 | Icera Inc. | Apparatus and method for separate asymmetric control processing and data path processing in a configurable dual path processor that supports instructions having different bit widths |

| TW200617703A (en) * | 2004-11-30 | 2006-06-01 | Tokyo Electron Ltd | Dynamically reconfigurable processor |

| JP4450737B2 (ja) * | 2005-01-11 | 2010-04-14 | 富士通株式会社 | 半導体集積回路 |

| US20060265485A1 (en) * | 2005-05-17 | 2006-11-23 | Chai Sek M | Method and apparatus for controlling data transfer in a processing system |

| US7603492B2 (en) * | 2005-09-20 | 2009-10-13 | Motorola, Inc. | Automatic generation of streaming data interface circuit |

| US7890686B2 (en) | 2005-10-17 | 2011-02-15 | Src Computers, Inc. | Dynamic priority conflict resolution in a multi-processor computer system having shared resources |

| US7716100B2 (en) * | 2005-12-02 | 2010-05-11 | Kuberre Systems, Inc. | Methods and systems for computing platform |

| WO2007074583A1 (ja) * | 2005-12-27 | 2007-07-05 | Matsushita Electric Industrial Co., Ltd. | 再構成可能な演算器を持つプロセッサ |

| KR100681199B1 (ko) * | 2006-01-11 | 2007-02-09 | 삼성전자주식회사 | 코어스 그레인 어레이에서의 인터럽트 처리 방법 및 장치 |

| US20080120497A1 (en) * | 2006-11-20 | 2008-05-22 | Motorola, Inc. | Automated configuration of a processing system using decoupled memory access and computation |

| KR101581882B1 (ko) | 2009-04-20 | 2015-12-31 | 삼성전자주식회사 | 재구성 가능한 프로세서 및 그 재구성 방법 |

| JP5990466B2 (ja) | 2010-01-21 | 2016-09-14 | スビラル・インコーポレーテッド | ストリームに基づく演算を実装するための汎用複数コアシステムのための方法および装置 |

| US8661424B2 (en) * | 2010-09-02 | 2014-02-25 | Honeywell International Inc. | Auto-generation of concurrent code for multi-core applications |

| US9698790B2 (en) * | 2015-06-26 | 2017-07-04 | Advanced Micro Devices, Inc. | Computer architecture using rapidly reconfigurable circuits and high-bandwidth memory interfaces |

| US11106467B2 (en) | 2016-04-28 | 2021-08-31 | Microsoft Technology Licensing, Llc | Incremental scheduler for out-of-order block ISA processors |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4763242A (en) * | 1985-10-23 | 1988-08-09 | Hewlett-Packard Company | Computer providing flexible processor extension, flexible instruction set extension, and implicit emulation for upward software compatibility |

| US5128871A (en) * | 1990-03-07 | 1992-07-07 | Advanced Micro Devices, Inc. | Apparatus and method for allocation of resoures in programmable logic devices |

| US5222030A (en) * | 1990-04-06 | 1993-06-22 | Lsi Logic Corporation | Methodology for deriving executable low-level structural descriptions and valid physical implementations of circuits and systems from high-level semantic specifications and descriptions thereof |

| JPH04213167A (ja) * | 1990-12-07 | 1992-08-04 | Ricoh Co Ltd | 回路設計方式 |

| JP3183415B2 (ja) * | 1992-02-25 | 2001-07-09 | 川崎製鉄株式会社 | 論理合成方法 |

| US5260942A (en) * | 1992-03-06 | 1993-11-09 | International Business Machines Corporation | Method and apparatus for batching the receipt of data packets |

| JPH064335A (ja) * | 1992-06-23 | 1994-01-14 | Nec Corp | 命令動作試験装置 |

| US5684980A (en) * | 1992-07-29 | 1997-11-04 | Virtual Computer Corporation | FPGA virtual computer for executing a sequence of program instructions by successively reconfiguring a group of FPGA in response to those instructions |

| US5892961A (en) * | 1995-02-17 | 1999-04-06 | Xilinx, Inc. | Field programmable gate array having programming instructions in the configuration bitstream |

| US5748979A (en) * | 1995-04-05 | 1998-05-05 | Xilinx Inc | Reprogrammable instruction set accelerator using a plurality of programmable execution units and an instruction page table |

| US5933642A (en) * | 1995-04-17 | 1999-08-03 | Ricoh Corporation | Compiling system and method for reconfigurable computing |

| US5794062A (en) * | 1995-04-17 | 1998-08-11 | Ricoh Company Ltd. | System and method for dynamically reconfigurable computing using a processing unit having changeable internal hardware organization |

| US5819067A (en) * | 1996-02-23 | 1998-10-06 | Advanced Micro Devices, Inc. | Computer system configured to translate a computer program into a second computer program prior to executing the computer program |

| DE19634031A1 (de) * | 1996-08-23 | 1998-02-26 | Siemens Ag | Prozessor mit Pipelining-Aufbau |

| US6047115A (en) * | 1997-05-29 | 2000-04-04 | Xilinx, Inc. | Method for configuring FPGA memory planes for virtual hardware computation |

| US5943501A (en) * | 1997-06-27 | 1999-08-24 | Wisconsin Alumni Research Foundation | Multiple processor, distributed memory computer with out-of-order processing |

| JP3194364B2 (ja) * | 1997-06-27 | 2001-07-30 | 日本電気株式会社 | プログラマブル機能ブロック |

| JPH1185507A (ja) * | 1997-09-05 | 1999-03-30 | Mitsubishi Electric Corp | 中央処理装置およびマイクロコンピュータシステム |

-

2000

- 2000-01-26 JP JP2000600174A patent/JP5148029B2/ja not_active Expired - Lifetime

- 2000-01-26 KR KR1020007011394A patent/KR100731371B1/ko active IP Right Grant

- 2000-01-26 EP EP00903638A patent/EP1073951A1/en not_active Withdrawn

- 2000-01-26 WO PCT/EP2000/000590 patent/WO2000049496A1/en active IP Right Grant

- 2000-02-11 US US09/501,642 patent/US6721884B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| WO2000049496A1 (en) | 2000-08-24 |

| KR100731371B1 (ko) | 2007-06-21 |

| EP1073951A1 (en) | 2001-02-07 |

| JP2002537599A (ja) | 2002-11-05 |

| KR20010042690A (ko) | 2001-05-25 |

| US6721884B1 (en) | 2004-04-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5148029B2 (ja) | 構成可能な機能ユニットを備えるデータプロセッサ及びそのようなデータプロセッサを使用する方法 | |

| US6948158B2 (en) | Retargetable compiling system and method | |

| US7493475B2 (en) | Instruction vector-mode processing in multi-lane processor by multiplex switch replicating instruction in one lane to select others along with updated operand address | |

| US5574930A (en) | Computer system and method using functional memory | |

| US7685404B2 (en) | Program subgraph identification | |

| JP3916680B2 (ja) | プロセッサ | |

| US7350055B2 (en) | Tightly coupled accelerator | |

| KR0149658B1 (ko) | 데이터 처리장치 및 데이터 처리방법 | |

| US7318143B2 (en) | Reuseable configuration data | |

| US9329866B2 (en) | Methods and apparatus for adapting pipeline stage latency based on instruction type | |

| US6453407B1 (en) | Configurable long instruction word architecture and instruction set | |

| US6185668B1 (en) | Method and apparatus for speculative execution of instructions | |

| EP0723220A2 (en) | Parallel processing system amd method using surrogate instructions | |

| JP2002512399A (ja) | 外部コプロセッサによりアクセス可能なコンテキストスイッチレジスタセットを備えたriscプロセッサ | |

| KR19980070019A (ko) | 명령어 요소들의 재조합에 의한 서로 다른 명령어 코드들 사이의 동적 변환 | |

| US20080263332A1 (en) | Data Processing Apparatus and Method for Accelerating Execution Subgraphs | |

| JP2008532162A (ja) | プロセッサ中の再構成可能論理 | |

| KR20000075837A (ko) | 보호형의 매우 긴 명령어 아키텍처를 위한 향상된 명령 디스패치 메카니즘 | |

| KR20210157421A (ko) | 벡터 인덱스 레지스터들을 이용한 벡터 요소들을 어드레싱하기 위한 멀티-레인 | |

| EP0982655A2 (en) | Data processing unit and method for executing instructions of variable lengths | |

| US7617494B2 (en) | Process for running programs with selectable instruction length processors and corresponding processor system | |

| KR100374401B1 (ko) | 마이크로 명령을 기초로 프로그램 가능한 명령을 실행하는하드웨어 장치 | |

| JP2004334429A (ja) | 論理回路及びその論理回路上で実行するプログラム | |

| US6099585A (en) | System and method for streamlined execution of instructions | |

| JP3737573B2 (ja) | Vliwプロセッサ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070125 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070125 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090929 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091217 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100316 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100324 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100617 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100928 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20101228 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110111 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110325 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120105 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120426 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20120507 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120904 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121001 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121101 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121128 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5148029 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151207 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |