JP4450737B2 - 半導体集積回路 - Google Patents

半導体集積回路 Download PDFInfo

- Publication number

- JP4450737B2 JP4450737B2 JP2005004403A JP2005004403A JP4450737B2 JP 4450737 B2 JP4450737 B2 JP 4450737B2 JP 2005004403 A JP2005004403 A JP 2005004403A JP 2005004403 A JP2005004403 A JP 2005004403A JP 4450737 B2 JP4450737 B2 JP 4450737B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor integrated

- integrated circuit

- processing

- circuit

- network

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/78—Architectures of general purpose stored program computers comprising a single central processing unit

- G06F15/7867—Architectures of general purpose stored program computers comprising a single central processing unit with reconfigurable architecture

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Semiconductor Integrated Circuits (AREA)

- Logic Circuits (AREA)

Description

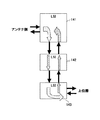

11 ダイナミックリコンフィギュラブル回路

12 ユーザロジック

13 パラメータ付専用ハードウェア

14 制御回路

15 ネットワーク

16 拡張I/O

17 内部I/O

18 バス

19 プロセッサ

Claims (9)

- 再構成可能に相互結合される複数の演算ユニットを含むリコンフィギュラブル回路と、

所定の処理を実行するよう構成される固定のロジック回路及びパラメータ設定により処理仕様を変更可能に構成されるパラメータ付専用ハードウェアの少なくとも一方である処理回路と、

該リコンフィギュラブル回路と該処理回路とに結合される接続変更可能なネットワークと、

該ネットワークを該ネットワーク以外と結合するために該ネットワークに接続される少なくとも2つのインターフェース

を含み、該ネットワークは、

複数の信号線と、

該複数の信号線のうちから所定数の信号線を選択するセレクタ

を含み、該セレクタにより選択された信号線のみを該インターフェースの1つに接続することを特徴とする半導体集積回路。 - 該リコンフィギュラブル回路、該処理回路、及び該ネットワークを1つのセットとし、別のリコンフィギュラブル回路、別の処理回路、及び別のネットワークを含むセットを更に少なくとも1セット含み、該複数のセットの複数のネットワークを該インターフェースを介して直列に結合するとともに、両端に位置する該ネットワークについては該インターフェースを介して該半導体集積回路の外部に結合可能に構成することを特徴とする請求項1記載の半導体集積回路。

- 該リコンフィギュラブル回路と該処理回路とに結合されるバスと、

該バスに結合されるプロセッサ

を更に含むことを特徴とする請求項1記載の半導体集積回路。 - 該ネットワークの接続を制御する制御回路を更に含み、該制御回路は該プロセッサからの指示に応じて該ネットワークの接続を設定するよう構成されることを特徴とする請求項3記載の半導体集積回路。

- 該リコンフィギュラブル回路は該プロセッサからの設定データに応じて該複数の演算ユニットの演算内容を設定することを特徴とする請求項3記載の半導体集積回路。

- 該プロセッサと外部システムとを結合するためのシステムインターフェースを更に含むことを特徴とする請求項3記載の半導体集積回路。

- 該ネットワークは該リコンフィギュラブル回路と該処理回路とを相互結合するクロスバーを含むことを特徴とする請求項1記載の半導体集積回路。

- 該パラメータ付専用ハードウェアは、

特定の処理を実行する専用ハードウェアと、

該専用ハードウェアの動作及び処理仕様を規定するデータを保持する設定レジスタ

を含むことを特徴とする請求項1記載の半導体集積回路。 - 該処理回路は、該半導体集積回路の外部との信号のやり取りのためのインターフェースを更に含むことを特徴とする請求項1記載の半導体集積回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005004403A JP4450737B2 (ja) | 2005-01-11 | 2005-01-11 | 半導体集積回路 |

| US11/147,173 US7702884B2 (en) | 2005-01-11 | 2005-06-08 | Semiconductor integrated circuit with selected signal line coupling |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005004403A JP4450737B2 (ja) | 2005-01-11 | 2005-01-11 | 半導体集積回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006197023A JP2006197023A (ja) | 2006-07-27 |

| JP4450737B2 true JP4450737B2 (ja) | 2010-04-14 |

Family

ID=36654627

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005004403A Expired - Fee Related JP4450737B2 (ja) | 2005-01-11 | 2005-01-11 | 半導体集積回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7702884B2 (ja) |

| JP (1) | JP4450737B2 (ja) |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7422152B2 (en) | 2004-05-13 | 2008-09-09 | Cisco Technology, Inc. | Methods and devices for providing scalable RFID networks |

| US8458467B2 (en) * | 2005-06-21 | 2013-06-04 | Cisco Technology, Inc. | Method and apparatus for adaptive application message payload content transformation in a network infrastructure element |

| US7664879B2 (en) | 2004-11-23 | 2010-02-16 | Cisco Technology, Inc. | Caching content and state data at a network element |

| US7987272B2 (en) | 2004-12-06 | 2011-07-26 | Cisco Technology, Inc. | Performing message payload processing functions in a network element on behalf of an application |

| US7725934B2 (en) * | 2004-12-07 | 2010-05-25 | Cisco Technology, Inc. | Network and application attack protection based on application layer message inspection |

| US8082304B2 (en) | 2004-12-10 | 2011-12-20 | Cisco Technology, Inc. | Guaranteed delivery of application layer messages by a network element |

| US7606267B2 (en) * | 2004-12-10 | 2009-10-20 | Cisco Technology, Inc. | Reducing the sizes of application layer messages in a network element |

| US7698416B2 (en) * | 2005-01-25 | 2010-04-13 | Cisco Technology, Inc. | Application layer message-based server failover management by a network element |

| US8266327B2 (en) * | 2005-06-21 | 2012-09-11 | Cisco Technology, Inc. | Identity brokering in a network element |

| US7345585B2 (en) | 2005-08-01 | 2008-03-18 | Cisco Technology, Inc. | Network based device for providing RFID middleware functionality |

| US20070157030A1 (en) * | 2005-12-30 | 2007-07-05 | Feghali Wajdi K | Cryptographic system component |

| US20070192571A1 (en) * | 2006-02-14 | 2007-08-16 | Feghali Wajdi K | Programmable processing unit providing concurrent datapath operation of multiple instructions |

| US7797406B2 (en) * | 2006-07-27 | 2010-09-14 | Cisco Technology, Inc. | Applying quality of service to application messages in network elements based on roles and status |

| JP2008085864A (ja) * | 2006-09-28 | 2008-04-10 | Fujitsu Ltd | 半導体装置 |

| JP5023856B2 (ja) * | 2007-07-18 | 2012-09-12 | 富士ゼロックス株式会社 | 演算処理装置及び演算処理プログラム |

| US7817636B2 (en) * | 2008-01-30 | 2010-10-19 | Cisco Technology, Inc. | Obtaining information on forwarding decisions for a packet flow |

| JP5007838B2 (ja) * | 2009-03-05 | 2012-08-22 | 富士ゼロックス株式会社 | 情報処理装置および情報処理プログラム |

| US8417930B2 (en) * | 2010-04-26 | 2013-04-09 | Broadcom Corporation | Modular integrated circuit with uniform address mapping |

| JP5745165B2 (ja) * | 2011-05-17 | 2015-07-08 | アルテラ コーポレイションAltera Corporation | ハイブリッド統合型デバイスにおいてハードロジックとソフトロジックとの間をインターフェース接続するシステムおよび方法 |

| JP6176407B2 (ja) | 2014-09-11 | 2017-08-09 | 三菱電機株式会社 | 入出力制御装置、入出力制御方法、及びプログラム |

| CN107003966B (zh) | 2014-12-05 | 2020-01-14 | 三菱电机株式会社 | 写入许可电路、访问切换电路以及模拟数字变换单元 |

| CN108307131B (zh) * | 2016-12-27 | 2021-08-03 | 株式会社半导体能源研究所 | 摄像装置及电子设备 |

| US11442763B2 (en) * | 2019-04-26 | 2022-09-13 | Dell Products L.P. | Virtual machine deployment system using configurable communication couplings |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5542074A (en) * | 1992-10-22 | 1996-07-30 | Maspar Computer Corporation | Parallel processor system with highly flexible local control capability, including selective inversion of instruction signal and control of bit shift amount |

| US5361373A (en) * | 1992-12-11 | 1994-11-01 | Gilson Kent L | Integrated circuit computing device comprising a dynamically configurable gate array having a microprocessor and reconfigurable instruction execution means and method therefor |

| US6052773A (en) * | 1995-02-10 | 2000-04-18 | Massachusetts Institute Of Technology | DPGA-coupled microprocessors |

| US5752035A (en) * | 1995-04-05 | 1998-05-12 | Xilinx, Inc. | Method for compiling and executing programs for reprogrammable instruction set accelerator |

| JP3686733B2 (ja) | 1996-08-12 | 2005-08-24 | 富士通テン株式会社 | 制御用半導体集積回路およびそれを搭載する電子制御装置 |

| US6150837A (en) * | 1997-02-28 | 2000-11-21 | Actel Corporation | Enhanced field programmable gate array |

| JPH1115866A (ja) | 1997-06-25 | 1999-01-22 | Fuji Xerox Co Ltd | 回路装置、情報入出力装置、情報処理装置および回路装置の再構成システム |

| US6163836A (en) * | 1997-08-01 | 2000-12-19 | Micron Technology, Inc. | Processor with programmable addressing modes |

| US6034538A (en) * | 1998-01-21 | 2000-03-07 | Lucent Technologies Inc. | Virtual logic system for reconfigurable hardware |

| JP3616518B2 (ja) * | 1999-02-10 | 2005-02-02 | 日本電気株式会社 | プログラマブルデバイス |

| JP5148029B2 (ja) * | 1999-02-15 | 2013-02-20 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 構成可能な機能ユニットを備えるデータプロセッサ及びそのようなデータプロセッサを使用する方法 |

| JP3993438B2 (ja) | 2002-01-25 | 2007-10-17 | 株式会社ルネサステクノロジ | 半導体装置 |

| JP4546711B2 (ja) | 2002-10-07 | 2010-09-15 | パナソニック株式会社 | 通信装置 |

| US7225324B2 (en) * | 2002-10-31 | 2007-05-29 | Src Computers, Inc. | Multi-adaptive processing systems and techniques for enhancing parallelism and performance of computational functions |

| US7584345B2 (en) * | 2003-10-30 | 2009-09-01 | International Business Machines Corporation | System for using FPGA technology with a microprocessor for reconfigurable, instruction level hardware acceleration |

-

2005

- 2005-01-11 JP JP2005004403A patent/JP4450737B2/ja not_active Expired - Fee Related

- 2005-06-08 US US11/147,173 patent/US7702884B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006197023A (ja) | 2006-07-27 |

| US20060155969A1 (en) | 2006-07-13 |

| US7702884B2 (en) | 2010-04-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4450737B2 (ja) | 半導体集積回路 | |

| KR101024048B1 (ko) | 단일 칩 무선 송수신기 | |

| US6967999B2 (en) | Method and apparatus to support multi standard, multi service base-stations for wireless voice and data networks | |

| US20020015401A1 (en) | Flexible TDMA system architecture | |

| US20020031166A1 (en) | Wireless spread spectrum communication platform using dynamically reconfigurable logic | |

| US20110103440A1 (en) | Physical Layer Device Having a SERDES Pass Through Mode | |

| US8095173B2 (en) | Wireless communication device with physical-layer reconfigurable processing engines | |

| US7856246B2 (en) | Multi-cell data processor | |

| US20060004902A1 (en) | Reconfigurable circuit with programmable split adder | |

| US7193435B2 (en) | Programmable application specific integrated circuit for communication and other applications | |

| JP4475145B2 (ja) | ソフトウェア無線機及びライブラリ構成 | |

| JP2011503913A (ja) | 異なる通信標準間のハンドオフのシステムおよび方法 | |

| US20090196199A1 (en) | Wireless programmable logic device | |

| WO2022139909A1 (en) | Wireless communication within a control plane and a data plane | |

| CN102737007B (zh) | 一种支持多个数据单元任意置换的方法和装置 | |

| EP1768326B1 (en) | Signal processing device, method, program, and recording medium | |

| JP4410162B2 (ja) | リコンフィギュアブルlsi | |

| Tang et al. | Reconfigurable pipelined coprocessor for multi-mode communication transmission | |

| Martina et al. | On chip interconnects for multiprocessor turbo decoding architectures | |

| Saito et al. | Cluster architecture for reconfigurable signal processing engine for wireless communication | |

| Jamuna et al. | Dynamic reconfigurable modulator for communication systems | |

| JP5124100B2 (ja) | 再構成可能である通信回路 | |

| EP1700439B1 (en) | Universal derotator for umts modes | |

| Rajagopal et al. | Communication processors | |

| JP5599408B2 (ja) | Mimo受信信号を木探索に基づき検出する場合のデータフロー制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070710 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090911 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091104 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091222 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100119 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100126 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4450737 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130205 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140205 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |