本発明は薄膜トランジスタ(以下、TFTという)で構成された回路を有する半導体装置およびその作製方法に関する。例えば、液晶表示パネルに代表される電気光学装置や有機発光素子を有する発光表示装置を部品として搭載した電子機器に関する。

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

近年、絶縁表面を有する基板上に形成された半導体薄膜(厚さ数〜数百nm程度)を用いて薄膜トランジスタ(TFT)を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。

従来、TFT駆動によるアクティブマトリクス型の液晶表示装置においては、基板上に多数の走査線およびデータ線が縦横に設けられ、これらの配線の交点に対応して多数のTFTが設けられている。各TFTは、走査線にゲート配線が電気的に接続され、データ線にソース電極が電気的に接続され、画素電極にドレイン電極が電気的に接続される。

透過型の液晶表示装置においては、画素電極として透明導電膜、代表的にはITOが用いられている。透明導電膜からなる画素電極は、データ線や走査線などの配線と絶縁するための層間絶縁膜上に設けられている。従って、層間絶縁膜に形成したコンタクトホールを介して画素電極とドレイン電極とが接続されている。

特に、大面積の表示を行うディスプレイを製造する際、配線の抵抗による信号の遅延問題が顕著になってくる。従って、配線や電極の材料としては、電気抵抗値の低い材料、代表的にはアルミニウムが用いられている。

配線や電極の材料として用いられるアルミニウムと、画素電極の材料として用いられるITOとは、接合する上で相性が悪く、両者を直接接合させると電触腐食が生じてしまう問題があった。

さらに、直接、アルミニウム膜とITO膜とを接合させると、接合界面においてアルミニウムが酸化し、ITO膜は還元することになり、接触抵抗が変化してしまっていた。これは、アルミニウムとITO膜との電極電位が相違するために生じる電気化学的な反応により現象であることが知られている。

そこで、このような相性の悪い2つの膜からなる配線や電極等を接続する際に、アルミニウム配線(または電極)とITOとの間に高融点金属膜(チタン膜など)または高融点金属化合物膜(窒化チタン膜など)などを設けて、ITOとの電触腐食を防ぐ技術も提案されている。

また、本出願人は、薄膜トランジスタのドレインと画素電極であるITOとの接続をチタン膜、アルミニウム膜、チタン膜の積層膜で構成することを特許文献1、特許文献2、および特許文献3に記載している。

また、本出願人らは、薄膜トランジスタのドレインと画素電極であるITOとの接続をチタン膜、アルミニウム膜の積層膜で構成することを特許文献4に記載し、窒化チタン膜、アルミニウム膜の積層膜で構成することを特許文献5に記載している。

特開平9−45927号公報

特開平10−32202号公報

特開平6−232129号公報

特開2004−6974

特開平8−330600号公報

しかしながら、アルミニウム配線(または電極)とITOとの間にチタン膜や窒化チタン膜を積層すると、配線抵抗が高くなってしまい、特に画面サイズが大面積化すると消費電力の増大を引き起こす。配線抵抗は、配線となる金属膜の断面積を大きくすることにより低減することが可能であるが、膜厚を厚くして断面積を増大させた場合には基板表面と厚膜配線表面との間に段差が生じ、液晶の配向不良の原因となる。

また、TFT駆動によるアクティブマトリクス型の発光装置においても、発光素子の陽極(または陰極)として透明導電膜を用いる場合がある。同様に、透明導電膜からなる陽極は、各種配線と絶縁するための層間絶縁膜上に形成される。従って、陽極としてITOを用い、TFTの電極(アルミニウム)とを接続させる際、上述の電触腐食が同様に生じる。

本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

また、配線材料としてアルミニウムを用いてTFTを作製した場合、熱処理によってヒロックやウィスカー等の突起物の形成や、アルミニウム原子のチャネル形成領域への拡散により、TFTの動作不良やTFT特性の低下を引き起こしていた。そこで、従来ではアルミニウムに他の元素(Siなど)を含有させたアルミニウム合金膜として、ヒロックなどの発生を抑制している。しかし、アルミニウム合金膜としても、接合界面においてアルミニウムが酸化し、ITO膜が還元することによる接合抵抗は変化してしまう問題は残る。

加えて、本発明は、アクティブマトリクス型の表示装置において、配線材料としてアルミニウムを用いてもヒロックやウィスカー等の突起物の形成を防止し、且つ、アルミニウム原子のチャネル形成領域への拡散を防止し、且つ、良好なオーミック接合を可能とすることを課題とする。

本発明は、配線または電極をアルミニウム合金膜の単層とし、そのアルミニウム合金膜の組成を調節してITOとの良好なオーミック接合を目指すのではなく、3層構造とすることで上述した課題を解決するものである。

加えて、本発明は、アルミニウム配線(または電極)とITOとの間に高融点金属膜(チタン膜など)または高融点金属化合物膜(窒化チタン膜など)などを設けることなく、上述した課題を解決するものである。

本発明は、アルミニウム原子のチャネル形成領域への拡散を防止するために、TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。さらに、その第2導電層の上に、ITOと反応しないアルミニウム合金からなる第3導電層を設け、配線又は電極を3層構造としてITOと接合させることを特徴の一つとしている。

シリコンとアルミニウムの相互拡散を防止するために設けられる第1導電層の膜厚は、20nm〜200nmの範囲とすることが望ましい。

また、電気抵抗値を低くするため、アルミニウム単体からなる第2導電層中の酸素濃度は5×1018atoms/cm3以下、好ましくは1×1019atoms/cm3以下とすることが望ましい。第2導電層の膜厚は、0.1μm〜2μmの範囲とすることが望ましい。電気抵抗値の低いアルミニウム単体からなる第2導電層を用いることによって、さらなる細線化が可能となり、回路面積の縮小を図ることができる。

なお、ITOと反応しないアルミニウム合金からなる第3導電層は、Ni(ニッケル)、Ti(チタン)、Mo(モリブデン)、またはC(炭素)を含むアルミニウム合金膜とする。例えば、Al中に0.1atoms%以上10atoms%以下の炭素(C)と、0.5atoms%以上7atoms%以下のNiを含有しているアルミニウム炭素合金膜や、Al中に0.1atoms%以上10atoms%以下の炭素(C)と、1atoms%以上20atoms%以下のTiを含有しているアルミニウム炭素合金膜や、Al中に0.1atoms%以上10atoms%以下の炭素(C)を含有しているアルミニウム炭素合金膜を用いる。第3導電層の膜厚は、5nm以上200nm以下の範囲とすることが望ましい。なお、アルミニウム炭素合金は、アルミニウム−炭素系合金とも呼ばれる。

ただし、環境問題を考慮すると、Niは有害な材料の一つであるため、第3導電層は、Ti(チタン)、Mo(モリブデン)、またはC(炭素)を含むアルミニウム合金膜とすることが望ましい。

また、各層の表面を酸化させないように、これら3層を同じスパッタ装置で連続して形成することが好ましい。

本明細書で開示する発明の構成は、絶縁表面を有する基板上に、半導体薄膜を活性層とした複数の薄膜トランジスタと、透明導電膜とを有する半導体装置であり、前記半導体装置は、前記活性層と接するチタン単体またはモリブデン単体からなる第1導電層と、前記第1導電層上に接するアルミニウム単体からなる第2導電層と、前記第2導電層上に接する炭素を含むアルミニウム合金からなる第3導電層と、を順に積層した電極または配線を有し、前記第3導電層上に接する透明導電膜を有していることを特徴とする半導体装置である。

また、炭素を含むアルミニウム合金に代えて、炭素、及びチタンを含むアルミニウム合金を用いてもよく、他の発明の構成は、絶縁表面を有する基板上に、半導体薄膜を活性層とした複数の薄膜トランジスタと、透明導電膜とを有する半導体装置であり、前記半導体装置は、前記活性層と接するチタン単体またはモリブデン単体からなる第1導電層と、前記第1導電層上に接するアルミニウム単体からなる第2導電層と、前記第2導電層上に接する炭素、及びチタンを含むアルミニウム合金からなる第3導電層と、を順に積層した電極または配線を有し、前記第3導電層上に接する透明導電膜を有していることを特徴とする半導体装置である。

また、炭素を含むアルミニウム合金に代えて、炭素、及びニッケルを含むアルミニウム合金を用いてもよく、他の発明の構成は、絶縁表面を有する基板上に、半導体薄膜を活性層とした複数の薄膜トランジスタと、透明導電膜とを有する半導体装置であり、前記半導体装置は、前記活性層と接するチタン単体またはモリブデン単体からなる第1導電層と、前記第1導電層上に接するアルミニウム単体からなる第2導電層と、前記第2導電層上に接する炭素、及びニッケルを含むアルミニウム合金からなる第3導電層と、を順に積層した電極または配線を有し、前記第3導電層上に接する透明導電膜を有していることを特徴とする半導体装置である。

上記各構成において、前記透明導電膜を陽極または陰極とする発光素子、或いは、前記透明導電膜を画素電極とする液晶素子を有していることを特徴の一つとしている。

また、上記各構成において、前記第1導電層と、前記第2導電層と、前記第3導電層は、同じスパッタ装置内で連続して形成されたことを特徴としている。同じスパッタ装置内で連続して形成することにより、前記層の表面が酸化することがなく、結果として透明導電膜とのコンタクト抵抗及び配線抵抗を低くすることができる。

また、透明導電膜を先に形成した後、積層構造を有する電極を形成して薄膜トランジスタと透明導電膜とを電気的に接続させる場合の発光素子を有する半導体装置の作製方法も本発明の特徴の一つであり、その作製方法は、

絶縁表面を有する基板上に、半導体薄膜を活性層とした複数の薄膜トランジスタを形成する工程と、

前記薄膜トランジスタに接続する透明導電膜を形成する工程と、を有する工程であり、

前記透明導電膜及び前記活性層に接する電極は、少なくともモリブデン膜と、アルミニウム膜からなる積層構造を有しており、

前記電極は、アルミニウム膜をドライエッチングする工程と、同じマスクを用いてモリブデン膜をウエットエッチングする工程と、によってパターニングされ、

前記ウェットエッチングは、モリブデン膜を選択的に除去すると同時に前記透明導電膜の表面を洗浄することを特徴とする半導体装置の作製方法である。

上記作製方法とすることによって、透明導電膜(代表的にはITO)からなる陽極表面に点在する微小な粒子(0.1μm以下の球状の微小な粒)を前記ウェットエッチングで同時に除去することができる。この微小な粒子は、スパッタ法によるITO成膜中のゴミ、隔壁のウエットエッチング工程におけるゴミ、またはITO膜のパターニング工程におけるゴミであると思われる。この微小な粒子が、有機化合物を有する発光素子の作製直後において生じているダークスポットの主原因となっている。なお、透明導電膜における表面の洗浄を行わずに作製した発光素子の電気特性は、電圧に対する輝度変化はほとんどない一方、低電圧(3V〜5V)での駆動において極端に発光効率が低下するという異常が見られる。また、微小な粒によって電流が局所的に集中して輝点(周りよりも輝度の高い箇所)が発生する場合もある。

また、本発明は3層構造に限定されず、2層構造の配線としてもよい。特に、2層構造の配線上に透明導電膜を形成する場合に有効であり、本発明の他の構成は、絶縁表面を有する基板上に、アルミニウム単体を含む第1導電層と、前記第1導電層上に接する炭素を含むアルミニウム合金を含む第2導電層と、を積層した電極または配線を有し、前記第2導電層上に接する透明導電膜を有していることを特徴とする半導体装置である。この構成において、前記第2導電層に含まれる炭素の含有量は、0.1atoms%以上10atoms%以下であることを特徴の一つとしている。また、前記第2導電層は、さらにチタンを含み、そのチタンの含有量は、1atoms%以上20atoms%以下であることを特徴としている。また、前記第2導電層は、さらにモリブデンを含んでもよい。

なお、発光素子は、電場を加えることで発生するルミネッセンス(Electro Luminescence)が得られる有機化合物を含む層(以下、EL層と記す)と、陽極と、陰極とを有する。有機化合物におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)とがあるが、本発明の成膜装置および成膜方法により作製される発光装置は、どちらの発光を用いた場合にも適用可能である。

また、本明細書中において、第1の電極とは、発光素子の陽極、或いは陰極となる電極を指している。発光素子は、第1の電極と、該第1の電極上に有機化合物を含む層と、該有機化合物を含む層上に第2の電極とを有する構成となっており、形成順序において先に基板に形成する電極を第1の電極と呼んでいる。

また、第1の電極の配置としてはストライプ配列、デルタ配列、モザイク配列などを挙げることができる。

なお、本明細書中における発光装置とは、画像表示デバイス、発光デバイス、もしくは光源(照明装置含む)を指す。また、発光装置にコネクター、例えばFPC(Flexible printed circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または発光素子にCOG(Chip On Glass)方式によりIC(集積回路)が直接実装されたモジュールも全て発光装置に含むものとする。

また、本発明の発光装置において、画面表示の駆動方法は特に限定されず、例えば、点順次駆動方法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、発光装置のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であってもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

さらに、ビデオ信号がデジタルの発光装置において、画素に入力されるビデオ信号が定電圧(CV)のものと、定電流(CC)のものとがある。ビデオ信号が定電圧のもの(CV)には、発光素子に印加される電圧が一定のもの(CVCV)と、発光素子に印加される電流が一定のもの(CVCC)とがある。また、ビデオ信号が定電流のもの(CC)には、発光素子に印加される電圧が一定のもの(CCCV)と、発光素子に印加される電流が一定のもの(CCCC)とがある。

また、本発明の発光装置において、静電破壊防止のための保護回路(保護ダイオードなど)を設けてもよい。

また、アクティブマトリクス型とする場合、第1の電極に接続するTFTを複数設けるが、TFT構造に関係なく本発明を適用することが可能であり、例えば、トップゲート型TFTや、ボトムゲート型(逆スタガ型)TFTや、順スタガ型TFTを用いることが可能である。また、シングルゲート構造のTFTに限定されず、複数のチャネル形成領域を有するマルチゲート型TFT、例えばダブルゲート型TFTとしてもよい。

また、発光素子と電気的に接続するTFTはpチャネル型TFTであっても、nチャネル型TFTであってもよい。pチャネル型TFTと接続させる場合は、陽極と接続させ、陽極上に正孔注入層、正孔輸送層、発光層、電子輸送層と順次積層した後、陰極を形成すればよい。また、nチャネル型TFTと接続させる場合は、陰極と接続させ、陰極上に電子輸送層、発光層、正孔輸送層、正孔注入層と順次積層した後、陽極を形成すればよい。

また、TFTの活性層としては、非晶質半導体膜、結晶構造を含む半導体膜、非晶質構造を含む化合物半導体膜などを適宜用いることができる。さらにTFTの活性層として、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいるセミアモルファス半導体膜(微結晶半導体膜、マイクロクリスタル半導体膜とも呼ばれる)も用いることができる。

また、本明細書中において、画素電極とは、TFTと接続される電極であり、且つ、対向基板に設けられる対向電極と対となす電極を指している。また、液晶素子は、画素電極と、対向電極と、これらの電極に挟まれた液晶層とを指している。アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を駆動することによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。

本発明により、TFTとITOとを備えた半導体装置において、配線材料として純アルミニウムを用いてもヒロックやウィスカー等の突起物の形成を防止し、且つ、シリコンとアルミニウムの相互拡散を防止し、且つ、ITOとの良好なオーミック接合を可能とすることができる。また、このような優れた配線または電極が得られ、さらなる半導体装置の低消費電力化を実現することができる。

本発明の実施形態について、以下に説明する。

(実施の形態1)

ここでは、アクティブマトリクス型の発光装置の例に本発明を説明することとする。

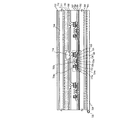

図1は、発光装置の画素部における一部を拡大した断面図である。以下に図1に示した発光素子を有する半導体装置の作製工程を示す。

まず、基板10上に下地絶縁膜11を形成する。基板10側を表示面として発光を取り出す場合、基板10としては、光透過性を有するガラス基板や石英基板を用いればよい。また、処理温度に耐えうる耐熱性を有する光透過性のプラスチック基板を用いてもよい。また、基板10側とは逆の面を表示面として発光を取り出す場合、前述の基板の他にシリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。ここでは基板10としてガラス基板を用いる。なお、ガラス基板の屈折率は1.55前後である。

下地絶縁膜11としては、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜を形成する。ここでは下地膜として2層構造を用いた例を示すが、前記絶縁膜の単層膜または2層以上積層させた構造を用いても良い。なお、特に下地絶縁膜を形成しなくてもよい。

次いで、下地絶縁膜上に半導体層を形成する。半導体層は、非晶質構造を有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)により成膜した後、公知の結晶化処理(レーザー結晶化法、熱結晶化法、またはニッケルなどの触媒を用いた熱結晶化法等)を行って得られた結晶質半導体膜を第1のフォトマスクを用いて所望の形状にパターニングして形成する。この半導体層の厚さは25〜80nm(好ましくは30〜70nm)の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム(SiGe)合金などで形成すると良い。

また、非晶質構造を有する半導体膜の結晶化処理として連続発振のレーザーを用いてもよく、非晶質半導体膜の結晶化に際し、大粒径に結晶を得るためには、連続発振が可能な固体レーザを用い、基本波の第2高調波〜第4高調波を適用するのが好ましい。代表的には、Nd:YVO4レーザー(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を適用すればよい。連続発振のレーザーを用いる場合には、出力10Wの連続発振のYVO4レーザから射出されたレーザ光を非線形光学素子により高調波に変換する。また、共振器の中にYVO4結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または楕円形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は0.01〜100MW/cm2程度(好ましくは0.1〜10MW/cm2)が必要である。そして、10〜2000cm/s程度の速度でレーザ光に対して相対的に半導体膜を移動させて照射すればよい。

次いで、レジストマスクを除去した後、半導体層を覆うゲート絶縁膜12を形成する。ゲート絶縁膜12はプラズマCVD法またはスパッタ法を用い、厚さを1〜200nmとする。好ましくは10nm〜50nmと薄くしてシリコンを含む絶縁膜の単層または積層構造で形成した後にマイクロ波によるプラズマを用いた表面窒化処理を行う。

このように膜厚の薄い絶縁膜をプラズマCVD法を用いる場合、成膜レートを遅くして薄い膜厚を制御性よく得る必要がある。例えば、RFパワーを100W、10kHz、圧力0.3Torr、N2Oガス流量400sccm、SiH4ガス流量1sccm、とすれば酸化珪素膜の成膜速度を6nm/minとすることができる。また、マイクロ波によるプラズマを用いた窒化処理は、マイクロ波源(2.45GHz)、および反応ガスである窒素ガスを用いて行う。

なお、ゲート絶縁膜12表面から離れるにつれて窒素濃度は減少する。これにより酸化珪素膜表面を高濃度に窒化できるだけでなく、酸化珪素膜と活性層の界面の窒素を低減し、デバイス特性の劣化を防ぐ。

次いで、ゲート絶縁膜12上に膜厚100〜600nmの導電膜を形成する。ここでは、スパッタ法を用い、TaN膜とW膜との積層からなる導電膜を形成する。なお、ここでは導電膜をTaN膜とW膜との積層としたが、特に限定されず、Ta、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料の単層、またはこれらの積層で形成してもよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。

次いで、第2のフォトマスクを用いてレジストマスクを形成し、ドライエッチング法またはウェットエッチング法を用いてエッチングを行う。このエッチング工程によって、導電膜をエッチングして、導電層14a、14bを得る。なお、導電層14a、14bはTFTのゲート電極となる。

次いで、レジストマスクを除去した後、第3のフォトマスクを用いてレジストマスクを新たに形成し、ここでは図示しないnチャネル型TFTを形成するため、半導体層にn型を付与する不純物元素(代表的にはリン、またはAs)を低濃度にドープするための第1のドーピング工程を行う。レジストマスクは、pチャネル型TFTとなる領域と、導電層の近傍とを覆う。この第1のドーピング工程によって絶縁膜を介してスルードープを行い、低濃度不純物領域を形成する。一つの発光素子は、複数のTFTを用いて駆動させるが、pチャネル型TFTのみで駆動させる場合には、上記ドーピング工程は特に必要ない。

次いで、レジストマスクを除去した後、第4のフォトマスクを用いてレジストマスクを新たに形成し、半導体にp型を付与する不純物元素(代表的にはボロン)を高濃度にドープするための第2のドーピング工程を行う。この第2のドーピング工程によってゲート絶縁膜12を介してスルードープを行い、p型の高濃度不純物領域17、18を形成する。

次いで、第5のフォトマスクを用いてレジストマスクを新たに形成し、ここでは図示しないnチャネル型TFTを形成するため、半導体にn型を付与する不純物元素(代表的にはリン、またはAs)を高濃度にドープするための第3のドーピング工程を行う。第3のドーピング工程におけるイオンドープ法の条件はドーズ量を1×1013〜5×1015/cm2とし、加速電圧を60〜100keVとして行う。レジストマスクは、pチャネル型TFTとなる領域と、導電層の近傍とを覆う。この第3のドーピング工程によってゲート絶縁膜12を介してスルードープを行い、n型の高濃度不純物領域を形成する。

この後、レジストマスクを除去し、水素を含む第1の層間絶縁膜13を成膜した後、半導体層に添加された不純物元素の活性化および水素化を行う。水素を含む第1の層間絶縁膜13は、PCVD法により得られる窒化酸化珪素膜(SiNO膜)を用いる。加えて、結晶化を助長する金属元素、代表的にはニッケルを用いて半導体膜を結晶化させている場合、活性化と同時にチャネル形成領域19におけるニッケルの低減を行うゲッタリングをも行うことができる。

次いで、層間絶縁膜の2層目となる平坦化絶縁膜16を形成する。平坦化絶縁膜16としては、塗布法によって得られるシリコン(Si)と酸素(O)との結合で骨格構造が構成されるシロキサンのような絶縁膜を用いる。

次いで、第6のマスクを用いてエッチングを行い、平坦化絶縁膜16にコンタクトホールを形成すると同時に周縁部の平坦化絶縁膜を除去する。ここでは、第1の層間絶縁膜13と選択比が取れる条件でエッチング(ウェットエッチングまたはドライエッチング)を行う。用いるエッチング用ガスに限定はないが、ここではCF4、O2、He、Arとを用いることが適している。CF4の流量を380sccm、O2の流量を290sccm、Heの流量を500sccm、Arの流量を500sccm、RFパワーを3000W、圧力を25Paとし、ドライエッチングを行う。なお、第1の層間絶縁膜13上に残渣を残すことなく平坦化絶縁膜をエッチングするためには、10〜20%程度の割合でエッチング時間を増加させると良い。1回のエッチングでテーパー形状としてもよいし、複数のエッチングによってテーパー形状にしてもよい。ここでは、さらにCF4、O2、Heを用いて、CF4の流量を550sccm、O2の流量を450sccm、Heの流量を350sccm、RFパワーを3000W、圧力を25Paとする2回目のドライエッチングを行ってテーパー形状とする。平坦化絶縁膜の端部におけるテーパー角θは、30°を越え75°未満とすることが望ましい。

次いで、第6のマスクをそのままマスクとしてエッチングを行い、露呈しているゲート絶縁膜12、および第1の層間絶縁膜13を選択的に除去する。エッチング用ガスにCHF3とArを用いてゲート絶縁膜12、および第1の層間絶縁膜13のエッチング処理を行う。なお、半導体層上に残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させると良い。

次いで、第6のマスクを除去し、コンタクトホールで半導体層と接する3層構造からなる導電膜を形成する。なお、各層の表面を酸化させないように、これら3層を同じスパッタ装置で連続して形成することが好ましい。次いで、第7のマスクを用いてエッチングを行い、配線または電極を形成する。

シリコンとアルミニウムの相互拡散を防止するための第1導電層22aは、Ti単体、またはMo単体を用い、20nm〜200nmの膜厚範囲とする。

また、配線の電気抵抗値を低くするための第2導電層22bは、アルミニウム単体を用い、0.1μm〜2μmの膜厚範囲とする。

また、ITOと反応しないアルミニウム合金からなる第3導電層22cは、Ti(チタン)、Mo(モリブデン)、またはC(炭素)を含むアルミニウム合金膜を用いる。第3導電層22cの膜厚は、5nm〜200nmの範囲とする。

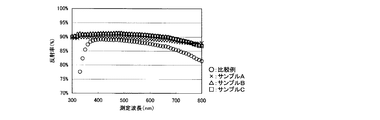

図2にスパッタ法で成膜したTi(チタン)、またはC(炭素)を含むアルミニウム合金膜の膜厚200nmの反射率のデータを示す。図2において、縦軸は反射率(%)を示し、横軸は、測定波長(nm)を示している。比較例は、アルミニウム単体ターゲットを用いたアルミニウム膜である。また、サンプルAは、アルミニウム単体ターゲット(φ6インチ)上にTiのペレット(面積0.5cm2)とCのペレット(面積0.5cm2)を設置して成膜を行ったTiを含むアルミニウム炭素合金膜である。なお、このサンプルをESCAで測定したところ、Al膜中にTiは2.7atoms%含まれ、Cは1atoms%以下であった。

また、サンプルBは、アルミニウム単体ターゲット上にCのペレット(面積0.5cm2)を設置して成膜を行ったアルミニウム炭素合金膜である。また、サンプルCは、アルミニウム単体ターゲット上にCのペレット(面積1cm2)を設置して成膜を行ったアルミニウム炭素合金膜である。

Tiを含むアルミニウム炭素合金膜、及びアルミニウム炭素合金膜は、アルミニウム膜(比較例)よりも短波長域で反射率が高く、平坦性が優れていることが図2から読み取れる。

また、上記サンプルをそれぞれ300℃のベークを行った後、再び反射率を測定したデータを図3に示す。

300℃のベークにより、アルミニウム膜(比較例)の反射率が変化するのに対し、Tiを含むアルミニウム炭素合金膜、及びアルミニウム炭素合金膜は、ほとんど変化していないことが図3から読み取れる。即ち、アルミニウム膜(比較例)はベークにより、表面にヒロックや酸化膜が形成され、反射率が低下してしまっていると考えられる。この結果から、Tiを含むアルミニウム炭素合金膜、及びアルミニウム炭素合金膜は、表面にヒロックや酸化膜が形成されにくいと言える。

また、ベーク前後での上記サンプルの抵抗率(μΩcm)をそれぞれ測定した。ベーク前に測定した結果を表1に示す。また、ベーク後に測定した結果を表2に示す。

表1に示すように、アルミニウム膜(比較例)については、ベーク前の抵抗率が、4.8(μΩcm)、表2に示すようにベーク後の抵抗率が4.5(μΩcm)であった。また、サンプルAについては、ベーク前の抵抗率が、12.7(μΩcm)、ベーク後の抵抗率が9.5(μΩcm)であった。また、サンプルBについては、ベーク前の抵抗率が、5.3(μΩcm)、ベーク後の抵抗率が4.3(μΩcm)であった。また、サンプルCについては、ベーク前の抵抗率が、6.3(μΩcm)、ベーク後の抵抗率が4.8(μΩcm)であった。

次いで、上記三層構造を有する配線または電極に接して透明導電膜を形成する。透明導電膜と第3導電層22cとを直接接して形成しても、良好なオーミック接合を得ることができる。そして、第8のマスクを用いてエッチングを行い、第1の電極23R、23G、即ち、有機発光素子の陽極(或いは陰極)を形成する。

第1の電極の材料として、ITO(酸化インジウムスズ)、またはITSO(ITOに酸化珪素が2〜10重量%含まれたターゲットを用いてスパッタリング法で得られる酸化珪素を含む酸化インジウムスズ)を用いる。ITSOの他、酸化珪素を含み酸化インジウムに2〜20%の酸化亜鉛(ZnO)を混合した透光性酸化物導電膜(IZO)などの透明導電膜を用いても良い。また、酸化珪素を含むATO(アンチモン・チン・オキサイド)の透明導電膜を用いても良い。

なお、第1の電極23R、23GとしてITOを用いる場合は、電気抵抗値を下げるために結晶化させるベークを行う。対して、ITSOやIZOは、ベークを行ってもITOのように結晶化せず、アモルファス状態のままである。

次いで、第8のマスクを用いて第1の電極23R、23Gの端部を覆う絶縁物29(バンク、隔壁、障壁、土手などと呼ばれる)を形成する。絶縁物29としては、塗布法により得られる有機樹脂膜、またはSOG膜(例えば、アルキル基を含むSiOx膜)を膜厚0.8μm〜1μmの範囲で用いる。

次いで、有機化合物を含む層24R、24Gを、蒸着法または塗布法を用いて積層形成する。なお、信頼性を向上させるため、有機化合物を含む層24R、24Gの形成前に真空加熱を行って脱気を行うことが好ましい。例えば、有機化合物材料の蒸着を行う前に、基板に含まれるガスを除去するために減圧雰囲気や不活性雰囲気で200℃〜300℃の加熱処理を行うことが望ましい。有機化合物を含む層24R、24Gの形成に蒸着法を用い、真空度が5×10-3Torr(0.665Pa)以下、好ましくは10-4〜10-6Torrまで真空排気された成膜室で蒸着を行う。蒸着の際、予め、抵抗加熱により有機化合物は気化されており、蒸着時にシャッターが開くことにより基板の方向へ飛散する。気化された有機化合物は、上方に飛散し、メタルマスクに設けられた開口部を通って基板に蒸着される。

なお、フルカラー化するために、発光色(R、G、B)ごとにマスクのアライメントを行う。

有機化合物を含む層24R、24Gは積層であり、第1の電極上に正孔注入層、正孔輸送層、発光層、電子輸送層と順次形成する。例えば、有機化合物を含む層24Rのうち、発光層としてDCMが添加されたAlq3を40[nm]成膜する。また、有機化合物を含む層24Gのうち、発光層としてDMQDが添加されたAlq3を40[nm]成膜する。また、ここでは図示していないが青色の青色の発光層としてCBP(4,4’−ビス(N−カルバゾリル)−ビフェニル)が添加されたPPD(4,4’−ビス(N−(9−フェナントリル)−N−フェニルアミノ)ビフェニル)を30nm、ブロッキング層としてSAlq(ビス(2−メチル−8−キノリノラト)(トリフェニルシラノラト)アルミニウム)を10[nm]成膜する。

次いで、第2の電極25、即ち、有機発光素子の陰極(或いは陽極)を形成する。第2の電極25の材料としては、MgAg、MgIn、AlLi、CaF2、CaNなどの合金、または周期表の1族もしくは2族に属する元素とアルミニウムとを共蒸着法により形成した膜を用いればよい。

また、第2の電極25を形成する前に陰極バッファ層としてCaF2、MgF2、またはBaF2からなる透光性を有する層(膜厚1nm〜5nm)を形成してもよい。

また、第2の電極25を保護する保護層を形成してもよい。

次いで、封止基板33をシール材(図示しない)で貼り合わせて発光素子を封止する。なお、一対の基板およびシール材で囲まれた領域27には乾燥した不活性気体、或いは透明な充填材を充填する。不活性気体としては希ガスまたは窒素を用いることができ、乾燥させるための乾燥剤を封止基板33に配置する。また、充填材としては、透光性を有している材料であれば特に限定されず、代表的には紫外線硬化または熱硬化のエポキシ樹脂を用いればよい。なお、充填材を一対の基板間に充填すると、全体の透過率を向上させることができる。

第1の電極を透明材料、第2の電極を金属材料とすれば、基板10を通過させて光を取り出す構造、即ちボトムエミッション型となる。また、第1の電極を金属材料、第2の電極を透明材料とすれば、封止基板33を通過させて光を取り出す構造、即ちトップエミッション型となる。また、第1の電極および第2の電極を透明材料とすれば、基板10と封止基板33の両方を通過させて光を取り出す構造とすることができる。本発明は、適宜、いずれか一の構造とすればよい。

また、基板10を通過させて光を取り出す際、発光層から放出される発光が通過する層、即ち、第1の電極、1層目の第1の層間絶縁膜13、2層目の層間絶縁膜である平坦化絶縁膜16、ゲート絶縁膜12、下地絶縁膜11には全て酸化珪素(約1.46前後)が含まれているため、それぞれの屈折率の差が小さくなって光の取り出し効率が向上する。即ち、屈折率の異なる材料層間での迷光を抑えることができる。

(実施の形態2)

ここでは、実施の形態1とは透明導電膜と、三層構造の電極の形成順序が異なる例を図4を用いて以下に説明する。

なお、平坦化絶縁膜16を形成するまでの工程は、実施の形態1と同一であるのでここでは詳細な説明は省略する。また、図4において、図1と同一の箇所には同じ符号を用いる。

まず、実施の形態1に示した工程に従って、平坦化絶縁膜16を形成する。次いで、透明導電膜を成膜して、パターニングを行い、第1の電極423R、423Gを形成する。

次いで、平坦化絶縁膜16を選択的にエッチングして、p型の高濃度不純物領域17に達するコンタクトホールを形成する。次いで、第1の電極およびp型の高濃度不純物領域17に接するモリブデン金属膜を成膜する。次いで、連続的にアルミニウム膜、アルミニウム合金膜を積層成膜する。その後、パターニングを行って第1導電層422a、第2導電層422b、および第3導電層422cを形成する。

シリコンとアルミニウムの相互拡散を防止するための第1導電層422aは、Mo単体を用い、20nm〜200nmの膜厚範囲とする。

また、配線の電気抵抗値を低くするための第2導電層422bは、アルミニウム単体を用い、0.1μm〜2μmの膜厚範囲とする。

また、アルミニウム合金からなる第3導電層422cは、Ti(チタン)、またはC(炭素)を含むアルミニウム合金膜を用いる。第3導電層422cの膜厚は、5nm〜200nmの範囲とする。

上記3層からなる電極パターニングの際、複数種類のエッチング方法を用いる。まず、ドライエッチングによって422c、422bを選択的に除去した後、ウェットエッチングによって422aを除去する。ウェットエッチングを用いることで、第1の電極にダメージを与えず、且つ、第1の電極表面を洗浄することもできる。

次いで、実施の形態1に示した工程と同様にして第1の電極423R、423Gの端部を覆う絶縁物29を形成する。以降の工程は実施の形態1と同一であるのでここでは詳細な説明は省略することとする。

図4に示す構造とすることで、第1導電層422aがp型の高濃度不純物領域17に接し、且つ、透明導電膜とも接して良好なオーミック接合を得ることができる。

また、本実施の形態は実施の形態1と自由に組み合わせることができる。

(実施の形態3)

ここでは、透明導電膜と、三層構造の電極との間にもう一層の絶縁膜を設けた例を図5を用いて以下に説明する。

なお、第1導電層22a、第2導電層22b、及び第3導電層22cからなる電極を形成するまでの工程は、実施の形態1と同一であるのでここでは詳細な説明は省略する。また、図5において、図1と同一の箇所には同じ符号を用いる。

まず、実施の形態1に示した工程に従って、三層構造の電極を形成する。次いで、層間絶縁膜の3層目となる平坦化絶縁膜520を形成する。平坦化絶縁膜520としては、塗布法によって得られるシリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜を用いる。ここでは3層目の平坦化絶縁膜520で平坦化を行うため、平坦化絶縁膜16は特に平坦でなくともよく、例えば、PCVD法による無機絶縁膜を用いてもよい。

次いで、平坦化絶縁膜520を選択的にエッチングして、第3導電層22cに達するコンタクトホールを形成する。次いで、透明導電膜を成膜して、パターニングを行い、第1の電極523R、523Gを形成する。

次いで、実施の形態1に示した工程と同様にして第1の電極523R、523Gの端部を覆う絶縁物529を形成する。次いで、有機化合物を含む層524R、524Gを、蒸着法または塗布法を用いて積層形成する。以降の工程は実施の形態1と同一であるのでここでは詳細な説明は省略することとする。実施の形態1に従って、第2の電極525を形成し、封止基板533をシール材で貼り合わせて発光素子を封止する。なお、一対の基板およびシール材で囲まれた領域527には乾燥した不活性気体、或いは透明な充填材を充填する。

図5に示す構造とすることで、実施の形態1に比べて第1の電極面積を広くすることが可能となり、発光領域を広くすることができる。

また、本実施の形態は実施の形態1と自由に組み合わせることができる。

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

本実施例では、フルカラーの発光装置の説明を図6を用いて説明する。図6はアクティブマトリクス型の発光装置の一部断面を示す図である。

第1の基板1001上には、下地絶縁膜1002が設けられ、その上に3つのTFT1003R、1003G、1003Bを設けている。これらのTFTは、チャネル形成領域1020と、ソース領域またはドレイン領域1021、1022とを活性層とし、ゲート絶縁膜1005と、ゲート電極1023a、1023bを有するpチャネル型TFTである。また、ゲート電極は2層となっており、テーパー形状となっている下層1023aと、上層1023bとで構成されている。

また、層間絶縁膜1006はPCVD法による無機絶縁膜である。また、平坦化絶縁膜1007は、塗布法による平坦な層間絶縁膜である。

発光素子においては、第1の電極を平坦とすることが重要であり、平坦化絶縁膜1007が平坦でない場合、平坦化絶縁膜1007の表面凹凸の影響によって第1の電極も平坦とならない恐れがある。従って、平坦化絶縁膜1007の平坦性は重要である。

また、TFTのドレイン配線、またはソース配線1024a、1024b、1024cは、3層構造としている。ここでは、Ti膜と、Al単体膜、Tiを含むアルミニウム炭素合金膜との積層膜を用いる。TFTのドレイン配線、またはソース配線は、層間絶縁膜のカバレッジを考慮して、テーパー形状とすることが好ましい。

また、隔壁1009は樹脂であり、異なる発光を示す有機化合物を含む層との仕切りの役目を果たしている。従って、隔壁1009は、一つの画素、即ち、発光領域を囲むように格子形状としている。また、異なる発光を示す有機化合物を含む層が隔壁上で重なってもよいが、隣り合う画素の第1の電極とは重ならないようにする。

赤色の発光素子は、透明導電材料からなる第1の電極1008と、有機化合物を含む層1015Rと、第2の電極1010とで構成されている。青色の発光素子は、透明導電材料からなる第1の電極1008と、有機化合物を含む層1015Bと、第2の電極1010とで構成されている。緑色の発光素子は、透明導電材料からなる第1の電極1008と、有機化合物を含む層1015Gと、第2の電極1010とで構成されている。

また、第1の電極1008及び第2の電極1010は仕事関数を考慮して材料を選択する必要がある。但し第1の電極及び第2の電極は、画素構成によりいずれも陽極、又は陰極となりうる。駆動用TFTの極性がpチャネル型である場合、第1の電極を陽極、第2の電極を陰極とするとよい。また、駆動用TFTの極性がNチャネル型である場合、第1の電極を陰極、第2の電極を陽極とすると好ましい。

また、有機化合物を含む層1015R、1015G、1015Bは、第1の電極(陽極)側から順に、HIL(ホール注入層)、HTL(ホール輸送層)、EML(発光層)、ETL(電子輸送層)、EIL(電子注入層)の順に積層されている。なお、有機化合物を含む層は、積層構造以外に単層構造、又は混合構造をとることができる。フルカラーとするため、有機化合物を含む層1015R、1015G、1015Bは、それぞれ選択的に形成して、R、G、Bの3種類の画素を形成する。

また、水分や脱ガスによるダメージから発光素子を保護するため、第2の電極1010を覆う保護膜1011、1012を設けることが好ましい。保護膜1011、1012としては、PCVD法による緻密な無機絶縁膜(SiN、SiNO膜など)、スパッタ法による緻密な無機絶縁膜(SiN、SiNO膜など)、炭素を主成分とする薄膜(DLC膜、CN膜、アモルファスカーボン膜)、金属酸化物膜(WO2、CaF2、Al2O3など)などを用いることが好ましい。

第1の基板1001と第2の基板1016との間の間隔1014には、充填材料または不活性ガスを充填する。窒素などの不活性ガスを充填する場合は、乾燥させるための乾燥剤を間隔1014に設けることが好ましい。

また、発光素子の光は、第1の基板1001を通過して取り出される。図6に示す構造は下方出射型の発光装置である。

また、ここではトップゲート型TFTを例として説明したが、TFT構造に関係なく本発明を適用することが可能であり、例えばボトムゲート型(逆スタガ型)TFTや順スタガ型TFTに適用することが可能である。

また、本実施例は実施の形態1、実施の形態2、または実施の形態3と自由に組み合わせることができる。

本実施例では、画素部と駆動回路と端子部とを同一基板上に形成し、両方の基板から光を取り出すことのできる発光装置の例を図7に示す。

基板610上に下地絶縁膜を形成した後、各半導体層を形成する。次いで、半導体層を覆うゲート絶縁膜を形成した後、各ゲート電極、端子電極を形成する。次いで、nチャネル型TFT636を形成するため、半導体にn型を付与する不純物元素(代表的にはリン、またはAs)をドープし、pチャネル型TFT637を形成するため、半導体にp型を付与する不純物元素(代表的にはボロン)をドープしてソース領域およびドレイン領域、必要であればLDD領域を適宜形成する。次いで、PCVD法により得られる水素を含む窒化酸化珪素膜(SiNO膜)を形成した後、半導体層に添加された不純物元素の活性化および水素化を行う。

次いで、層間絶縁膜となる平坦化絶縁膜616を形成する。平坦化絶縁膜616としては、塗布法によって得られるシリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜を用いる。

次いで、マスクを用いて平坦化絶縁膜にコンタクトホールを形成すると同時に周縁部の平坦化絶縁膜を除去する。

次いで、平坦化絶縁膜616をマスクとしてエッチングを行い、露呈している水素を含むSiNO膜またはゲート絶縁膜を選択的に除去する。

次いで、導電膜を形成した後、マスクを用いてエッチングを行い、ドレイン配線やソース配線を形成する。

次いで、第1の電極623、即ち、有機発光素子の陽極(或いは陰極)を形成する。

次いで、塗布法により得られるSOG膜(例えば、アルキル基を含むSiOx膜)をパターニングして、第1の電極623の端部を覆う絶縁物629(バンク、隔壁、障壁、土手などと呼ばれる)を形成する。

次いで、有機化合物を含む層624を、蒸着法または塗布法を用いて形成する。次いで、透明導電膜からなる第2の電極625、即ち、有機発光素子の陰極(或いは陽極)を形成する。次いで、蒸着法またはスパッタ法により透明保護層626を形成する。透明保護層626は、第2の電極625を保護する。

次いで、透明な封止基板633をシール材628で貼り合わせて発光素子を封止する。即ち、発光表示装置は、表示領域の外周をシール材で囲み、一対の基板で封止される。TFTの層間絶縁膜は、基板全面に設けられているため、シール材のパターンが層間絶縁膜の外周縁よりも内側に描画された場合、シール材のパターンの外側に位置する層間絶縁膜の一部から水分や不純物が浸入する恐れがある。従って、TFTの層間絶縁膜として用いる平坦化絶縁膜の外周は、シール材のパターンの内側、好ましくは、シール材パターンと重なるようにして平坦化絶縁膜の端部をシール材が覆うようにする。なお、シール材628で囲まれた領域には透明な充填材627を充填する。

最後にFPC632を異方性導電膜631により公知の方法で端子電極と貼りつける。端子電極は、透明導電膜を用いることが好ましく、ゲート配線と同時に形成された端子電極上に形成する。(図7)

また、発光素子の光は、基板610及び封止基板633を通過して両側に取り出される。図7に示す構造は、基板と封止基板の両方を通過させて光を取り出す構造の発光装置である。

以上の工程によって、画素部と駆動回路と端子部とを同一基板上に形成することができる。

また、本実施例は実施の形態1、実施の形態2、または実施の形態3と自由に組み合わせることができる。

本実施例は、上記実施例によって作製されるEL表示パネルにFPCや、駆動用の駆動ICを実装する例について説明する。

図8(A)に示す図は、FPC1209を4カ所の端子部1208に貼り付けた発光装置の上面図の一例を示している。基板1210上には発光素子及びTFTを含む画素部1202と、TFTを含むゲート側駆動回路1203と、TFTを含むソース側駆動回路1201とが形成されている。TFTの活性層が結晶構造を有する半導体膜で構成されている場合には同一基板上にこれらの回路を形成することができる。従って、システムオンパネル化を実現したEL表示パネルを作製することができる。

なお、基板1210はコンタクト部以外において保護膜で覆われており、保護膜上に光触媒機能を有する物質を含む下地層が設けられている。

また、画素部を挟むように2カ所に設けられた接続領域1207は、発光素子の第2の電極を下層の配線とコンタクトさせるために設けている。なお、発光素子の第1の電極は画素部に設けられたTFTと電気的に接続している。

また、封止基板1204は、画素部および駆動回路を囲むシール材1205、およびシール材に囲まれた充填材料によって基板1210と固定されている。また、透明な乾燥剤を含む充填材料を充填する構成としてもよい。また、画素部と重ならない領域に乾燥剤を配置してもよい。

また、図8(A)に示した構造は、XGAクラスの比較的大きなサイズ(例えば対角4.3インチ)の発光装置で好適な例を示したが、図8(B)は、狭額縁化させた小型サイズ(例えば対角1.5インチ)で好適なCOG方式を採用した例である。

図8(B)において、基板1310上に駆動IC1301が実装され、駆動ICの先に配置された端子部1308にFPC1309を実装している。実装される駆動IC1301は、生産性を向上させる観点から、一辺が300mmから1000mm以上の矩形状の基板上に複数個作り込むとよい。つまり、基板上に駆動回路部と入出力端子を一つのユニットとする回路パターンを複数個形成し、最後に分割して取り出せばよい。ドライバICの長辺の長さは、画素部の一辺の長さや画素ピッチを考慮して、長辺が15〜80mm、短辺が1〜6mmの矩形状に形成してもよいし、画素領域の一辺、又は画素部の一辺と各駆動回路の一辺とを足した長さに形成してもよい。

駆動ICのICチップに対する外形寸法の優位性は長辺の長さにあり、長辺が15〜80mmで形成された駆動ICを用いると、画素部に対応して実装するのに必要な数がICチップを用いる場合よりも少なくて済み、製造上の歩留まりを向上させることができる。また、ガラス基板上に駆動ICを形成すると、母体として用いる基板の形状に限定されないので生産性を損なうことがない。これは、円形のシリコンウエハからICチップを取り出す場合と比較すると、大きな優位点である。

また、TAB方式を採用してもよく、その場合は、複数のテープを貼り付けて、該テープに駆動ICを実装すればよい。COG方式の場合と同様に、単数のテープに単数の駆動ICを実装してもよく、この場合には、強度の問題から、駆動ICを固定する金属片等を一緒に貼り付けるとよい。

また、基板1310もコンタクト部以外において保護膜で覆われており、保護膜上に光触媒機能を有する物質を含む下地層が設けられている。

また、画素部1302と駆動IC1301の間に設けられた接続領域1307は、発光素子の第2の電極を下層の配線とコンタクトさせるために設けている。なお、発光素子の第1の電極は画素部に設けられたTFTと電気的に接続している。

また、封止基板1304は、画素部1302を囲むシール材1305、およびシール材に囲まれた充填材料によって基板1310と固定されている。

また、TFTの活性層として非晶質半導体膜を用いる場合には、駆動回路を同一基板上に形成することは困難であるため、大きなサイズであっても図8(B)の構成となる。

また、本実施例は実施の形態1、実施の形態2、実施の形態3、実施例1、または実施例2と自由に組み合わせることができる。

本実施例では、画素部と駆動回路と端子部とを同一基板上に形成した液晶表示装置の例を図9に示す。図9は、カラーフィルタを用いない液晶パネルの断面図を示している。

カラーフィルタを用いない液晶パネルと偏光板によって光シャッタを構成し、RGBの3色のバックライト光源を高速で点滅させるフィールドシーケンシャル方式の駆動方法を用いる。フィールドシーケンシャル方式は、人間の目の時間的な能力の限界を利用し、連続時間的な加法混色によってカラー表示を実現するものである。

第1の基板701上には、下地絶縁膜702が設けられ、その上に3つのTFT703を設けている。これらのTFTは、チャネル形成領域720と、低濃度不純物領域725、726と、ソース領域またはドレイン領域721、722とを活性層とし、ゲート絶縁膜705と、ゲート電極723a、723bを有するnチャネル型TFTである。また、ゲート電極は2層となっており、テーパー形状となっている第1層723aと、第2層723bとの積層で構成されている。

また、層間絶縁膜706はPCVD法による無機絶縁膜である。平坦化絶縁膜707は、塗布法による平坦な層間絶縁膜である。

また、TFTのドレイン配線、またはソース配線724a、724b、724cは、3層構造としている。ここでは、Ti膜と、Al単体膜、Niを含むアルミニウム炭素合金膜の順で形成した積層膜を用いる。TFTのドレイン配線、またはソース配線は、層間絶縁膜のカバレッジを考慮して、テーパー形状とすることが好ましい。

また、画素電極708は、ITO(酸化インジウムスズ)、ITSO(ITOに酸化珪素が2〜10重量%含まれたターゲットを用いてスパッタリング法で得られる酸化珪素を含む酸化インジウムスズ)、酸化珪素を含み酸化インジウムに2〜20%の酸化亜鉛(ZnO)を混合した透光性酸化物導電膜(IZO)、酸化珪素を含むATO(アンチモン・チン・オキサイド)などの透明導電膜を用いることができる。画素電極708としてITOを用いても、画素電極と接する第3導電層がNiを含むアルミニウム炭素合金膜であるため、電触などの不良は生じず、良好なオーミックコンタクトも得ることができる。

また、柱状スペーサ714は樹脂であり、基板間隔を一定に保つ役目を果たしている。従って、柱状スペーサ714は、等間隔で配置されている。また、高速応答させるため、基板間隔は2μm以下にすることが好ましく、柱状スペーサ714の高さを適宜調節する。また、2インチ角以下の小さい画面サイズの場合には、柱状スペーサは特に設けなくともよく、シール材に含ませるフィラーなどのギャップ材のみで基板間隔を調節してもよい。

また、柱状スペーサ714及び画素電極708を覆う配向膜710も設ける。対向基板となる第2の基板716にも配向膜712を設け、シール材(図示しない)で第1の基板701と第2の基板716を貼り合わせている。

また、第1の基板701と第2の基板716との間の間隔には、液晶材料711を充填する。液晶材料711は、シール材を閉パターンとして気泡が入らないように減圧下で液晶の滴下を行い、両方の基板を貼り合わせる方法を用いてもよいし、開口部を有するシールパターンを設け、TFT基板を貼りあわせた後に毛細管現象を用いて液晶を注入するディップ式(汲み上げ式)を用いてもよい。

本実施例の液晶パネルは、いわゆるπセル構造を有しており、OCB(Optically Compensated Bend)モードという表示モードを用いる。πセル構造とは、液晶分子のプレチルト角がアクティブマトリクス基板と対向基板との基板間の中心面に対して面対称の関係で配向された構造である。πセル構造の配向状態は、基板間に電圧が印加されていない時はスプレイ配向となり、電圧を印加するとベンド配向に移行する。さらに電圧を印加するとベンド配向の液晶分子が両基板と垂直に配向し、光が透過する状態となる。なお、OCBモードにすると、従来のTNモードより約10倍速い高速応答性を実現できる。

また、液晶パネルは一対の光学フィルム(偏光板、位相差板など)731、732の間に挟む。加えて、OCBモードによる表示においては、リタデーションの視角依存性を3次元的に補償するため、2軸性位相差板を用いることが好ましい。

図9に示す液晶パネルのバックライトとしてRGBの3色のLED735として用いる。LED735の光は導光板734によって導出される。フィールドシーケンシャル駆動方法においては、LED点灯期間TR期間、TG期間およびTB期間に、それぞれR、G、BのLEDが順に点灯する。赤のLEDの点灯期間(TR)には、赤に対応したビデオ信号(R1)が液晶パネルに供給され、液晶パネルに赤の1画像画面分の信号が書き込まれる。また、緑のLEDの点灯期間(TG)には、緑に対応したビデオ信号(G1)が液晶パネルに供給され、液晶パネルに緑の画像1画面分が書き込まれる。また、青のLEDの点灯期間(TB)には、青に対応したビデオ信号(B1)が液晶表示装置に供給され、液晶表示装置に青の1画像画面分の信号が書き込まれる。これらの3回の画像の書き込みにより、1フレームが形成される。

本発明を実施して得たELパネルまたは液晶パネルを組み込むことによって様々な電子機器を作製することができる。電子機器としては、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD))等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それらの電子機器の具体例を図10、図11に示す。

図10(A)はテレビであり、筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含む。本発明はテレビに内蔵している半導体集積回路、および表示部2003に適用し、消費電力が低減されたテレビを実現することができる。なお、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用のテレビが含まれる。

図10(B)はデジタルカメラであり、本体2101、表示部2102、受像部2103、操作キー2104、外部接続ポート2105、シャッター2106等を含む。本発明は、デジタルカメラに内蔵されている半導体集積回路(メモリやCPUなど)、および表示部2102に適用し、消費電力が低減されたデジタルカメラとすることができる。

図10(C)はパーソナルコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を含む。本発明は、パーソナルコンピュータに内蔵されている半導体集積回路(メモリやCPUなど)、および表示部2203に適用し、表示部に配置されるTFTと、CPUを構成するCMOS回路とに用いられる配線や接触抵抗を低減することが可能となり、消費電力が低減されたパーソナルコンピュータを実現することができる。

図10(D)は電子書籍であり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。本発明は、電子書籍に内蔵されている半導体集積回路(メモリやCPUなど)、および表示部2302に適用し、消費電力が低減された電子書籍を実現することができる。

図10(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体2401、筐体2402、表示部A2403、表示部B2404、記録媒体(DVD等)読込部2405、操作キー2406、スピーカー部2407等を含む。表示部A2403は主として画像情報を表示し、表示部B2404は主として文字情報を表示する。本発明は画像再生装置に内蔵されている半導体集積回路(メモリやCPUなど)、および表示部A、B2403、2404に適用し、消費電力が低減された画像再生装置を実現することができる。

図10(F)は携帯型のゲーム機器であり、本体2501、表示部2505、操作スイッチ2504等を含む。ゲーム機器に内蔵されている半導体集積回路(メモリやCPUなど)、および表示部2503、2505に適用し、消費電力が低減された携帯型のゲーム機器を実現することができる。

図10(G)はビデオカメラであり、本体2601、表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609、接眼部2610等を含む。本発明は、ビデオカメラに内蔵されている半導体集積回路(メモリやCPUなど)、および表示部2602に適用し、消費電力が低減されたビデオカメラを実現することができる。

図10(H)は携帯電話であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。本発明は、携帯電話に内蔵されている半導体集積回路(メモリやCPUや高周波回路など)、および表示部2703に適用し、消費電力が低減された携帯電話を実現できる。

また、図11は、記録媒体を備えた携帯型の音楽再生装置であり、本体2901、表示部2903、記録媒体(カード型メモリ、小型HDD等)読み込み部、操作キー2902、2906、接続コード2904に接続されたヘッドフォンのスピーカー部2905等を含む。本発明は、表示部2903に適用し、消費電力が低減された音楽再生装置を実現できる。

また、本実施例は実施の形態1、実施の形態2、実施の形態3、実施例1、実施例2、実施例3、実施例4、または実施例5と自由に組み合わせることができる。

実施の形態1を示す断面図。

成膜後の反射率を示すグラフ。

ベーク後の反射率を示すグラフ。

実施の形態2を示す断面図。

実施の形態3を示す断面図。

EL表示パネルの断面図。

EL表示パネルの断面図。

EL表示パネルを示す上面図。

液晶パネルを示す断面図。

電子機器の一例を示す図。

電子機器の一例を示す図。

符号の説明

10 基板

11 下地絶縁膜

12 ゲート絶縁膜

13 第1の層間絶縁膜

14a 導電層

14b 導電層

16 平坦化絶縁膜

17 p型の高濃度不純物領域

18 p型の高濃度不純物領域

19 チャネル形成領域

22a 第1導電層

22b 第2導電層

22c 第3導電層

23R 第1の電極

23G 第1の電極

24R 有機化合物を含む層

24G 有機化合物を含む層

25 第2の電極

27 一対の基板およびシール材で囲まれた領域

29 絶縁物

33 封止基板

422a 第1導電層

422b 第2導電層

422c 第3導電層

423R 第1の電極

423G 第1の電極

520 平坦化絶縁膜

523R 第1の電極

523G 第1の電極

524R 有機化合物を含む層

524G 有機化合物を含む層

525 第2の電極

527 一対の基板およびシール材で囲まれた領域

529 絶縁物

533 封止基板

610 基板

616 平坦化絶縁膜

623 第1の電極

624 有機化合物を含む層

625 第2の電極

626 透明保護層

627 充填材

628 シール材

629 絶縁物

632 FPC

633 封止基板

636 nチャネル型TFT

637 pチャネル型TFT

701 第1の基板

702 下地絶縁膜

703 TFT

705 ゲート絶縁膜

706 層間絶縁膜

707 平坦化絶縁膜

708 画素電極

710 配向膜

711 液晶材料

712 配向膜

714 柱状スペーサ

716 第2の基板

720 チャネル形成領域

721 ソース領域またはドレイン領域

722 ソース領域またはドレイン領域

723a ゲート電極

723b ゲート電極

724a ソース配線

724b ソース配線

724c ソース配線

725 低濃度不純物領域

726 低濃度不純物領域

731 光学フィルム

732 光学フィルム

734 導光板

735 LED

1001 第1の基板

1002 下地絶縁膜

1003R TFT

1003G TFT

1003B TFT

1005 ゲート絶縁膜

1006 層間絶縁膜

1007 平坦化絶縁膜

1008 第1の電極

1009 隔壁

1010 第2の電極

1011 保護膜

1012 保護膜

1014 間隔

1015R 有機化合物を含む層

1015G 有機化合物を含む層

1015B 有機化合物を含む層

1016 第2の基板

1020 チャネル形成領域

1021 ソース領域またはドレイン領域

1022 ソース領域またはドレイン領域

1023a ゲート電極の下層

1023b ゲート電極の上層

1024a ドレイン配線、またはソース配線

1024b ドレイン配線、またはソース配線

1024c ドレイン配線、またはソース配線

1201 ソース側駆動回路

1202 画素部

1203 ゲート側駆動回路

1204 封止基板

1205 シール材

1207 接続領域

1208 端子部

1209 FPC

1210 基板

1301 駆動IC

1302 画素部

1304 封止基板

1305 シール材

1307 接続領域

1308 端子部

1309 FPC

1310 基板