JP4966965B2 - 電源喪失によるデータ破損に強いフラッシュメモリ管理方法 - Google Patents

電源喪失によるデータ破損に強いフラッシュメモリ管理方法 Download PDFInfo

- Publication number

- JP4966965B2 JP4966965B2 JP2008510725A JP2008510725A JP4966965B2 JP 4966965 B2 JP4966965 B2 JP 4966965B2 JP 2008510725 A JP2008510725 A JP 2008510725A JP 2008510725 A JP2008510725 A JP 2008510725A JP 4966965 B2 JP4966965 B2 JP 4966965B2

- Authority

- JP

- Japan

- Prior art keywords

- page

- pages

- written

- data

- writing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/16—Protection against loss of memory contents

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/023—Free address space management

- G06F12/0238—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory

- G06F12/0246—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory in block erasable memory, e.g. flash memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1072—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices in multilevel memories

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/14—Error detection or correction of the data by redundancy in operation

- G06F11/1402—Saving, restoring, recovering or retrying

- G06F11/1415—Saving, restoring, recovering or retrying at system level

- G06F11/1435—Saving, restoring, recovering or retrying at system level using file system or storage system metadata

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/22—Safety or protection circuits preventing unauthorised or accidental access to memory cells

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Quality & Reliability (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Library & Information Science (AREA)

- Computer Security & Cryptography (AREA)

- Computer Hardware Design (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

Description

1.2ページのスーパーページ34のうちのページ32の1つが、成功裡に書き込まれ、もう一方のページが、書き込まれていない。

2.2ページのスーパーページ34のうちのもう一方のページ32への書き込みが、電源喪失によって中断される。

VT1 ビット1の値 ビット2の値

−3.0V 1 1

−0.5V 1 0

+2.0V 0 1

+4.5V 0 0

a.ページ19およびページ20が、ページ21の危険ゾーン内にあること、

b.ページ20が、ページ22の危険ゾーン内にあること、

c.ページ23が、その危険ゾーン内に書き込み済みページを含まないこと、

d.ページ24が、その危険ゾーン内に書き込み済みページを含まないこと、

e.ページ25が、その危険ゾーン内に書き込み済みページを含まないこと、

が分かる。

Claims (29)

- マルチレベルセルに複数のページを格納し、シングルレベルセルにログを格納するメモリの管理方法であって、

(a)各ページのそれぞれの危険ゾーンを識別するステップと、

(b)新しいデータを書き込むために少なくとも1つの未書き込みページを選択するステップと、

(c)少なくとも1つの書き込み済みページを自身の危険ゾーンが含む各前記未書き込みページのために、各前記書き込み済みページを、シングルレベルセルの前記ログにコピーするステップと、

を含む方法。 - (d)前記新しいデータを前記少なくとも1つの未書き込みページに書き込むステップを含む、請求項1に記載の方法。

- 前記新しいデータが2ページ以上にわたる場合に、前記書き込むステップが同時に行われる、請求項2に記載の方法。

- 前記コピーするステップおよび前記書き込むステップが、同時に行われる、請求項2または3に記載の方法。

- (e)少なくとも1つの書き込み済みページに格納されたデータが破損しているかどうかをチェックするステップと、

(f)前記データが破損している場合には、前記データを前記ログからの対応するデータと取り替えるステップと、

をさらに含む、請求項2から4のいずれかに記載の方法。 - 前記チェックするステップが誤り検出符号を用いて行われる、請求項5に記載の方法。

- 前記チェックするステップおよび前記取り替えるステップが、メモリを含むシステムが電源投入されるときに行われる、請求項5に記載の方法。

- 未書き込みページに書き込まれる前記新しいデータが、前記未書き込みページの前記危険ゾーンにおける全ての書き込み済みページが前記ログとしてコピーされて初めて、前記未書き込みページに書き込まれる請求項2に記載の方法であって、前記方法が、前記ログとしてコピーされる各書き込み済みページのために、

(e)対応するフラグを設定するステップと、

(f)前記各書き込み済みページを自身の危険ゾーンが含む前記少なくとも1つの未書き込みページに書き込まれることになる前記新しいデータが、前記各書き込み済みページを自身の危険ゾーンが含む全ての前記少なくとも1つの未書き込みページに書き込まれた後で、前記対応するフラグをクリアするステップと、

をさらに含む、請求項2に記載の方法。 - (g)設定される各前記フラグについて、前記各フラグに対応する前記書き込み済みページに格納されたデータを、前記ログからの対応するデータと取り替えるステップをさらに含む、請求項8に記載の方法。

- 前記取り替えるステップが、前記メモリを含むシステムが電源投入されるときに行われる、請求項9に記載の方法。

- 前記新しいデータが2ページ以上にわたる場合には、前記選択された未書き込みページが順次的に書き込まれる、請求項2に記載の方法。

- 前記新しいデータが2ページ以上にわたる場合には、前記選択された未書き込みページがランダムな順序で書き込まれる、請求項2に記載の方法。

- 前記コピーするステップおよび前記書き込むステップが、それぞれ異なる書き込みモードを用いて行われる、請求項2に記載の方法。

- 前記コピーするステップの前記書き込みモードが、前記書き込むステップの前記書き込みモードより、メモリのセルに少数のビットを書き込む、請求項13に記載の方法。

- 全ての前記危険ゾーンが等しいページ数を含む、請求項1に記載の方法。

- 各前記危険ゾーンが1ページを含む、請求項15に記載の方法。

- 少なくとも2つの前記危険ゾーンが、異なるページ数を含む、請求項1に記載の方法。

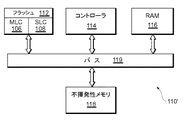

- (a)複数のページを格納するマルチレベルセルと、ログを格納するシングルレベルセルと、を含むデータ記憶媒体と、

(b)(i)前記複数のページにおける各ページのそれぞれの危険ゾーンを識別するステップと、

(ii)前記新しいデータを書き込むために、前記複数のページの少なくとも1つの未書き込みページを選択するステップと、

(iii)前記複数のページの少なくとも1つの書き込みページを自身の危険ゾーンが含む各前記未書き込み済みページのために、各前記書き込み済みページを、前記シングルレベルセルにログとしてコピーするステップと、を含むステップによって、前記複数のページに新しいデータを書き込むためのコントローラと、

を含むデータ記憶システム。 - 前記データ記憶媒体が不揮発性である、請求項18に記載のデータ記憶システム。

- 前記データ記憶媒体がフラッシュメモリである、請求項19に記載のデータ記憶システム。

- 前記フラッシュメモリが複数のマルチレベルセルを含む、請求項20に記載のデータ記憶システム。

- 前記フラッシュメモリが、複数のブロックの各ブロックのそれぞれが前記複数のページの一部の複数ページを含むように、前記複数のブロックを含み、前記コントローラが、前記新しいデータを、各前記ブロックの前記ページに順次的にのみ書き込む、請求項20に記載のデータ記憶システム。

- 前記フラッシュメモリが、複数のブロックの各ブロックのそれぞれが前記複数のページの一部の複数ページを含むように、前記複数のブロックを含み、前記コントローラが、前記新しいデータを、各前記ブロックの前記ページにランダムな順序で書き込む、請求項20に記載のデータ記憶システム。

- 前記ログが、前記データ記憶媒体の一部に格納される、請求項18に記載のデータ記憶システム。

- 前記コントローラが、

(iv)前記複数のページの前記少なくとも1つの未書き込みページに前記新しいデータを書き込むステップ、

をさらに含むステップによって、前記複数のページに前記新しいデータを書き込む、請求項18に記載のデータ記憶システム。 - 前記ログとして前記コピーするステップおよび前記少なくとも1つの未書き込みページへの前記書き込むステップが、それぞれ異なる書き込みモードを用いて行われる、請求項25に記載のデータ記憶システム。

- 前記ログとして前記コピーするステップの前記書き込みモードが、前記少なくとも1つの未書き込みページへの前記書き込むステップの前記書き込みモードより、前記データ記憶媒体のセルに少数のビットを書き込む、請求項26に記載のデータ記憶システム。

- コンピュータ可読コードを自身に埋め込んだコンピュータ可読記憶媒体であって、前記コンピュータ可読コードが、データ記憶媒体の複数のページの少なくとも1つに新しいデータを書き込むためのものであり、

前記データ記憶媒体が、複数のページを格納するマルチレベルセルと、ログを格納するシングルレベルセルと、を含み

前記コンピュータ可読コードが、

(a)各ページのそれぞれの危険ゾーンを識別するためのプログラムコードと、

(b)新しいデータを書き込むために少なくとも1つの未書き込みページを選択するためのプログラムコードと、

(c)少なくとも1つの書き込み済みページを自身の危険ゾーンが含む各前記未書き込みページのために、各前記書き込み済みページを、前記シングルレベルセルにログとしてコピーするためのプログラムコードと、を含むコンピュータ可読記憶媒体。 - 複数のページを含むメモリの管理方法であって、

(a)各ページのそれぞれの危険ゾーンを識別するステップと、

(b)新しいデータを書き込むために少なくとも1つの未書き込みページを選択するステップと、

(c)少なくとも1つの書き込み済みページを自身の危険ゾーンが含む各前記未書き込みページのために、各前記書き込み済みページをログとしてコピーするステップと、

(d)前記新しいデータを前記少なくとも1つの未書き込みページに書き込むステップと、

(e)少なくとも1つの書き込み済みページに格納されたデータが破損しているかどうかをチェックするステップと、

(f)前記データが破損している場合には、前記データを前記ログからの対応するデータと取り替えるステップと、を含み、

前記チェックステップが誤り検出符号を用いて行われる、方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US67982505P | 2005-05-12 | 2005-05-12 | |

| US11/370,942 US7275140B2 (en) | 2005-05-12 | 2006-03-09 | Flash memory management method that is resistant to data corruption by power loss |

| PCT/IL2006/000558 WO2006120686A2 (en) | 2005-05-12 | 2006-05-11 | Flash memory management method that is resistant to data corruption by power loss |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008544345A JP2008544345A (ja) | 2008-12-04 |

| JP4966965B2 true JP4966965B2 (ja) | 2012-07-04 |

Family

ID=37396974

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008510725A Expired - Fee Related JP4966965B2 (ja) | 2005-05-12 | 2006-05-11 | 電源喪失によるデータ破損に強いフラッシュメモリ管理方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7275140B2 (ja) |

| EP (1) | EP1883884B1 (ja) |

| JP (1) | JP4966965B2 (ja) |

| KR (1) | KR101215864B1 (ja) |

| CN (1) | CN101198939B (ja) |

| AT (1) | ATE537504T1 (ja) |

| WO (1) | WO2006120686A2 (ja) |

Families Citing this family (66)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20080071973A1 (en) * | 2000-01-06 | 2008-03-20 | Chow David Q | Electronic data flash card with various flash memory cells |

| WO2007023674A1 (ja) * | 2005-08-22 | 2007-03-01 | Matsushita Electric Industrial Co., Ltd. | メモリコントローラ、不揮発性記憶装置、不揮発性記憶システム、及びデータ書き込み方法 |

| KR100771521B1 (ko) * | 2006-10-30 | 2007-10-30 | 삼성전자주식회사 | 멀티 레벨 셀을 포함하는 플래시 메모리 장치 및 그것의데이터 쓰기 방법 |

| KR100791006B1 (ko) * | 2006-12-06 | 2008-01-03 | 삼성전자주식회사 | 싱글레벨 셀 및 멀티레벨 셀을 구비하는 반도체 메모리장치 및 그 구동방법 |

| JP4563992B2 (ja) * | 2006-12-26 | 2010-10-20 | 株式会社京都ソフトウェアリサーチ | 多値フラッシュメモリおよび多値フラッシュメモリへのデータ書き込み方法 |

| KR100877610B1 (ko) * | 2007-01-23 | 2009-01-09 | 삼성전자주식회사 | 페이지 데이터 저장 방법과 저장 장치 |

| US20080189473A1 (en) * | 2007-02-07 | 2008-08-07 | Micron Technology, Inc | Mlc selected multi-program for system management |

| KR100889781B1 (ko) | 2007-04-30 | 2009-03-20 | 삼성전자주식회사 | 멀티-비트 데이터를 저장하는 메모리 시스템, 그것의프로그램 방법, 그것을 포함한 컴퓨팅 시스템 |

| KR100873825B1 (ko) * | 2007-05-02 | 2008-12-15 | 삼성전자주식회사 | 비휘발성 메모리의 멀티 비트 프로그래밍 장치 및 방법 |

| KR101300821B1 (ko) * | 2007-07-04 | 2013-08-26 | 삼성전자주식회사 | 비휘발성 메모리의 데이터 손실을 방지하기 위한 장치 및방법 |

| US8151034B2 (en) * | 2007-09-12 | 2012-04-03 | Sandisk Technologies Inc. | Write abort and erase abort handling |

| US8307180B2 (en) | 2008-02-28 | 2012-11-06 | Nokia Corporation | Extended utilization area for a memory device |

| JP4703673B2 (ja) * | 2008-03-12 | 2011-06-15 | 株式会社東芝 | メモリシステム |

| US8276043B2 (en) | 2008-03-01 | 2012-09-25 | Kabushiki Kaisha Toshiba | Memory system |

| JP2009211215A (ja) * | 2008-03-01 | 2009-09-17 | Toshiba Corp | メモリシステム |

| US20090287893A1 (en) * | 2008-05-16 | 2009-11-19 | Skymedi Corporation | Method for managing memory |

| US20120311243A1 (en) * | 2008-05-30 | 2012-12-06 | Ite Tech. Inc. | Method for increasing reliability of data accessing for a multi-level cell type non-volatile memory |

| TW200949840A (en) * | 2008-05-30 | 2009-12-01 | Ite Tech Inc | Method for increasing reliability of data accessing for a multi-level cell type non-volatile memory |

| US20090319721A1 (en) * | 2008-06-19 | 2009-12-24 | Silicon Motion, Inc. | Flash memory apparatus and method for operating the same |

| US8843691B2 (en) * | 2008-06-25 | 2014-09-23 | Stec, Inc. | Prioritized erasure of data blocks in a flash storage device |

| US8074012B2 (en) * | 2008-07-02 | 2011-12-06 | Silicon Motion, Inc. | Flash memory apparatus and method for securing a flash memory from data damage |

| TWI386803B (zh) * | 2008-07-02 | 2013-02-21 | Silicon Motion Inc | 快閃記憶卡及快閃記憶體預防資料毀損的方法 |

| US8762661B2 (en) * | 2008-09-18 | 2014-06-24 | Seagate Technology Llc | System and method of managing metadata |

| US7962801B2 (en) * | 2008-10-15 | 2011-06-14 | Silicon Motion, Inc. | Link table recovery method |

| CN101727397B (zh) * | 2008-10-20 | 2012-06-27 | 群联电子股份有限公司 | 区块管理与更换方法、闪存储存系统及其控制器 |

| US8103631B2 (en) * | 2008-11-19 | 2012-01-24 | Sandisk Il Ltd | Merging files on storage and retrieve |

| JP4551958B2 (ja) * | 2008-12-22 | 2010-09-29 | 株式会社東芝 | 半導体記憶装置および半導体記憶装置の制御方法 |

| US20100235605A1 (en) * | 2009-02-13 | 2010-09-16 | Nir Perry | Enhancement of storage life expectancy by bad block management |

| US9098396B2 (en) * | 2009-02-13 | 2015-08-04 | Sandisk Il Ltd. | Enhancement of efficiency in power failure handling in flash memory |

| US8874824B2 (en) | 2009-06-04 | 2014-10-28 | Memory Technologies, LLC | Apparatus and method to share host system RAM with mass storage memory RAM |

| JP2011048725A (ja) * | 2009-08-28 | 2011-03-10 | Panasonic Corp | 不揮発性記憶装置および不揮発性メモリコントローラ |

| US8966176B2 (en) | 2010-05-27 | 2015-02-24 | Sandisk Il Ltd. | Memory management storage to a host device |

| US8738844B2 (en) | 2011-04-14 | 2014-05-27 | Macronix International Co., Ltd. | Program method, data recovery method, and flash memory using the same |

| US20120297248A1 (en) * | 2011-05-17 | 2012-11-22 | Alan David Bennett | Block write handling after corruption |

| KR101856506B1 (ko) * | 2011-09-22 | 2018-05-11 | 삼성전자주식회사 | 데이터 저장 장치 및 그것의 데이터 쓰기 방법 |

| US9417998B2 (en) | 2012-01-26 | 2016-08-16 | Memory Technologies Llc | Apparatus and method to provide cache move with non-volatile mass memory system |

| US20130205066A1 (en) * | 2012-02-03 | 2013-08-08 | Sandisk Technologies Inc. | Enhanced write abort management in flash memory |

| US9311226B2 (en) | 2012-04-20 | 2016-04-12 | Memory Technologies Llc | Managing operational state data of a memory module using host memory in association with state change |

| US8923045B2 (en) | 2012-05-31 | 2014-12-30 | Seagate Technology Llc | Multi-level cell (MLC) update with protected mode capability |

| US20140013031A1 (en) * | 2012-07-09 | 2014-01-09 | Yoko Masuo | Data storage apparatus, memory control method, and electronic apparatus having a data storage apparatus |

| US9053011B2 (en) | 2012-09-28 | 2015-06-09 | Sandisk Technologies Inc. | Selective protection of lower page data during upper page write |

| US9478271B2 (en) * | 2013-03-14 | 2016-10-25 | Seagate Technology Llc | Nonvolatile memory data recovery after power failure |

| JP5695112B2 (ja) * | 2013-03-18 | 2015-04-01 | 富士通テン株式会社 | データ記憶装置、データの記憶方法および車載用制御装置 |

| US9305655B2 (en) | 2013-09-27 | 2016-04-05 | Virtium Technology, Inc. | Solving MLC NAND paired page program using reduced spatial redundancy |

| US8819337B1 (en) * | 2014-04-16 | 2014-08-26 | Sandisk Technologies Inc. | Storage module and method for determining whether to back-up a previously-written lower page of data before writing an upper page of data |

| US9715345B2 (en) | 2014-04-25 | 2017-07-25 | Micron Technology, Inc. | Apparatuses and methods for memory management |

| CN104503707B (zh) * | 2014-12-24 | 2018-03-06 | 华为技术有限公司 | 读取数据的方法以及装置 |

| KR102222444B1 (ko) | 2015-03-05 | 2021-03-04 | 삼성전자주식회사 | 전력 상태 정보를 사용하는 저장 장치 및 그것의 동작 방법 |

| US9558839B2 (en) * | 2015-03-09 | 2017-01-31 | Toshiba Corporation | Power fail saving modes in solid state drive with MLC memory |

| KR20160133283A (ko) * | 2015-05-12 | 2016-11-22 | 삼성전자주식회사 | 비휘발성 메모리 저장장치를 운영하는 방법 및 이를 구현한 전자장치 |

| US10055236B2 (en) | 2015-07-02 | 2018-08-21 | Sandisk Technologies Llc | Runtime data storage and/or retrieval |

| US10303571B2 (en) * | 2015-11-04 | 2019-05-28 | Intel Corporation | Data recovery in memory devices |

| CN106776362B (zh) * | 2015-11-24 | 2019-12-03 | 中芯国际集成电路制造(上海)有限公司 | 存储器的控制方法及装置 |

| KR102641107B1 (ko) | 2016-07-29 | 2024-02-27 | 삼성전자주식회사 | 스토리지 장치, 이를 포함하는 시스템 및 그 동작 방법 |

| CN106227623B (zh) * | 2016-08-03 | 2019-03-26 | 深圳市智行畅联科技有限公司 | 一种基于智能终端的文件格式及数据掉电修复方法及系统 |

| US10048887B2 (en) | 2016-10-27 | 2018-08-14 | Micron Technology, Inc. | Apparatuses and methods for single level cell caching |

| US10977186B2 (en) * | 2017-11-21 | 2021-04-13 | Micron Technology, Inc. | Last written page searching |

| US11249845B2 (en) | 2017-12-06 | 2022-02-15 | Rambus Inc. | Error-correction-detection coding for hybrid memory module |

| US11163679B2 (en) * | 2018-04-04 | 2021-11-02 | SK Hynix Inc. | Garbage collection strategy for memory system and method of executing such garbage collection |

| TWI669610B (zh) | 2018-06-13 | 2019-08-21 | 慧榮科技股份有限公司 | 資料儲存裝置以及非揮發式記憶體控制方法 |

| US11416144B2 (en) | 2019-12-12 | 2022-08-16 | Pure Storage, Inc. | Dynamic use of segment or zone power loss protection in a flash device |

| US11704192B2 (en) | 2019-12-12 | 2023-07-18 | Pure Storage, Inc. | Budgeting open blocks based on power loss protection |

| US11106372B2 (en) * | 2019-12-27 | 2021-08-31 | Micron Technology, Inc. | Asynchronous power loss handling approach for a memory sub-system |

| KR20220153863A (ko) | 2021-05-12 | 2022-11-21 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 동작 방법 |

| US11960757B2 (en) | 2021-10-04 | 2024-04-16 | Samsung Electronics Co., Ltd. | Flash translation layer with rewind |

| US11893243B2 (en) * | 2021-10-06 | 2024-02-06 | Western Digital Technologies, Inc. | Storage system and method for program reordering to mitigate program disturbs |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5043940A (en) | 1988-06-08 | 1991-08-27 | Eliyahou Harari | Flash EEPROM memory systems having multistate storage cells |

| US5095344A (en) | 1988-06-08 | 1992-03-10 | Eliyahou Harari | Highly compact eprom and flash eeprom devices |

| US5404485A (en) | 1993-03-08 | 1995-04-04 | M-Systems Flash Disk Pioneers Ltd. | Flash file system |

| EP0913834A1 (en) * | 1996-07-10 | 1999-05-06 | Hitachi, Ltd. | Nonvolatile semiconductor storage device |

| US5937425A (en) | 1997-10-16 | 1999-08-10 | M-Systems Flash Disk Pioneers Ltd. | Flash file system optimized for page-mode flash technologies |

| KR100389867B1 (ko) * | 2001-06-04 | 2003-07-04 | 삼성전자주식회사 | 플래시 메모리 관리방법 |

| US6522580B2 (en) | 2001-06-27 | 2003-02-18 | Sandisk Corporation | Operating techniques for reducing effects of coupling between storage elements of a non-volatile memory operated in multiple data states |

| CN1255733C (zh) * | 2001-07-25 | 2006-05-10 | 索尼株式会社 | 非易失性存储器和非易失性存储器的数据改写方法 |

| US6773083B2 (en) * | 2001-08-29 | 2004-08-10 | Lexmark International, Inc. | Method and apparatus for non-volatile memory usage in an ink jet printer |

| US6456528B1 (en) | 2001-09-17 | 2002-09-24 | Sandisk Corporation | Selective operation of a multi-state non-volatile memory system in a binary mode |

| US6678785B2 (en) | 2001-09-28 | 2004-01-13 | M-Systems Flash Disk Pioneers Ltd. | Flash management system using only sequential write |

| US6977847B2 (en) * | 2001-11-23 | 2005-12-20 | M-Systems Flash Disk Pioneers Ltd. | Detecting partially erased units in flash devices |

| US6542407B1 (en) * | 2002-01-18 | 2003-04-01 | Sandisk Corporation | Techniques of recovering data from memory cells affected by field coupling with adjacent memory cells |

| US7702659B2 (en) | 2003-03-27 | 2010-04-20 | Sandisk Il Ltd. | Robust, self-maintaining file system |

| US6988175B2 (en) * | 2003-06-30 | 2006-01-17 | M-Systems Flash Disk Pioneers Ltd. | Flash memory management method that is resistant to data corruption by power loss |

| JP4874566B2 (ja) * | 2005-04-11 | 2012-02-15 | 株式会社東芝 | 半導体記憶装置 |

| WO2007023674A1 (ja) * | 2005-08-22 | 2007-03-01 | Matsushita Electric Industrial Co., Ltd. | メモリコントローラ、不揮発性記憶装置、不揮発性記憶システム、及びデータ書き込み方法 |

| JP2007094921A (ja) * | 2005-09-30 | 2007-04-12 | Toshiba Corp | メモリカードとその制御方法 |

| JP2007109352A (ja) * | 2005-10-17 | 2007-04-26 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置およびその駆動方法。 |

-

2006

- 2006-03-09 US US11/370,942 patent/US7275140B2/en active Active

- 2006-05-11 EP EP06745093A patent/EP1883884B1/en not_active Not-in-force

- 2006-05-11 AT AT06745093T patent/ATE537504T1/de active

- 2006-05-11 WO PCT/IL2006/000558 patent/WO2006120686A2/en active Application Filing

- 2006-05-11 KR KR1020077028919A patent/KR101215864B1/ko not_active IP Right Cessation

- 2006-05-11 CN CN2006800211307A patent/CN101198939B/zh active Active

- 2006-05-11 JP JP2008510725A patent/JP4966965B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| WO2006120686A3 (en) | 2007-11-01 |

| US20060259718A1 (en) | 2006-11-16 |

| EP1883884A2 (en) | 2008-02-06 |

| EP1883884B1 (en) | 2011-12-14 |

| ATE537504T1 (de) | 2011-12-15 |

| JP2008544345A (ja) | 2008-12-04 |

| EP1883884A4 (en) | 2010-10-27 |

| WO2006120686A2 (en) | 2006-11-16 |

| CN101198939B (zh) | 2011-11-23 |

| KR101215864B1 (ko) | 2013-01-02 |

| KR20080008419A (ko) | 2008-01-23 |

| US7275140B2 (en) | 2007-09-25 |

| CN101198939A (zh) | 2008-06-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4966965B2 (ja) | 電源喪失によるデータ破損に強いフラッシュメモリ管理方法 | |

| US7603525B2 (en) | Flash memory management method that is resistant to data corruption by power loss | |

| KR101392701B1 (ko) | 메모리 장치를 위한 삽입된 매핑 정보 | |

| US9665301B2 (en) | Methods and devices for storing user data along with addresses corresponding to physical pages storing valid data | |

| JP4256175B2 (ja) | 不揮発性半導体メモリ | |

| US8909986B2 (en) | Data storing method for solid state drive to preserve data integrity after power failure | |

| US8046528B2 (en) | Data writing method for flash memory, and flash memory controller and storage device thereof | |

| US7389397B2 (en) | Method of storing control information in a large-page flash memory device | |

| KR100672996B1 (ko) | 메타 데이터가 저장되는 에프램을 포함하는 메모리 장치 | |

| JP2003187585A (ja) | フラッシュデバイスにおける部分的に消去されたユニットの検出 | |

| US9558128B2 (en) | Selective management of security data | |

| US20110138113A1 (en) | Raid storage systems having arrays of solid-state drives and methods of operation | |

| KR20200076886A (ko) | 저장 장치 및 그 동작 방법 | |

| US8954692B2 (en) | File protecting method and system, and memory controller and memory storage apparatus thereof | |

| Lin et al. | Achieving fast sanitization with zero live data copy for MLC flash memory | |

| KR100932801B1 (ko) | 메모리 관리 방법, 메모리 장치 및 컴퓨터 판독 가능 저장매체 | |

| JP4551938B2 (ja) | メモリシステム | |

| JP5264459B2 (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110218 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110518 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110525 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110616 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20111014 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120210 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20120216 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120309 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120402 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4966965 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150406 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |