JP4965617B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4965617B2 JP4965617B2 JP2009210588A JP2009210588A JP4965617B2 JP 4965617 B2 JP4965617 B2 JP 4965617B2 JP 2009210588 A JP2009210588 A JP 2009210588A JP 2009210588 A JP2009210588 A JP 2009210588A JP 4965617 B2 JP4965617 B2 JP 4965617B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- insulating film

- semiconductor

- layer

- adhesion improving

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H10W72/0198—

-

- H10W70/09—

-

- H10W72/241—

-

- H10W72/874—

-

- H10W90/734—

Landscapes

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

Description

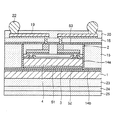

図1はこの発明の第1実施形態としての半導体装置の断面図を示す。この半導体装置は平面方形状のベース板(ベース部材)1を備えている。ベース板1は、例えば、通常、プリント基板用として用いられている材料であればよく、一例を挙げれば、ガラス布、ガラス繊維、アラミド繊維などからなる基材にエポキシ系樹脂、ポリイミド系樹脂、BT(ビスマレイミド・トリアジン)樹脂などからなる熱硬化性樹脂を含浸させたもの、あるいは、エポキシ系樹脂などの熱硬化性樹脂のみからなっている。

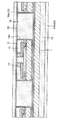

図20はこの発明の第2実施形態としての半導体装置の断面図を示す。この半導体装置において、図1に示す場合と大きく異なる点は、半導体構成体2のシリコン基板4の下面に設けられたシランカップリング剤からなる密着力向上膜(第1の密着力向上膜)51の下面に接着された接着層3を、ベース板1の上面に設けられたシランカップリング剤からなる密着力向上膜52の上面に接着させた点である。

図24はこの発明の第3実施形態としての半導体装置の断面図を示す。この半導体装置において、図20に示す場合と異なる点は、図20において半導体構成体2の上面上のみに設けられた密着力向上膜14cを、上層絶縁膜16の下面全面に対応する密着力向上膜53として設け、半導体構成体2および絶縁層15の上面と上層絶縁膜16との間の密着力を一層大きくした点である。

図29はこの発明の第4実施形態としての半導体装置の断面図を示す。この半導体装置において、図1に示す場合と大きく異なる点は、上層絶縁膜、上層配線および下層絶縁膜を2層とした点である。すなわち、第1の上層配線19Aを含む第1の上層絶縁膜16Aの上面には第1の上層絶縁膜16Aと同一の材料からなる第2の上層絶縁膜16Bが設けられている。第2の上層絶縁膜16Bの上面には第2の上層下地金属層18Bを含む第2の上層配線19Bが設けられている。

上記実施形態では、互いに隣接する半導体構成体2間において切断したが、これに限らず、2個またはそれ以上の半導体構成体2を1組として切断し、マルチチップモジュール型の半導体装置を得るようにしてもよい。この場合、複数で1組の半導体構成体2は同種、異種のいずれであってもよい。

2 半導体構成体

3 接着層

4 シリコン基板

5 接続パッド

11 配線

12 柱状電極

13 封止膜

14a、14b、14c 密着力向上膜

15 絶縁層

16 上層絶縁膜

19 上層配線

20 最上層絶縁膜

22 半田ボール

Claims (6)

- 第2の密着力向上膜が上面に設けられたベース部材上に、各々が半導体基板および該半導体基板上に設けられた複数の外部接続用電極としての柱状電極、前記柱状電極の周囲を覆う封止膜、前記半導体基板下に設けられた第1の密着力向上膜、前記第1の密着力向上膜下に設けられた接着層、を有する複数の半導体構成体を相互に離間させて配置する工程と、

前記各半導体構成体の周側面、前記半導体構成体の周囲における前記ベース部材上の前記第2の密着力向上膜の上面および前記半導体構成体の上面に、第3の密着力向上膜を形成する工程と、

前記ベース部材上の前記第2の密着力向上膜の上面に、前記各半導体構成体の周側面、前記ベース部材上の前記第2の密着力向上膜の上面に設けられた前記第3の密着力向上膜を介してシート状部材からなる絶縁層を配置する工程と、

前記第3の密着力向上膜が形成された前記各半導体構成体の上面および前記絶縁層上に少なくとも1層の上層絶縁膜を形成する工程と、

前記絶縁層および前記上層絶縁膜を加熱加圧する工程と、

前記半導体構成体間における前記ベース板、前記上層絶縁膜および前記絶縁層を少なくとも切断して前記半導体構成体が少なくとも1つ含まれる半導体装置を複数個得る工程と、

を有することを特徴とする半導体装置の製造方法。 - 請求項1に記載の発明において、前記上層絶縁膜上に少なくとも1層の上層配線を形成することを特徴とする半導体装置の製造方法。

- 請求項1または2のいずれかに記載の発明において、前記密着力向上膜はシランカップリング剤からなることを特徴とする半導体装置の製造方法。

- 請求項3に記載の発明において、前記密着力向上膜は、分子中に一般式(CnH2n+1O)m−Si−(ただし、n、m=1、2、3)を有する材料からなることを特徴とする半導体装置の製造方法。

- 請求項1〜4のいずれかに記載の発明において、前記最上層の上層配線の接続パッド部を除く部分を覆う最上層絶縁膜を形成する工程を有することを特徴とする半導体装置の製造方法。

- 請求項5に記載の発明において、前記最上層の上層配線の接続パッド部上に半田ボールを形成する工程を有することを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009210588A JP4965617B2 (ja) | 2009-09-11 | 2009-09-11 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009210588A JP4965617B2 (ja) | 2009-09-11 | 2009-09-11 | 半導体装置の製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004164363A Division JP4398305B2 (ja) | 2004-06-02 | 2004-06-02 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010016398A JP2010016398A (ja) | 2010-01-21 |

| JP4965617B2 true JP4965617B2 (ja) | 2012-07-04 |

Family

ID=41702131

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009210588A Expired - Fee Related JP4965617B2 (ja) | 2009-09-11 | 2009-09-11 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4965617B2 (ja) |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08264686A (ja) * | 1995-03-22 | 1996-10-11 | Hitachi Ltd | 樹脂封止型半導体装置及びその製造方法 |

| JP2001244383A (ja) * | 2000-02-29 | 2001-09-07 | Sumitomo Bakelite Co Ltd | 半導体装置 |

| JP2003298005A (ja) * | 2002-02-04 | 2003-10-17 | Casio Comput Co Ltd | 半導体装置およびその製造方法 |

| JP2003249691A (ja) * | 2002-02-22 | 2003-09-05 | Matsushita Electric Works Ltd | 発光装置及びその製造方法 |

| JP4054216B2 (ja) * | 2002-05-13 | 2008-02-27 | 日本特殊陶業株式会社 | 配線基板の製造方法 |

| JP3888267B2 (ja) * | 2002-08-30 | 2007-02-28 | カシオ計算機株式会社 | 半導体装置およびその製造方法 |

-

2009

- 2009-09-11 JP JP2009210588A patent/JP4965617B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010016398A (ja) | 2010-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4398305B2 (ja) | 半導体装置およびその製造方法 | |

| JP3925809B2 (ja) | 半導体装置およびその製造方法 | |

| JP4093186B2 (ja) | 半導体装置の製造方法 | |

| JP4012496B2 (ja) | 半導体装置 | |

| US7968992B2 (en) | Multi-chip package structure and method of fabricating the same | |

| EP2019574B1 (en) | Electronic component-embedded board and method of manufacturing the same | |

| JP2006173232A (ja) | 半導体装置およびその製造方法 | |

| US20120285013A1 (en) | Electronic Component-Embedded Board and Method of Manufacturing the Same | |

| JP2004221417A (ja) | 半導体装置およびその製造方法 | |

| US7906833B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP4965617B2 (ja) | 半導体装置の製造方法 | |

| JP4316622B2 (ja) | 半導体装置の製造方法 | |

| JP4316624B2 (ja) | 半導体装置 | |

| JP5377403B2 (ja) | 半導体装置及び回路基板の製造方法 | |

| JP5292848B2 (ja) | 部品内蔵基板及びその製造方法 | |

| JP4461801B2 (ja) | 半導体装置およびその製造方法 | |

| JP2012038765A (ja) | 半導体装置およびその製造方法 | |

| JP4341484B2 (ja) | 半導体装置およびその製造方法 | |

| JP4977169B2 (ja) | 半導体装置およびその製造方法 | |

| JP4561079B2 (ja) | 半導体装置の製造方法 | |

| JP2007134739A (ja) | 半導体装置の製造方法 | |

| JP2010251795A (ja) | 半導体パッケージ | |

| KR20110081628A (ko) | 기판의 제조 방법 및 이를 이용한 기판 및 반도체 패키지 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110413 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110418 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110616 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110818 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111017 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20111205 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120321 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120329 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150406 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |