JP4920748B2 - セキュリティ機能を備えた電子ボード、及び電子ボードのセキュリティを確実にする方法 - Google Patents

セキュリティ機能を備えた電子ボード、及び電子ボードのセキュリティを確実にする方法 Download PDFInfo

- Publication number

- JP4920748B2 JP4920748B2 JP2009513662A JP2009513662A JP4920748B2 JP 4920748 B2 JP4920748 B2 JP 4920748B2 JP 2009513662 A JP2009513662 A JP 2009513662A JP 2009513662 A JP2009513662 A JP 2009513662A JP 4920748 B2 JP4920748 B2 JP 4920748B2

- Authority

- JP

- Japan

- Prior art keywords

- control

- circuit

- electrical

- data

- circuits

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/073—Special arrangements for circuits, e.g. for protecting identification code in memory

- G06K19/07309—Means for preventing undesired reading or writing from or onto record carriers

- G06K19/07345—Means for preventing undesired reading or writing from or onto record carriers by activating or deactivating at least a part of the circuit on the record carrier, e.g. ON/OFF switches

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/073—Special arrangements for circuits, e.g. for protecting identification code in memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K19/00—Record carriers for use with machines and with at least a part designed to carry digital markings

- G06K19/06—Record carriers for use with machines and with at least a part designed to carry digital markings characterised by the kind of the digital marking, e.g. shape, nature, code

- G06K19/067—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components

- G06K19/07—Record carriers with conductive marks, printed circuits or semiconductor circuit elements, e.g. credit or identity cards also with resonating or responding marks without active components with integrated circuit chips

- G06K19/073—Special arrangements for circuits, e.g. for protecting identification code in memory

- G06K19/07309—Means for preventing undesired reading or writing from or onto record carriers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06K—GRAPHICAL DATA READING; PRESENTATION OF DATA; RECORD CARRIERS; HANDLING RECORD CARRIERS

- G06K7/00—Methods or arrangements for sensing record carriers, e.g. for reading patterns

- G06K7/0013—Methods or arrangements for sensing record carriers, e.g. for reading patterns by galvanic contacts, e.g. card connectors for ISO-7816 compliant smart cards or memory cards, e.g. SD card readers

- G06K7/0086—Methods or arrangements for sensing record carriers, e.g. for reading patterns by galvanic contacts, e.g. card connectors for ISO-7816 compliant smart cards or memory cards, e.g. SD card readers the connector comprising a circuit for steering the operations of the card connector

- G06K7/0091—Methods or arrangements for sensing record carriers, e.g. for reading patterns by galvanic contacts, e.g. card connectors for ISO-7816 compliant smart cards or memory cards, e.g. SD card readers the connector comprising a circuit for steering the operations of the card connector the circuit comprising an arrangement for avoiding intrusions and unwanted access to data inside of the connector

Description

保護ゾーンは、第1の回路と第2の回路との間の信号の伝送を可能にする通信回路を備え、通信回路内の電気信号の伝送は、制御回路によって送出される電気制御信号によって調節され、上記方法は、その電気ステータスを読み出すことができるように制御回路によって電気制御信号を読み出す読み出し工程と、検出された電気ステータスが、制御回路によって課されるステータスに対応しない場合、制御回路を遮断する遮断工程とを含むアクセス制御方法に関する。

Claims (10)

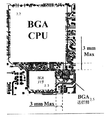

- 電子カードであって、制御回路を含む複数の第1の電子回路を備える保護ゾーンであって、前記第1の電子回路は互いに3ミリメートル以下だけ離れており、電気リンクが前記第1の回路に接続され、3ミリメートルを上回る距離だけ前記第1の回路と離れて保護信号を伝送する保護ゾーンと、3ミリメートルを上回る距離だけ、前記第1の回路と離れているか、又は前記保護信号を伝送するその電気リンクが3ミリメートルを上回る距離だけ離れている第2の電子回路を備える非保護ゾーンとを備え、前記保護ゾーンは、前記第1の回路と前記第2の回路との間の信号の伝送を可能にする通信回路を備え、前記通信回路内の電気信号の伝送は、前記制御回路によって送出される電気制御信号によって調節される電子カード。

- 請求項1記載の電子カードであって、前記通信回路内の電気信号の伝送を調節する前記電気制御信号は、前記制御回路において実行される命令の動作コードに依存する電子カード。

- 請求項1及び2の何れか一項に記載の電子カードであって、前記通信回路内の電気信号の伝送を調節する前記電気制御信号は、前記制御回路において実行される命令の動作コードのアドレスに依存する電子カード。

- 請求項1乃至3の何れか一項に記載の電子カードであって、前記通信回路内の電気信号の伝送を調節する前記電気制御信号は、前記制御回路の出力ポートによって送出される電子カード。

- 請求項1乃至4の何れか一項に記載の電子カードであって、前記電気制御信号は、前記制御回路の入力ポートに、その電気ステータスを読み出すことができるように接続され、前記制御回路によって課される論理ステータスに、ポート上に存在しているステータスが対応しない場合に前記制御回路が遮断される電子カード。

- 請求項1乃至5の何れか一項に記載の電子カードであって、前記通信回路は、前記電子制御信号がイネーブルされると、前記制御回路がデータをバックアップすることを可能にし、よって、保護部分への前記データの出力を阻止する電子カード。

- 電子カード内のデータへのアクセス制御方法であって、制御回路を含む複数の第1の電子回路を備える保護ゾーンであって、前記第1の電子回路は互いに3ミリメートル以下だけ離れており、電気リンクが前記第1の回路に接続され、最大、3ミリメートルを上回る距離だけ前記第1の回路と離れて保護信号を伝送する保護ゾーンと、3ミリメートルを上回る距離だけ、前記第1の回路と離れているか、又は、前記保護信号を伝送する電気リンクが3ミリメートルを上回る距離だけ離れている第2の電子回路を備える非保護ゾーンとを備える電子カード内のデータへのアクセス制御方法において、

前記保護ゾーンは、前記第1の回路と前記第2の回路との間の信号の伝送を可能にする通信回路を備え、前記通信回路内の電気信号の伝送は、前記制御回路によって送出される電気制御信号によって調節され、前記方法は、その電気ステータスを読み出すことができるように前記制御回路によって前記電気制御信号を読み出す読み出し工程と、検出された電気ステータスが、前記制御回路によって課されるステータスに対応しない場合、前記制御回路を遮断する遮断工程とを含む、データへのアクセス制御方法。 - 請求項7記載の、データへのアクセス制御方法であって、前記電気制御信号のステータスは、前記制御回路において実行される命令の動作コードに依存する、データへのアクセス制御方法。

- 請求項7記載の、データへのアクセス制御方法であって、前記電気制御信号のステータスは、前記制御回路において実行される命令の動作コードのアドレスに依存する、データへのアクセス制御方法。

- 請求項7乃至9の何れか一項に記載の、データへのアクセス制御方法であって、前記電子制御信号がイネーブルされると、前記通信回路において記憶を行い、よって、非保護部分に対する前記データの出力を阻止するデータ記憶工程を含む、データへのアクセス制御方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FR0652064 | 2006-06-08 | ||

| FR0652064A FR2902213B1 (fr) | 2006-06-08 | 2006-06-08 | Carte electronique dotee de fonctions securitaires |

| PCT/EP2007/055458 WO2007141233A1 (fr) | 2006-06-08 | 2007-06-04 | Carte electronique dotee de fonctions securitaires et procede de securisation de la carte electronique |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009540410A JP2009540410A (ja) | 2009-11-19 |

| JP4920748B2 true JP4920748B2 (ja) | 2012-04-18 |

Family

ID=37744086

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009513662A Expired - Fee Related JP4920748B2 (ja) | 2006-06-08 | 2007-06-04 | セキュリティ機能を備えた電子ボード、及び電子ボードのセキュリティを確実にする方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US8499332B2 (ja) |

| EP (1) | EP2024909B1 (ja) |

| JP (1) | JP4920748B2 (ja) |

| KR (1) | KR101287480B1 (ja) |

| CN (1) | CN101479746B (ja) |

| DE (1) | DE602007008233D1 (ja) |

| FR (1) | FR2902213B1 (ja) |

| WO (1) | WO2007141233A1 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW201227391A (en) * | 2010-12-16 | 2012-07-01 | Walton Advanced Eng Inc | Storage device with a hidden space and its operation method |

| JP2014038408A (ja) | 2012-08-13 | 2014-02-27 | International Business Maschines Corporation | 同時マルチスレッディング機能をもったプロセッサのパイプラインにおけるストール削減方法、削減装置及び削減プログラム |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4860351A (en) * | 1986-11-05 | 1989-08-22 | Ibm Corporation | Tamper-resistant packaging for protection of information stored in electronic circuitry |

| JPH07272398A (ja) * | 1994-03-28 | 1995-10-20 | Hitachi Ltd | ディスク装置の制御装置 |

| US5861662A (en) * | 1997-02-24 | 1999-01-19 | General Instrument Corporation | Anti-tamper bond wire shield for an integrated circuit |

| JPH1165937A (ja) * | 1997-08-25 | 1999-03-09 | Mitsubishi Electric Corp | Icメモリカード |

| US6704871B1 (en) * | 1997-09-16 | 2004-03-09 | Safenet, Inc. | Cryptographic co-processor |

| US6708273B1 (en) * | 1997-09-16 | 2004-03-16 | Safenet, Inc. | Apparatus and method for implementing IPSEC transforms within an integrated circuit |

| JPH11258293A (ja) * | 1998-03-16 | 1999-09-24 | Fujitsu Ltd | プリント配線板電気試験装置 |

| US6553496B1 (en) * | 1999-02-01 | 2003-04-22 | Koninklijke Philips Electronics N.V. | Integration of security modules on an integrated circuit |

| JP3822768B2 (ja) * | 1999-12-03 | 2006-09-20 | 株式会社ルネサステクノロジ | Icカードの製造方法 |

| US6418552B1 (en) | 1999-12-10 | 2002-07-09 | Hewlett-Packard Company | Method and apparatus for optimizing trace lengths to maximize the speed of a clocked bus |

| US20030212897A1 (en) * | 2001-08-18 | 2003-11-13 | Russell Dickerson | Method and system for maintaining secure semiconductor device areas |

| US6996692B2 (en) * | 2002-04-17 | 2006-02-07 | Matsushita Electric Industrial Co., Ltd. | Nonvolatile semiconductor memory device and method for providing security for the same |

| US7469420B2 (en) * | 2002-05-21 | 2008-12-23 | Thomson Licensing | Key transport tamper protection |

| EP1795991A1 (en) * | 2002-07-30 | 2007-06-13 | Fujitsu Limited | Method and apparatus for reproducing information using a security module |

| US7770008B2 (en) * | 2002-12-02 | 2010-08-03 | Silverbrook Research Pty Ltd | Embedding data and information related to function with which data is associated into a payload |

| FR2857534B1 (fr) * | 2003-07-09 | 2005-10-28 | Innova Card | Circuit integre comportant un module ordinaire et un module securise raccordes par une liaison protegee |

| ATE352815T1 (de) * | 2003-09-09 | 2007-02-15 | Siemens Ag | Schaltungsanordnung als schnittstelle zwischen sim-karte und gsm-modem |

| JP2005250538A (ja) * | 2004-03-01 | 2005-09-15 | Kawasaki Microelectronics Kk | デバイス間通信装置 |

| US7644289B2 (en) * | 2004-03-23 | 2010-01-05 | Harris Corporation | Modular cryptographic device providing enhanced communication control features and related methods |

| TW200538001A (en) * | 2004-05-14 | 2005-11-16 | Hon Hai Prec Ind Co Ltd | System and method for verifying space of the pcb layout nets |

| DK3422583T3 (da) * | 2004-08-30 | 2020-09-28 | Google Llc | System og fremgangsmåde for at tilvejebringe ikke-flygtig hukommelsesadministration i trådløse telefoner |

| JP2006127679A (ja) * | 2004-10-29 | 2006-05-18 | Toshiba Corp | 光ディスク装置及び光ディスク再生方法 |

| US7549064B2 (en) * | 2005-05-10 | 2009-06-16 | Hewlett-Packard Development Company, L.P. | Secure circuit assembly |

-

2006

- 2006-06-08 FR FR0652064A patent/FR2902213B1/fr not_active Expired - Fee Related

-

2007

- 2007-06-04 CN CN200780020620XA patent/CN101479746B/zh not_active Expired - Fee Related

- 2007-06-04 EP EP07729846A patent/EP2024909B1/fr not_active Expired - Fee Related

- 2007-06-04 JP JP2009513662A patent/JP4920748B2/ja not_active Expired - Fee Related

- 2007-06-04 KR KR1020087028945A patent/KR101287480B1/ko active IP Right Grant

- 2007-06-04 DE DE602007008233T patent/DE602007008233D1/de active Active

- 2007-06-04 WO PCT/EP2007/055458 patent/WO2007141233A1/fr active Application Filing

- 2007-06-04 US US12/308,022 patent/US8499332B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| FR2902213B1 (fr) | 2008-10-17 |

| KR101287480B1 (ko) | 2013-07-19 |

| CN101479746B (zh) | 2012-07-25 |

| US8499332B2 (en) | 2013-07-30 |

| WO2007141233A1 (fr) | 2007-12-13 |

| DE602007008233D1 (de) | 2010-09-16 |

| EP2024909B1 (fr) | 2010-08-04 |

| CN101479746A (zh) | 2009-07-08 |

| FR2902213A1 (fr) | 2007-12-14 |

| EP2024909A1 (fr) | 2009-02-18 |

| JP2009540410A (ja) | 2009-11-19 |

| KR20090017542A (ko) | 2009-02-18 |

| US20100017852A1 (en) | 2010-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10515234B2 (en) | Method and apparatus for securing KVM matrix | |

| US4525599A (en) | Software protection methods and apparatus | |

| CN109643360B (zh) | 用于储存于集成电路上的认证固件的系统和方法 | |

| US8185934B2 (en) | Programmable data protection device, secure programming manager system and process for controlling access to an interconnect network for an integrated circuit | |

| US9152576B2 (en) | Mode-based secure microcontroller | |

| US11003801B2 (en) | Functional device and control apparatus | |

| US9418251B2 (en) | Mesh grid protection system | |

| US6962294B2 (en) | Integrated circuit having an active shield | |

| JP4920748B2 (ja) | セキュリティ機能を備えた電子ボード、及び電子ボードのセキュリティを確実にする方法 | |

| CN101615160B (zh) | 用于码转储保护的安全系统及安全方法 | |

| WO2006052935A2 (en) | Method and apparatus for conditionally obfuscating bus communications | |

| US6665782B2 (en) | Method and apparatus for preventing unauthorized access of memory devices | |

| US11288405B2 (en) | Integrated circuit(s) with anti-glitch canary circuit(s) | |

| US6901343B2 (en) | Multilayer board in which wiring of signal line that requires tamper-resistance is covered by component or foil, design apparatus, method, and program for the multilayer board, and medium recording the program | |

| JP2007035729A (ja) | 半導体集積回路装置 | |

| JP7446708B2 (ja) | データを処理するための方法および装置 | |

| TWI807766B (zh) | 安全之全晶片通信 | |

| KR101665562B1 (ko) | 검출 회로, 그 검출 방법, 및 이를 포함하는 메모리 시스템 | |

| US20060253899A1 (en) | Expansion connector |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100507 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111004 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111216 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120117 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120201 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4920748 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150210 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |