本明細書において、各図面は理解を容易するために、また作図を容易にするため、省略および拡大あるいは縮小した箇所がある。また、同一番号または、記号等を付した箇所は同一もしくは類似の形態もしくは材料あるいは機能もしくは動作を有する。

本明細書では、駆動用トランジスタ11a、スイッチング用トランジスタ11bなどは薄膜トランジスタとして説明するが、これに限定するものではない。薄膜ダイオード(TFD)、リングダイオードなどでも構成することができる。また、薄膜素子に限定するものではない。また、シリコンウエハに形成したトランジスタでもよい。もちろん、トランジスタとは、FET、MOS−FET、MOSトランジスタ、バイポーラトランジスタでもよい。その他、ダイオード、バリスタ、サイリスタ、リングダイオード、ホトダオード、ホトトランジスタ、PLZT素子などでもよいことは言うまでもない。

本発明における定電流Iwとは、所定値に設定した電流あるいは制御した電流の意味であり、必ずしも定電流に限定するものではない。つまり、所定値の電流の意味である。定電流発生回路は、電流階調回路154と兼用してもよいし、別途定電流発生回路を設けてもよい。また、定電流Iwをソース信号線18に流し、前記ソース信号線18の電位を測定あるいは取得し、測定あるいは取得した電位をデータとしてメモリなどの記憶手段に保持させる時は、画像表示には定電流発生回路は必要ない。つまり、EL表示装置の一部ではない。

電圧プログラム方式は、画素のトランジスタの特性補償が不十分であるという欠点を有していた。しかし、本発明は、画素のトランジスタに定電流を印加するという電流プログラム方式を実施し、トランジスタのゲート端子電位を測定することにより、電流プログラム方式の利点であるトランジスタの特性補償能力を発揮させる。

ソースドライバ回路(IC)14は、単なるドライバ機能だけでなく、電源回路(チャージポンプ回路、DCDCコンバータ回路)、バッファ回路(シフトレジスタなどの回路を含む)、レベルシフタ回路、データ変換回路、ラッチ回路、コマンドデコーダ、アドレス変換回路、画像メモリなどを内蔵させてもよい。ソースドライバ回路14は、アレイ基板30にポリシリコン技術で形成してもよい。

アレイ基板30はガラス基板として説明をするが、シリコンウエハで形成してもよい。また、アレイ基板30は、金属基板、シリコンなどの半導体基板、セラミック基板、プラスティックシート(板)などを使用してよい。

本発明の表示パネルなどを構成するトランジスタ11、ゲートドライバ回路12、ソースドライバ回路(IC)14などは、ガラス基板などに形成し、転写技術により他の基板(プラスチックシート)に移し変えて構成または形成したものでもよいことは言うまでもない。

まず、本発明のEL表示装置の画素16の構造と動作、ソースドライバ回路14などについて説明をする。

図1は、本発明のEL表示装置の画素16の構成図である。1画素内に4つのトランジスタ(TFT)11(11a、11b、11c、11d)を有している。駆動用トランジスタ11aのゲート端子は、トランジスタ11bのソース端子に接続されている。トランジスタ11bおよびトランジスタ11cのゲート端子は、ゲート信号線17aに接続されている。トランジスタ11bのドレイン端子は、トランジスタ11cのソース端子ならびにトランジスタ11dのソース端子に接続され、トランジスタ11cのドレイン端子は、ソース信号線18に接続されている。トランジスタ11dのゲート端子はゲート信号線17bに接続され、トランジスタ11dのドレイン端子はEL素子15のアノード電極(端子)に接続されている。

図1の画素構成では、トランジスタ11b、11cのゲート端子は、ゲート信号線17aに接続されている。トランジスタ11b、11cは、ゲート信号線17aに印加されたオンオフ制御信号によりオン(クローズ)、オフ(オープン)制御される。トランジスタ11dのゲート端子は、ゲート信号線17bに接続されている。トランジスタ11dは、ゲート信号線17bに印加されたオンオフ制御信号によりオン(クローズ)、オフ(オープン)制御される。

ゲートドライバ12(図3では、ゲートドライバ回路12a、12b)は、ゲート信号線17a、17bを制御する。図3に図示するように、表示画面34の左端にゲートドライバ回路12aを形成または配置し、右端にゲートドライバ回路12bを形成または配置してもよい。ゲートドライバ回路12aはゲート信号線17aを制御し、ゲートドライバ回路12bはゲート信号線17bを制御する。

図1に図示する有機ELの画素構成では、第1のトランジスタ11bは、画素を選択するためのスイッチング用トランジスタとして機能させる。また、第2のトランジスタ11aは、EL素子15に電流を供給するための駆動用トランジスタとして機能させている。

ゲートドライバ12に印加するクロックCLK信号(CLK1、CLK2)、スタート信号ST(ST1、ST2)などは、コントローラ回路801からソースドライバ回路14に印加される。クロックCLK信号、スタート信号は、ソースドライバ回路14でロジックレベルがレベルシフトされ、ゲートドライバ回路12に印加される。つまり、ゲートドライバ回路12に印加される信号は、ソースドライバ回路14から供給される。

ゲートドライバ回路12aが同時に選択するゲート信号線17aは、1ゲート信号線に限定されるものではない。複数の画素行を同時に選択してもよい。たとえば、2本のゲート信号線17aを同時に選択してもよい。つまり、2画素行を同時に選択する。

表示領域34には、赤(R)、緑(G)、青(B)の3原色の画素がマトリックス状に形成されている。RGBの画素は塗りわけ蒸着により形成する。なお、R、G、Bに限定されるものではない。単色でもよく、また、シアン、イエロー、マゼンダなどでもよく、RGBに加えて、白色(W)の4色などでもよい。R、G、B、Wの場合は、カラーフィルタにより形成する。

表示領域34は複数画面を有してもよい。たとえば、メイン画面とサブ画面である。メイン画面とサブ画面のゲートドライバ回路は独立して形成し、ソース信号線18を共通にする。また、ソースドライバ回路14もメイン画面とサブ画面を共通にする。

トランジスタのオン電流は単結晶で形成されたトランジスタであれば、比較的均一である。形成温度が450〜550度(摂氏)以下の低温ポリシリ技術で形成した低温多結晶トランジスタでは、そのしきい値のバラツキが±0.2V〜±0.5Vの範囲でバラツキがある。そのため、駆動用トランジスタ11aを流れるオン電流がこれに対応してばらつき、表示にムラが発生する。これらのムラは、しきい値電圧のバラツキのみならず、トランジスタの移動度、ゲート絶縁膜の厚みなどでも発生する。また、トランジスタ11の劣化によっても特性は変化する。

トランジスタの特性バラツキは、低温ポリシリコン技術で形成されたトランジスタに限定されるものではなく、プロセス温度が450度(摂氏)以上の高温ポリシリコン技術でも、固相成長(CGS)させた半導体膜を用いて形成したトランジスタでも発生する。その他、有機材料で形成した有機トランジスタでも発生する。アモルファスシリコントランジスタでも発生する。

本発明は、以上のすべての技術で形成されたトランジスタなどからなるEL表示装置あるいは表示パネルの構成もしくは駆動方法に適用できるものである。

図1などで示す本発明の表示パネルの画素16を構成するトランジスタ11は、p−チャンネルポリシリコン薄膜トランジスタに構成される。また、トランジスタ11b、11dは、デュアルゲート以上であるマルチゲート構造としている。

図1において、本発明の表示パネルの画素16を構成するトランジスタ11bは、トランジスタ11aのソース−ドレイン間のスイッチとして作用する。したがって、トランジスタ11bは、できるだけ低リーク電流特性が要求される。トランジスタ11bのゲートの構造をデュアルゲート構造以上のマルチゲート構造とすることにより低リーク電流特性を実現できる。

図1ではすべてのトランジスタはPチャンネルで構成している。PチャンネルはNチャンネルのトランジスタに比較してモビリティが低いが、耐圧が大きくまた劣化も発生しにくい。したがって、EL表示装置に採用することが好ましい。ただし、本発明はEL表示装置の画素、ドライバ回路などをPチャンネルで構成することのみに限定するものではない。これらをNチャンネルのみで構成してもよい。また、NチャンネルとPチャンネルの両方を用いて構成してもよい。

ただし、パネルを低コストで作製するためには、画素を構成するトランジスタ11をすべてPチャンネルで形成し、ゲートドライバ回路12もPチャンネルで形成することが好ましい。このようにアレイをPチャンネルのみのトランジスタで形成することにより、マスク枚数が5枚となり、低コスト化、高歩留まり化を実現できる。

図1のように画素16の駆動用トランジスタ11a、トランジスタ(11b、11c)がPチャンネルトランジスタの場合は、突き抜け電圧が発生する。これは、ゲート信号線17aの電位変動が、トランジスタ(11b、11c)のG−S容量(寄生容量)を介して、コンデンサ19の端子に突き抜けるためである。Pチャンネルトランジスタ11bがオフするときにはVGH電圧(トランジスタのオフ電圧)となる。そのため、コンデンサ19の端子電圧がアノード電圧Vdd側に少しシフトする。そのため、トランジスタ11aのゲート(G)端子電圧は上昇し、トランジスタ11aは電流を流さない方向に変化する。したがって、より黒表示となる、良好な黒表示を実現できる。

コンデンサ19などによる突き抜け電圧のシフト量は一定であり、また、VGH電圧(トランジスタのオフ電圧)、VGL電圧(トランジスタのオン電圧)が一定値であるからである。電流駆動方式(電流プログラム方式)では、低階調ではプログラム電流が小さくなり、ソース信号線18の寄生容量の充放電が困難である。突き抜け電圧の発生効果により、プログラム電流を低減(電流が流れない方向にトランジスタ11aのゲート電圧電位をシフトさせる)させる。したがって、ソース信号線18に印加するプログラム電流を比較的大きくでき、駆動用トランジスタ11aがEL素子15に流す電流はプログラム電流よりも小さくすることができる。結果的に、小さなプログラム電流(低階調領域のプログラム電流)を画素16に書き込むことができる。

突き抜け電圧は、画素16を選択するゲート信号線17aの振幅の大きさVg=VGH−VGLに依存する。電流駆動方式においては、この突き抜け電圧を有効に作用させることが重要である。本発明では、Vgの大きさを6(V)以上としている。また、アノード電圧Vdd、カソード電圧Vssとするとき、アノード電圧とカソード電圧の電位差Ve=Vdd−Vssは、Ve=Vg−0.5(V)以下となるようにしている。

なお、トランジスタがPチャンネルの場合は、VGHはトランジスタをオフ(オープン)させる電圧であり、VGLはトランジスタをオン(クローズ)させる電圧である。トランジスタがNチャンネルの場合は、VGLはトランジスタをオフ(オープン)させる電圧であり、VGHはトランジスタをオン(クローズ)させる電圧である。

本発明は、駆動用トランジスタ11a、トランジスタ11bなどをPチャンネルに限定するものではない。しかし、駆動用トランジスタ11a(カレントミラー回路の場合は、トランジスタ11b(図12などを参照のこと))の極性(PまたはN)とスイッチ用トランジスタ11b、11cの極性を一致させることが本発明の特徴である。もしくは、スイッチ用トランジスタ11b、11cがオフになる時、駆動用トランジスタ11aの電流が流れにくくなる方向に、電位シフトするようにトランジスタの極性、ゲート信号線12bの振幅変化方向が設定されていることが特徴である。

以上のように、本発明は、画素16の駆動用トランジスタ11aおよびスイッチングトランジスタ11bの両方をPチャンネルトランジスタで形成することにより黒表示(黒および低階調範囲)を良好にできるという特徴ある効果を発揮する。なお、画素16の駆動用トランジスタ11aがNチャンネルトランジスタの場合は、スイッチングトランジスタ11bもNチャンネルトランジスタとする。つまり、駆動用トランジスタ11aとスイッチングトランジスタ11bの両方を同一極性のトランジスタで構成することが好ましい。

つぎに、図3を用いて、本発明のEL表示パネルで使用する電源(電圧)について説明をする。ゲートドライバ回路12は、主としてバッファ回路32とシフトレジスタ回路31から構成される。バッファ回路32はオフ電圧(VGH)とオン電圧(VGL)を電源電圧として使用する。一方、シフトレジスタ回路31はシフトレジスタの電源VGDDとグランド(GND)電圧を使用し、また、入力信号(CLK、UD、ST)の反転信号を発生させるためのVREF電圧を使用する。また、ソースドライバ回路(IC)14は、電源電圧Vsとグランド(GND)電圧を使用する。

ゲートドライバ回路12aはゲート信号線17aをオンオフ制御する。ゲートドライバ回路12bはゲート信号線17bをオンオフ制御する。説明を容易にするため、画素構成は図1を例にあげて説明をする。

各シフトレジスタ回路31は、正相と負相のクロック信号CLKx(CLKxP、CLKxN)、スタートパルス(STx)で制御される。なお、xは添え字である。その他、ゲート信号線の出力、非出力を制御するイネーブル(ENBL)信号、シフト方向を上下逆転するアップダウン(UD)信号を付加することが好ましい。他に、スタートパルスがシフトレジスタ回路31にシフトされ、そして出力されていることを確認する出力端子などを設けることが好ましい。

シフトレジスタ回路31のシフトタイミングはコントローラ回路(図示せず)からの制御信号で制御される。また、外部データのレベルシフトを行うレベルシフト回路31を内蔵する。なお、クロック信号は正相のみとしてもよい。正相のみのクロック信号とすることにより信号線数が削減でき、狭額縁化を実現できる。

シフトレジスタ回路31のシフトタイミングはコントロールIC(図示せず)からの制御信号で制御される。また、ゲートドライバ回路12は、外部データのレベルシフトを行うレベルシフト回路を内蔵する。なお、クロック信号は正相のみとしてもよい。正相のみのクロック信号とすることにより信号線数が削減でき、狭額縁化を実現できる。

シフトレジスタ回路31の駆動能力は小さいため、直接にはゲート信号線17を駆動することができない。そのため、シフトレジスタ回路31の出力とゲート信号線17を駆動する出力ゲート間には少なくとも2つ以上のインバータ回路(バッファ回路32に含まれる)が形成されている。

ここで理解を容易にするため、電圧値を規定する。まず、アノード電圧Vddを6(V)とし、カソード電圧Vssを−9(V)とする(図1などを参照のこと)。GND電圧は0(V)とし、ソースドライバ回路14のVs電圧はVdd電圧と同一の6(V)とする。VGH1とVGH2電圧は、Vddより0.5(V)以上3.0(V)以下とすることが好ましい。ここでは、VGH1=VGH2=8(V)とする。

ゲートドライバ回路12のVGL1は、図1のトランジスタ11cのオン抵抗を十分に小さくするため、低くする必要がある。ここでは、回路構成を容易にするため、VGH1と絶対値が逆であるVGL1=−8(V)にする。VGDD電圧はシフトレジスタ回路の電圧である。VGHよりも低く、GND電圧よりも高くする必要がある。ここでは、発生電圧回路を容易にし、回路コストを低減するため、VGH電圧の1/2の4(V)にする。一方で、VGL2電圧は、余り低くすると、トランジスタ11bのリークを発生する危険性があるため、VGDD電圧とVGL1電圧の中間電圧にすることが好ましい。ここでは、電圧回路を容易にし、回路コストを低減するため、VGDD電圧と絶対値が等しく、また反対極性である−4(V)にする。

本発明のEL表示装置の各部の電圧について図4を用いて説明をする。本発明では、カソード電圧Vssをグランド(GND)電圧とする。アノード電圧Vddとソースドライバ回路14の電源電圧Vdは共通にしている。つまり同一電圧とする。もちろん、カソード電圧Vssは、GND以外の電圧に設定することができるが、図4のように構成することにより、電源回路が簡略化でき、効率も向上する。

図4の本発明の電源回路方式では、アノード電圧Vddが上下変動すれば、ソースドライバ回路14の電源電圧Vdも同様に上下変動する。プリチャージ電圧Vpの最高電圧は、アノード電圧Vddと同一(一致)にし、最低電圧は、図4に図示するようにVminとする。したがって、プリチャージ電圧Vpは、アノード電圧Vddを基準としてグランド方向に電位をとる。Vmin電圧は、負のレギュレータで入力電圧をVddとグランド(GND)にすることにより容易に発生できる。なお、Vdd−Vminの値は、2V以上4V以下とすることが好ましい。プリチャージ電圧Vpは、VddとVmin電圧を刻み数(階調数)で分割して電子ボリウムを構成し、入力デジタルデータを前記電子ボリウムでアナログデータに変換して出力する。プリチャージ電圧Vpとは、プリチャージ電圧Vp電圧だけでなく、プログラム電圧も意味する。

ゲートドライバ回路12が出力するゲートオン電圧VGHは、図4に図示するようにアノード電圧Vddを基準(原点)にして正方向にとる。VGH−Vddは、0.5V以上2.5V以下にする。また、ゲートドライバ回路12が出力するゲートオフ電圧VGLは、図4に図示するようにグランド電圧(GND)を基準(原点)にして負方向にとる。GND−VGLは、0.5以上2.5V以下にする。VGLは、Vddを基準として発生してもよい。VGH、VGLはチャージポンプ回路で発生する。

画素16を選択するゲート信号線17aの振幅の大きさVg=VGH−VGLとするとき、本発明では、Vgの大きさを6(V)以上としている。また、アノード電圧Vdd、カソード電圧Vssとするとき、アノード電圧とカソード電圧の電位差Ve=Vdd−Vssは、Vg+2(V)以上としている。また、VGL電圧は、ポリシリコン技術により、アレイ基板30にチャージポンプ回路などを形成して発生させてもよい。また、アノード電圧を発生するDCDC(直流−直流)コンバータ回路には、入力部または出力部に突入電流制限回路を設けることが好ましい。

図4では、VGL1とVGL2(図3を参照のこと)を同一の電圧としたが、これに限定するものではなく、VGL1<VGL2の関係にすることが好ましい。つまり、VGL1の方がVGL2より電圧が低い。ただし、駆動用トランジスタ11aがPチャンネルの場合である。駆動用トランジスタ11aがNチャンネルの場合は、逆の関係にする。なお、VGL1は画素行を選択するゲートドライバ回路12aのオン電圧であり、VGL2は、トランジスタ11dを選択するゲートドライバ12bのオン電圧である。

VGL1をVGL2より小さくすることにより、ゲート信号線17aの振幅動作により、駆動用トランジスタ11aのゲート端子の突き抜け電圧が大きくなり、本発明の駆動方式と組み合わせることにより良好な黒表示を実現できるからである。たとえば、VGL1=−9(V)、VGL2=−3(V)が例示される。

駆動用トランジスタ11aが出力するプログラム電流の大きさを大きくするには、アノード電圧Vddを高くする必要がある。プログラム電流を大きくすれば、EL素子15は高輝度に発光するから、EL表示装置を高輝度表示することができる。高輝度表示はEL表示装置を屋外で使用するときに有効である。しかし、常時、アノード電圧Vddを高くするとEL表示装置で使用する消費電力が増大する。そのため、駆動用トランジスタ11aが大きなプログラム電流を出力する期間あるいは状態を極力少なくしたい。本発明では、高輝度表示が必要な場合に、アノード電圧Vddを高くする。また、低階調表示あるいは低点灯率のように、プログラム電流の書き込み不足が発生する場合に、図4に示すようにアノード電圧を高くする。

図4では、高輝度表示が必要な場合、低階調表示あるいは低点灯率のようにプログラム電流の書き込み不足が発生する場合に、アノード電圧Vddを高くするとして説明した。しかし、駆動方式としては、カソード電圧Vssを低下させる方式も考えられる。つまり、高輝度表示が必要な場合、低階調表示あるいは低点灯率のようにプログラム電流の書き込み不足が発生する場合に、カソード電圧Vssを低くする方式が例示される。また、高輝度表示が必要な場合、低階調表示あるいは低点灯率のようにプログラム電流の書き込み不足が発生する状態をアノード電圧Vddまたはカソード電圧Vssを通常状態とし、通常の輝度時あるいは、書き込み不足が発生してもよい場合に、アノード電圧Vddまたはカソード電圧を低くしてもよい。また、アノード電圧Vddとカソード電圧Vssの両方を変化させてもよい。

また、動画、静止画など表示画像の種類あるいは状態により、アノード電圧Vdd、カソード電圧Vssを変化させてもよい。また、外部照度の高低に対応してアノード電圧Vdd、カソード電圧Vssを変化させてもよい。外部照度が高い時は、アノード電圧Vddなどを高くし、照度が低い時は、アノード電圧Vddなどを低くする。照度の検出は、PINホトダイオードなどにより行う。また、パネル温度より、プログラム電圧またはプログラム電流を印加したときの書き込み状態が変化する場合がある。この場合も、アノード電圧Vddなどを変化すればよい。温度の検出はパネルの裏面あるいは無効領域(表示に有効な光が出射しない領域)に取り付けたサーミスタ、ポジスタで行う。アノード電圧Vdd、カソード電圧Vssの変化あるいは調整は、本発明は、表示輝度、プログラム電流の書き込み状態、表示状態、点灯率、外部照度などに対応させて、アノード電圧Vdd、カソード電圧Vssを変化あるいは調整する方式である。

以上のように表示装置で使用する電源電圧を発生あるいは制御することにより、アノード電圧Vddを変化させた時、同時にソースドライバ回路14の電源電圧、プリチャージ電圧VpのVmin、VGHも変化する。したがって、高輝度表示が必要な時に、アノード電圧Vddなどを変化させても、VGH、プリチャージ電圧Vpの相対値も同時に変化するので良好な画像表示を維持できる。また、図6、図9などで説明するN倍駆動、duty比駆動方式と組み合わせることも有効である。Nが大きいときに、アノード電圧Vddなどを高くする。

本発明では、点灯率に対応して図4で示すアノード電圧Vddなどを変化させる。点灯率が低い時は、アノード電圧Vddを定常値よりも高くし、また、基準電流を大きくすることにより、電流駆動における書き込み不足を改善する。また、図9、図10、図11などで説明するN倍駆動(非点灯領域挿入駆動)を実施し、階調に対する輝度は定常値と略同一に制御している。

図5は図1の動作の説明図である。図5(a)は、ソースドライバ回路14から定電流を供給し、駆動用トランジスタ11aから定電流Iwがソースドライバ回路14に向かって流れている状態を示している。駆動用トランジスタ11aが定電流Iwを流している時は、トランジスタ11b、11cがクローズ(オン)状態である。したがって、駆動用トランジスタ11aのゲート端子電位とソース信号線18の電位は同一である。

図5(b)は、駆動用トランジスタ11aからEL素子15に電流Ieを供給している状態を示している。つまり、EL素子15に電流を供給し、画像表示を行っている状態である。

以上の動作を表示画面34で図示すると、図6に図示するようになる。図6(a)の61は、表示画面34における、ある時刻での電流プログラムされている画素(行)(書き込み画素行)を示している。あるいは、Va、V0電圧を測定している画素行(画素)である。または、目標電圧Vcを書き込んでいる画素行(画素)である。

基本的には、定電流が0(A)の時のソース信号線18の電位をV0とし、定電流Ia(Iaは任意の値)の時のソース信号線18の電位をVaと呼ぶ。しかし、便宜的に、また、説明を容易にするため、映像信号の階調0に対応する電圧をV0とし、映像信号の階調aに対応する電圧をVaの意味で使用する場合もある。

画素(行)61は、非点灯(非表示画素(行))とする。非点灯にするには、ゲートドライバ回路12bを制御し、画素16のトランジスタ11dをオープン状態にすればよい。トランジスタ11dをオープンにするためには、ゲート信号線17bにオフ電圧を印加すればよい。ゲートドライバ回路12がゲート信号線17にオフ電圧を印加する位置は、水平同期信号に同期してシフトさせる。

非点灯(非表示)とは、EL素子15に流れていない状態をいう。もしくは、一定以内の小さな電流が流れている状態をいう。つまり、暗い表示状態である。したがって、非点灯画素行とは、該当画素行のEL素子15に電流が流れていない状態あるいは比較的暗い表示状態を意味する。

表示画面34の非表示(非点灯)の範囲を非表示領域62と呼ぶ。表示画面34の表示(点灯)の範囲を表示(点灯)領域63と呼ぶ。表示領域63の画素16のスイッチング用トランジスタ11dはクローズし、EL素子15に電流が流れている。ただし、黒表示の画像表示ではEL素子15に電流が流れないのは当然である。スイッチング用トランジスタ11dがオープンの領域は、非表示領域62となる。

図6、図9では、表示画面34に非表示領域62と、表示領域63を発生させる。このように表示する駆動方法をduty比駆動方式と呼ぶ。

本発明は、表示領域63と非表示領域62との比を変化させる、あるいは表示画面34の面積に対し非表示領域62の面積を変化させる、あるいは表示状態の画素数を増減することにより、画面の輝度あるいは明るさを調整することを特徴とする。

本発明は、画面34に占める表示領域63を複数に分割できる。また、表示領域63または非表示領域62の分割数を動画表示と静止画表示で異ならせる。画面34に占める非表示領域62または表示領域63が、帯状となって画面の上から下方向または画面の下から上方向に移動することを特徴とする。

通常、NTSCのフレームレートは60Hz(1秒間に60枚、1画面を書き換える時間は1/60秒)、PALは50Hz(1秒間に50枚)である。図6、図9のように、本発明のduty比駆動を実施する場合は、フレームレートを1.2倍以上2.5倍以下に変換して表示する。つまり、入力フレームレートが60Hzの場合は、60×1.2=72Hz以上、60×2.5=150Hz以下にする。好ましくは、1.25倍の75Hz以上2倍の120Hz以下とする。あるいは、1.25倍の75Hz、1.5倍の90Hz、2倍の120Hzのいずれかを選択する。

入力信号は、画像メモリに蓄積し、フレームレート変換を行う。もしくは、入力信号のフレームレートを72Hz以上150Hz以下で本発明の表示装置に入力する。以上のフレームレートに関する事項は、本発明の他の実施例においても適用される。

図1の画素構成の場合は、図5(a)に図示するように、プログラム電流(定電流)Iwがソース信号線18に流れる。このプログラム電流Iwが駆動用トランジスタ11aを流れ、プログラム電流Iwを流す電流が保持されるように、コンデンサ19に電圧設定(プログラム)される。または、駆動用トランジスタ11aのゲート端子にプログラム電流Iwを流す電流が流れるようにコンデンサ19に電圧が保持される。このとき、トランジスタ11dはオープン状態(オフ状態)である。

EL素子15に電流を流す期間は図5(b)のように、トランジスタ11c、11bがオフし、トランジスタ11dが動作する。つまり、ゲート信号線17aにオフ電圧(VGH)が印加され、トランジスタ11b、11cがオフする。一方、ゲート信号線17bにオン電圧(VGL)が印加され、トランジスタ11dがオンする。

タイミングチャートを図7に図示する。図7において、選択された画素行の画素16では、ゲート信号線17aにオン電圧(VGL)が印加されている時(図7(a)を参照)には、ゲート信号線17bにはオフ電圧(VGH)が印加されている(図7(b)を参照)。この期間は、選択された画素行のEL素子15には電流が流れていない(非点灯状態)。選択期間は1水平走査期間(1H)としている。

ゲート信号線17aにオン電圧が印加されていない(選択されていない)画素行で、点灯状態の画素行では、ゲート信号線17bにはオン電圧(VGL)が印加されている。この画素行のEL素子15には電流が流れ、EL素子15が発光している。

ゲート信号線17aにオン電圧が印加されていない(選択されていない)画素行で、非点灯状態の画素行では、ゲート信号線17bにはオフ電圧(VGH)が印加されている。この画素行のEL素子15には電流が流れず、EL素子15は非発光状態である。

以上の動作を図示すると、図6のようになる。図6(a)の61は、表示画面34における、ある時刻での電流プログラムされている画素(行)(書き込み画素行)を示している。画素(行)61は、非点灯(非表示画素(行))とする。また、スイッチング用トランジスタ11dがクローズし、EL素子15に電流が流れている(ただし、黒表示は流れない)領域は、表示領域63となる。また、スイッチング用トランジスタ11dがオープンの領域は、非表示領域62となる。

図1の画素構成の場合は、図5(a)に示すように、電流Iwが駆動用トランジスタ11aを流れ、プログラム電流Iwを流す電流が保持されるように、コンデンサ19に電圧設定(プログラム)される。または、駆動用トランジスタ11aのゲート端子にプログラム電流Iwを流す電流が流れるように電圧が保持される。このとき、トランジスタ11dはオープン状態(オフ状態)である。

次に、EL素子15に電流を流す期間は図5(b)のように、トランジスタ11c、11bがオフし、トランジスタ11dが動作する。つまり、ゲート信号線17aにオフ電圧(VGH)が印加され、トランジスタ11b、11cがオフする。一方、ゲート信号線17bにオン電圧(VGL)が印加され、トランジスタ11dがオンする。

Va電圧を測定あるいは取得する際に、ソース信号線18の充放電を高速に行う場合、また、画像表示に黒挿入(非表示領域挿入)を行い、動画視認性を向上させる場合は、定電流の大きさをN倍にする。定電流の大きさをN倍にすることによりEL素子15に流れる電流もN倍となる。

Vx(xは階調番号)を従来と同様に1倍とする場合は、N倍の定電流を書き込み効果によりソース信号線18の充放電を高速にできるという効果が発揮される。この場合は、基準となるVa電圧がすでにN倍のEL電流となる電圧であるから、加減算するVx電圧もこの点を考慮して設定する必要がある。目標電圧Vcも同様である。

以下、説明を容易にするため、Va電圧を測定する際の定電流IwもN倍(基準となる電圧Vaも駆動用トランジスタ11aがN倍の電流を流すように設定される。)とし、Va、V0に加算されるVxも駆動用トランジスタ11aがEL素子15にN倍の電流を流すように設定されるとする。また、1倍の電流の時にEL表示装置が表示する表示画面34の輝度はBとし、N倍の電流が流れる時は発光部の輝度は、B×Nの輝度で表示されるものとする。なお、説明は、Nは1以上として説明するが、Nが1未満であっても、本発明は適用できることは言うまでもない。

図6、図9では、表示画面34の表示領域63の画素16をN倍の輝度で発光させる。もしくは、N倍の電流を流す。このように、表示する駆動方法をN倍駆動方式と呼ぶ。

EL素子15に流す定電流あるいはプログラム電流Iwは、表示画面34の平均(所定)輝度Bを得るのに必要な電流のN倍とする。したがって、EL素子15は、所定のN倍の輝度(N・B)で点灯する。点灯期間は1F/Nとする。1Fとは1フィールド(フレーム)である。なお、説明を容易にするため、1フィールド(フレーム)にブランキング期間はないとして説明をする。実用上は、ブランキング期間があるため、正確にはN・Bとはならない。つまり、1Fの1/Nの期間、N倍の輝度(N・B)でEL素子15が発光する。したがって、1Fを平均した表示パネルの表示輝度は、(N・B)×(1/N)=B(所定輝度)となる。

なお、Nはいずれの値でもよい。ただし、Nがあまりにも大きいとEL素子15に流れる瞬時電流が大きいため、Nは10以下にすることが好ましい。もちろん、N=1とし、書き込み画素行181以外を表示(点灯)領域63としてもよいことは言うまでもない。この場合は、EL素子15に流す電流Iwは、表示画面34の平均(所定)輝度Bを得るのに必要な電流とする。したがって、EL素子15は、所定の輝度Bで点灯(発光)する。

また、発光輝度N・Bとなるように定電流あるいはプログラム電流Iwを流す理由の1つは、ソース信号線18の寄生容量の影響を小さくするためである。大きな電流を流すことにより、寄生容量の電荷を短期間で充放電することができるようになる。

以上の実施例は、主としてシリコンチップからなるICでソースドライバ回路(IC)14を構成するものであった。しかし、本発明はこれに限定するものではなく、図8などに図示するように、アレイ基板30に直接にポリシリコン技術(CGS技術、低温ポリシリコン技術、高温ポリシリコン技術など)を用いて出力段回路81など(ポリシリコン電流保持回路82)を形成または構成してもよい。

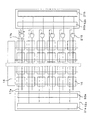

図8は、R、G、Bの出力段回路81(R用は81R、G用は81G、B用は81B)と、RGBの出力段回路81を選択するスイッチSがポリシリコン技術で形成(構成)されている。スイッチSは1水平走査期間(1H期間)を時分割して動作する。基本的には、スイッチSは、1Hの1/3期間がRの出力段回路81Rに接続され、1Hの1/3期間がGの出力段回路81Gに接続され、残りの1Hの1/3期間がBの出力段回路81Bに接続される。

図8に図示するように、シフトレジスタ回路、サンプリング回路などを有するソースドライバ(回路)14は、出力端子83でソース信号線18と接続される。ポリシリコンからなるスイッチSが時分割で切り換えられ、出力段回路81R、81G、81Bに接続される。出力段回路81(81R、81G、81B)はRGBの映像データからなる電流が保持される。なお、図8ではポリシリコン電流保持回路82は1段分しか図示していないが、実際には2段構成されていることは言うまでもない。

図8では、スイッチSは、1Hの1/3期間がRの出力段回路81Rに接続され、1Hの1/3期間がGの出力段回路81Gに接続され、残りの1Hの1/3期間がBの出力段回路81Bに接続されると説明したが本発明はこれに限定するものではない。R、G、Bを選択する期間は異なっていてもよい。これは、R、G、Bのプログラム電流Iwの大きさが異なっているためである。R、G、BでEL素子15の効率が異なるため、R、G、Bでプログラム電流の大きさが異なる。プログラム電流の大きさが小さいと、ソース信号線18の寄生容量の影響を受けやすいため、プログラム電流の印加期間を長くし、十分にソース信号線18の寄生容量の充放電期間を確保する必要がある。一方で、ソース信号線18の寄生容量の大きさは、R、G、Bで同一であることが多い。

図6では表示領域63を1つにした方式である。しかし、本発明はこれに限定するものではない。たとえば、図9に図示するように、表示領域63と非表示領域62とを複数に分散させてもよい。

また、図9に図示するように、間欠する間隔(非表示領域62/表示領域63)は等間隔に限定するものではない。たとえば、ランダムでもよい(全体として、表示期間もしくは非表示期間が所定値(一定割合)となればよい)。また、RGBで異なっていてもよい。つまり、白(ホワイト)バランスが最適になるように、R、G、B表示期間もしくは非表示期間が所定値(一定割合)となるように調整(設定)すればよい。

非表示領域62とは、ある時刻において非点灯EL素子15の画素16領域である。表示領域63とは、ある時刻において点灯EL素子15の画素16領域である。非表示領域62、表示領域63は、水平同期信号に同期して、1画素行ずつ位置がシフトしていく。

本発明の駆動方法では、図10に図示するように間欠表示実施することができる。しかし、間欠表示を実施するにあたり、トランジスタ11dは最大でも1H周期でオンオフ制御するだけでよい。したがって、回路のメインクロックは従来と変わらないため、回路の消費電力が増加することもない。液晶表示パネルでは、間欠表示を実現するために間欠表示の期間、映像データを蓄積するため画像メモリが必要である。本発明は、画像データは各画素16のコンデンサ19に保持されている。そのため、本発明の駆動方法では間欠表示を実施するための画像メモリは不要である。

本発明の駆動方法はスイッチングのトランジスタ11d(図1などを参照のこと)などをオンオフさせるだけでEL素子15に流す電流を制御する。つまり、EL素子15に流れる電流Iwをオフしても、画像データはそのまま画素16のコンデンサ19に保持されている。したがって、次のタイミングでトランジスタ11dなどをオンさせ、EL素子15に電流を流せば、その流れる電流は前に流れていた電流値と同一である。

本発明では黒挿入(黒表示などの間欠表示)を実現する際においても、回路のメインクロックをあげる必要がない。また、時間軸伸張を実施する必要もないための画像メモリも不要である。また、有機EL素子15は電流を印加してから発光するまでの時間が短く、高速に応答する。そのため、動画表示に適し、さらに間欠表示を実施することにより、従来のデータ保持型の表示パネル(液晶表示パネル、EL表示パネルなど)の問題である動画表示の問題を解決できる。

さらに、大型の表示装置でソース信号線18の配線長が長くなり、ソース信号線18の寄生容量が大きくなる場合は、N値(Nは1よりも大きな値)を大きくすることにより対応できる。ソース信号線18に印加するプログラム電流値をN倍にした場合、ゲート信号線17b(トランジスタ11d)の導通期間を1F/Nとすればよい。これによりテレビ、モニターなどの大型表示装置などにも適用が可能である。

1つの本発明は、電流駆動の画素構成のEL表示パネルにおいて、各画素の駆動用トランジスタ11aに定電流を流し、または、定電流(Iw=0)が流れないようにして、Va電圧またはV0電圧を測定あるいは取得する。測定あるいは取得したVa電圧またはV0電圧をA/D変換してメモリなどに格納する。画像表示時に、このVa電圧またはV0電圧を読み出しD/A変換し、プリチャージ電圧Vpとしてソース信号線18に印加する。プリチャージ電圧Vpの印加後に、必要に応じてプログラム電流を印加するものである。

1つの本発明は、各画素の駆動用トランジスタ11aに定電流を印加し、または、電流が流れないようにして、Va電圧またはV0電圧を測定する。測定した電圧はA/D変換してメモリなどに格納する。画像表示時に、このVa電圧またはV0電圧を読み出しD/A変換し、このVa電圧またはV0電圧を基準として階調電圧Vx(xは階調番号)を加算し、目標電圧Vcを発生する方式である。

なお、本発明はこれに限定するものでない。たとえば、電圧Vaを測定あるいは取得する際、印加する定電流Iwを最大階調Iwmに該当する電流としてもよい。

最大階調に該当する定電流Iwmを駆動用トランジスタ11aに印加することにより、駆動用トランジスタ11aは最大階調の電流が流れるように、そのゲート端子に電圧Vamが発生する。このVamを基準にし、階調電圧Vxを減算して目標電圧Vcを発生させる。発生させた電圧Vcmを駆動用トランジスタ11aのゲート端子に印加する。

以上のように、本発明の重要な駆動方式の重要なあるいは特徴ある動作は、電流駆動方式の画素を流れる電流をソース信号線18に取り出す、もしくはソース信号線18の電位を測定することである。駆動用トランジスタ11aもしくは駆動用トランジスタ11aとカレントミラー結合されたトランジスタ11bのドレイン端子またはソース端子が、直流的にソース信号線18に結線されている構成あるいは配置、つまり、駆動用トランジスタ11(11a、11b)である必要がある。EL素子15に電流を流すとは、EL素子15に電流を供給する場合と、EL素子15から前記駆動用トランジスタ11に流れ込む場合の両方を含む。

本発明は、Va、V0、Vamを基準として駆動用トランジスタ11に略1倍の電流Ieを流す実施例であった。しかし、本発明はこれに限定するものではない。たとえば、「1F/Nの期間の間だけ、EL素子15に電流を流し、他の期間(1F(N−1)/N)は電流を流さない」駆動方式では、定電流をN倍に設定してもよいことは言うまでもない。つまり、N倍の定電流(リセット電流)に対応するVa電圧を求め、この電圧Vaを基準にして目標電圧Vcを発生させる。なお、N倍の定電流としたが、これに限定するものではない。Nは1以上であればいずれの値でもよい。

この方式は、ソース信号線18の寄生容量が大きい場合に特に有効である。また、EL表示装置が10インチ以上と大きい場合に有効である。ソース信号線18の寄生容量が大きい場合、リセット電流(プログラム電流Iw)をN倍にすること(少なくも1倍以上とすること)により、定電流Iwの「書き込み不足」を改善することができる。

本発明の駆動方法では、図11に図示するように赤(R)、緑(G)、青(B)ごとに間欠表示実施することができる。しかし、間欠表示を実施するにあたり、トランジスタ11dは最大でも1H周期でオンオフ制御するだけでよい。したがって、回路のメインクロックは間欠表示を行わない駆動方式と同じであるため、回路の消費電力が増加することもない。液晶表示パネルでは、間欠表示を実現するために画像メモリが必要である。

本発明の画素構成は、図1の構成を例示して説明するが、これに限定するものではない。たとえば、図12の画素構成であってもよい。図12の画素構成は、電流プログラム時は、トランジスタ11c、11dがオン(クローズ)する。ソースドライバ回路14がプログラム電流(定電流)Iwを出力する。駆動用トランジスタ11bとカレントミラー回路を構成するトランジスタ11aにプログラム電流(定電流)Iwが流れ、プログラム電流に対応した電圧がコンデンサ19に保持される。なお、トランジスタ11eはゲート信号線17bに印加した制御信号(オンオフ信号)により、オンオフ(クローズオープン)制御されて図11、図9などで説明した間欠制御などを実現する。

図12の実施例は、トランジスタ11aにプログラム電流Iwを流す。図1のようにEL素子15に電流Ieを印加するトランジスタ11bにプログラム電流(定電流)Iwを流す実施例ではない。図12の画素構成は、トランジスタ11aとトランジスタ11bとがカレントミラー回路を構成し、ミラー比が1の場合は、トランジスタ11aを流れる電流Iwとトランジスタ11bを流れる電流Ieが等しい。しかし、トランジスタ11aにプログラム電流Iwを流し、トランジスタ11bの特性補償をするという点では、図1の画素構成と同一である。

本発明の技術的思想は、ソースドライバ回路14などからプログラム電流または定電流Iwなどを流し、直接的に駆動用トランジスタ11aまたは間接的にEL素子15に電流を流す駆動用トランジスタ11bの特性補償を行う点にある。定電流Iwの印加により、駆動用トランジスタ11の特性がゲート端子電位(=ソース信号線18の電位)として出力されるからである。この出力された電圧を変数として用いて、階調電流あるいは階調電圧を求める。したがって、図12の画素構成であっても、本発明の駆動方式を実施することができるから、図12の画素構成は、本発明の技術的範疇である。なお、図12の画素構成では、トランジスタ11eを省略してもよい。Va測定時などに定電流Iwが分流されてEL素子15に流れることがないからである。

図1、図12などの画素構成は、トランジスタ11dによりEL素子15に流す電流をトランジスタ11dにより制御するものであった。本発明はこれに限定するものではない。たとえば、図13に図示する画素構成でも本発明を適用できる。図13は、トランジスタ11dがなくともEL素子15に印加する電流をオンオフ制御することができる。

図13では、ゲートドライバ回路12bは、ゲート信号線17bを制御し、ゲート信号線17bの電位は、Vdd電圧と、それより低い電圧であるEL素子15に電流が流れない電圧Vgで駆動される。つまり、ゲート信号線17bには、Vdd電圧とVg電圧が出力される。ゲート信号線17bにVdd電圧が印加されたときは、EL素子15に電流が流れ、ゲート信号線17bにVg電圧が印加されたときには、EL素子15には電流が流れない。駆動用トランジスタ11aに定電流Iwを印加する点において、図13でも図1と同様である。したがって、図13のように、ゲートドライバ12bを有さない構成も本発明の技術的範疇である。同様に、図1の画素構成の変形である図14にも適用できることはいうまでもない。スイッチング用トランジスタ11dをオンオフ制御する。

駆動用トランジスタ11a、11bは1つのトランジスタに限定するものではなく、複数個で構成してもよい。たとえば、5つのトランジスタ11aを並列あるいは直列に形成する構成が例示される。また、スイッチング用トランジスタ11c、11dなどを複数個並列にあるいは直列に形成してもよい。

以下、ソースドライバ回路14と、定電流あるいはプログラム電流Iwの電流出力回路について説明をする。図15は、本発明のソースドライバ回路14の構成の説明図である。本発明のソースドライバ回路14は、赤(R)、緑(G)、青(B)に対応する基準電流回路153(153R,153G、153B)を有している。

基準電流回路153は、抵抗R1(R1r、R1g、R1b)とオペアンプ151a、トランジスタ167aから構成される。抵抗R1(R1r、R1g、R1b)の値は、R、G、Bの階調電流に対応して独立に設定あるいは調整できるように構成されている。抵抗R1は、ソースドライバ回路14の外部に配置された外付け抵抗である。

オペアンプの+端子cには、電子ボリウム152により、電圧Viが印加されている。電圧Viは、安定した基準電圧Vsを抵抗Rで分圧し、スイッチS(S1、S2、S3、・・・・)で分圧して発生した電圧を選択することにより得られる。

電子ボリウム152は、外部信号でスイッチSの制御することにより出力電圧Viを変化させるものである。したがって、外部からの制御信号により、出力電圧を変化させる電圧出力回路と考えてもよい。また、本発明はこれに限定するものではなく、内部インピーダンスを変化させる電子抵抗であってもよい。また、電圧だけでなく、出力電流を変化させるものであってもよい。たとえば、図15において、外部からの制御信号により、基準電流Icを直接発生あるいは供給するものであってもよい。これらの概念も電子ボリウム152の技術的思想に含まれる。

基準電流Icは(Vs−Vi)/R1となる。RGBの基準電流Ic(Icr、Icg、Icb)は、それぞれ独立した基準電流回路153で調整あるいは可変される。可変は、RGBごとに形成された電子ボリウムで実施される。したがって、電子ボリウム152に印加される制御信号により、電子ボリウム152から出力される電圧Viの値が変化する。電圧ViによりRGBの基準電流の大きさが変化し、端子83から出力される階調電流(プログラム電流)Iwの大きさが比例して変化する。

発生した基準電流Ic(Icr、Icg、Icb)は、トランジスタ167aから167bに印加される。トランジスタ167bとトランジスタ群165cとはカレントミラー回路を構成している。なお、図15において、トランジスタ167b1は、1つのトランジスタで構成しているように図示しているが、実際には、トランジスタ群165cと同様に、単位トランジスタ164の集合(トランジスタ群)として形成している。

ソースドライバ回路14が出力する階調数をKとし、単位トランジスタ164の大きさをSt(平方μm)としたとき、40 ≦ K/√(St) かつ St ≦ 300を満足するように、単位トランジスタ164が形成されている。

トランジスタ群165cからのプログラム電流Iwは出力端子83より出力される。トランジスタ群165cの各単位トランジスタ164のゲート端子およびトランジスタ167bのゲート端子は、ゲート配線163で接続されている。

トランジスタ群165cは、図16に図示するように、単位トランジスタ164の集合として構成される。理解を容易にするため、映像データとプログラム電流は比例あるいは相関の関係で変換されるとして説明する。映像信号によりスイッチ161が選択され、スイッチ161の選択により、単位トランジスタ164の集合としてのプログラム電流Iwが発生する。したがって、映像信号をプログラム電流Iwに変換できる。本発明は単位トランジスタ164の単位電流が、映像データ1の大きさに該当するように構成されている。

各端子83の出力電流Iwがバラツキなく発生するには、複数の単位トランジスタ164を動作させる必要がある。各出力端子83で出力電流Iwのバラツキを少なくするためには、電流を発生する単位トランジスタ164が占める面積を一定以上の大きさにする必要がある。したがって、定電流Iwを各端子83でバラツキなく(精度よく)出力できるようにするには、出力電流源を複数の単位トランジスタ164で形成し、かつ、所定の面積以上に構成する必要がある。本発明では、図15、図16は階調電流回路として、説明しているが、単位トランジスタ164の個数を固定すれば、所定の定電流Iwとなる。したがって、トランジスタ群165は定電流Iwの発生部であり、階調電流回路154である。もちろん、図15の定電流回路153などを使用してもよい。

単位電流とは、基準電流Icの大きさに対応して単位トランジスタ164が出力する1単位のプログラム電流の大きさである。基準電流Icが変化すると、単位トランジスタ164が出力する単位電流も比例して変化する。トランジスタ167bと単位トランジスタ164がカレントミラー回路を構成しているからである。

図15のトランジスタ167b1、図16のトランジスタ167bは、本発明の別のトランジスタの一例にあたる。なお、トランジスタ167bはトランジスタ群165bを構成してもよい。図20にトランジスタ群165bとして図示している。

単位トランジスタ164とは、1単位あるいは最小単位のプログラム電流Iwを出力するトランジスタもしくは電流源である。つまり、単位トランジスタ164=単位電流源である。また、複数の単位トランジスタ164が集合し、階調に対応したプログラム電流を出力する構成あるいは部分をトランジスタ群(電流出力回路)165cと呼ぶ。

単位電流の大きさは基準電流回路153が出力する基準電流Icの大きさあるいは強さを調整することにより可変することができる。基準電流Icの調整は、ソースドライバ回路14内に内蔵した電子ボリウム152などで行う。基準電流Icを発生する基準電流回路153はR、G、B回路ごとに設けられている。

RGBの各トランジスタ群165cは単位トランジスタ164の集合で構成されており、単位トランジスタ164の出力電流(単位プログラム電流)の大きさは、基準電流Icの大きさで調整できる。基準電流Icの大きさを調整すれば、RGBごとに各階調のプログラム電流(定電流)Iwの大きさを変更あるいは可変することができる。したがって、RGBの単位トランジスタ164の特性が同一であるような理想的状態では、RGBの基準電流回路153の基準電流Icの大きさの比率を変化させることにより、EL表示装置の表示画像のホワイトバランスをとることができる。

以下、説明を容易にする、また作図を容易にするため、ソースドライバ回路(IC)14のトランジスタ群165cは6ビットであるとして説明をする。図16において、各単位トランジスタ164は、定電流データ(D0〜D5)ごとに配置される。D0ビットには1個の単位トランジスタ164が配置される。D1ビットには2個の単位トランジスタ164が配置される。D2ビットには4個の単位トランジスタ164が配置され、D3ビットには8個の単位トランジスタ164が配置され、D4ビットには16個の単位トランジスタ164が配置される。同様に、D5ビットには32個の単位トランジスタ164が配置されている。

各ビットの単位トランジスタ164の出力電流が出力端子83に出力されるか否かは、アナログスイッチ161(161a〜161f)によるオンオフ制御で実現される。アナログスイッチ161a〜161fは定電流Iwの制御信号の各ビット(一例として6ビット)に対応する。D0ビットに対応するスイッチ161aが閉じると、1単位電流が出力端子83から出力(入力)される。出力端子83には、ソース信号線18が接続されている。同様に、D1ビットに対応するスイッチ161bが閉じると、2単位電流が出力端子83から出力(入力)される。

同様に、D2ビットに対応するスイッチ161cが閉じると、4単位電流が出力端子83から出力(入力)される。D3ビットに対応するスイッチ161dが閉じると、8単位電流が出力端子83から出力(入力)される。D4ビットに対応するスイッチ161eが閉じると、16単位電流が出力端子83から出力(入力)される。D5ビットに対応するスイッチ161fが閉じると、32単位電流が出力端子83から出力(入力)される。

以上のように、定電流の制御信号のビットに対応して、デジタル的にスイッチ161がクローズまたはオープンし、単位電流の総和(プログラム電流Iw)が出力端子83から出力される。

プログラム電流Iwは内部配線162を流れる。内部配線162の電位Vwは、ソース信号線18の電位となる。ソース信号線18の電位は、定電流Iwをソース信号線18に印加し、定常状態した時は、画素16の駆動用トランジスタ11aのゲート端子の電圧(図1の画素構成の場合)である。

単位トランジスタ164はトランジスタ167bとカレントミラー回路を構成している。なお、図15、図16、図17では、理解を容易にするためトランジスタ167bを1つと図示している。実際は、複数のトランジスタ(トランジスタ群)で構成(形成)される。トランジスタ167bとトランジスタ群165cとは所定のカレントミラー比でカレントミラー回路を構成する。

つまり、トランジスタ167bも多数の単位トランジスタ164を有する群として構成されている。ただし、トランジスタ群165cを構成する単位トランジスタ164とトランジスタ167bを構成する単位トランジスタのサイズ、出力電流特性は異ならせてもよいことは言うまでもない。また、トランジスタ167aも複数のトランジスタで形成あるいは構成してもよいことは言うまでもない。なお、単位トランジスタ164を有する定電流出力回路をトランジスタ群165cと呼ぶ。

以上のように、1つの動作を行うトランジスタ(図15、図16、図17などの167b、167a、168a、168b、165b、165c)を、複数の同一特性の単位トランジスタ164からなるトランジスタ群として形成することにより、出力端子83間、ソースドライバ回路14間で特性バラツキが少なくなり、良好な動作を実現できる。

トランジスタ167bには基準電流Icが流れ、この基準電流Icのカレントミラー比に応じた電流が単位トランジスタ164に流れる。図16の63個の単位トランジスタ164はすべて同一の単位電流を出力する。単位トランジスタ164の単位電流が内部配線162に流れるためには、該当のスイッチ161を閉じ、電流経路を構成する必要がある。

図15で説明したように、基準電流Icはオペアンプ151aと抵抗R1からなる定電流発生回路153で発生する。基準電流Icは基準電圧Vsを安定化かつ高精度化することにより安定化させる。電圧ViとVsが抵抗R1の両端に印加される。したがって、基準電流Ic=(Vs−Vi)/R1となる。基準電流IcはRGBごとに設定することができる。つまり、RGBごとにトランジスタ群165cが構成(形成)されている。前記トランジスタ群165cのトランジスタ167bに流れる電流Icを設定(調整)できる。抵抗R1は、ソースドライバ回路(IC)14外に配置されており、抵抗R1の値をRGBで調整することにより、良好にホワイトバランスを調整あるいは設定できる。

図17(a)は基準電流Icを、Vs電圧を用いて発生する回路構成である。図17(b)はGNDとオペアンプ151aの−端子間に配置(挿入)された抵抗R1を用いて基本的な電流を発生させ、トランジスタ292bとトランジスタ167aからなるカレントミラー回路で折り返し、トランジスタ167bに基準電流Icを流す構成である。図17(b)の方が、基準電流のIcの大きさを調整しやすい。しかし、トランジスタ292bとトランジスタ167aからなるカレントミラー回路で折り返すために、出力電流Iwのバラツキが発生しやすい。したがって、図15、図17(a)のように構成することが好ましい。

本発明は図16(a)に図示するように、各ビットに1個または複数の単位トランジスタ164を形成または配置するとした。たとえば、1ビット目は、1個の単位トランジスタを形成し、2ビット目は2個の単位トランジスタを形成する。

しかし、本発明はこれに限定するものではない。たとえば、各ビットに、各ビットに応じた電流を出力する1つの単位トランジスタ164を形成または配置してもよいことは言うまでもない。たとえば、1ビット目のトランジスタは、0ビット目のトランジスタの2倍の電流を出力するトランジスタを1個形成または配置する。2ビット目のトランジスタは、0ビット目のトランジスタの4倍の電流を出力するトランジスタを1個形成または配置する。その他、2ビット目のトランジスタは、1ビット目のトランジスタの2倍の電流を出力するトランジスタを2個形成または配置してもよい。

図16(a)に図示するように、64階調(RGB各6ビット)の場合は、63個の単位トランジスタ164を形成するとした。したがって、256階調(RGB各8ビット)の場合、255個の単位トランジスタ164が必要になることになる。

トランジスタ群165cが出力する電流は、電流の加算ができるという特徴ある効果がある。また、単位トランジスタ164において、チャンネル長Lを一定にし、チャンネル幅Wを1/2にすれば、単位トランジスタ164が流す電流がおよそ1/2になるという特徴ある性質がある。同様に、チャンネル長Lを一定にし、チャンネル幅Wを1/4にすれば、単位トランジスタ164が流す電流がおよそ1/4になるという特徴ある性質がある。実際には、完全には1/nにはならない。しかし、本明細書では説明を容易にするため、チャンネルWを1/nにするとして説明をする。技術的な主旨は、単位トランジスタの単位電流の1/nの電流を出力する単位トランジスタを形成または配置することである。

図18(a)は、各ビットに対して同一のサイズの単位トランジスタ164を配置したトランジスタ群165cの構成である。説明を容易にするため、図18(a)は63個の単位トランジスタ164が構成され、6ビットのトランジスタ群165cを構成(形成)している。また、図18(b)は8ビットであるとする。

図18(b)では、下位2ビット(Aで示す)は、単位トランジスタ164よりも小さいサイズのトランジスタで構成している。最小ビット目の第0ビット目は、単位トランジスタ164のチャンネル幅Wの1/4で形成している(単位トランジスタ164bで示す)。また、第1ビット目は、単位トランジスタ164のチャンネル幅Wの1/2で形成している(単位トランジスタ164aで示す)。なお、単位トランジスタ164aは、単位トランジスタ164のチャンネル幅Wの1/4である単位トランジスタ164bを2個で形成してもよい。

以上の実施例では、単位トランジスタ164bのWは、単位トランジスタ164のWの1/4であるとした。単位トランジスタ164bの出力電流は、単位トランジスタ164の1/4である。単位トランジスタ164のWが6μmであれば、単位トランジスタ164bのWは1/4の1.5μmとなる。しかし、これは理想的な特性を示す場合である。実際には1.5μmより大きくしている。つまり、2.0μmなど大きくしている。一般的にトランジスタが小さな領域では、出力電流とチャンネル幅は比例関係にない。チャンネル幅を理想値の1/4よりも大きくすることにより、単位トランジスタ164bの4倍の電流が単位トランジスタ164の電流と一致するように構成することができる。以上の事項は後にさらに詳しく説明をする。

図19に図示するように、単位トランジスタ164a(図19(b))、トランジスタ164b(図19(b))、トランジスタ164(図19(a))のゲート端子はゲート配線163に接続される。ゲート配線163はトランジスタ167bのゲート端子と接続されている。

下位2ビットは上位の単位トランジスタ164よりも小さいサイズの単位トランジスタ(164a、164b)で形成している。したがって、単位トランジスタ164a、164bは、単位トランジスタ164の1/2、1/4の単位電流を出力することができる。単位トランジスタ164a、164bが占める面積はわずかである。また、正規の単位トランジスタ164の個数は63個で変化がない。したがって、6ビット(64階調)から8ビット(256階調)に変更しても、トランジスタ群165cの形成面積は図18(a)と図18(b)で大差はない。つまり、プログラム電流方式で用いるソースドライバ回路14のチップサイズは階調数にほとんど依存しない。逆に、プログラム電圧方式で用いるソースドライバ回路14は、階調数に大きく依存する。

図18(b)に図示するように、6ビットから8ビット仕様に変化させても、電流プログラム方式のソースドライバ回路14の出力段のトランジスタ群165cのサイズが大きくならないのは、単位電流(1/nの単位電流も含む)の加算によりプログラム電流(定電流)が発生できるという点、単位トランジスタ164において、チャンネル長Lを一定にし、チャンネル幅Wを1/nにすれば、単位トランジスタ164が流す電流がおよそ1/nになるという点をうまく利用しているからである。

また、図18(b)に図示するように、単位トランジスタ164a、164bのようにトランジスタサイズが小さくなると、出力電流(定電流)バラツキも大きくなる。しかし、いかにバラツキが大きくとも、単位トランジスタ164aまたは164bの出力電流は加算される。つまり、階調の逆転は原理的に発生しない。また、出力されるプログラム電流のバラツキは、最大階調時は、6ビットも8ビットも同一である。出力電流のバラツキは、各出力段の単位トランジスタ群が占める面積に依存しているからである。

実際にはチャンネル幅Wを1/nにしても出力電流は正確には1/nにはならない。多少の補正が必要である。チャンネル幅W1/2にすることに大きな意味を持つものではなく、トランジスタ24aの出力電流を単位トランジスタ164の出力電流を1/2にすることに技術的意味がある。したがって、チャンネル幅Wだけでなく、チャンネル長Lを変化させて出力電流を1/2あるいは1/4のように、略整数分の1に構成すれはよい。また、図18(b)で図示した単位トランジスタ164、164a、164bは同一ゲート電圧で動作させる。これは図16に図示するように、内部配線162にすべての単位トランジスタのゲート端子を接続することにより容易に実現できる。また、すべての単位トランジスタ(164、164a、164b)はトランジスタ167bとカレントミラー回路を構成させればよい。

チャンネル幅Wを1/2にすると、トランジスタのゲート端子電圧を同一とした場合、出力電流は、1/2以下となる。そのため、本発明は、下位ビットを構成するトランジスタと、上位ビットを構成するトランジスタのサイズを変化させる場合、以下のようにトランジスタサイズを設定している。

ソースドライバ回路(IC)14の単位トランジスタ164を2種類のサイズのように、少ない形状の種類で構成する。複数の単位トランジスタ164のチャンネル長Lは同一にする。つまり、チャンネル幅Wのみを変化させる。もしくは、チャンネル幅Wまたはチャンネル長Lの一方のみを変化させて単位トランジスタを形成する。好ましくは、トランジスタ群165cを構成する単位トランジスタ164の大きさ、形状は、3種類以下とする。特に、2種類以下とすることが好ましい。

第1の単位トランジスタの第1の単位出力電流と、第2の単位トランジスタの第2の単位出力電流の比をn(第1の単位出力電流:第2の単位出力電流=1:n、ただし、nは1より小さい値)とするとき、第1の単位トランジスタのチャンネル幅W1 < 第2の単位トランジスタのチャンネル幅W2×n×aの関係となるように構成する。

W1×n×a=W2とした場合、1.05< a <1.3の関係が成り立つようにすることが好ましい。補正係数aは、テストトランジスタを形成し、測定あるいは評価することにより補正係数を容易に把握することができる。

本発明は、下位のビットを作製(構成)するために、上位のビットの単位トランジスタ164に比較して小さい単位トランジスタ164を形成または配置するものである。この小さいという概念は、上位ビットを構成する単位トランジスタ164の出力電流よりも小さいという意味である。したがって、単位トランジスタ164に比較してチャンネル幅Wが小さいだけでなく、同時にチャンネル長Lも小さい場合も含まれる。また、他の形状も含まれる。単位トランジスタ164aの出力電流が単位トランジスタ164の1/2とは精度が要求されるものではない。したがって、各ビットでの出力電流が反転しないように、60%〜140%の範囲で設定できればよい。つまり、略1/2、略1/4であればよい。

図18(b)はトランジスタ群165cを構成する単位トランジスタ164のサイズを複数種類とするものであった。図18(b)では3種類(164、164a、164b)としている。種類の数を限定する理由は、先に説明したように、単位トランジスタ164のサイズが異なると出力電流の大きさが形状に比例しないため、設計が難しくなるからである。したがって、トランジスタ群165cを構成する単位トランジスタ164のサイズは低階調用と高階調用の2種類とすることが好ましい。たとえば、図18(b)において、低階調の単位トランジスタである0ビット目の単位トランジスタ164bを2個用いて、1ビット目を構成すればよい。つまり、高階調用の単位トランジスタ164で2ビット目から7ビット目を形成し、低階調の単位トランジスタ164bを用いて0ビット目と1ビット目を形成する。

図16でも図示しているように、トランジスタ群165cを構成する単位トランジスタ164のゲート端子は、1つの内部配線162で接続されている。内部配線162に印加された電圧により単位トランジスタ164の出力電流が決定される。したがって、トランジスタ群165c内の単位トランジスタ164の形状が同一であれば、各単位トランジスタ164は同一の単位電流を出力する。

本発明は、トランジスタ群165cを構成する単位トランジスタ164の内部配線162を共通にすることには限定されない。たとえば、図19(a)のように構成してもよい。なお、トランジスタ群165bとはトランジスタ167bが対応する。つまり、トランジスタ群165cによりトランジスタ167bが構成されている。図19(a)において、トランジスタ群165b1とカレントミラー回路を構成する単位トランジスタ164と、トランジスタ群165b2とカレントミラー回路を構成する単位トランジスタ164とが配置されている。

トランジスタ群165b1は内部配線162aで接続されている。トランジスタ群165b2は内部配線162bで接続されている。図19(a)の一番上の1個の単位トランジスタ164はLSB(0ビット目)であり、2段目の2個の単位トランジスタ164は1ビット目、3段目の4個の単位トランジスタ164は2ビット目である。また、4段目の組の8個の単位トランジスタ164は3ビット目である。

図19(a)において、内部配線162aと内部配線162bの印加電圧を変化させることにより、各単位トランジスタ164のサイズ、形状が同一であっても、各単位トランジスタ164の出力電流を内部配線162の印加電圧により変化(変更)することができる。

図19(a)において、単位トランジスタ164のサイズなどを同一にして、内部配線162a、162bの電圧を異ならせるとしたが、本発明はこれに限定するものではない。単位トランジスタ164のサイズなどを異ならせ、印加する内部配線162a、162bの電圧を調整することにより、異なる形状の単位トランジスタ164の出力電流を同一となるようにしてもよい。

ソースドライバ回路(IC)14の単位トランジスタ164の最小出力電流は0.5nA以上10nAにしている。特に単位トランジスタ164の最小出力電流は2nA以上20nAにすることがよい。ドライバIC14内のトランジスタ群165cを構成する単位トランジスタ164の精度を確保するためである。

また、図20に図示するように、トランジスタ167bを単位トランジスタ164の集合からなるトランジスタ群165bとして形成してもよい。トランジスタ群165bの単位トランジスタのゲート端子はトランジスタ群165cの単位トランジスタ164のゲート端子と共通にされ、カレントミラー回路を構成している。トランジスタ群165bは複数形成することが好ましい。

また、図20に図示するように、トランジスタ167bまたはトランジスタ群165bは、トランジスタ群165cの左右に形成配置することが好ましい。また、トランジスタ群165b、トランジスタ167bには、基準電流発生回路153から基準電流Icを供給する。

本発明のトランジスタ群165cが電流出力であるとして説明するが、これに限定するものではない。たとえば、トランジスタ群165cが電圧出力であってもよい。つまり、ソースドライバ回路(IC)14が液晶表示パネルのように、トランジスタ群165cが電圧を出力し、電圧駆動を実施する場合が例示される。その他、トランジスタ群165cが電圧出力するオペアンプなどで構成してもよい。本発明は、EL表示パネルが電圧駆動である場合も同様に適用される。また、選択回路222、291は、ソースドライバ回路(IC)14がシリコンチップとして構成され、前記チップ14に内蔵されているとして説明するが、これに限定するものではない。たとえば、トランジスタ群165cを、ポリシリコン技術などでガラスアレイ基板30に直接形成してもよい。また、別チップに形成または構成してもよい。

図21に図示するように、ソースドライバ回路(IC)14は、ソース信号線18の電荷を強制的に放出または充電するプリチャージ回路214を内蔵する。プリチャージ回路は、プリチャージ電圧Vpを出力する。プリチャージ電圧Vpとは、Va電圧、V0電圧が該当する。また、プリチャージ電圧Vpの概念には、ソース信号線18の電荷を強制的に放出する電圧と充電する電圧の両方が含まれる。また、プリチャージ電圧Vpの概念には、プログラム電圧も含まれる。つまり、プリチャージ電圧Vpを印加するとは、電圧を印加する動作である。プリチャージ電圧Vpは、基本的にはソース信号線18に印加する。もちろん、画素16の駆動用トランジスタ11aのゲート端子に直接印加してもよい。たとえば、画素電極に圧接したプローブでプリチャージ電圧Vpを印加する方式が例示される。プリチャージ電圧Vpは、R、G、Bで独立に設定できるように構成することが好ましい。EL素子15の閾値がRGBで異なるからである。

プリチャージ電圧Vpの印加とは、ソース信号線18の電荷を充放電させるため、もしくはソース信号線18に所定の電圧にするために用いる方式である。Va、V0電圧を印加すること、水平走査期間の最初に目標階調電圧またはプログラム電圧を印加すること、過電流印加によりソース信号線電位を変化させることも、プリチャージ電圧Vpの印加の概念に含まれる。

図21はプリチャージ回路部の構成図である。プリチャージ電圧Vpは映像データD0〜D5により出力期間範囲が決定される。プリチャージ電圧Vpは、水平走査期間におよびドットクロックCLKに同期して出力される。プリチャージ電圧Vpを出力する時間は、水平同期信号HDを基点としてカウンタ回路212の設定値で決定される。カウンタ回路212はクロックCLK信号に同期してカウントアップされる。プリチャージ電圧Vpの出力期間は、水平走査期間(1H)の最初から開始される。

カウンタ回路212はカウントしたカウント値と設定値が一致すると、プリチャージ電圧Vpの出力期間が終了する。カウンタ回路342の出力はアンド(AND)回路213のa部入力となる。なお、プリチャージ電圧Vpは、オン(印加する)/オフ(印加しない)を切り替えられるように構成する。オン/オフは、ソース信号線18に印加する映像信号もしくは映像信号に対応するプログラム電流またはプログラム電圧の大きさ、あるいは映像信号の変化(前水平走査期間に印加した映像信号との差)映像信号に対応するプログラム電流またはプログラム電圧の大きさ(前水平走査期間で印加したプログラム電流またはプログラム電圧の変化)で決定される。

図21の構成では、どの電圧範囲までプリチャージするかは、一致回路211で決定される。一致回路211には、映像データD0〜D5が印加される。一致回路はプリチャージ範囲が記憶あるいは設定されている。記憶または設定された値よりも、映像データD0〜D5が小さい時、プリチャージ電圧が端子83から出力される。一致回路211はクロックCLKで同期して動作する。また、イネーブル信号ENがHレベルの時、プリチャージ電圧は出力され、Lレベルの時は映像データの値によらず、プリチャージ電圧は出力されない。一致回路211の出力はAND回路213のb端子入力となる。

AND回路213のa部入力がHで、b端子入力がHの時、スイッチ161aが閉じ、プリチャージ電圧Vpが内部配線162に印加され、かつHI信号がHの時、スイッチ161bが閉じて出力端子83からプリチャージ電圧Vpが出力される。

図22は、ソースドライバ回路(IC)14のプリチャージ回路(プリチャージ電圧を出力する回路構成部)を中心とするブロック図である。プリチャージ回路214は、プリチャージ制御回路からプリチャージ制御信号PC信号(赤(RPC)、緑(GPC)、青(BPC))が出力される。

選択(セレクタ)回路222は、メインクロックに同期して出力段に対応するラッチ回路221に順次ラッチしていく。ラッチ回路221はラッチ回路221aとラッチ回路221bの2段構成である。ラッチ回路221bは水平走査クロック(1H)に同期してプリチャージ回路214にデータを送出する。つまり、セレクタは、1画素行分の画像データおよびPCデータを順次ラッチしていき、水平走査クロック(1H)に同期して、ラッチ回路221bでデータをストアする。

なお、図22では、ラッチ回路221のR、G、BはRGBの画像データ6ビットのラッチ回路であり、Pはプリチャージ電圧(RPC、GPC、BPC)の3ビットを保持するラッチ回路である。

プリチャージ回路214は、ラッチ回路221bの出力がHレベルの時、スイッチ161aをオンさせ、ソース信号線18にプリチャージ電圧Vpを出力する。トランジスタ群165cは画像データに応じて、プログラム電流(定電流)をソース信号線18に出力する。

プリチャージ電圧Vpを印加するか否かは、判断前にソース信号線18に印加されている電圧(保持されている電位)に基づいて判断する。判断前にソース信号線18に印加されている電位と、次に印加する電圧(あるいはプログラム電流の印加による想定されるソース信号線18の電位)との電位差あるいは変化量にもとづいて判断する。たとえば、第N(Nは1以上最大画素行以下の整数)画素行の画素に印加した電圧あるいはプログラム電流の印加による変化電位が、4.0(V)で、次に印加する電圧が、4.1(V)と電位差が小さい時は、第N+1画素行の画素にはプリチャージ電圧Vを印加する。逆に2.0(V)と電位差が大きな時は、第N+1画素行の画素にはプリチャージ電圧Vpを印加しない。

本発明は、画素16の駆動用トランジスタ11aがPチャンネルの時にあっては以下の範囲で、プリチャージ電圧Vpの印加の有無を判断する。説明を容易にするため、アノード電圧をVdd、カソード電圧をVssとし、ソースドライバ回路14の電源電圧をVd、ソースドライバ回路14のグランド電位をGNDとする。また、ソース信号線18に保持されている電位(1H前に印加された電圧)をVn、ソースドライバ回路14から出力される電圧(またはプログラム電流の印加により変化する目標電圧)をVmとする。なお、アノードVdd、カソードVss、Vn、VmはGNDに対する電圧値である。また、図4の電位関係を満足させることが好ましい。

画素16の駆動用トランジスタ11aがPチャンネルの時にあっては少なくとも以下の条件の1つ以上が合致する時に、ソース信号線18または画素16にプリチャージ電圧Vpを印加する。

0.5≦(Vdd−Vm)/Vdd≦0.9

0.5≦(Vd−Vm)/Vdd≦0.9

0.1≦|(Vn−Vm)|/Vn ≦0.3 ただし、0.5≦(Vd−Vm)/Vdd

画素16の駆動用トランジスタ11aがNチャンネルの時にあっては少なくとも以下の条件の1つ以上が合致する時に、ソース信号線18または画素16にプリチャージ電圧Vpを印加する。ただし、Vn、Vmは、Vss側の電圧であり、−極性の電圧である。

0.5≦|(Vss−Vm)|/Vss≦0.9

0.5≦|(Vss−Vn)|/Vss≦0.9

0.1≦|(Vn−Vm)|/Vn ≦0.3 ただし、0.5≦(Vss−Vm)/Vss

以上の実施例は、ソース信号線18に保持されている電位または印加する電圧などに基づき、プリチャージ電圧Vpを印加するか否かを判断するとした。しかし、このことは、画素16に印加する映像信号の階調により判断を行っても同様のことを実現できることは言うまでもない。本発明では、最大の階調数をMとし、各ソース信号線18に対して、1H前に印加した映像信号の階調をN1とし、次に印加する映像信号の階調をN2とした時、少なくとも、以下の条件のうち、1つ以上が該当するときに、プリチャージ電圧Vpを印加する。

1≦N2≦M×0.25

1≦|N2−N1|≦8

1画素のデータについてプリチャージするかしないかを判断することに限定するものではない。たとえば、複数画素行の画像データにもとづいてプリチャージ判断をおこなってもよい。また、プリチャージを行う周辺画素の画像データを勘案して(たとえば、重み付け処理など)プリチャージ判断を行っても良い。また、動画と静止画でプリチャージ判断を変化する方法も例示される。以上事項は、画像データに基づき、コントローラがプリチャージ電圧を発生することにより、良好な汎用性が発揮される点が重要である。

本発明は、1画素のデータについてプリチャージするかしないかを判断することに限定するものではない。たとえば、複数画素行の画像データにもとづいてプリチャージ判断を行ってもよい。また、プリチャージを行う周辺画素の画像データを勘案して(たとえば、重み付け処理など)プリチャージ判断を行っても良い。また、動画と静止画でプリチャージ判断を変化する方法も例示される。以上は、画像データに基づき、コントローラがプリチャージ電圧を発生することにより、良好な汎用性が発揮される点が重要である。以降、このプリチャージ判断とプリチャージモードを中心に説明をする。

プリチャージをするかしないかの判定は、1画素行前の画像データ(あるいは、直前にソース信号線に印加された画像データ)にもとづいて行っても良い。たとえば、あるソース信号線18に印加される画像データが白→黒→黒であれば、白から黒になる時は、プリチャージ電圧を印加する。黒階調は書込みにくいからである。黒から黒の場合は、プリチャージ電圧を印加しない。先に黒表示でソース信号線18の電位が次に書き込む黒表示の電位となっているからである。以上の動作は、コントローラ回路(IC)801に1画素行分(FIFOのため2ラインのメモリが必要)のラインメモリを形成(配置)することにより容易に実現できる。

本発明において、プリチャージ駆動では、プリチャージ電圧Vp(Va、V0)を出力するとして説明をするが、これに限定するものではない。1水平走査期間よりも短く、プログラム電流よりも大きい電流をソース信号線18に書き込む方式でもよい。つまり、プリチャージ電流をソース信号線18に書込み、その後にプログラム電流をソース信号線18に書き込む方式でもよい。プリチャージ電流も物理的には電圧変化を引き起こしていることには差異はない。プリチャージをプリチャージ電流で行う方式も本発明のプリチャージ駆動の技術的範疇である(本発明の範囲内である)。

本発明のプリチャージ駆動では所定電圧をソース信号線18に印加する。また、ソースドライバICはプログラム電流を出力するとした。しかし、本発明は、プリチャージ駆動を階調に応じて出力電圧を変化させてもよい。つまり、ソース信号線18に出力するプリチャージ電圧はプログラム電圧になる。ソースドライバIC内にこのプリチャージ電圧の電圧階調回路231を導入した回路構成が図23である。

電圧階調回路231は、プログラム電圧などの階調電圧を出力する構成あるいは動作として説明するが、本発明はこれに限定するものではない。所定の定電圧あるいはプログラム電圧を出力する回路の意味でも用いる。その他、サンプルホールド回路の意味でも用いる。つまり、多段階で電圧値を出力できる回路である。ただし、プリチャージ電圧Vpが固定値の場合は、1つの電圧を出力する構成でよい。この場合も、電圧階調回路231の概念に含まれる。また、電子ボリウム152も外部入力データにより、出力電圧を変化あるいは調整できるから、電圧階調回路である。また、D/A(デジタルーアナログ変換)回路391も電圧階調回路である。

なお、電圧階調回路231は、デジタル信号入力に対応してアナログ電圧を出力するものに限定するものではなく、アナログ電圧をインピーダンス変換あるいは、増幅もしくは低減して出力するものも含まれる。また、広義には、1つの所定電圧あるいは複数の電圧を選択して出力するものも電圧階調回路231である。つまり、電圧階調回路231とは、定電圧発生源として理解してもよい。

図23は主として1つのソース信号線18に対応する1出力回路のブロック図である。階調に応じてプログラム電流を出力する電流階調回路154と、階調に応じたプリチャージ電圧を出力する電圧階調回路231で構成される。電流階調回路154と電圧階調回路231には映像データが印加される。電圧階調回路231の出力はスイッチ161a、161bがオンすることによりソース信号線18に印加される。スイッチ161aはプリチャージイネーブル(プリチャージENBL)信号と、プリチャージ信号(プリチャージSIG)で制御される。

電流階調回路154は、基本的にはプログラム電流などの階調電流を出力するとして説明するが、本発明はこれに限定しない。所定の定電流を出力する回路(定電流出力回路)としての意味でも使用する。また、定電流源の意味でも使用する。階調電流を出力できる回路構成であれば、1μA、0.5μAなどのように、所定値の定電流を出力できるからである。

当然のことながら、電流階調回路154を簡略化し、定電流Iwを出力する定電流回路として構成してもよいことは言うまでもない。また、Va、V0を測定するためには、定電流Iwを印加するだけで十分であり、この機能を達成するためには、階調電流回路154を用いてもよいし、簡略化された定電流回路を用いてもよいことは言うまでもない。また、階調電流は、プログラム電流Iwを定電流と考えてもよい。

電圧階調回路231は、一例としてサンプルホールド回路で構成される。また、必要に応じてD/A変換回路などで構成される。デジタルの映像データに基づいて、D/A変換回路によりプリチャージ電圧に変換される。この変換されたプリチャージ電圧は、サンプルホールド回路241によりサンプルホールドされ、オペアンプを介してスイッチ161aの一端子に印加される。

D/A変換回路は電圧階調回路231ごとに構成または形成する必要がなく、ソースドライバ回路(IC)14の外部にD/A変換回路を構成し、このD/A変換回路の出力を電圧階調回路231内でサンプルホールドしてもよい。また、ポリシリコン技術で形成してもよい。

図24に図示するように、8ビットの映像信号DATAに対応する電圧(プログラム電圧)が、映像クロックに同期して電子ボリウム152から出力される。プログラム電圧は、駆動用トランジスタ11aにプリチャージ電圧として印加される電圧である。また、プログラム電圧は、この電圧を印加することにより、階調にほぼ対応した電流がEL素子15に印加されるように駆動用トランジスタ11aのゲート端子に保持される電圧である。

プログラム電圧はCc容量に一時的に保持され、バッファアンプ151aから出力される。出力された電圧は、サンプルホールド回路(この実施例では切り換え回路のように図示している)241により、各出力端子83に順次振り分けられる(出力端子83a、83b、83c、83d・・・・・、83n、83a、83b、83c、・・・・・・・83n・・・・・・)。振り分けはクロックCLKに同期して実施される。なお、本発明では、8ビットのアドレス信号PADRSにより、任意の端子にプログラム電圧を振り分けできるように構成されている。このように、アドレス信号PADRSにより任意の出力端子83に振り分け(8ビットであるから256本の端子のいずれかに振り分け可能である)できるように構成することにより、プログラム電圧の書き換えが必要な端子のみ新規のプログラム電圧を印加することができる。また、プログラム電圧の振り分けをランダム化することができる。プログラム電圧は容量Cに保持され(サンプリングされ)、バッファ回路151bの出力は、スイッチSpの制御により出力端子83に印加されたり、遮断されたりする。スイッチSpは、図23ではスイッチ161aが該当する。

電流階調回路154は、具体的には図16の回路構成が該当する。電流階調回路154のプログラム電流出力はスイッチSiにより制御される。以上のように、電流階調回路154と電圧階調回路231の出力はスイッチSi、Spにより制御され、プリチャージ駆動(電圧プログラム)+電流プログラミングが実現される。以上の信号は、出力端子83からソース信号線端子242に印加される。プログラム電圧はソース信号線18の寄生容量Caを短期間で充放電させる。

電圧階調回路231の出力であるプリチャージ電圧Vpは、図25に図示するように、1水平走査期間(1H)の最初に印加される(記号Aで示す)。その後、電流階調回路154によりソース信号線にプログラム電流が供給される(記号Bで示す)。つまり、プリチャージ電圧により概略のソース信号線電位まで電圧設定される。したがって、駆動用トランジスタ11aは目的電流に近い値まで、高速に設定される。その後、電流階調回路154が出力するプログラム電流により駆動用トランジスタ11aの特性バラツキを補償する目的電流(=プログラム電流)まで設定される。

プリチャージ電圧が印加されるA期間は、1水平走査期間(1H)の1/100以上1/2以下の期間が好ましい。または、0.2μsec以上40μsec以下の期間に設定することが好ましい。好ましくは1水平走査期間(1H)の1/100以上1/5以下の期間が好ましい。または、0.2μsec以上10μsec以下の期間に設定することが好ましい。したがって、A期間以外がB期間のプログラム電流の印加期間である。A期間が短いとソース信号線18の電荷の充放電が十分に行われないため、書き込み不足が発生する。一方、長すぎると電流印加期間(B)が短くなり十分にプログラム電流を印加することができない。したがって、駆動用トランジスタ11aの電流補正不足となる。

電圧印加期間(A期間)は、1Hの最初から実施することが好ましいが、これに限定されない。たとえば、1Hの終わりのブランキング期間から開始してもよい。また、1H(水平走査期間)の途中にA期間を実施してもよい。つまり、1Hのいずれかの期間に電圧印加期間を実施すれはよい。しかし、好ましくは、電圧印加期間は、1Hの最初から1/4H(=0.25H)の期間内に実施することが好ましい。

図25の実施例では、電圧プリチャージ(A)の期間後、電流を印加(B期間)するとしたがこれに限定するものではない。たとえば、図26(a)に図示するように、1Hの期間のすべてを(あるいは大半を、あるいは過半数を)プリチャージ電圧Vpを印加する期間(電圧プリチャージ(*Aで示す)期間)としてもよい。

図26(a)でも理解できるように、ソース信号線18の電位がアノード電位(Vdd)に近い場合に、1Hの期間のすべてに(大半に)電圧が印加される。ソース信号線18の電位が0(V)に近くなると、電圧プログラム(A期間)と電流プログラム(B)が1Hの期間内に実施される。なお、ソース信号線18の電位が0(V)に近い場合(高階調領域)では、1Hの期間中のすべての期間にわたり、電流プログラムを実施してもよい。

図26(a)の*A以外の期間は、1Hの一定期間(Aで示す)に電圧プログラムによる電圧をソース信号線18に印加し、その後、Bの期間に電流プログラムによる電流を印加している。以上のようにA期間の電圧の印加により画素16のトランジスタ11aのゲート電位に所定電圧を印加し、概略EL素子15に流す電流が所望値になるようにしている。その後、B期間のプログラム電流により、EL素子15に流れる電流が所定値となるようにしている。*A期間は、1H期間の全般にわたり電圧プログラムが実施されている(電圧が印加されている)。

図26(a)は、画素16のトランジスタ11a(駆動用トランジスタ)がPチャンネルの場合のソース信号線18への印加信号波形である。しかし、本発明はこれに限定するものではない。画素16のトランジスタ11aがNチャンネルであってもよい。この場合は、図26(b)に図示するように、ソース信号線18の電位が0(V)に近い場合に、1Hの期間のすべてに(大半に)電圧が印加される。ソース信号線18の電位がアノード電圧(Vdd)に近くなると、電圧プログラム(A期間)と電流プログラム(B)が1Hの期間に実施される。

なお、ソース信号線18の電位がVddに近い場合(高階調領域)では、1Hの期間中のすべての期間にわたり、電流プログラムを実施してもよい。

本発明では、駆動用トランジスタ11aはPチャンネルとして説明するがこれに限定するものではなく、駆動用トランジスタ11aはNチャンネルであってもよいことはいうまでもない。説明を容易にするために、駆動用トランジスタ11aがPチャンネルトランジスタであるとして説明を行うだけである。

本発明の実施例では、主として低階調領域は電圧プログラムが主で画素に書き込みがされる。中高階調領域は、電流プログラムが主で書き込みが行われる。つまり、電流と電圧駆動の両方のよいところの融合を実現できる。なぜなら、低階調領域は、電圧により所定階調表示される。これは、電流駆動では書き込み電流が微小のため、1Hの最初に印加した電圧(電圧駆動あるいはプリチャージ駆動による。プリチャージ駆動と電圧駆動は概念的には同一である。大きく差別化するならば、プリチャージ駆動は印加する電圧に種類が比較的少なく、電圧駆動は印加する電圧の種類が多いと言うべきである)が支配的となるからである。

中階調領域は、電圧により書き込んだ後、電圧のずれ量を、プログラム電流で補償する。つまり、プログラム電流が支配的となる(電流駆動が支配的である)。高階調領域は、プログラム電流で書き込む。プログラム電圧印加は不要である。印加した電圧がプログラム電流で書き換えられるからである。つまり、電流駆動が圧倒的に支配的である。もちろん、電圧を印加してもよいことは言うまでもない。

電圧階調回路の出力と電流階調回路(プリチャージ回路も含む)の出力とを出力端子83でショートして構成することができるのは、電流階調回路は高インピーダンスであることによる。つまり、電流階調回路は高インピーダンスのため、電圧階調回路からの電圧が電流階調回路に印加されても、回路に問題点(短絡で過電流が流れるなど)が発生することがない。

本発明で電圧出力と電流出力状態とを切り換えるとしたがこれに限定するものではない。電流階調回路154からプログラム電流を出力した状態で、スイッチ161(図23を参照のこと)をオンして、電圧階調回路231の電圧を出力端子83に印加してもよいことは言うまでもない。

スイッチ161を閉じて出力端子83に電圧を印加した状態で、電流階調回路154からプログラム電流を出力してもよい。電流階調回路154は高インピーダンスであるので回路的には問題がない。以上の状態も、本発明は電圧駆動状態と電流駆動状態とを切り換えているという動作の範疇である。本発明は電流回路と電圧回路の性質をうまく利用している。このことは、他のドライバ回路にない特徴ある構成である。

図27に図示するように、1H期間に印加するプログラムを電圧またはプログラム電流の一方にしてもよいことは言うまでもない。図27において、Aの期間は電圧プログラムが実施された1H期間であり、Bの期間は電流プログラムが実施されている1H期間である。主として低階調領域では電圧プログラムが実施され(Aで示す)、中間調以上の領域では電流プログラムが実施される(Bで示す)。以上のように、階調あるいはプログラム電流の大きさに応じて、電圧駆動を選択するか電流駆動を選択するかを切り換えても良い。

図23の本発明の実施例では、電圧階調回路231と電流階調回路154には、同一の映像信号DATAが入力されている。したがって、映像信号DATAのラッチ回路は電圧階調回路231と電流階調回路154と共通でよい。つまり、映像信号DATAのラッチ回路は電圧階調回路231と電流階調回路154とに独立に設ける必要はない。共通の映像信号DATAのラッチ回路からのデータに基づき、電流階調回路154または(および)電圧階調回路231がデータを出力端子83に出力する。

図28は本発明の駆動方法のタイミングチャートである。図28において、(a)のDATAは画像データである。(b)のCLKは回路クロックである。(c)のPcntlは、プリチャージのコントロール信号である。Pcntl信号がHレベルの時は、電圧駆動のみモード状態になり、Lレベルの時、電圧+電流駆動モードになる。(d)のPtcはプリチャージ電圧あるいは電圧階調回路231からの出力の切り換え信号である。Ptc信号がHレベルの時は、プリチャージ電圧などの電圧出力がソース信号線18に印加される。Ptc信号がLレベルの時は、電流階調回路154からのプログラム電流がソース信号線に出力される。

たとえば、映像信号データD(2)、D(3)、D(8)の時は、Pcntl信号がHレベルであるから、ソース信号線18に電圧階調回路231から電圧が出力される(A期間)。PcntlがLレベルの時は、ソース信号線18にはまず、電圧が出力され、その後、プログラム電流が出力される。電圧が出力される期間をAで示し、電流が出力される期間をBで示す。電圧を出力する期間Aは、Ptc信号で制御される。Ptc信号は、図23のスイッチ161のオンオフを制御する信号である。

Pcntl信号がHレベルの時は、電圧駆動のみモード状態になり、Lレベルの時、電圧+電流駆動モードになると説明した。電圧を印加する期間は、点灯率あるいは階調に応じて変化させることが好ましい。低階調の時は、電流駆動では画素にプログラム電流を完全に書き込むことができない。したがって、電圧駆動を実施することが好ましい。電圧を印加する期間を長くすることによって、電圧+電流駆動モードであっても、電圧駆動モードが支配的になり、良好に画素に低階調状態を書き込むことができる。低点灯率の場合は、低階調状態の画素が多い。したがって、低階調状態(低点灯率)の場合も、電圧を印加する期間を長くすることによって、電圧+電流駆動モードであっても、電圧駆動モードが支配的になり、良好に画素に低階調状態を書き込むことができる。

以上のように、電圧+電流駆動モードであっても、点灯率あるいは画素に書き込む階調データ(映像データ)に応じて、電圧駆動状態の期間を変化させることが好ましい。つまり、EL素子15に流す電流を小さくするときは(本発明では低点灯率範囲)、電圧駆動モード期間を長くし、EL素子15に流す電流を大きくするときは(本発明では高点灯率範囲)、電圧駆動モード期間を短くするか、もしくは’なし’にするように制御あるいは調整もしくは装置を構成する。

図28において、電圧出力期間Aと電流出力期間Bとを切り換えるとしたが、これに限定するものではない。プログラム電流の出力した状態で、スイッチ161(図23を参照)をオンして、電圧階調回路231の電圧を出力端子83に印加してもよいことは言うまでもない。また、スイッチ161を閉じて出力端子83に電圧を印加した状態で、電流階調回路154からプログラム電流を出力してもよい。A期間後にスイッチ161をオープンにする。以上のように電流階調回路154は高インピーダンスであるので電圧回路と短絡状態にしても回路的には問題がない。

図29は、図23などの電流階調回路154と電圧階調回路231の構成部分をさらに詳細に記載したブロック図である。シフトレジスタ回路(セレクタ回路)222はスタート信号(ST1)、クロック(CLK1)により順次シフト動作する。シフト動作により、第1のラッチ回路(保持回路)221aに、DATA9ビットの保持位置を指定する。DATA9ビットとは、映像信号8ビットとプリチャージ信号1ビットの計9ビットである。ラッチ回路221aは1水平期間に順次DATAを保持していく。

第1のラッチ回路に保持されたDATAは、ロード信号(LD)により2段目の第2のラッチ回路221bにロードされる。ラッチ回路221bに保持されたDATAは、電圧階調回路231の入力と、電流階調回路154の入力となる。プリチャージ信号の1ビットは、電圧階調回路231のプログラム電圧と、電流階調回路154のプログラム電流の切り換え信号である。プリチャージ信号は、切り換え回路(図23のスイッチ161などが該当する)291を時間的に制御し、出力端子83からプリチャージ信号がオンのときはまずプリチャージ電圧を出力し、その後プログラム電流を出力する。

なお、電圧階調回路のサンプルホールド回路は比較的低速でしか動作しないため、電圧階調回路のサンプルホールド用として1段のラッチ回路を追加し、3段のラッチ回路で構成してもよいことは言うまでもない。また、切り換え回路291はアレイ基板30にポリシリコン技術で形成してもよい。

図30はプリチャージ電圧発生回路からの出力(一例としてVpa、Vpb、Vp)をソースドライバ回路14の内部配線で伝達した構成である。配線は、ICチップの長手方向に形成される(各トランジスタ群165と垂直)。プリチャージ電圧Vp(Vpa、Vpb、Vp、open)を伝達するプリチャージ電圧配線PS(PSa、PSb、PSc、PSd)がソース信号線18に直交するように配線される。プリチャージ電圧配線PSと内部配線162とは直交し、各交点にスイッチSpが配置されている。スイッチSpはSEL信号(プリチャージ電圧の選択信号、openを含む)で切り換えられる。openがスイッチSp0aで選択された場合は、プリチャージ電圧は出力されない。スイッチSpは出力端子83ごとに自由に設定できる。スイッチSpは映像信号の大きさ、変化などにより適切なものが選択され制御される。

図29と図30との差異は、図29が映像信号ごとに対応するプリチャージ電圧をサンプルホールドして発生させる構成である。サンプルホールドしたプリチャージ電圧は、出力端子ごとに、プリチャージビット(プリチャージ電圧を印加するか否かの判断ビット)により判断され印加される。図30は複数のプリチャージ電圧を発生させておき、1つのプリチャージ電圧を選択する構成である。選択するプリチャージ電圧は、プリチャージビット(SEL信号:どのプリチャージ電圧を印加するかの指定ビット。ただし、プリチャージ電圧を印加しない(open)場合もある)により判断され、ソース信号線18に印加される。

以上の実施例は、ソースドライバ回路14内にプリチャージ電圧Vp(Va、V0)を形成し、この回路から、必要に応じてソース信号線18にプリチャージ電圧Vpを印加するものであったが、本発明はこれに限定するものではない。たとえば、アレイ基板30にプリチャージ電圧用トランジスタ素子を形成し、このトランジスタ素子をオンオフ制御することにより、プリチャージ電圧線に印加されたプリチャージ電圧Vpをソース信号線18に印加するように構成してもよいことは言うまでもない。

図30などで、オープン機能(openの選択、つまりプリチャージを実施しない)を設けている。しかし、必ずしもソースドライバ回路14内に構成あるいは形成することに限定するものではない。

以上の実施例では、プリチャージ電圧Vp(Va、V0)はアノード電圧Vddに近い電圧(Vdd以下Vdd−3(V))であるとして説明をした、しかし、画素構成によっては、プリチャージ電圧Vpがカソード電圧に近い(Vss以上Vss+3(V))場合がある。たとえば、駆動用トランジスタ11aがNチャンネルトランジスタで形成している場合、駆動用トランジスタ11aが、Pチャンネルトランジスタで吐き出し電流(図1の画素構成は吸い込み(シンク)電流)で電流プログラムが実施される場合である。この場合は、プリチャージ電圧Vpはカソード電圧に近い電圧とする必要がある。

電流駆動で書き込み不足が発生する原因は、図31に図示するようにソース信号線18の寄生容量Csによる影響が大きい。寄生容量Csはゲート信号線17とソース信号線18との交差部などに発生する。

以下の説明は説明を容易にするために、画素16の駆動用トランジスタ11aがPチャンネルトランジスタで、かつ吸い込み(シンク)電流(ソースドライバ回路(IC)14に吸い込む電流)で電流プログラムを実施する場合であるとして説明をする。

なお、画素16の駆動用トランジスタ11aがNチャンネルトランジスタの場合、あるいは駆動用トランジスタ11aを吐き出し(ソース)電流(ソースドライバ回路14から吐き出す電流)で電流プログラムを実施する場合は逆の関係にする。この場合は、ソースドライバ回路14内に形成された単位トランジスタ164は、Pチャンネルトランジスタで形成する。つまり、本発明は吸い込み(シンク)電流の場合を例示して説明するが、吐き出し(ソース)電流の場合は、画素の構成あるいは動作、ソースドライバ回路14の構成あるいは動作を逆の関係に変更あるいは読み変える。このことは当業者であれば容易であるので説明を省略する。

図31(a)に図示するように、黒表示(低階調表示)から白表示(高階調表示)に変化する時は、ソースドライバ回路(IC)14が出力するシンク電流が主体的に関与する。ソースドライバ回路(IC)14がプログラム電流Id1(Iw)で寄生容量Csの電荷を吸い込む。電流を吸い込むことにより、寄生容量Csの電荷を放電し、ソース信号線18の電位が低下する。したがって、画素16の駆動用トランジスタ11aのゲート端子電位が低下し、プログラム電流Iwを流すように電流プログラムが行われる。

白表示(高階調表示)から黒表示(低階調表示)に変化する時は、画素16の駆動用トランジスタ11aの動作が主体である。ソースドライバ回路(IC)14は黒表示の電流を出力するが、微小であるため実効的に動作しない。駆動用トランジスタ11aが動作し、プログラム電流Id2(Iw)の電位に一致するように寄生容量Csを充電する。寄生容量Csに電荷を充電することにより、ソース信号線18の電位が上昇する。したがって、画素16の駆動用トランジスタ11aのゲート端子電位が上昇し、プログラム電流Iwを流すように電流プログラムが行われる。

しかし、図31(a)の駆動は低階調領域では電流Id1が小さく、また、定電流動作のため、寄生容量Csの電荷の放電に非常に長時間を必要とする。特に白輝度に到達するまでの時間が長いため白ウィンドウ表示で上辺の輝度が所定輝度より低い。ソース信号線18の電位が黒表示電位(アノード電圧Vddに近い)から白表示電位(アノード電圧Vdd−3(V)など)へ、1水平走査期間内に変化できないためである。白ウィンドウ部の下辺の次の画素行の黒表示輝度は、比較的目標の黒表示になりやすい。この変化では、図31(b)に図示するように駆動用トランジスタ11aが主体的に変化する。また、図31(b)では駆動用トランジスタ11aが非線形動作するため、比較的電流Id2が大きい。そのため、Csの充電時間が比較的はやい。したがって、白ウィンドウ部の最終白表示画素部の次に位置する黒表示画素行では、輝度が目標の輝度あるいはその近傍に変化する。

プログラム電流の書き込み不足の課題を解決するために、プリチャージ駆動を実施する。しかし、この方法だけでは、パネルが超大型になれば、図31(b)の白から黒表示の実現が困難になる場合がある(プリチャージ電圧Vpにより、ソース信号線18の電位をアノードVdd側に変化させることにより、黒表示を実現することを想定している)。

この対策として、本発明では、1Hの前半にソースドライバ回路(IC)14からのプログラム電流を増加させる。なお、後半は正規のプログラム電流Iwを出力する。ただし、正規のプログラム電流は、図6、図9などの場合はN倍される。つまり、所定条件の時は、1Hの最初に所定のプログラム電流よりも大きな電流をソース信号線18に流し、後半に正規のプログラム電流をソース信号線18に流す。以下この実施例について説明をする。

以下に説明する駆動方法(駆動装置あるいは駆動方式)を過電流駆動と呼ぶ。また、過電流駆動は本発明の他の駆動方式あるいは駆動装置と組み合すことができることは言うまでもない。たとえば、プリチャージ電圧Vpを印加した後、過電流駆動を実施し、その後、プログラム電流を印加(プログラム電流駆動)することが例示される。また、プリチャージ電圧Vpを印加せず、過電流駆動を実施し、その後、プログラム電流駆動を行う方式が例示される。

なお、過電流駆動は、ソース信号線18の電荷を充放電する方式であるから、技術的思想としては、プリチャージ電圧駆動の概念に含まれる。

なお、過電流は、吐き出し電流と吸い込み電流のいずれでもよい。画素16の駆動用トランジスタ11aのチャンネル極性に対応して実施する。画素16の駆動用トランジスタ11aがPチャンネルの場合は、過電流は、ソースドライバ回路14に流れ込む方向(シンク電流)とし、画素16の駆動用トランジスタ11aがNチャンネルの場合は、過電流は、ソースドライバ回路14から吐き出す方向(ソース電流)とする。また、過電流駆動は、すべての画素16に実施するものではなく、画素16に印加された階調値、ソース信号線18の電位、または、次に印加する階調による電位変化などに対応して印加の有無を判断する。また、過電流の大きさ、印加期間を変化させる。

図32は本発明の過電流駆動方式を実現するソースドライバ回路(IC)14の説明図である。図示を容易とするため、単位トランジスタ164が1個の電流回路は単位トランジスタ群321aとし、’1’で図示している。以下同様に、単位トランジスタ164が2個の電流回路(カレントミラー回路)は単位トランジスタ群321bとし、’2’で図示している。また、単位トランジスタ164が4個の電流回路は単位トランジスタ群321cとし、’4’で図示している。単位トランジスタ164が8個の電流回路は単位トランジスタ群321dとし、’8’で図示している。

以下、同様に、単位トランジスタ164が64個の電流回路は単位トランジスタ群321gとし、’64’で図示し、単位トランジスタ164が128個の電流回路は単位トランジスタ群321hとし、’128’で図示している。ただし、図18(b)で説明したように、各単位トランジスタ群321に、物理的に必要な単位トランジスタ164を形成することに限定しない。各単位トランジスタ群321に必要な単位電流を出力するものであればいずれの構成あるいは方式であってもよい。

これらの単位トランジスタ群321(321a〜321h)の1組がトランジスタ群165cである。なお、作図を容易にするため、また、説明を容易にするため単位トランジスタ群321のビット数は各8ビットとしている。したがって、ビット数は、6ビット、10ビットでもよいことは言うまでもない。

また、単位トランジスタ群321は、RGBごとに形成される。ただし、RGBで、形成するビット数を変化させてもよい。たとえば、RとBを6ビットとし、階調が多く必要なGを8ビットにする構成が例示される。また、過電流の大きさについても、RGBで変化あるいは変更できるように構成することが好ましい。たとえば、R、Bで過電流の大きさを大きくし、Gで過電流の大きさを小さくできるようにする構成、方式が例示される。以上の事項は、本発明の他の実施例に適用される。以上の事項は、トランジスタ群165cにも適用される。また、トランジスタ群165bにも適用される。

図32の構成は、過電流のプログラム電流を流す担当のトランジスタ群は、単位トランジスタ群321hとしている。つまり、階調データの最上位ビットのスイッチD7をオンオフ制御することにより、過電流をソース信号線18に流す。過電流を流すことにより寄生容量Csの電荷を短時間で放電させることができる。たとえば、階調5の場合は、スイッチD0とD2をクローズさせて、5単位のプログラム電流を流すが、プログラム電流印加前に、スイッチD7をオンさせて、128単位の電流(過電流)をソース信号線18に印加する。また、過電流の印加前に、必要に応じてあるいは必須的にソース信号線18にプリチャージ電圧Vpを印加する。

最上位ビットを過電流制御(過電流を発生させる)に使用するのは、以下の理由による。まず、説明を容易にするため、1階調から4階調に変化させるとする。また、階調数は256階調(RGB各8ビット)とする。

1階調から白階調に変化させる場合であっても、1階調から中間調以上(たとえば、128階調以上)に変化させる場合は、プログラム電流の書き込み不足は発生しない。プログラム電流が比較的大きく、寄生容量Csの充放電が比較的早いからである。

しかし、1階調から中間調以下(たとえば、127階調以下)に変化する場合は、プログラム電流が小さく、1H期間に寄生容量Csを十分に充放電させることができない。したがって、1階調から4階調などのように、中間調以下に階調変化させることを改善させる必要がある。この場合に、本発明の過電流駆動を実施する。

以上のように変化する階調が中間調以下であるから、プログラム電流の指定に最上位ビットは使用しない。つまり、1階調から変化させる場合、目標の階調は、’01111111’以下である(最上位ビットのスイッチD7は絶えずオフ状態である。本発明はたえず、オフ状態の最上位ビットを制御して過電流駆動を実施する。

最初の階調(変化前の階調)が1であれば、スイッチD0がオンで単位トランジスタ164が1個動作する。目標の階調が4であれば、スイッチD2が動作し、単位トランジスタ164が4個動作する。しかし、単位トランジスタ164が4個では十分に寄生容量Csの電荷を目標値まで放電させることができない。そこで、スイッチD7を閉じ単位トランジスタ群321hを動作させる。

なお、D7スイッチの動作は、D2スイッチの動作に加えて実施してもよいし(1Hの前半あるいは最初にD7とD2スイッチをオンさせ、後半にD2スイッチのみをオンさせる)、1Hの前半あるいは最初にスイッチD7のみをオンさせ、後半にスイッチD2のみをオンさせてもよい。

スイッチD7がオンすれば、単位トランジスタ164が128個動作する(もしくは128個分に相当する単位電流が出力される)。したがって、D2スイッチのみの動作に比較して128/4=32であるから32倍の速度で寄生容量Csの電荷を放電させることができる。したがって、プログラム電流の書き込み改善が可能である。

スイッチD7をオンさせるか否かは、RGBの映像データごとにコントローラ回路(IC)(図示せず)で判断する。コントローラ回路(IC)からは判断ビットKDATAがソースドライバ回路(IC)14に印加される。KDATAは一例として5ビットである。KDATAは、MSBの1ビットと下位4ビットに分けられる。KDATAのMSBが0(Lレベル)の時は、過電流駆動は実施しない。KDATAのMSBが1(Hレベル)の時は過電流駆動を実施する。つまり、過電流駆動を実施し、その後、目的階調に対応するプログラム電流を印加する。

なお、プリチャージ電圧Vpを印加するか否かは、プリチャージビットで設定する。プリチャージビットが0(Lレベル)の時は、プリチャージ電圧Vpを印加しない。プリチャージビットが1(Hレベル)の時は、プリチャージ電圧Vpを印加し、また、KDATAの設定値に対応して過電流駆動を実施し、その後、目的階調に対応するプログラム電流を印加する。

KDATAの下位4ビットは過電流を印加する期間を15段階で示す。この値に基づき、16段階の期間の過電流駆動を実施する。したがって、KDATAの下位4ビットの大きさは、D5ビットをオンさせる時間を示す。

KDATAはラッチ回路221で1H期間保持される。カウンタ回路212はHD(1Hの同期信号)でリセットされ、クロックCLKでカウントされる。カウンタ回路212とラッチ回路221のデータが比較され、カウンタ回路212のカウント値が、ラッチ回路221のデータ値(KDATAの下位4ビット)よりも小さいとき、AND回路213は内部配線162bにオン電圧を出力しつづけ、スイッチD5のオン状態が維持される。したがって、単位トランジスタ群321hの単位トランジスタ164の電流が内部配線162aおよびソース信号線18に流れる。なお、電流プログラム時はスイッチ161bが閉じ、プリチャージ駆動時は、スイッチ161aが閉じ、スイッチ161bがオープン状態となる。

図33はコントローラIC(回路)の動作の説明図である。ただし、1画素列(RGBの組)の処理の説明図である。映像データDATA(8ビット×RGB)は内部クロックに同期してラッチ回路221aと221bに2段ラッチされる。したがって、ラッチ回路221bには、1H前の映像データが保持され、ラッチ回路221aには現在の映像データが保持される。

比較回路331は1H前の映像データと現在の映像データを比較し、KDATAの値を導出する。導出は、過電流駆動を実施するか否かのMSBの1ビットと、過電流を印加する期間である下位4ビットの値である。また、必要に応じて、プリチャージ電圧Vpを印加するか否かのプリチャージビットの設定も行う。また、過電流駆動において必要に応じて、どのスイッチD0〜D7をオン(クローズ)するかを設定してもよい。また、プリチャージ電圧Vpの大きさを設定してもよい。

映像データDATAはソースドライバ回路(IC)14に転送される。また、コントローラIC(回路)はカウンタ回路212の上限カウント値CNTをソースドライバ回路(IC)14に転送する。

KDATAは比較回路331で決定される。決定は、変化前の映像データ(1H前のデータ)と変化後の映像データ(現在のデータ)から決定される。1H前のデータとは、現在のソース信号線18の電位を示す。現在のデータとは、変化させるソース信号線18の目標電位を示す。また、ソース信号線18の電位は、映像データの階調に対応するから、映像データに基づいて決定してもよい。

図31に図示して説明したように、プログラム電流の書き込みは、ソース信号線18の電位を考慮して行うことが重要である。書き込み時間Tは、T=ACV/I(A:比例定数、C:寄生容量の大きさ、V:変化する電位差、I:プログラム電流)で表すことができる。したがって、変化する電位差Vが大きければ書き込み時間が長くなる。一方、プログラム電流I=Iwが大きくすれば書き込み時間は短くなる。

本発明では、過電流駆動でIを大きくする。しかし、いずれの場合でもIを大きくすると、目標のソース信号線18電位を越える場合が発生する。したがって、過電流駆動を実施する場合には、電位差Vを考慮する必要がある。現在のソース信号線18の電位と、次の映像データ(現在の映像データ(次に印加する映像データ=(変化後:図34の縦方向)))から決定される目標のソース信号線18電位から、KDATAを求める。

KDATAはD7スイッチをオンさせる時間の場合もあるが、過電流駆動での電流の大きさでもよい。また、D7スイッチのオン時間(時間が長いほどソース信号線18に印加する過電流印加時間が長くなり、過電流の実効値が大きくなる)と、過電流の大きさ(大きさが大きいほどソース信号線18に印加する過電流の実効値が大きくなる)の両方を組み合わせてもよい。説明を容易にするため、最初、KDATAはD7スイッチのオン時間であるとして説明をする。

比較回路331は1H前と変化後(図34を参照のこと)の映像データを比較してKDATAの大きさを決定する。KDATAに0以外のデータが設定される場合は以下の条件に合致する場合である。

1H前の映像データが低階調領域である場合(0階調以上全階調の1/8以下の領域であることが好ましい。たとえば、256階調の場合は、0階調以上32階調以下である。)で、かつ、変化後の映像データが中間調領域以下である場合(1階調以上全階調の1/2以下の領域であることが好ましい。たとえば、256階調の場合は、1階調以上128階調以下の領域である。)にKDATAを設定する。設定するデータは、駆動用トランジスタ11aのVI特性カーブを考慮して決定する。ソース信号線18のVdd電圧から、0階調目の電圧であるV0(完全黒表示)までの電位差は大きい。また、V0電圧から、1階調目のV1までの電位差は大きい。次の2階調目であるV2電圧とV1電圧までの電位差は、V0電圧からV1電圧までの電位差よりもかなり小さい。以降、V3とV2、V4とV3になるにつれて電位差は小さくなる。以上のように高階調側になるにしたがって、電位差が小さくなるのは、駆動用トランジスタ11aのVI特性が非線形であることにほかならない。

階調間の電位差は、寄生容量Csの電荷の放電量に比例する。したがって、プログラム電流の印加時間つまり、過電流駆動では過電流Idの印加時間と大きさに連動する。たとえば、1H前のV0(階調0)と変化後のV1(階調1)の階調差が小さいからといって、過電流Idの印加時間を短くすることはできない。電位差が大きいからである。

逆に、階調差が大きくとも過電流を大きくする必要がない場合もある。たとえば、階調10と階調32では、階調10の電位V10と階調32の電位V32の電位差も小さく、階調32のプログラム電流Iwも大きいため、寄生容量Csを短時間で充放電できるからである。

図34は、横軸に1H前(変化前、つまり現在のソース信号線18電位を示す)の映像データの階調番号を示している。また、縦軸に現在の映像データの階調番号(変化後、つまり変化させる目標のソース信号線18電位を示す)を示している。

0階調目(1H前)から0階調目(変化後)に変化させるのは、電位変化がないため、KDATAは0でよい。ソース信号線18の電位変化がないからである。0階調目(1H前)から1階調目(変化後)に変化させるのは、V0電位からV1電位に変化させる必要がある。V1−V0電圧は大きいから、KDATAはMSBを1とし、下位4ビットを最高値の15(一例である)に設定する。ソース信号線18の電位変化が大きいからである。1階調目(1H前)から2階調目(変化後)に変化させるのは、V1電位からV2電位に変化させる必要があり、V2−V1電圧は比較的大きいから、KDATAの下位4ビットは最高値近傍の12(一例である)に設定する。ソース信号線18の電位変化が大きいからである。3階調目(1H前)から4階調目(変化後)に変化させるのは、V3電位からV4電位に変化させる必要がある。しかし、V4−V3電圧は比較的小さいため、KDATAの下位4ビットは小さい値の2に設定する。ソース信号線18の電位変化が小さくてすみ、寄生容量Csの充放電が短時間で実施でき、目標のプログラム電流を画素16に書き込むことができるからである。

変化前が低階調領域であっても、変化後の階調が中間調以上の場合は、KDATAのMSB=0とし、下位4ビットの値は0である。変化後の階調に対応するプログラム電流が大きく、1H期間内にソース信号線18の電位を目標電位または近傍の電位まで変化させることができるからである。たとえば、2階調から38階調目に変化させる場合は、KDATA=0である。

変化後が変化前より低階調の場合において、過電流駆動は実施しない。38階調から2階調目に変化させる場合は、KDATAのMSBを0とし、下位4ビット=0である。この場合は、図31(b)が該当し、主として画素16の駆動用トランジスタからプログラム電流Idが寄生容量Csに供給されるからである。図31(b)の場合は、過電流駆動方式は実施せず、電圧+電流駆動方式あるいはプリチャージ電圧駆動を実施することが好ましい。

本発明の過電流駆動方式において、図6、図9などで説明したN倍駆動方式、duty比を制御する駆動方式と組み合わせることは効果がある。また、過電流を印加する時に基準電流を増加させることは効果がある。基準電流の可変は、図15などで説明した電子ボリウム152などで行う。基準電流の増加により、図32などの構成では過電流も増加させることができるからである。したがって、寄生容量Csの充放電時間も短くなる。基準電流の大きさあるいは基準電流比の制御により、過電流駆動方式の過電流の大きさを制御することができる点も本発明の特徴ある構成である。

以上のように、KDATAがコントロールIC(回路)で決定され、KDATAがソースドライバ回路(IC)14に差動信号で伝送される。伝送されたKDATAは図32のラッチ回路221で保持され、D7スイッチが制御される。なお、制御は、スイッチD7だけでなく、スイッチD7、D6を同時に制御してもよい。また、時分割で制御してもよい。つまり、複数のスイッチを過電流印加時に制御を行ってもよい。

図34の表の関係は、マトリックスROMテーブルまたはルックアップテーブル931を用いてKDATAを設定してもよいが、計算式をプログラムし、マイコンあるいはコントローラIC(回路)の乗算器を用いてKDATAの算出(導出)を行ってもよい。また、コントローラIC(回路)で実施することに限定されるものではなく、ソースドライバ回路(IC)14に内蔵のコントロール回路あるいは演算回路で実施してもよいことは言うまでもない。

本発明は、基準電流の大きさによりプログラム電流Iwの大きさが基準電流に比例して変化する。したがって、図32などの過電流駆動の過電流の大きさも基準電流の大きさに比例して変化する。図34で説明したKDATAの大きさも基準電流の大きさの変化に連動させる必要があることは言うまでもない。つまり、KDATAの大きさは、基準電流の大きさに連動させる、あるいは基準電流の大きさを考慮することが好ましい。基準電流が大きければ過電流の大きさが比例して大きくなり、基準電流の大きさが小さければ過電流の大きさも小さくなるからである。

本発明の過電流駆動方式の技術的思想は、プログラム電流の大きさ、駆動用トランジスタ11aからの出力電流などに対応して過電流の大きさ、印加時間(印加期間)、過電流の実効値を設定するものである。また、過電流駆動とプリチャージ駆動とを組み合わせるものである。

比較回路331または比較手段などではRGBの映像データごとに比較を実施するが、RGBデータから輝度(Y値)を求めて、KDATAを算出してもよいことは言うまでもない。つまり、単に、各RGBで比較するのではなく、色度変化、輝度変化を考慮し、また、階調データの連続性、周期性、変化割合を考慮してKDATAを算出あるいは決定もしくは演算する。また、1画素単位でなく、周辺の画素の映像データもしくは映像データに類するデータを考慮してKDATAを導出してもよいことは言うまでもない。たとえば、表示画面34を複数のブロックに分割し、各ブロック内の映像データなどを考慮してKDATAを決定する方式が例示される。

図32などにおいて、過電流駆動時に過電流を流すために選択するスイッチのクローズ期間(たとえば、D7スイッチが選択される時間)は、1H(1水平走査期間)の3/4期間以下1/32期間以上に設定することが好ましい。さらに好ましくは1H(1水平走査期間)の1/2期間以下1/16期間以上に設定することが好ましい。過電流を印加する期間が長いと、正規のプログラム電流を印加する期間が短くなり、電流補償が良好にならない場合がある。また、寄生容量の温度依存性により過電流を印加しすぎとなるからである。逆に過電流の印加期間が短いとソース信号線18の電位変化を目標値に到達させることができなくなり、目標値の電位に対する偏差も大きくなる。

過電流を印加する期間が短いと、目標のソース信号線18の電位まで到達することができない。過電流駆動では、目標の階調のソース信号線18電位まで行うことが好ましいのは言うまでもない。しかし、過電流駆動のみで完全に目標のソース信号線電位にする必要はない。1Hの前半の過電流駆動後に、正規の電流駆動を実施し、過電流駆動により生じた誤差は、正規の電流駆動によるプログラム電流で補償されるからである。したがって、過電流駆動は、ソース信号線18の電位目標値よりも小さめに設定(未到達)することが好ましい。本発明は、過電流駆動での偏差が発生しても、映像信号に対するプログラム電流で補正できることが1つの特徴ある方式である。

図35は、過電流駆動方式を実施した場合の、ソース信号線18の電位変化を図示している。図35(a)は一例としてD7スイッチを1/(2H)期間オン状態にした場合である。1水平走査期間(1H)の最初であるt1よりD7スイッチをオンし、128個分の単位トランジスタ164の単位電流が出力端子83から吸い込まれる。D7スイッチは1/(2H)のt2期間までの間、オン状態が維持され、過電流Id2がソース信号線18に流れる。したがって、ソース信号線18の電位は目標電位のVn電位近傍のVm電位まで低下する。その後(t2後)、D5スイッチはオフ状態となり、正規のプログラム電流Iwが1Hの終了(t3)まで、ソース信号線18に流れて、ソース信号線18電位は目標のVn電位となる。

ソースドライバ回路(IC)14は定電流動作する。したがって、t2〜t3期間には定電流のプログラム電流Iwが流れる。このプログラム電流Iwにより、寄生容量Csが目標電位になるまで充放電されると、画素16の駆動用トランジスタ11aから電流Iが流れ、ソース信号線18の電位は目標プログラム電流Iwが流れるように保持される。したがって、駆動用トランジスタ11aは所定プログラム電流Iwが流れるように保持される。以上のように、過電流駆動の過電流の精度は必要ない。精度がなくとも、画素16の駆動用トランジスタ11aにより補正される。

図35(b)はD7スイッチを1/(4H)期間オン状態にした場合である。1水平走査期間(1H)の最初であるt1よりD7スイッチをオンし、32個分の単位トランジスタ164の単位電流が出力端子83から吸い込まれる。D7スイッチは1/(4H)のt4期間までの間、オン状態が維持され、過電流Id2がソース信号線18に流れる。したがって、ソース信号線18の電位は目標電位のVn電位近傍のVm電位まで低下する。その後(t4後)、D7スイッチはオフ状態となり、正規のプログラム電流Iwが1Hの終了(t3)まで、ソース信号線18に流れて、ソース信号線18電位は目標のVn電位となる。

ソースドライバ回路(IC)14は定電流動作する。したがって、t4〜t3期間には定電流のプログラム電流Iwが流れる。このプログラム電流Iwにより、寄生容量Csが目標電位になるまで充放電されると、画素16の駆動用トランジスタ11aから電流Iが流れ、ソース信号線18の電位は目標プログラム電流Iwが流れるように保持される。したがって、駆動用トランジスタ11aは所定プログラム電流Iwが流れるように保持される。以上のように、過電流駆動の過電流の精度は必要ない。精度がなくとも、画素16の駆動用トランジスタ11aにより補正される。

図35(c)はD7スイッチを1/(8H)期間オン状態にした場合である。1水平走査期間(1H)の最初であるt1よりD7スイッチをオンし、32個分の単位トランジスタ164の単位電流が出力端子83から吸い込まれる。D7スイッチは1/(8H)のt5期間までの間、オン状態が維持され、過電流Id2がソース信号線18に流れる。したがって、ソース信号線18の電位は目標電位のVn電位近傍のVm電位まで低下する。その後(t5後)、D7スイッチはオフ状態となり、正規のプログラム電流Iwが1Hの終了(t3)まで、ソース信号線18に流れて、ソース信号線18電位は目標のVn電位となる。

以上のように、単位トランジスタ164の動作個数と、1つの単位トランジスタ164の単位電流の大きさが固定値である。したがって、D7スイッチのオン時間により、比例して寄生容量Csの充放電時間を操作することができ、ソース信号線18の電位を操作することができる。なお、説明を容易にするため、寄生容量Csを過電流により充放電させるとしているが、画素16のスイッチトランジスタなどのリークもあるから、Csの充放電に限定されるものではない。

以上のように、過電流の大きさが単位トランジスタ164の動作個数により把握できる点が本発明の特徴ある構成である。書き込み時間tは、T=ACV/I(A:比例定数、C:寄生容量の大きさ、V:変化する電位差、I:プログラム電流)で表すことができるから、KDATAも値も、寄生容量(アレイ設計時に把握できる)、駆動用トランジスタ11aのVI特性(アレイ設計時に把握できる)などから理論値にKDATAの値を決定できる。

図32の実施例は、最上位ビットD7スイッチを操作することにより、過電流駆動の過電流Idの大きさ、印加時間を制御するものであった。本発明はこれに限定するものではない。最上位ビット以外のスイッチを操作あるいは制御してもよいことは言うまでもない。

図36は、ソースドライバ回路(IC)14が各RGB8ビット構成である場合において、最上位ビットのスイッチD7と最上位ビットから2番目のスイッチD6をKDATAにより制御した構成である。なお、説明を容易にするため、D7ビットには128個の単位トランジスタ164が形成または配置されているとし、D6ビットには64個の単位トランジスタ164が形成または配置されているとする。

図36(a1)はD7スイッチの動作を示している。図36(a2)はD6スイッチの動作を示している。図36(a3)はソース信号線18の電位変化を示している。図36(a)ではD7、D6のスイッチが同時に動作するため、単位トランジスタ164は128+64個が同時に動作し、出力端子83からソースドライバ回路(IC)14に流れ込む。したがって、階調0のV0電圧から階調3のV3電圧まで高速にソース信号線18電位を変化させることができる。なお、t2後は、正規のスイッチDが閉じ、正規のプログラム電流Iwが出力端子83からソースドライバ回路(IC)14に吸い込まれる。

同様に、図36(b1)はD7スイッチの動作を示している。図36(b2)はD6スイッチの動作を示している。図36(b3)はソース信号線18の電位変化を示している。図36(b)ではD7スイッチのみが動作するため、単位トランジスタ164は128個が同時に動作し、出力端子83からソースドライバ回路(IC)14に流れ込む。したがって、階調0のV0電圧から階調2のV2電圧まで高速にソース信号線18電位を変化させることができる。図36(a)より変化速度は小さい。しかし、変化する電位がV0からV2であるから、適正である。なお、t2後は、正規のスイッチDが閉じ、正規のプログラム電流Iwが出力端子83からソースドライバ回路(IC)14に吸い込まれる。

なお、以上の実施例は、シンク電流の場合である。駆動用トランジスタ11aがNチャンネルの場合は、ソースドライバ回路14の単位トランジスタ164は、Pチャンネルトランジスタで形成される。したがって、単位トランジスタ164からの出力電流(過電流)は、ソース信号線18に吐き出される。

以上のように、本発明は、ソースドライバ回路14がシンク電流動作する場合を例示して説明しているがこれに限定するものではなく、ソース電流(吐き出し電流)の場合も、実施例の必要箇所を読み替えるだけで適用することができるから、本発明の技術的範疇である。

同様に、図36(c1)はD7スイッチの動作を示している。図36(c2)はD6スイッチの動作を示している。図36(c3)はソース信号線18の電位変化を示している。図36(c)ではD6スイッチのみが動作するため、単位トランジスタ164は64個が同時に動作し、出力端子83からソースドライバ回路(IC)14に流れ込む。したがって、階調0のV0電圧から階調1のV1電圧まで高速にソース信号線18電位を変化させることができる。図36(b)より変化速度は小さい。しかし、変化する電位がV0からV1であるから、適正である。なお、t2後は、正規のスイッチDが閉じ、正規のプログラム電流Iwが出力端子83からソースドライバ回路(IC)14に吸い込まれる。

以上のようにKDATAにより、スイッチのオン期間だけでなく、複数のスイッチを操作あるいは動作させ、動作させる単位トランジスタ164の個数あるいは単位電流の大きさを変化あるいは可変もしくは調整することにより、適正なソース信号線電位に設定あるいは変化させることができる。

図36では、過電流駆動によるスイッチD(D6、D7)をt1からt2の期間に動作させるとしたが、これに限定するものではなく、図28に図示あるいは説明したように、t2、t3、t4などのようにKDATAの値によって変化あるいは変更してもよいことは言うまでもない。また、過電流を印加している期間に基準電流あるいは基準電流の大きさを制御あるいは変更し、過電流の大きさを調整してもよい。なお、この場合であっても、正規のプログラム電流を印加している期間は基準電流あるいは基準電流の大きさは正規の値にする。

操作するスイッチはD7、D6に限定するものではなく、D7など他のスイッチも同時にあるいは選択して動作あるいは制御してもよいことは言うまでもない。a期間の例では、過電流駆動として1/(2H)の期間D7スイッチをオン状態にして、128個の単位電流からなる過電流をソース信号線18に印加している。

b期間の例では、過電流駆動として1/(2H)の期間D7、D6スイッチをオン状態にして、128+64個の単位電流からなる過電流をソース信号線18に印加している。

c期間の例では、過電流駆動として1/(2H)の期間D7、D6、D5スイッチをオン状態にして、128+64+32個の単位電流からなる過電流をソース信号線18に印加している。

d期間の例では、過電流駆動として1/(2H)の期間D7、D6、D5スイッチと前記スイッチに該当しない映像データのスイッチ(たとえば、映像データが4であれば、D2スイッチ)をオン状態にして、128+64+32+α個の単位電流からなる過電流をソース信号線18に印加している。

以上の実施例は、図32などで説明したように、スイッチD7などを制御することにより、所定期間に過電流を発生させる方式であった。他に、図15で説明した基準電流Icを変化させることも例示される。つまり、所定期間に、電子ボリウム152を制御することにより、基準電流Icを大きくし、出力端子83から出力されるプログラム電流Iwを大きくする。大きくしたプログラム電流Iwは図32などで説明した過電流とみなせる。したがって、図32などで説明した効果を享受できる。また、以上に説明した所定期間に基準電流を大きくする方式と、図32などで説明した所定期間にスイッチDを制御する方式を組み合わせてもよいことは言うまでもない。また、duty比制御、N倍駆動方式、プリチャージ駆動などと組み合わせてもよいことは言うまでもない。

本発明では、ソースドライバ回路(IC)14内にトランジスタ群165cを有し、このトランジスタ群165cはスイッチDのオンオフにより、階調の対応した単位電流(プログラム電流)を出力できる。したがって、トランジスタ群165cから所定の階調に該当するプログラム電流を出力し、画素16の駆動用トランジスタ11aを動作させることにより、前記画素16の駆動用トランジスタ11aがプログラム電流を流すことができるように設定あるいは調整することができる。

この動作時、図1に図示する画素構成では、トランジスタ11b、11cがクローズ状態であるから、ソース信号線18の電位と、画素16の駆動用トランジスタ11aのゲート端子の電位は同一電位である。したがって、画素16の駆動用トランジスタ11aがプログラム電流Iwを流している時のソース信号線18の電位は、画素16の駆動用トランジスタ11aがプログラム電流Iwを流すのに必要な電位(電圧)ということになる。この電圧をプリチャージ電圧Vpとすると、プリチャージ電圧Vpをソース信号線18に印加すれば、画素16の駆動用トランジスタ11aがプログラム電流Iwを流すことになる。

ソースドライバ回路14からプリチャージ電圧Vpをソース信号線18に印加し、該当画素行のゲート信号線17aにオン電圧を印加することにより選択する。画素16の駆動用トランジスタ11aのゲート端子にプリチャージ電圧Vpが印加され、駆動用トランジスタ11aがプログラム電流Iwを流すようにプログラム(設定)される。したがって、プリチャージ電圧Vpを該当画素16の駆動用トランジスタ11aの特性に合わせて印加すれば、精度よく駆動用トランジスタ11aはプログラム電流Iwにプログラムされる。プリチャージ電圧Vpは電圧であるから、ソース信号線18に寄生容量があっても、順次のソース信号線18の電位を充放電できる。つまり、プリチャージ駆動の利点を享受できる。

本発明では、映像の階調信号に対応するプログラム電流と、定電流をIwと表現している。これは、定電流Iwはソースドライバ回路14から発生させるため発生素子、その構造が一致していること、階調に対応するプログラム電流を所定の設定にした場合が定電流であるためである。

本発明の明細書において、表示画面34において、表示領域63と全表示画面34の割合をduty比と呼ぶ。つまり、duty比は表示領域63の面積/全表示画面34の面積である。あるいは、duty比はオン電圧が印加されているゲート信号線17bの本数/全ゲート信号線17bの本数でもある。また、ゲート信号線17bにオン電圧が印加され、このゲート信号線17bに接続されている選択画素行数/表示画面34の全画素行数でもある。

本明細書において、点灯率に応じてduty比制御などを変化させるとして説明する。しかし、点灯率とは、一定の意味ではない。たとえば、低点灯率とは、表示画面34に流れる電流が小さいことを意味しているが、画像を構成する低階調表示の画素が多いことも意味する。つまり、表示画面34を構成する映像は、暗い画素(低階調の画素)が多い。

したがって、低点灯率とは、画面を構成する映像データのヒストグラム処理をした時、低階調の映像データが多い状態と言い換えることができる。高点灯率とは、表示画面34に流れる電流が大きいことを意味しているが、画像を構成する高階調表示の画素が多いことも意味する。つまり、表示画面34を構成する映像は、明るい画素(高階調の画素)が多い。高点灯率とは、画面を構成する映像データのヒストグラム処理をした時、高階調の映像データが多い状態と言い換えることができる。つまり、点灯率に対応して制御するとは、画素の階調分布状態あるいはヒストグラム分布に対応して制御することと同義あるいは類似の状態を意味することがある。

以上のことから、点灯率にもとづいて制御するとは、場合に応じて画像の階調分布状態(低点灯率=低階調画素が多い。高点灯率=高階調画素が多い。)にもとづいて制御すると言い換えることができる。たとえば、低点灯率になるにしたがって基準電流比を増加させ、高点灯率になるにしたがってduty比を小さくするとは、低階調の画素数が多くなるにしたがって、基準電流比を増加させ、高階調の画素数が多くなるにしたがってduty比を小さくすると言い換えることができる。または、低点灯率になるにしたがって基準電流比を増加させ、高点灯率になるにしたがってduty比を小さくするとは、低階調の画素数が多くなるにしたがって基準電流比を増加させ、高階調の画素数が多くなるにしたがってduty比を小さくするのと同一あるいは類似の意味あるいは動作もしくは制御である。

また、たとえば、所定の低点灯率以下で基準電流比をN倍し、かつ選択信号線数をN本にするとは、低階調の画素数が一定以上の時に、基準電流比をN倍し、かつ選択信号線数をN本にすることと同一あるいは類似の意味あるいは動作もしくは制御である。

また、たとえば、通常は、duty比1/1で駆動し、所定の高点灯率以上で段階的にあるいはスムーズにduty比を低下させるとは、低階調あるいは高階調の画素数が一定の範囲以内の時に、duty比1/1で駆動し、高階調の画素数が一定以上の数となった時に、段階的にあるいはスムーズにduty比を低下させることと同一あるいは類似の意味あるいは動作もしくは制御である。

図37に図示するように、低点灯率領域(図37では点灯率20%以下)でduty比を低下させ(図37(a))、duty比の低下にあわせて、基準電流比を上昇させ(図37(b))てもよい。以上のようにduty比制御と基準電流比制御を同時に行うことにより、図37(c)で図示するように輝度の変化はなくなる。

低点灯率では低階調領域でのプログラム電流の書き込み不足が顕著に目立つ。しかし、図37(a)、(b)に図示するように低点灯率領域で基準電流を増加させることによりプログラム電流を基準電流に比例して増加させることができるので電流の書き込み不足がなくなる。かつ輝度も一定であるから良好な画像表示を実現できる。つまり、低点灯率あるいは所定の点灯率の範囲で基準電流比×duty比が定数の関係となるように制御する。

図37において、点灯率が高い領域(図37では40%以上)では、duty比は低下させるが、基準電流比は1のまま一定とする。したがって、輝度はduty比の低下にともなって低下するから、パネルの消費電力を制御(基本的には少なく)することができる。

基準電流比、duty比と点灯率との関係は以下に説明するように一定の関係を保つことが好ましい。フリッカの発生の増加またはパネルの自己発熱による劣化が加速されるからである。点灯率が30%以下の領域では、duty比×基準電流比(A)が0.7以上1.4以下にすることが好ましい。さらに好ましくは0.8以上1.2以下にすることが好ましい。また、点灯率が80%以下の領域では、duty比×基準電流比(A)が0.1以上0.8以下になるように制御あるいは設定することが好ましい。また、さらに好ましくは0.2以上0.6以下なるように制御あるいは設定することが好ましい。

あるいは、点灯率50%の時のduty比×基準電流比をAとした時、点灯率が30%以下の領域では、duty比×基準電流比×Aが0.7以上1.4以下に設定あるいは制御することが好ましい。さらに好ましくは0.8以上1.2以下に設定あるいは制御することが好ましい。また、点灯率が80%以下の領域では、duty比×基準電流比×Aが0.1以上0.8以下に設定あるいは制御することが好ましい。さらに好ましくは0.2以上0.6以下に設定あるいは制御することが好ましい。

しかし、基準電流の可変は、過電流駆動で課題となる。過電流の大きさが、基準電流の大きさに比例するからである。したがって、図37(b)に図示するように低点灯率の領域で基準電流の大きさを変化させると、この領域での過電流プリチャージの大きさが変化する。具体的には、基準電流比を2倍にすると過電流も2倍となり、目標の階調値に到達する時間が1/2となる。過電流を印加する期間は、固定であるから、基準電流比が大きくなるなど変化すると目標値からずれてしまう。

この課題に対して、図37(d)に図示するように、過電流(プリチャージ電流)の比(プリチャージ電流比と呼ぶ)も、基準電流比および点灯率に対応して変化させる。図37(d)では、基準電流比が点灯率20%以下で2まで変化するため、点灯率20%以下でプログラム電流比を1から1/2まで変化させる。(過電流)プリチャージ電流比×基準電流比が定数(C)となるように設定する。つまり、C=プリチャージ電流比×基準電流比とする。また、基準電流比がn倍になれば、プリチャージ電流比を1/nにする。なお、Cは完全に固定(定数)値とすることに限定されない。多少の変化があっても、表示には反映されないからである。Cの変動幅は、0.8以上1.2以下となるようにする。

なお、図37(d)において、点灯率に対応させて線形に、プリチャージ電流比を変化させるとした。しかし、本発明はこれに限定するものではない。プリチャージ電流比などをステップで変化させてもよい。たとえば、図37の実施例において、点灯率0%以上5%以下は、プリチャージ電流比を2.0とし、点灯率5%以上10%以下は、プリチャージ電流比を1.75とし、点灯率10%以上15%以下は、プリチャージ電流比を1.50とし、点灯率15%以上20%以下は、プリチャージ電流比を1.25Vとし、点灯率20%以上でプリチャージ電流比を1.0と変化させてもよい。

プリチャージ電流比をステップ的に変化させた場合であっても、プリチャージ電流比の変化に対応して基準電流比を変化させる。また、基準電流比、プリチャージ電流比などの変化スピードは、ローパスフィルタ特性(速い点灯率の変化には追従しない)を持たせることが好ましい。また、ヒステリシス特性(一度、変化すると、再び点灯率が元に復帰しても比が変化しない)を持たせることが好ましい。

また、同様のこと(ステップ的に変化させること、ヒステリシス特性を有すること)は、duty比についても適用される。

以上のように、duty比、基準電流比、プリチャージ電流比は、相関の関係に制御する。duty比×基準電流比は定数の関係とする。基準電流比×プリチャージ電流比も定数の関係にする。したがって、duty比×(1/プリチャージ電流比)も定数の関係にする。あるいは略定数の関係にする。

図38の実施例では、プリチャージ電流としての過電流は最上位ビットのD7スイッチをオン(クローズ)させることにより実施している。過電流の大きさは、D7スイッチがクローズする期間によって制御あるいは調整する。

図38の実施例は、階調は階調スイッチ制御回路381で実施する。つまり、8ビットの映像信号に対応して該当のスイッチD0〜D7がオンオフ制御される。一方プリチャージ電流(過電流)は、の基準電流比に対応して、スイッチS0〜S7を制御して出力される。

図38は、8ビットの映像電流信号の1出力段である。映像データD0〜D7はスイッチD*a(*は0〜7で、ビット位置を示す)がクローズすることにより出力端子83から出力される。スイッチD*aは、映像データに応じて該当スイッチがクローズする。一方、スイッチD*b(*は0〜7で、ビット位置を示す)は、電流プリチャージ期間の間クローズする。スイッチD*bのクローズにより、プリチャージ電流(過電流Id)が出力端子83から出力される。

0階調目に相当するオフセット電圧であるプリチャージ電圧V0はスイッチ161aがクローズすることにより出力端子83から出力される。プリチャージ電流Idおよびプログラム電流Iwはスイッチ161bがクローズすることにより出力端子83から出力される。スイッチ161aとスイッチ161bとは同時にクローズしないようにインバータ384により排他的に制御されている。

インバータ384へのロジックデータは、プリチャージ期間判定部383により印加される。つまり、プリチャージ期間判定部383は、電流プリチャージパルスの長さ設定値によりインバータ383を制御する。

実施例では、基準電流比が1から2まで変化する。したがって、プリチャージ電流の大きさ(比率)も、1から1/2に変化させる。たとえば、基準電流比が1の時は、プリチャージ電流制御回路382によりスイッチS7がクローズすると設定されていれば、基準電流比が2に変化した時は、プリチャージ電流制御回路382によりスイッチS6がクローズするように制御される。スイッチS7がクローズ状態でのプリチャージ電流の大きさと、スイッチS6がクローズ状態でのプリチャージ電流の大きさは、2倍差が発生するからである。基準電流比1から2の間のプリチャージ電流の変化はスイッチS0〜S7を制御することによりリニアに調整することができる。

以上のように実施することにより、プリチャージ電流比×基準電流比が定数(C)となるように設定あるいは制御することができる。つまり、C=プリチャージ電流比×基準電流比とする。また、プリチャージ電流の大きさも、プリチャージ電流期間の調整、スイッチSの選択の組み合わせにより調整することができる。

以上のように、図37に図示するように、低点灯率範囲など点灯率に対応させて基準電流を変化させても、同時に点灯率に対応してプリチャージ電流の大きさの相対値を変化させることにより、プリチャージ電流を良好に実現できる。したがって、階調が変化してもプリチャージ電流により良好に目標階調に到達させることができる。

基準電流を大きくすることは、EL素子15に流れる電流の大きさも大きくなる。また、駆動用トランジスタ11aのチャンネル(S−D)間電圧も高くなる。したがって、基準電流比が大きくなれば、アノード電圧(Vdd)とカソード電圧(Vss)間の絶対値を大きくする必要がある。

アノード電圧(Vdd)とカソード電圧(Vss)間の絶対値を大きくすることは、EL表示装置の消費電力が増大することになる。消費電力の増大は発熱を引き起こし、EL表示装置を劣化させる。本発明は、点灯率にあわせて、特に低点灯率の範囲で書き込み不足を解消する点から基準電流を大きくする。したがって、低点灯率領域で、基準電流が大きくなるため、アノード電圧(Vdd)とカソード電圧(Vss)間の絶対値を大きくする必要がある。しかし、従来の電圧発生回路は点灯率によらず、アノード電圧(Vdd)とカソード電圧(Vss)の電圧値は一定であった。そのため、特に、高点灯率の領域で消費電流も増大するため、EL表示装置が発熱するという問題点があった。

この課題に解決するため、図39に図示するように、低点灯率領域でカソード電圧を低下させている。カソード電圧の低下制御は、基準電流の変化に対応して行う。図37の実施例では、点灯率が20%以下で基準電流を増大させている。したがって、図39の実施例でも点灯率20%以下でカソード電圧を低下させている。

図39でアノード電圧を一定にし、基準電流の変化に対応してカソード電圧を変化させているのは、本発明の実施例における画素16の駆動用トランジスタ11aがPチャンネルであるからである。アノード電位を起点として、電流プログラムを行うからである。したがって、アノード電圧を一定値とした方が、電流プログラムの精度が高く維持でき、また、回路構成も容易だからである。また、本発明のEL表示装置は、カソードにEL素子15の一端子が接続されているため、カソード電圧の変化が発生しても表示に影響を与えないからである。しかし、図41に図示するようにアノード電圧を基準電流に対応して変化させてもよい。

以上のように、本発明は、点灯率に応じてEL表示装置の電源電圧を変化させることに特徴がある。特に、基準電流の変化に対応して電源電圧を変化させる。また、点灯率に対応して電源電圧(アノード電圧Vddとカソード電圧Vssのうち、少なくとも一方)を変化させる駆動方式である。また、プリチャージ電流の大きさに対応して電源電圧を変化させる。もしくは、アノード電圧Vddとカソード電圧Vssの絶対値を大きくする。特に、低点灯率の領域において、電源電圧(アノード電圧Vddとカソード電圧Vss)の絶対値を大きくする。

電源電圧の絶対値を大きくする方法は、容易である。通常、電源ICは、パルス制御が行われている。印加される(電源ICの内部で発生する)パルスの周波数が高くなれば、電圧は上昇する。印加される(電源ICの内部で発生するあるいは発振する)パルスの周波数が低くなれば、電圧は低下する。したがって、電源ICのパルス制御を行うことにより、電源ICから出力される電圧の大きさを容易に制御できる。

逆に、基準電流が大きい領域を基準として考えれば、本発明は点灯率に対応して電源電圧(アノード電圧Vddとカソード電圧Vssのうち、少なくとも一方)を低下させる駆動方式である。つまり、高点灯率領域で電源電圧を低下させる。また、プリチャージ電流の大きさに対応して電源電圧を低下させる。もしくは、アノード電圧Vddとカソード電圧Vssの絶対値を大きくする。つまり、プリチャージ電流が小さくなれば、電源電圧を低下させる。特に、高点灯率の領域において、電源電圧(アノード電圧Vddとカソード電圧Vss)の絶対値を小さくする方式である。

図39はアノード電圧とカソード電圧を発生させる2電源方式の実施例である。図41は、カソード側をグランド(GND)とし、アノード電圧を変化させる方式である。図41でも、図39と同様に、点灯率に応じてEL表示装置の電源電圧を変化させることに特徴がある。特に、基準電流の変化に対応して電源電圧を変化させる。また、点灯率に対応して電源電圧(アノード電圧Vdd)を変化させる駆動方式である。また、プリチャージ電流の大きさに対応して電源電圧を変化させる。もしくは、アノード電圧Vddの絶対値を大きくする。特に、低点灯率の領域において、電源電圧(アノード電圧Vdd)の絶対値を大きくする。

図41の単一電源の場合は、図40に図示するように、パルス制御などを実施するロジック信号レベルVccをレベルシフトしてアノード電圧Vddレベルまで上昇させる。オフセットキャンセル電圧V0などのプリチャージ電圧Vpレベルは、アノード電圧Vddを基準となるようにする。この構成により、Vdd電圧が変化してもプリチャージ電圧には影響を与えない。

なお、図39、図40において、点灯率に対応させて線形に、カソード電圧またはアノード電圧を変化させるとした。しかし、本発明はこれに限定するものではない。カソード電圧などをステップで変化させてもよい。たとえば、図39の実施例において、点灯率0%以上5%以下は、カソード電圧を−9Vとし、点灯率5%以上10%以下は、カソード電圧を−8.5Vとし、点灯率10%以上15%以下は、カソード電圧を−8.0Vとし、点灯率15%以上20%以下は、カソード電圧を−6.5Vとし、点灯率20%以上で−5.5Vと変化させてもよい。

また、カソード電圧とアノード電圧は同時に変化させてもよい。また、カソード電圧とアノード電圧との絶対値を変化させるように制御してもよいことはいうまでもない。

カソード電圧の変化は、電源ICの外付け抵抗の分圧比で調整する。したがって、スイッチ回路により複数の抵抗を切り替え、選択することにより、抵抗値はステップ的に変更あるいは変化させることができる。また、他ステップを有する電子ボリウムなどを用いることにより、点灯率に対してほぼリニアに変化させることができる。

また、カソード電圧値、アノード電圧値などの電圧の変化スピードは、ローパスフィルタ特性(速い点灯率の変化には追従しない)を持たせることが好ましい。また、ヒステリシス特性(一度、カソード電圧値、アノード電圧値が変化すると、再び点灯率が元に復帰しても電圧値が変化しない)を持たせることが好ましい。

本発明の実施例において、ソース信号線18などに定電流を流す、あるいは、ソース信号線18をハイインピーダンス状態に保持してV1、V0電圧などを測定するとした。測定した電圧は、EEPROMや、ROMなどに電圧データ(あるいは電流データ)として保持される。あるいはソースドライバ回路14などに保持される。しかし、すべての電圧データなどを保持すると非常に膨大なデータ量となる。そのため、圧縮技術を用いてROMなどに保持させてもよい。

たとえば、JPEGなどの静止画圧縮技術あるいはフォーマットが例示される。とくに、トランジスタ11aの特性分布はランダムではなく、周辺部の特性と近似している。そのため、画像データの圧縮技術を用いることにより良好な圧縮を実施することができる。また、MPEGなどの動画圧縮技術などを用いてもよいことはいうまでもない。以上の事項は本発明の他の実施例にも適用できることは言うまでもない。

図6、図6などの実施例では、ゲートドライバ回路12aとゲートドライバ回路12bは、水平同期信号に同期して動作するとした。そのため、点灯、非点灯の制御は、1画素行単位(1水平走査期間)であった。

図42の実施例は、点灯、非点灯制御を1水平走査期間以内で実施できる実施例である。ゲートドライバ回路12aのシフトレジスタ回路31aは、水平走査期間信号(水平同期信号)に同期してデータ位置をシフトする。

ゲート信号線17bを選択するゲートドライバ回路12bのシフトレジスタ回路31bは、ゲートドライバ回路12aのシフトレジスタ回路31aの4倍の段数を有している。ゲートドライバ回路12bのシフトレジスタ回路31bは、シフトレジスタ回路31aの4倍の動作クロック(CLK4)でデータをシフトする。

つまり、シフトレジスタ回路31aが1データシフトする期間に、シフトレジスタ回路31bは、4データをシフトする。以上の構成により、1水平走査期間の1/4単位で画素行の点灯、非点灯制御を実現できる。

図43にさらに、シフトレジスタ回路31bの段数と、ゲート信号線17bの接続された位置を示したものである。シフトレジスタ回路31bの出力は4段ごとにゲート信号線17bのロジック出力として出力される。

隣接したシフトレジスタ回路31bの段数を低減するため、また、各段のデータの変化を緩和するためには、図44のように構成するとよい。

図44において、×はゲート信号線17を非選択(オフ電圧を出力する)にするデータであることを、○はゲート信号線17を選択(オン電圧を出力する)にするデータであることを示している。なお、AND回路213の出力にはレベル変換回路が構成されるが説明を容易にするため省略している。

シフトレジスタ回路31bの隣接した各段のデータ出力は、AND回路213でAND(積和)する。また、垂直方向のアウトプットイネーブル(OEV)端子により、ゲート信号線17bの選択を強制的に非選択とするように構成されている。

以上の構成によりシフトレジスタ回路31bの隣接した段の2つが、選択”○”の時、該当のゲート信号線17bから選択電圧(VGL)が出力される。

図45は、シフトレジスタ回路31bの隣接した2つの段数のデータが選択の時で、かつ2つの段数が独立してロジック制御できるように構成した実施例である。隣接した段の2つが、選択”○”の時、該当のゲート信号線17bから選択電圧(VGL)が出力される。

以上の実施例は、シフトレジスタ回路31bの出力にAND回路213を形成した実施例であった。しかし、本発明はこれに限定するものではなく、図46に図示するように、OR回路951を形成してもよい。

また、シフトレジスタ回路31をシフトレジスタ回路31aとシフトレジスタ回路31bの2段で構成し、さらにOEV端子を形成し、シフトレジスタ回路31aとシフトレジスタ回路31bとOEV端子のロジックとをANDすることにより、ゲート信号線17bの選択、非選択を柔軟に実施することができる。このロジック信号の組み合わせ例を図47に示す。

以上のように、図42などの本発明の構成は、ゲートドライバ回路12bのシフトレジスタ回路31bの段数を、ゲートドライバ回路12aのシフトレジスタ回路31aの段数のm倍(mは2以上の整数)とし、また、ゲートドライバ回路12bのシフトレジスタ回路31bの動作クロックを、ゲートドライバ回路12aのシフトレジスタ回路31aの動作クロックのm倍(mは2以上の整数)とすることにより、1水平走査期間以下の点灯制御を実施できるように構成したもの、あるいは方式である。この構成により、輝度制御をフリッカレスでスムーズに行うことができる。

図6などで説明したように、本発明は、主として表示領域63または非表示領域62を帯状にし、画面34を上下または逆に移動させた表示する方式であった。しかし、本発明はこれに限定するものではない。図49に図示するように、画面34を上下に分割し、画像表示をおこなってもよい。

図49(a)は、1フレームの前半の(1/2)フレームの表示状態である。図49(b)は、1フレームの後半の(1/2)フレームの表示状態である。1フレームの前半では、画面34の上半分は非表示領域62(該当領域のゲート信号線17bに選択電圧(VGL)が印加されていない)となっている。上半分の領域では、ゲートドライバ回路12aによりゲート信号線17aに選択電圧が順次印加されている。

図49(b)は、1フレームの後半の(1/2)フレームの表示状態である。1フレームの後半では、画面34の下半分は非表示領域62(該当領域のゲート信号線17bに選択電圧(VGL)が印加されていない)となっている。下半分の領域では、ゲートドライバ回路12aによりゲート信号線17aに選択電圧が順次印加されている。

理解を容易にするため、具体的数値を記載して説明する。画素行を240とする。したがって、上半分の領域とは、1画素行目から120画素行目が該当する。下半分の領域とは、121画素行目から240画素行目が該当する。ゲートドライバ回路12aは、ゲート信号線17aを順次選択し、1フレーム期間で、1画素行目から240画素行目を順次選択し、ソースドライバ回路14のプログラム電流(電圧)を順次画素16に印加する。ゲートドライバ回路12bは、図51に図示するように、画面34の上半分を駆動するゲートドライバ回路12b1と画面34の下半分を駆動するゲートドライバ回路12b2が構成されている。ゲートドライバ回路12b1、ゲートドライバ回路12b2は、それぞれ内部にシフトレジスタ回路31を有し、データをシフトすることにより、任意のゲート信号線17bのオン電圧またはオフ電圧を印加することができる。しかし、図49の実施例では、OEV端子制御を行う。

OEV1端子は、端子にロジックレベルのLを入力することにより、ゲートドライバ回路12b1の全ゲート信号線17bにオフ電圧が出力される。したがって、画面34の上半分が非表示領域62となる。また、OEV1端子にロジックレベルのHを入力することにより、ゲートドライバ回路12b1の全ゲート信号線17bにオン電圧が出力される。したがって、画面34の上半分が表示領域63となる。

OEV2端子は、端子にロジックレベルのLを入力することにより、ゲートドライバ回路12b2の全ゲート信号線17bにオフ電圧が出力される。したがって、画面34の下半分が非表示領域62となる(図49(b))。また、OEV2端子にロジックレベルのHを入力することにより、ゲートドライバ回路12b2の全ゲート信号線17bにオン電圧が出力される。したがって、画面34の下半分が表示領域63となる(図49(a))。

ゲートドライバ回路12aが、画面34の1画素行目から120画素行目を書き換えている期間は、図49(a)の状態に制御される。つまり、OEV1端子にLロジック信号が印加され、ゲートドライバ回路12b1が受け持つゲート信号線17bにはオフ電圧が印加される。また、OEV2端子にHロジック信号が印加され、ゲートドライバ回路12b2が受け持つゲート信号線17bにはオン電圧が印加される。

ゲートドライバ回路12aが、画面34の121画素行目から24画素行目を書き換えている期間は、図49(b)の状態に制御される。つまり、OEV1端子にHロジック信号が印加され、ゲートドライバ回路12b1が受け持つゲート信号線17bにはオン電圧が印加される。また、OEV2端子にLロジック信号が印加され、ゲートドライバ回路12b2が受け持つゲート信号線17bにはオフ電圧が印加される。

図50は、2フレーム期間の画像表示状態を図示している。画面34の上半分とした下半分とが交互に表示される。以上のように表示制御することにより、動画視認性が大幅に向上する。また、ゲートドライバ回路12bにシフトレジスタ回路31を形成する必要がなく、回路構成を簡略化できる。また、狭額縁化が可能である。

以上の実施例は、画面34を上下に2分割にする構成であった。しかし、本発明はこれに限定するものではなく、たとえば、図52に図示するように、画面を4分割してもよい。この実施例の場合は、ゲートドライバ回路12bをゲートドライバ回路12b1、ゲートドライバ回路12b2、ゲートドライバ回路12b3、ゲートドライバ回路12b4に構成し、各ゲートドライバ回路12bにOEV端子(OEV1、OEV2、OEV3、OEV4)を配置すればよい。ゲートドライバ回路12aの動作は図51と同様に画面の上方から下方に向かって順次走査する。

さらに、図57に図示するように、表示領域34を細分化して制御をおこってもよい。図76は1画素行ごとに、表示領域63と非表示領域62の制御を行ったものである。

以上の実施例は、フレームを2分割し、表示領域63と非表示領域62を交互に実施するものであった。しかし、本発明はこれに限定するものではない。たとえば、1フレームを4つの期間に分割し、表示領域63と非表示領域62を交互に実施してもよい。

以上のように、本発明は、1フレーム期間を複数の時間に分割し、また、表示領域を複数に分割して表示領域63、非表示領域62の制御を実施するものである。

なお、本発明は、図49などの画面34を分割する方式に限定するものではない。たとえば、図53に図示するように、実施してもよい。図53は1フレーム期間の駆動方式の説明図である。

図53において、図53(a)((a1)、(a2)、(a3)、(a4))は、ゲートドライバ回路12aによる画像の書き込み位置(矢印で示している)を示している。ゲートドライバ回路12aは、図49などと同様に画面の1画素行目から240画素行目に順次ゲート信号線17aを選択し、ソースドライバ回路14からの映像信号を画素行に書き込む。

図53(b)((b1)、(b2)、(b3)、(b4))は、ゲートドライバ回路12bによる表示領域63、非表示領域62の制御状態を示している。ゲートドライバ回路12bは、画面34全体をOEV端子の制御により、点灯あるいは非点灯状態に制御する。

ゲートドライバ回路12aの画像書き込みは、(1/2)フレーム期間で完了する。つまり、倍速書き込みを行う。その期間は、ゲートドライバ回路12bのOEV端子は、Lロジックが印加され、すべてのゲート信号線17bにはオフ電圧が印加される。1フレームの後半の1/2フレーム期間では、ゲートドライバ回路12aの書き込み動作は停止する。この期間は、ゲートドライバ回路12bのOEV端子にはHロジック信号が印加され、すべてのゲート信号線17bにはオン電圧が印加される。したがって、1フレームの(1/2)フレーム期間では画面34は非点灯状態(非表示)であり、後半の(1/2)フレーム期間では画面34は点灯状態(表示)である。なお、画像の表示時間、非表示期間は、(1/2)フレームに限定するものではない。ゲートドライバ回路12aの書き込みクロック、ゲートドライバ回路12bのOEV端子の制御により自由に設定あるいは調整できる。

図49の実施例は、画面34を2分割した実施例であった。また、図52は画面を4分割し、そのうち、複数の領域を表示領域63とする実施例であった。また、図52は、画面34の画像を書き換えてから画面34を表示状態にする実施例であった。本発明は、以上の実施例に限定されるものではなく、多くの変形例が考えられる。

図58は、画面34を3以上の複数(実施例では4)分割する実施例である。また、画像を書き換えている領域のみを非表示領域62をするものである。

図58において、画像を書き換えている画素行(書き込み位置と図示している)を含む領域を非表示領域62としている。他の領域は表示領域63(画像表示状態の領域)と制御している。書き込み位置は、画面34の上から下方向に順次書き換えられる。書き込み位置の移動にしたがって、書き込み位置を含む領域は非表示領域62に制御される。

非表示領域62と表示領域63の切り換えは、ゲートドライバ回路12bに入力するスタートパルス(ST信号)の制御によって行っても良いが、図58に図示するようにOEV端子による制御で行っても良い。ゲートドライバ回路12bのOEV端子に、Lロジックを入力することにより該当領域は非表示領域62となる。OEV端子に、Hロジック信号を入力することにより該当領域が表示領域63となる。

図59に図示するように、EL素子15に流す電流をオンオフ制御するゲート信号線17bを直接に制御する方法も例示される。図59では、画面34を複数のブロックに分割し、各ブロックのゲート信号線17bを選択信号線591で共通にしている。ゲートドライバ回路12aは、各ブロック(分割された画面34)で共通である。つまり、ゲート信号線17aは、1画素行または隣接した複数の画素行が順次選択される。

選択信号線591aは第1のブロックのゲート信号線17bと接続されている。選択信号線591bは第1のブロックのゲート信号線17bと接続されている。選択信号線591aにオフ電圧VGHを印加することにより、第1のブロックは非表示領域62となる。選択信号線591aにオン電圧VGLを印加することにより、第1のブロックは表示領域63となる。選択信号線591bにオフ電圧VGHを印加することにより、第1のブロックは非表示領域62となる。選択信号線591bにオン電圧VGLを印加することにより、第1のブロックは表示領域63となる。以上のように、選択信号線591にオン電圧またはオフ電圧を印加することにより、画面34をブロックごとに表示、非表示制御を容易に実現できる。

なお、以上の実施例は、ブロック内の隣接したゲート信号線17bを選択信号線591で電気的に共通にするとしたが、本発明はこれに限定するものではない。たとえば、隣接した画素行のゲート信号線17bを、異なる選択信号線591と電気的に接続してのよい。たとえば、図76の構成あるいは方式が例示される。

以上のように画面34の表示を制御することにより動画視認性が向上し、CRTと同等の画像表示を実現できる。

以上の実施例は、本明細書の他の実施例と組み合わせることができることは言うまでもない。また、本実施例を本発明の装置などに適用できることも言うまでもない。

図3、図6、図9、図11、図42などの実施例では、ゲートドライバ12aの動作周波数とゲートドライバ12bの動作周波数とは一致させるとした。もしくは、画素16行を選択するゲート信号線12aと、EL素子15の行を選択するゲート信号線17bとは同期させ、選択画素16行とEL素子15の行とは一定間隔を保持し、選択するとした。

しかし、本発明はこれに限定するものではない。たとえば、図48に図示するように、ゲートドライバ回路12aとゲートドライバ回路12bの動作周波数あるいは選択周波数を異ならせても良い。図48の実施例では、ゲートドライバ回路12aを60Hz周期で動作させ、ゲートドライバ回路12bを1.5倍の75Hz周期で動作させた実施例である。

周期とは、m(mは1以上画素行n以下の整数)番目のゲート信号線12を選択し、次にm番目のゲート信号線12を選択する時間である。たとえば、ゲートドライバ回路12aの60Hz周期とは、1秒間に1番目の画素行のゲート信号線12aを選択する回数が60回である。つまり、それぞれのゲート信号線12aが選択され、次に選択されるまでを1周期とし、1秒間におけるその周期が60回発生するのが60Hzである。ゲートドライバ回路12bの75Hz周期とは、1秒間に1番目の画素行のゲート信号線12aを選択する回数が75回である。

図48の実施例では、ゲートドライバ回路12aは、入力映像信号の周波数60Hz(1秒間に画像が60枚)に同期して画面34を書き換える。つまり、ゲートドライバ回路12aは、水平走査同期信号に同期して表示領域34の1番目の画素行からn(nは画素行の最大値)番目の画素行を順次選択し、ソースドライバ回路14からのプログラム電流(電圧)を選択された画素行に印加する。この書き換えの回数が1秒間に60回である。

ゲートドライバ回路12bは、ゲートドライバ回路12aの水平走査同期信号とは異なる同期信号に同期して表示領域34の1番目の画素行からn(nは画素行の最大値)番目の画素行を順次選択する。このゲートドライバ回路12bが使用する同期信号を点灯制御同期信号と呼ぶ。点灯制御同期信号は、メインクロックから発生させる。ただし、水平走査同期信号もメインクロックから発生させているため、点灯制御同期信号と水平走査同期信号とは同期がとれている。

ゲートドライバ回路12bは、点灯制御同期信号に同期してゲート信号線17bを選択し、ゲート信号線17bのオンオフ制御を行う。ゲートドライバ回路12bは、点灯制御同期信号に同期して表示領域34の1番目の画素行からn(nは画素行の最大値)番目の画素行のゲート信号線17bを順次選択し、EL素子15の発光制御を実施する。m(mは1以上n以下の整数)番目のゲート信号線17bが選択され、つぎにm番目のゲート信号線17bが選択される期間を1周期とし、この周期の回数が1秒間に75回実施される(75Hz動作のとき)。

図6などで説明したように、黒挿入(非表示領域の挿入)あるいは表示領域を間欠にして駆動することにより、動画視認性が大幅に向上する。しかし、帯状の表示領域63の周期が遅いとフリッカが発生する。この課題に対して本発明は、ゲートドライバ回路12bの動作速度(周期=フレームレート)を入力映像信号のフレームレート(通常60フレーム/秒=60Hz)よりも速くする。

本発明のEL表示装置は、図1でも説明したように、映像信号は画素16のコンデンサ19で保持されている。つまり、表示領域の画像メモリを保有するのと等価である。コンデンサ19で保持された画像は、トランジスタ11dをオンさせることによりEL素子15に電流が流れ、画像表示される。したがって、ゲート信号線17bを制御するだけで画像表示を実現できる。

なお、ゲート信号線17bにオン電圧を印加することにより、EL素子15に電流が流れるとして説明するが、駆動トランジスタ11aにプログラムされた映像信号が、黒表示であれば、EL素子15には電流は流れない。本明細書において、EL素子15に電流が流れるとは、映像信号などに応じてEL素子15に流れる電流が制御される意味である場合がある。

表示領域34に画像メモリが有すると言うことは、この画像メモリを用いてフレームレート変換を実現できる。たとえば、入力映像信号のフレームレート(周期)が60Hzであれば、フレームレート=60Hzで表示領域34にマトリックス状に形成されたコンデンサ19に画像を書き込み、保持させる。読み出しは、ゲートドライバ回路12bを操作することにより読み出せる。読み出しとはEL素子15に電流を流し、画像表示を行うことである。

ゲートドライバ回路12bがゲート信号線17bを選択する周期(フレームレート)はゲートドライバ回路12aと独立に行えるから、フレームレート変換を実現できる。つまり、ゲートドライバ回路12bのフレームレート(動作周期)を75Hzとすれば、図6の表示領域63が画面34の上下方向に移動する動作を1秒間に75回実施できる。

液晶表示装置では、フレームレート変換を行うには、外付けの半導体メモリが必要である。また、フレームレート変換にはメモリの読み出し速度を高速に行う必要がある。しかし、本発明のEL表示装置では半導体メモリは不要であり、低コスト化を実現できる。

図48の技術的思想としては、EL素子15行を選択し、EL素子15行を発光させる周期を60Hz以上とすることが重要である。好ましくは、周期は70Hz以上150Hz以下とする。さらに好ましくは、72Hz以上130Hz以下とする。

また、好ましくは、ゲートドライバ回路12bの1周期動作する周波数は、ゲートドライバ回路12bの動作周波数の1.25倍、1.5倍、1.75倍、2.0倍の周波数をする。たとえば、ゲートドライバ回路12aが1画面34を書き換える周期が60Hzであれば、ゲートドライバ回路12bが1画面34を選択する周期は、75Hz、90Hz、105Hz、120Hzとする。ゲートドライバ回路12aが1画面34を書き換える周期が50Hzであれば、ゲートドライバ回路12bが1画面34を選択する周期は、62.5Hz、75Hz、87.5Hz、100Hzとする。

なお、以上の1.25倍、1.5倍などの倍数は、この数値のみに限定されるものではない。回路の構成上、前後してもその効果は有効である。したがって、上記に例示する倍数の±10%の範囲であれば問題ない。以上の事項は以下の実施例においても同様に適用される。

また、ゲート信号線17bの1番目が選択され、次にゲート信号線17bの1番目が選択される周期は、周期は70Hz以上150Hz以下とする。さらに好ましくは、72Hz以上130Hz以下とすることが好ましい。

また、ゲート信号線17bの1番目が選択され次にゲート信号線17bの1番目が選択される周期は、ゲート信号線17aの1番目が選択され次にゲート信号線17aの1番目が選択される周期の1.25倍、1.5倍、1.75倍、2.0倍の周波数をすることが好ましい。

以下、本発明の駆動方法の動作について、図77を参照しながら説明をする。図77において、縦軸は、画素行番号である。画素行は、n画素行あるとする。したがって、ゲートドライバ回路12が選択する画素行は1番目からn番目の画素行である。横軸は、時間である。フレームとも考えることができる。なお、説明を容易にするため、画素行の選択は、画面34の上辺の1画素行から開始されるものとする。また、図77では、ゲートドライバ回路12bは、フレームレート(周期)は入力の60Hz×2=120Hzとしている。また、画素構成は、図1の画素構成を例示して説明をする。

図77において、実線は、ゲートドライバ回路12aの動作を示している。つまり、ゲートドライバ回路12aがシフト動作し、オン電圧(VGL)を出力するゲート信号線17aの位置を示している。ゲートドライバ回路12aは、60Hzの1フレーム(1F)で1画素行からn画素行を選択する。ゲートドライバ回路12bは、120Hzで動作する。したがって、ゲートドライバ回路12aの1Fで2回画面34を選択する。つまり、(1/2)Fで、1番目の画素行からn番目の画素行を選択する。なお、ゲートドライバ回路12bは、duty駆動では、複数の画素行を選択する。図77では理解を容易にするため、点線をゲートドライバ回路12bが動作の先端位置とする。たとえば、1画素行しかゲート信号線17bを選択しない状態において、そのゲート信号線17bにオン電圧(VGL)が印加されている画素行の位置である。

図77において、Aからゲートドライバ回路12による画素行の選択が行われる。説明を容易にするため、また、理解を容易にするため、ゲートドライバ回路12bが1画素行目を選択し、次の走査期間でゲートドライバ回路12aが1画素行目を選択するとする。つまり、ゲート信号線12aが選択するゲート信号線17aとゲートドライバ回路12bが選択するゲート信号線17bが同一の画素行とならないように制御を開始する。

ゲートドライバ回路12aによりゲート信号線17aが順次選択され、ソースドライバ回路14からプログラム電流が出力されて選択された画素行に書き込まれる。1Fで画面34の下辺であるn画素行(C点)まで走査が完了し、次のフレームではまた画面34の上辺の1画素行目からゲート信号線17aの選択が開始される。

また、ゲートドライバ回路12bによりゲート信号線17bが順次選択され、ゲート信号線17bにオン電圧(VGL)またはオフ電圧(VGH)が印加され、その印加位置が、点灯制御同期信号に同期してシフトされる。ゲートドライバ回路12bの動作フレームレートは120Hzであるから、B点で1フレームが完了し、このフレーム期間は、ゲートドライバ回路12aの(1/2)F期間である。