本発明は、無線通信により情報信号の送受信を行う半導体装置に関する。特に薄膜トランジスタで形成される半導体装置に関する。

近年、超小型化したICチップと、無線通信用のアンテナを備えた半導体装置(以下「半導体装置」、「ICタグ」ともいう)が注目されている。この半導体装置は、リーダ/ライタと呼ばれる無線通信装置を介して情報の送受信を非接触で行う。

無線通信により情報の送受信を行う半導体装置の応用分野として、流通業界における商品管理が知られている。現在はバーコードを利用した商品管理システムが普及しているが、バーコードは光学的に読み取るため、曲面に付した場合や印刷面が汚れているときはデータが上手く読み取れない場合がある。一方、リーダ/ライタと呼ばれる無線通信装置を用いて非接触で情報の送受信を行う方式では、商品の形態に依存せずに読み取りを行うことができる。そのため、商品管理の効率化、低コスト化などが期待されている。その他、乗車券、航空旅客券、料金の自動精算など、広範な応用が期待されている(特許文献1参照)。このように、微小な半導体装置により人やモノを識別、管理する仕組みはRFID(Radio Frequency Identification)と呼ばれ、IT化社会の基盤技術として注目が高まっている。

特開2000−149194号公報

RFIDにおける通信規格としては、例えば、ISO/IEC 15693などが規定されている。ISO/IEC 15693によると、通信信号における搬送波の周波数として13.56MHz±7kHzを用い、リーダ/ライタから半導体装置へのデータの伝送は、ASK(Amplitude Shift Keying 振幅変位キーイング)方式を用いる。

図5に、ASK方式における半導体装置へのデータ伝送時の通信信号を示す。図5において、通信信号101は、搬送波の周波数で振動する電磁波である。通信信号101により伝送されるデータは、通信信号101の振幅の包絡線102によって表される。通信信号101の振幅が最大の場合を”1”、最小の場合を”0”とする。半導体装置は、このような通信信号101より、”0”及び”1”を受信する。

また、ISO/IEC 15693によると、半導体装置の動作に必要な電源電圧は、通信信号101より電磁誘導などの方法を用いて供給される。したがって、無線通信を利用して動作する半導体装置において、大規模な演算回路を動作させるためには、通信信号より大電流を供給し得る大規模なアンテナや大規模の電源回路が必要となり、チップ面積大、高価格化などを招く恐れがある。また、データ伝送にASK方式を用いるため、”0”を受信している際は、電源電圧の供給が不安定になりやすい。つまり、電磁誘導により供給される電源電圧も変動するため、半導体装置の低消費電力化の要求が益々厳しくなる。

このような状況に鑑み本発明は、無線通信を利用して動作する半導体装置の低消費電力化と高性能化を図ることを目的とする。

本発明は、演算回路、状態制御レジスタ及び通信回路を含む半導体装置である。状態制御レジスタは、受信処理状態、演算処理状態、送信状態のいずれかで半導体装置が動作するように制御する。受信回路は、リーダ/ライタからの通信信号より、受信データの開始(SOF = Start Of Frame)を示すデータ、受信データ、受信データの終了(EOF = End Of Frame)を示すデータを識別して抽出する。EOF信号を示すデータ抽出した場合、状態制御レジスタを演算処理状態に変化させる。演算処理状態の場合は、演算回路が動作する。演算処理回路は、受信回路が通信信号から抽出した受信データに従って演算処理を行う。演算処理が終了した場合、状態制御レジスタを送信処理状態に変化させる。送信処理状態の場合は、送信回路のみ動作する。送信回路は、送信データの開始(SOF信号)を示すデータと、送信データと、送信データの終了(EOF信号)を示すデータと、からリーダ/ライタへの通信信号を生成する。

以上のような構成にすることで、ASK方式を用いたデータのデータ伝送時、すなわち、通信信号の振幅が変動する場合には、消費電力の大きい演算回路の動作を停止し、受信又は送信に最低限必要な回路のみ動作させることを可能とする。また、通信信号の振幅が変動しない場合にのみ、演算回路を動作させることを可能とする。

本発明によれば、データ伝送にASK方式を用いる場合にも大規模な電源回路を必要とせずに、高機能な半導体装置を実現できる。それにより、演算処理回路を大規模化することが可能であり、高性能且つ低消費電力の半導体装置を提供することができる。

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

(実施の形態1)

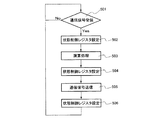

本実施の形態では、演算回路を特定の機能を実現するための専用回路とした構成を図1及び図2を参照して説明する。図1は本実施の形態に係る半導体装置のハードウェア構成であり、図2は本実施の形態に係る半導体装置における処理のフローチャートである。

図1において、半導体装置201は、演算回路202、状態制御レジスタ203、受信回路204、送信回路205、アンテナ206、共振回路207、電源回路208、リセット回路209、クロック回路210、復調回路211、変調回路212、受信信号213、送信信号214を有する。なお、図1では、説明の簡単化のため、受信信号213と、送信信号214とを別の信号として示したが、実際には、両者は重ね合わされており、半導体装置201及びリーダ/ライタの間で同時に送受信される。

図1において、通信信号(動作磁界)により形成される磁界中に半導体装置201を置くと、アンテナ206と共振回路207により誘導起電力を生じる。この誘導起電力により、半導体装置201の動作に必要な電源電圧を生成する。誘導起電力は電源回路208における電気容量により保持され、また電気容量によって電位が安定化される。リセット回路209は半導体装置201全体を初期状態とするシステムリセット信号215を生成する。システムリセット信号215はクロック信号の一種であり、例えば電源電圧の立ち上がりに対し、一定の時間遅れて立ち上がる信号をシステムリセット信号215とすることができる。クロック回路210は通信信号からクロック信号を生成する。例えば通信信号を半波整流した後、インバーター回路を通すことで、通信信号と同周期のクロック信号が生成される。このクロック信号を半導体装置201におけるシステムクロック信号216としても良いが、さらに分周しシステムクロック信号216としてもよい。復調回路211は、ASK方式の受信信号213の振幅の変動を”0”又は”1”の信号として検出する。例えばローパスフィルターとする。変調回路212は、送信データをASK方式の送信信号214の振幅を変動させて送信する。例えば、送信データが”0”の場合、共振回路207の共振点を変化させ、通信信号の振幅を変化させる。

状態制御レジスタ203は、受信処理状態と、演算処理状態と、送信処理状態と、のいずれかの状態であることを示すことができる。また、状態制御レジスタ203を変更することで、各状態間を遷移することができる。具体的には、状態制御レジスタ203における特定のビットを、受信処理状態フラグ、演算処理状態フラグ、送信処理状態フラグとし、各状態フラグが”1”の場合に各々の状態であるとし、各フラグを変更する。

受信処理状態の場合は受信回路204が動作し、演算回路202及び送信回路205は停止する。また、演算処理状態の場合は演算回路202が動作し、受信回路204及び送信回路205は停止する。さらに、送信処理状態の場合は送信回路205が動作し、受信回路204及び演算回路202は停止する。

以上のような状態制御において、クロック信号の供給を停止するには、受信処理状態フラグが”1”の場合に受信回路204に供給するクロック信号のイネーブル信号217を”1”とする。そして、演算処理状態フラグが”1”の場合に演算回路202のリセット信号を”0”及び演算回路202に供給するクロック信号のイネーブル信号218を”1”とする。さらに、送信処理状態フラグが”1”の場合に送信回路205に供給するクロック信号のイネーブル信号219を”1”とすることで実現できる。

具体的には、システムクロック信号216とイネーブル信号217との論理積を受信回路204に供給するクロック信号とする。そして、システムクロック信号216とイネーブル信号218との論理積を演算回路202に供給するクロック信号とする。さらに、システムクロック信号216とイネーブル信号219との論理積を送信回路205に供給するクロック信号とすることで実現できる。

次に、図17に示すタイミングチャートを用いて、状態制御に係わる信号の説明をする。第1の信号1701は、図1におけるシステムクロック信号216である。第2の信号1702は、図1における演算回路202のリセット信号である。第3の信号1703は、図1における状態制御レジスタ203の受信処理状態フラグである。第4の信号1704は、図1における状態制御レジスタ203の演算処理状態フラグである。また、第5の信号1705は、図1における状態制御レジスタ203の送信処理状態フラグである。

図17において、第3の信号1703が”1”の期間は、受信処理状態の期間1712である。第4の信号1704が”1”の期間は、演算処理状態の期間1713である。第5の信号1705が”1”の期間は、送信処理状態の期間1714である。

受信処理状態の期間1712では、図1の受信回路204に供給するクロック信号のイネーブル信号217は”1”であり、図17の第6の信号1706(イネーブル信号217)のようになる。ここで、受信回路204に供給するクロック信号は、システムクロック信号216とイネーブル信号217との論理積なので、図17の第7の信号1707のようになる。

演算処理状態の期間1713では、図1の演算回路202のリセット信号は”0”であり、図17において第2の信号1702として表されている。演算回路202に供給するクロック信号のイネーブル信号218は”1”であり、図17において第8の信号1708(イネーブル信号218)のようになる。ここで、演算回路202に供給するクロック信号は、システムクロック信号216とイネーブル信号218との論理積なので、図17の第9の信号1709のようになる。

送信処理状態の期間1714では、図1の送信回路205に供給するクロック信号のイネーブル信号219は”1”であり、図17の第10の信号1710(イネーブル信号219)のようになる。ここで、送信回路205に供給するクロック信号は、システムクロック信号216とイネーブル信号219との論理積なので、図17の第11の信号1711のようになる。

演算処理状態の場合は、演算回路202に供給する電源電圧を供給しない構成とすると、消費電力を低減できるので好適である。具体的には、演算回路202における電源線を他の回路における電源線とは独立した電源線とし、演算回路202の電源線と電源回路208との電気的接続を遮断すれば良い。

なお、状態制御レジスタ203は、伝送データを保存する機能も有することが望ましい。この場合は、半導体装置201が信号を送受信中は電源電圧が供給されていなくてはならない。具体的には、状態制御レジスタ203における電源線を他の回路における電源線とは独立した電源線とし、半導体装置201が信号を送受信中は、状態制御レジスタ203と電源回路208の電気的接続を接続してあれば良い。

以下、図2のフローチャートと対応させながら説明する。受信回路204は、復調回路211により復調された信号より、SOF信号と、受信データと、EOF信号とを識別して抽出する(通信信号受信301)。EOF信号を抽出した場合、状態制御レジスタ203を演算処理状態に変化させる(状態制御レジスタ設定302)。状態制御レジスタ203を演算処理状態に変化させるには、演算処理状態フラグを1に書き換える手段を有していれば良い。

演算回路202は、例えば暗号化されたデータの送受信において復号化/暗号化の処理を行う専用回路である。演算処理状態フラグが1の場合、受信回路が送信信号から抽出した受信データに従って演算処理を行う(演算処理303)。また、演算処理が終了した場合、状態制御レジスタを送信処理状態に変化させる(状態制御レジスタ設定304)。状態制御レジスタを送信処理状態に変化させるには、送信状態フラグを”1”に書き換える手段を有していれば良い。

送信回路205は、送信データを通信信号の形式に沿って加工し、変調回路212に出力する(通信信号送信305)。送信が終了次第、状態制御レジスタを受信処理状態に変化させる(状態制御レジスタ設定306)。状態制御レジスタを受信処理状態に変化させるには、受信状態フラグを”1”に書き換える手段を有していれば良い。

以上のような形態とすることで、通信信号からの誘導起電力により電源電圧を供給し、ASK方式により通信データを送受信する半導体装置において、データの送受信時、すなわち動作磁界が変動する場合に消費電力の大きい演算回路の動作を停止し、動作磁界が変動しない場合に演算回路を動作させることができる。一方、動作磁界が変動する場合に、受信又は送信に最低限必要な機能を受信回路もしくは送信回路で実現することで大容量電源を必要としない。つまり、高度な演算処理を小規模な電源回路で実行することが可能である。このようにして、大規模回路を搭載した半導体装置に好適な構成で、高性能且つ低消費電力の半導体装置を提供できる。

また、本実施の形態における半導体装置を、ガラス基板、石英基板、プラスチック基板などの絶縁表面を有する基板上に形成された半導体薄膜を活性層として用いた薄膜トランジスタから構成することで、高性能且つ低消費電力の半導体装置を、より軽量で安価に提供することができる。

(実施の形態2)

本実施の形態では、演算回路を、CPUとメモリとし、ソフトウェアにより演算処理を行う構成を、図3及び図4を用いて説明する。図3は、本実施の形態における半導体装置のハードウェア構成であり、図4は、本実施の形態における半導体装置における処理のフローチャートである。

図3において、半導体装置201は、演算回路202、状態制御レジスタ203、受信回路204、送信回路205、アンテナ206、共振回路207、電源回路208、リセット回路209、クロック回路210、復調回路211、変調回路212、受信信号213、送信信号214を有する。演算回路202は、CPU401(Central Processing Unit:中央処理装置)、RAM402(Random Access Memory:ランダムアクセスが可能な読み出しと書き込みができるメモリ)、ROM403(Read Only Memory:読み出し専用メモリ)、CPUインターフェース404(CPU InterFace:CPUインターフェース)を有する。なお、図3では、説明の簡単化のため、受信信号213と、送信信号214とを別の信号として示したが、実際には、両者は重ね合わされており、半導体装置201及びリーダ/ライタの間で同時に送受信される。

図3において、通信信号により形成される磁界中に半導体装置201を置くと、アンテナ206と共振回路207により、誘導起電力を生じる。この誘導起電力により、半導体装置201における電源電圧を供給することができる。誘導起電力は、電源回路208における電気容量により保持され、また電気容量によって電位が安定化される。リセット回路209は半導体装置201全体を初期状態とするシステムリセット信号215を生成する。例えばシステムリセット信号215のため、電源電圧の立ち上がりに対して一定の時間遅れて立ち上がる信号を生成する。クロック回路210は、通信信号からクロック信号を生成する。例えば、通信信号を半波整流した後、インバータ回路を通すことで、通信信号と同周期のクロック信号が生成される。このクロック信号をさらに分周し、半導体装置201におけるクロック信号としてもよい。復調回路211は、ASK方式の受信信号213の振幅の変動を”0”及び”1”の信号として検出する。例えばローパスフィルターとする。変調回路212は、送信データをASK方式の送信信号214の振幅を変動させて送信する。例えば、送信データが”0”の場合、共振回路207の共振点を変化させ、通信信号の振幅を変化させる。

状態制御レジスタ203は、受信処理状態と、演算処理状態と、送信処理状態と、のいずれかの状態であることを示す。また、状態制御レジスタ203を変更することで、各状態間を遷移することができる。具体的には、状態制御レジスタにおける特定のビットを、受信処理状態フラグ、演算処理状態フラグ、送信処理状態フラグとし、各状態フラグが”1”の場合に各々の状態であるとし、各フラグを変更する。

受信処理状態の場合は、受信回路204が動作し、CPU401、RAM402、ROM403、CPUインターフェース404、送信回路205は停止する。また、演算処理状態の場合は、CPU401、RAM402、ROM403、CPUインターフェース404が動作し、受信回路204及び送信回路205は停止する。さらに、送信処理状態の場合は、送信回路205が動作し、受信回路204、CPU401、RAM402、ROM403、CPUインターフェース404は停止する。

以上のような状態制御において、クロック信号の供給を停止するには、受信処理状態フラグを、受信回路204に供給するクロック信号のイネーブル信号として用いる。そして、演算処理状態フラグを、CPU401、RAM402、ROM403、CPUインターフェース404のリセット信号405,及びCPU401、RAM402、ROM403、CPUインターフェース404に供給するクロック信号のイネーブル信号として用いる。さらに、送信処理状態フラグを送信回路205に供給するクロック信号のイネーブル信号とすることで実現できる。

このような状態制御は、受信処理状態フラグが”1”の場合に受信回路204に供給するクロック信号のイネーブル信号217を”1”とする。そして、演算処理状態フラグが”1”の場合にCPU401、RAM402、ROM403、CPUインターフェース404のリセット信号405を”0”及びCPU401、RAM402、ROM403、CPUインターフェース404に供給するクロック信号のイネーブル信号218を”1”とする。そして、送信処理状態フラグが”1”の場合に送信回路205に供給するクロック信号のイネーブル信号219を”1”とすることができる。

より具体的には、システムクロック信号216とイネーブル信号217との論理積を受信回路204に供給するクロック信号とする。そして、システムクロック信号216とイネーブル信号218との論理積をCPU401、RAM402、ROM403、CPUインターフェース404に供給するクロック信号とする。さらに、システムクロック信号216とイネーブル信号219との論理積を送信回路205に供給するクロック信号とすることで実現できる。

次に、図17に示すタイミングチャートを用いて、状態制御に係わる信号の説明をする。第1の信号1701は、図3におけるシステムクロック信号216である。第2の信号1702は、図3におけるCPU401、RAM402、ROM403、CPUインターフェース404のリセット信号である。第3の信号1703は、図3における状態制御レジスタ203の受信処理状態フラグである。第4の信号1704は、図3における状態制御レジスタ203の演算処理状態フラグである。第5の信号1705は、図3における状態制御レジスタ203の送信処理状態フラグである。

図17において、第3の信号1703が”1”の期間は、受信処理状態の期間1712である。第4の信号1704が”1”の期間は、演算処理状態の期間1713である。第5の信号1705が”1”の期間は、送信処理状態の期間1714である。

受信処理状態の期間1712では、図3の受信回路204に供給するクロック信号のイネーブル信号は”1”であり、図17の第6の信号1706(イネーブル信号217)のようになる。ここで、受信回路204に供給するクロック信号は、システムクロック信号216とイネーブル信号217との論理積なので、図17の第7の信号1707のようになる。

演算処理状態の期間1713では、図3のCPU401、RAM402、ROM403、CPUインターフェース404のリセット信号は”0”及びCPU401、RAM402、ROM403、CPUインターフェース404に供給するクロック信号のイネーブル信号218は”1”であり、各々図17の第2の信号1702、第8の信号1708(イネーブル信号218)のようになる。ここで、CPU401、RAM402、ROM403、CPUインターフェース404に供給するクロック信号は、システムクロック信号216とイネーブル信号218との論理積なので、図17の第9の信号1709のようになる。

送信処理状態の期間1714では、図3の送信回路205に供給するクロック信号のイネーブル信号219は”1”であり、図17の第10の信号1710(イネーブル信号219)のようになる。ここで、送信回路205に供給するクロック信号は、システムクロック信号216とイネーブル信号219との論理積なので、図17の第11の信号1711のようになる。

演算処理状態の場合は、演算回路202に供給する電源電圧を供給しない構成とすると、消費電力を低減できるので好適である。具体的には、演算回路202における電源線を他の回路における電源線とは独立した電源線とし、演算回路202の電源線と電源回路208との電気的接続を遮断すれば良い。

なお、状態制御レジスタ203は、伝送データを保存する機能も有することが望ましい。この場合は、半導体装置201が信号を送受信中は電源電圧が供給されていなくてはならない。具体的には、状態制御レジスタ203における電源線を他の回路における電源線とは独立した電源線とし、半導体装置201が信号を送受信中は、状態制御レジスタ203と電源回路208の電気的接続を接続してあれば良い。

また、受信処理状態及び送信処理状態の場合は、CPU401、RAM402、ROM403、CPUインターフェース404に供給する電源電圧を停止しても良い。この場合、演算処理状態に遷移した際に、状態制御レジスタ203の演算処理状態フラグが”1”となり、さらに電源電圧が規定値以上に達した後にクロック信号のイネーブル信号を有効化し、続いてリセット信号を解除するとCPU401の動作を安定化できる。。

以下、図4のフローチャートと対応させながら説明する。受信回路204は、復調回路により復調された信号より、SOF信号と、受信データと、EOF信号と、を識別して抽出する(通信信号受信501)。EOF信号を抽出した場合、状態制御レジスタ203を演算処理状態に変化させる(状態制御レジスタ設定502)。具体的には、演算処理状態フラグを”1”に書き換える手段を有していれば良い。

演算処理状態フラグが”1”の場合に、受信回路204が送信信号から抽出した受信データに従って、CPU401は、演算処理を行う(演算処理503)。具体的な演算処理としては、例えば暗号化されたデータの送受信において復号化/暗号化の処理を行う。さらに、復号化したデータの内容に従って、あらかじめ決められた内容の演算処理を行っても良い。これらの処理内容は、ROM403にあらかじめプログラムを格納することで自由に変えられる。演算処理の作業用メモリとしてRAM402を用いると良い。RAM402、ROM403、状態制御レジスタ203は、CPU401のアドレス空間上に存在する構成とすると好適である。この際、CPUインターフェース404は、CPU401が発行したアドレスが、RAM402、ROM403もしくは状態制御レジスタ203のいずれに相当するか識別する機能を有する。

なお、演算処理が終了した場合CPU401は、状態制御レジスタを送信処理状態に変化させる(状態制御レジスタ設定504)。状態制御レジスタを送信処理状態に変化させるには、送信状態フラグを”1”に書き換える手段を有していれば良い。この手段も、ROM403にあらかじめ格納されたプログラムをCPU401が実行することで実現することができる。

送信回路205は、送信データを、通信信号の形式に沿って加工し、変調回路212に出力する(通信信号送信505)。送信が終了次第、状態制御レジスタを受信処理状態に変化させる(状態制御レジスタ設定506)。状態制御レジスタを受信処理状態に変化させるには、受信状態フラグを”1”に書き換える手段を有していれば良い。

以上のような形態とすることで、通信信号からの誘導起電力により電源電圧を供給し、ASK方式により通信データを送受信する半導体装置において、データの送受信時、すなわち、動作磁界が変動する場合に、消費電力の大きいCPUやメモリの動作を停止し、動作磁界が変動しない場合に、CPUやメモリを動作させることができる。一方、動作磁界が変動する場合に、受信又は送信に最低限必要な機能を受信回路もしくは送信回路で実現することで、大容量電源を必要としない。つまり、高度な演算処理を小規模な電源回路で実行することが可能である。このようにして、大規模回路を搭載した半導体装置に好適な構成で、高性能化と低消費電力化を両立させることができる。

また、本実施の形態における半導体装置を、ガラス基板、石英基板、プラスチック基板などの絶縁表面を有する基板上に形成された半導体薄膜を活性層として用いた薄膜トランジスタから構成することで、高性能且つ低消費電力の半導体装置を、より軽量で安価に提供することができる。

(実施の形態3)

本実施の形態は、実施の形態1及び実施の形態2を併用した構成である。すなわち、本発明における半導体装置において、専用回路とCPUとメモリとで演算回路を構成し、演算処理の一部を専用回路でハードウェア的に処理し、残りの演算処理のプログラムをCPUでソフトウェア的に処理する構成である。

専用回路では、並列に実行できる演算や、繰り返し実行する演算を行うことが望ましい。一方、CPUでは、より複雑な演算を行うことが望ましい。実用的には、演算速度、消費電力、チップ面積、開発資産などを考慮し、適宜最適な構成を選択すれば良い。

なお、本実施の形態に関する他の詳細は、実施の形態1及び実施の形態2に示した説明から容易に推測できるので割愛する。

以上のような形態とすることで、大規模回路を搭載した半導体装置に好適な構成で、高性能且つ低消費電力の半導体装置を提供できる。

また、本実施の形態における半導体装置を、ガラス基板、石英基板、プラスチック基板などの絶縁表面を有する基板上に形成された半導体薄膜を活性層として用いた薄膜トランジスタから構成することで、高性能且つ低消費電力の半導体装置を、より軽量で安価に提供することができる。

以下に、本発明の実施例を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施例の記載内容に限定して解釈されるものではない。なお、実施例を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

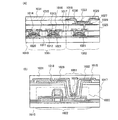

本実施例では、本発明における半導体装置を、薄膜トランジスタ(TFT)により構成する場合について、断面図を用いて説明する。

図10(A)は、絶縁基板1010上に形成されたTFT部1001とメモリ部1002の断面図を示す。TFT部1001は、実施の形態1に示した演算回路や実施の形態2に示したCPU、RAM、CPUインターフェースなどに相当する。メモリ部1002は、実施の形態2に示したROMに相当する。絶縁基板1010には、ガラス基板、石英基板、珪素からなる基板、金属基板、プラスチック基板等を用いることができる。またガラス基板を用いる場合、TFT等が形成される側と反対面を研磨し、薄くしたものを用いることができる。このように薄くしたガラス基板は、装置の軽量化、薄型化を達成することができる。

絶縁基板1010上には下地膜1011が設けられている。TFT部1001では下地膜1011を介して薄膜トランジスタ1020、1021が設けられ、メモリ部1002には下地膜1011を介して薄膜トランジスタ1022が設けられている。各薄膜トランジスタは、島状に分離形成された半導体膜1012、ゲート絶縁膜を介して設けられたゲート電極1014、ゲート電極側面に絶縁物で形成されたサイドウォール1013を有している。半導体膜1012は、膜厚が0.2μm以下、代表的には40nmから170nm、好ましくは50nmから150nmとなるように形成する。さらに、サイドウォール1013、及び半導体膜1012を覆う絶縁膜1016、半導体膜1012に形成された不純物領域に接続する電極1015を有する。なお電極1015は不純物領域と接続するため、ゲート絶縁膜及び絶縁膜1016にコンタクトホールを形成し、当該コンタクトホールに重ねて導電膜を形成し、当該導電膜をパターニングして形成することができる。

半導体膜1012は非晶質シリコン、多結晶シリコンを用いることができる。多結晶シリコンを用いる場合、まず非晶質シリコンを形成し、熱処理又はレーザ照射を行って多結晶シリコンを形成することができる。このとき、ニッケルを代表とする金属元素を用いて熱処理、又はレーザ照射を行うことにより、結晶化温度を低減することができる。レーザ照射には、連続発振、又はパルス発振のレーザ照射装置を用いることができる。また、熱処理を伴った結晶化法と、連続発振レーザ若しくは10MHz以上の周波数で発振するレーザビームを照射する結晶化法とを組み合わせても良い。連続発振レーザ又は10MHz以上の周波数で発振するレーザビームを照射することで、結晶化された半導体膜の表面を平坦なものとすることができる。それにより、ゲート絶縁膜を薄膜化することも可能であり、また、ゲート絶縁膜の耐圧を向上させることに寄与することができる。

また、半導体膜に対し、連続発振レーザ若しくは10MHz以上の周波数で発振するレーザビームを照射しながら一方向に走査して結晶化させて得られた半導体膜は、そのビームの走査方向に結晶が成長する特性がある。その走査方向をチャネル長方向(チャネル形成領域が形成されたときにキャリアが流れる方向)に合わせてトランジスタを配置し、以下に示すゲート絶縁膜を組み合わせることで、特性ばらつきが小さく、しかも電界効果移動度が高いトランジスタ(TFT)を得ることができる。

本発明における半導体装置を構成する薄膜トランジスタにおいて、ゲート絶縁膜等を代表とする絶縁膜は、高密度プラズマ処理を用いて被形成面の表面を酸化又は窒化することによって作製することができる。高密度プラズマ処理とは、プラズマ密度が1×1011cm−3以上、好ましくは1×1011cm−3から9×1015cm−3以下であり、マイクロ波(例えば周波数2.45GHz)といった高周波を用いたプラズマ処理である。このような条件でプラズマを発生させると、低電子温度が0.2eVから2eVとなる。このように低電子温度が特徴である高密度プラズマは、活性種の運動エネルギーが低いため、プラズマダメージが少なく欠陥が少ない膜を形成することができる。このようなプラズマ処理を可能とする成膜室に、被形成体、ゲート絶縁膜を形成する場合であればパターニングされた半導体膜が形成された基板を配置する。そして、プラズマ発生用の電極、所謂アンテナと被形成体との距離を20mmから80mm、好ましくは20mmから60mmとして成膜処理を行う。このような高密度プラズマ処理は、低温プロセス(基板温度400℃以下)の実現が可能となる。そのため、耐熱性の低いプラスチックを基板上に成膜することができる。

このような絶縁膜の成膜雰囲気は窒素雰囲気、又は酸素雰囲気とすることができる。窒素雰囲気とは、代表的には、窒素と希ガスとの混合雰囲気、又は窒素と水素と希ガスとの混合雰囲気である。希ガスは、ヘリウム、ネオン、アルゴン、クリプトン、キセノンの少なくとも1つを用いることができる。また酸素雰囲気とは、代表的には、酸素と希ガスとの混合雰囲気、酸素と水素と希ガスとの混合雰囲気である。又は一酸化二窒素と希ガスとの混合雰囲気を用いてプラズマ処理をしても同様の効果が得られる。希ガスは、ヘリウム、ネオン、アルゴン、クリプトン、キセノンの少なくとも1つを用いることができる。また水素と希ガスとの混合雰囲気を用いてもよい。

この高密度プラズマで生成された酸素ラジカル(OHラジカルを含む場合もある)や窒素ラジカル(NHラジカルを含む場合もある)によって、被形成面の表面を酸化又は窒化することができる。

このような高密度プラズマを用いた処理により、1〜20nm、代表的には5〜10nmの絶縁膜を形成することができる。この場合の反応は固相反応であるため、当該絶縁膜と半導体膜との界面準位密度はきわめて低くすることができる。このような、高密度プラズマ処理は、被形成面、例えば半導体膜であれば結晶性シリコン、又は多結晶シリコンを直接酸化、若しくは窒化するため、形成される絶縁膜の厚さは、ばらつきをきわめて小さくすることができる。加えて、結晶性シリコンの場合、結晶粒界でも酸化が強くされることがないため、非常に好ましい状態となる。すなわち、ここで示す高密度プラズマ処理で半導体膜の表面を固相酸化することにより、結晶粒界において異常な酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶縁膜を形成することができる。

このように形成された絶縁膜は、緻密なものとなる。また高密度プラズマ処理により形成された絶縁膜は、当該絶縁膜と半導体膜の接触する界面状態を改善することができる。例えば高密度プラズマ処理を用いてゲート絶縁膜を形成すると、半導体膜との界面状態を改善することができる。その結果、薄膜トランジスタの電気特性を向上させることができる。

絶縁膜の作製に高密度プラズマ処理を用いる場合を説明したが、半導体膜に高密度プラズマ処理を施してもよい。高密度プラズマ処理によって、半導体膜表面の改質を行うことができる。その結果、界面状態を改善でき、薄膜トランジスタの電気特性を向上させることができる。

本実施例においてゲート絶縁膜等の絶縁膜は、高密度プラズマ処理によって形成される絶縁膜のみを用いても良いし、それにプラズマや熱反応を利用したCVD法で酸化シリコン、酸窒化シリコン、窒化シリコンなどの絶縁膜を堆積し、積層させても良い。いずれにしても、高密度プラズマで形成した絶縁膜をゲート絶縁膜の一部又は全部に含んで形成されるトランジスタは、特性のばらつきを小さくすることができる。

また平坦性を高めるため、絶縁膜1017、1018が設けられているとよい。このとき絶縁膜1017は有機材料から形成し、絶縁膜1018は無機材料から形成するとよい。絶縁膜1017、1018が設けられている場合、電極1015は、これら絶縁膜1017、1018にコンタクトホールを介して不純物領域と接続するように形成することができる。

さらに絶縁膜1025が設けられ、電極1015と接続するように下部電極1027を形成する。下部電極1027の端部を覆い、下部電極1027が露出するように開口部が設けられた絶縁膜1028を形成する。開口部内に、メモリ材料層1029を形成し、上部電極1030を形成する。このようにして、下部電極1027、メモリ材料層1029、上部電極1030を有するメモリ素子1023が形成される。メモリ材料層1029は、有機材料又は無機材料から形成することができる。下部電極1027又は上部電極1030は、導電性材料から形成することができる。例えば、アルミニウム(Al)、チタン(Ti)、モリブデン(Mo)、タングステン(W)もしくはシリコン(Si)の元素からなる膜又はこれらの元素を用いた合金膜等から形成することができる。またインジウム錫酸化物(ITO)、酸化珪素を含むインジウム錫酸化物、2%から20%の酸化亜鉛を含む酸化インジウム等の透光性材料を用いることができる。

さらに平坦性を高め、不純物元素の侵入を防止するため、絶縁膜1031を形成するとよい。

本実施例で説明した絶縁膜は、無機材料又は有機材料を用いることができる。無機材料は、酸化珪素、窒化珪素を用いることができる。有機材料はポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、シロキサン、ポリシラザンを用いることができる。なお、シロキサン樹脂とは、Si−O−Si結合を含む樹脂に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。ポリシラザンは、珪素(Si)と窒素(N)の結合を有するポリマー材料を出発原料として形成される。

図10(B)は、図10(A)と異なり、電極1015のコンタクトホール1051内にメモリ材料層を形成したメモリの断面図を示す。図10(A)と同様に、下部電極として電極1015を用い、電極1015上にメモリ材料層1029、上部電極1030を形成し、メモリ素子1023を形成することができる。その後、絶縁膜1031を形成する。その他の構成は図10(A)と同様であるため、説明を省略する。

このようにコンタクトホール1051にメモリ素子を形成すると、メモリ素子の小型化を図ることができる。またメモリ用の電極が不要となるため製造工程を削減し、低コストでメモリを搭載した半導体装置を提供することができる。

以上のように、半導体装置をガラス基板、石英基板、プラスチック基板などの絶縁表面を有する基板上に形成された半導体薄膜を活性層として用いた薄膜トランジスタから構成することで、高性能且つ低消費電力の半導体装置を、より軽量で安価に提供することができる。

本実施例は、実施の形態1、実施の形態2または実施の形態3と自由に組み合わせて実施することが可能である。

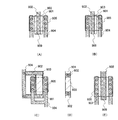

本実施例では、本発明における半導体装置において、回路の一部を構成する薄膜トランジスタのレイアウトについて、図11、図12及び図13を用いて説明する。

実施例1で示した半導体膜1012に相当する半導体層は、絶縁表面を有する基板の全面若しくは一部(トランジスタの半導体領域として確定されるよりも広い面積を有する領域)に、下地膜等を介して形成される。そして、フォトリソグラフィー技術によって、半導体層上にマスクパターンを形成する。そのマスクパターンを利用して半導体層をエッチング処理することにより、図11に示す薄膜トランジスタのソース領域、ドレイン領域及びチャネル形成領域を含む特定形状を有する島状の半導体パターン1101を形成することができる。そのパターン形成された半導体層の形状は、薄膜トランジスタの特性に基づき、要求される回路特性やレイアウトの適切さを考慮して決められる。

本発明における半導体装置の回路を構成する薄膜トランジスタにおいて、半導体層を形成するためのフォトマスクは特徴的なパターンを備えている。そのマスクパターンの屈曲する部分は、少なくとも直角に折れ曲がらないように複雑な形状で構成されている。例えば、屈曲部の外側は頂部を切り欠いた形状としている。この場合、マスクパターンの角部に丸みを持たせてもよい。図11は、このようなマスクパターンを有するフォトマスクを用いて形成された半導体層の形状を示している。この場合、当該フォトマスクを用いたフォトリソグラフィー工程の露光条件を制御することにより、半導体層1101の角部は、フォトマスクパターンの角部よりさらに丸みを帯びるように調節することもできる。すなわち、半導体層1101の角部には、フォトマスクのパターンよりもさらにパターン形状をなめらかにした丸みが設けられてもよい。なお図11において、後に形成されるゲート電極1014やゲート配線1201、電極1015や配線を点線で示す。

次に、角部に丸みがついた半導体層1101上には、ゲート絶縁膜が形成される。そして、実施例1で示したように、半導体層と一部が重なるようにゲート電極1014、及び同時にゲート配線1201が形成される。ゲート電極又はゲート配線は、金属層や半導体層を成膜し、フォトリソグラフィー技術によって形成することができる。

このゲート電極又はゲート配線を形成するためのフォトマスクのパターンは、屈曲部外側の角部を切り欠いた形状となっている。また、そのパターンの屈曲部内側は直角に折れ曲がらないように複数回に渡って折れ曲がっている。このような屈曲する形状はゲート配線パターンの幅を基準に考慮することができ、配線の線幅の1/2以下で、線幅の1/5以上の長さでに角部を削除している。このマスクパターンの形状は、図12に示すように、ゲート電極1014又はゲート配線のパターン形状として転写することができる。またゲート電極又はゲート配線への転写のときに、ゲート電極又はゲート配線の角部がさらに丸みを帯びるように転写することもできる。すなわちゲート電極又はゲート配線の角部には、フォトマスクのパターンよりもさらにパターン形状をなめらかにした丸みが設けられていてもよい。なお図12において、後に形成される電極1015や配線を点線で示す。

このようなゲート電極又はゲート配線は、レイアウトの制約上、矩形に折れ曲がる。そのため、ゲート電極又はゲート配線の丸みを帯びた角部には凸部(外側の辺)と凹部(内側の辺)が設けられる。この丸みを帯びた凸部ではプラズマによるドライエッチの際、異常放電による微粉の発生を抑えることができる。また丸みを帯びた凹部では、洗浄のときに、たとえできた微粉があっても、それが角に集まりやすいのを洗い流すことができる。その結果、歩留まり向上が甚だしく期待できるという効果を有する。

次に、ゲート電極又はゲート配線上には、上記実施例1で示したように絶縁膜1016、1017、1018に相当する絶縁層等を形成する。勿論、本発明において絶縁膜は単層であっても構わない。

そして絶縁層上に、絶縁膜には所定の位置に開口を形成し、当該開口に電極1015や配線に相当する導電膜を形成する。この開口は、下層に位置する半導体層又はゲート配線層と、配線層との間の電気的な接続をとるために設けられる。配線は、フォトリソグラフィー技術によってマスクパターンが形成され、エッチング加工により所定のパターンに形成される。

配線によって、ある特定の素子間を連結することができる。この配線は、特定の素子と素子の間を直線で結ぶのではなく、レイアウトの制約上、矩形に折れ曲がる(以下、屈曲部という)。また配線は、開口部やその他の領域において配線幅が変化することがある。例えば開口部では、開口が配線幅と同等若しくは大きい場合には、その部分で配線幅が広がるように変化する。また、配線は回路のレイアウト上、容量部の一方の電極を兼ねるため、配線幅を大きくとることがある。

図13に示すように、配線層は、L字形に折れ曲がった各コーナー部であって(直角三角形)の一辺が10μm以下、または、配線の線幅の1/2以下で、線幅の1/5以上の長さに角部を削除し、コーナー部を丸みをおびるパターンを有せしめる。即ち、上面からみたコーナー部における配線層の外周は曲線を形成するようにする。具体的には、コーナー部の外周縁に丸みを帯びさせるため、コーナー部を挟む互いに垂直な2つの第1直線と、これら2つの第1直線と約45度の角度をなす一つの第2直線と、で形成される直角2等辺三角形の部分に相当する配線層の一部を除去する。除去すると新たに2つの鈍角の部分が配線層に形成されるが、マスク設計や、エッチング条件を適宜設定することにより、各鈍角部分に第1直線と第2直線との両方に接する曲線が形成されるように配線層をエッチングすることが好ましい。なお、前記直角2等辺三角形の互いに等しい2辺の長さは、配線幅の1/5以上1/2以下とする。またコーナー部の内周についても、コーナー部の外周に沿って内周が丸みを帯びるよう形成する。

図13に示したレイアウトを有する回路において、屈曲部や配線幅が変化する部位の角部をなめらかにして、丸みを付けることにより、プラズマによるドライエッチの際、異常放電による微粉の発生を抑えることができる。また、洗浄のときに、微粉が角部に集まらずに容易に洗い流すことができるので、生産性が向上するという効果もある。すなわち、製造工程で発生する塵や微粉の問題を解消することができる。特に多数の平行配線が設けられる駆動回路部等の配線において、ゴミを洗い流すことを可能とすることは、きわめて好都合である。

本実施例では、半導体層、ゲート配線、配線の3つのレイアウトにおいて、角部又は屈曲部に丸みを帯びる形態を説明したが、これに限定されるものではない。すなわち、いずれか一の層において、角部又は屈曲部に丸みを帯びさせ、製造工程における塵や微粉等の問題を解消することができればよい。

以上のようなレイアウトを用いて半導体装置を構成することで、高性能且つ低消費電力の半導体装置を、より軽量で安価に提供することができる。

なお、本実施例は、実施の形態1、実施の形態2、実施の形態3または実施例1と自由に組み合わせて実施することが可能である。

本実施例では、本発明における半導体装置を構成する要素の一つとして、スタティックRAM(SRAM)を構成する一例について、図6〜図8を参照して説明する。なお、本実施例におけるSRAMを、実施の形態1及び実施の形態2で示した構成におけるRAMに用いると好適である。

図6(A)で示す半導体層610、611はシリコン若しくはシリコンを成分とする結晶性の半導体で形成することが好ましい。例えば、シリコン膜をレーザアニールなどによって結晶化された多結晶シリコン、単結晶シリコンなどが適用される。その他にも半導体特性を示す、金属酸化物半導体、アモルファスシリコン、有機半導体を適用することも可能である。

いずれにしても、最初に形成する半導体層は絶縁表面を有する基板の全面若しくは一部(トランジスタの半導体領域として確定されるよりも広い面積を有する領域)に形成する。そして、フォトリソグラフィー技術によって、半導体層上にマスクパターンを形成する。そのマスクパターンを利用して半導体層をエッチング処理することにより、TFTのソース及びドレイン領域及びチャネル形成領域を含む特定形状の島状の半導体層610、611を形成する。その半導体層610、611はレイアウトの適切さを考慮して決められる。

図6(A)で示す半導体層610、611を形成するためのフォトマスクは、図6(B)に示すマスクパターン620を備えている。このマスクパターン620は、フォトリソグラフィー工程で用いるレジストがポジ型かネガ型かで異なる。ポジ型レジストを用いる場合には、図6(B)で示すマスクパターン620は、遮光部として作製される。マスクパターン620は、頂部Aを切り欠いた形状となっている。また、屈曲部Bにおいては、その角部が直角とならないように複数段に渡って屈曲する形状となっている。このフォトマスクのパターンは、例えば、パターンの角部を一辺が10μm以下の長さで削除している。

図6(B)で示すマスクパターン620は、その形状が、図6(A)で示す半導体層610、611に反映される。その場合、マスクパターン620と相似の形状が転写されても良いが、マスクパターン620の角部がさらに丸みを帯びるように転写されていても良い。すなわち、マスクパターン620よりもさらにパターン形状をなめらかにした、丸め部を設けても良い。

半導体層610、611の上には、酸化シリコン若しくは窒化シリコンを少なくとも一部に含む絶縁層が形成される。この絶縁層を形成する目的の一つはゲート絶縁層である。そして、図7(A)で示すように、半導体層と一部が重なるようにゲート配線712、713、714を形成する。ゲート配線712は半導体層610に対応して形成される。ゲート配線713は半導体層610、611に対応して形成される。また、ゲート配線714は半導体層610、611に対応して形成される。ゲート配線は、金属層又は導電性の高い半導体層を成膜し、フォトリソグラフィー技術によってその形状を絶縁層上に作り込む。

このゲート配線を形成するためのフォトマスクは、図7(B)に示すマスクパターン721を備えている。このマスクパターン721は、配線の線幅の1/2以下で、線幅の1/5以上の長さで角部を削除している。図7(B)で示すマスクパターン721は、その形状が、図7(A)で示すゲート配線712、713、714に反映される。その場合、マスクパターン721と相似の形状が転写されても良いが、マスクパターン721の角部がさらに丸みを帯びるように転写されていても良い。すなわち、マスクパターン721よりもさらにパターン形状をなめらかにした、丸め部を設けても良い。凸部はプラズマによるドライエッチの際、異常放電による微粉の発生を抑え、凹部では、洗浄のときに、たとえできた微粉であっても、それが角に集まりやすいのを洗い流す結果として歩留まり向上が甚だしく期待できるという効果を有する。

層間絶縁層はゲート配線712、713、714の次に形成される層である。層間絶縁層は酸化シリコンなどの無機絶縁材料若しくはポリイミドやアクリル樹脂などを使った有機絶縁材料を使って形成する。この層間絶縁層とゲート配線712、713、714の間には窒化シリコン若しくは窒化酸化シリコンなどの絶縁層を介在させても良い。また、層間絶縁層上にも窒化シリコン若しくは窒化酸化シリコンなどの絶縁層を設けても良い。この絶縁層は、外因性の金属イオンや水分などTFTにとっては良くない不純物により半導体層やゲート絶縁層を汚染するのを防ぐことができる。

層間絶縁層には所定の位置に開孔が形成されている。例えば、下層にあるゲート配線や半導体層に対応して設けられる。金属若しくは金属化合物の一層若しくは複数層で形成される配線層は、フォトリソグラフィー技術によってマスクパターンが形成され、エッチング加工により所定のパターンに形成される。そして、図8(A)で示すように、半導体層と一部が重なるように配線815〜820を形成する。配線はある特定の素子間を連結する。配線は特定の素子と素子の間を直線で結ぶのではなく、レイアウトの制約上屈曲部が含まれる。また、コンタクト部やその他の領域において配線幅が変化する。コンタクト部では、コンタクトホールが配線幅と同等若しくは大きい場合には、その部分で配線幅が広がるように変化する。

この配線815〜820を形成するためのフォトマスクは、図8(B)に示すマスクパターン827を備えている。この場合においても配線は、配線の線幅の1/2以下で、線幅の1/5以上の長さで角部を削除し、コーナー部において丸みをおびるパターンを有せしめる。角部は、線幅の1/2以下で、1/5以上にコーナー部に丸みをおびさせる。このような配線は、凸部はプラズマによるドライエッチの際、異常放電による微粉の発生を抑え、凹部では、洗浄のときに、たとえできた微粉であっても、それが角に集まりやすいのを洗い流す結果として歩留まり向上が甚だしく期待できるという効果を有する。また、多数の平行配線では、ゴミを洗い流すのにはきわめて好都合である。

図8(A)には、nチャネル型トランジスタ821〜824、pチャネル型トランジスタ825、826が形成されている。nチャネル型トランジスタ823とpチャネル型トランジスタ825及びnチャネル型トランジスタ824とpチャネル型トランジスタ826はインバータ827、828を構成している。この6つのトランジスタを含む回路はSRAMを形成している。これらのトランジスタの上層には、窒化シリコンや酸化シリコンなどの絶縁層が形成されていても良い。

以上のような構成とすることで、高性能且つ低消費電力の半導体装置を、より軽量で安価に提供することができる。

なお、本実施例は、実施の形態1、実施の形態2、実施の形態3、実施例1または実施例2と自由に組み合わせて実施することが可能である。

本実施例では、本発明における半導体装置を構成するトランジスタについて、図9及び図14を参照して説明する。

本発明における半導体装置を構成するトランジスタは、単結晶基板に形成されるMOSトランジスタの他、薄膜トランジスタ(TFT)で構成することもできる。図9はこれらの回路を構成するトランジスタの断面構造を示す図である。図9には、nチャネル型トランジスタ801、nチャネル型トランジスタ802、容量素子804、抵抗素子805、pチャネル型トランジスタ803が示されている。各トランジスタは半導体層905、絶縁層908、ゲート電極909を備えた薄膜トランジスタを用いることができる。ゲート電極909は、第1導電層903と第2導電層902の積層構造で形成されている。また、図14(A)〜(D)は、図9で示すトランジスタ、容量素子、抵抗素子に対応する上面図であり、併せて参照することができる。

図9において、nチャネル型トランジスタ801は、チャネル長方向(キャリアの流れる方向)において、ゲート電極の両側に低濃度ドレイン(LDD)とも呼ばれ、配線904とコンタクトを形成するソース及びドレイン領域を形成する不純物領域906の不純物濃度よりも低濃度にドープされた不純物領域907が半導体層905に形成されている。不純物領域906と不純物領域907には、nチャネル型トランジスタ801を構成する場合、n型を付与する不純物としてリンなどが添加されている。LDDはホットエレクトロン劣化や短チャネル効果を抑制する手段として形成される。

図14(A)で示すように、nチャネル型トランジスタ801のゲート電極909において、第1導電層903は、第2導電層902の両側に広がって形成されている。この場合において、第1導電層903の膜厚は、第2導電層の膜厚よりも薄く形成されている。第1導電層903の厚さは、10〜100kVの電界で加速されたイオン種を通過させることが可能な厚さに形成されている。不純物領域907はゲート電極909の第1導電層903と重なるように形成されている。すなわち、ゲート電極909とオーバーラップするLDD領域を形成している。この構造は、ゲート電極909において、第2導電層902をマスクとして、第1導電層903を通して一導電型の不純物を添加することにより、自己整合的に不純物領域907を形成している。すなわち、ゲート電極とオーバーラップするLDDを自己整合的に形成している。

両側にLDDを有するトランジスタは、実施の形態1及び実施の形態2における電源回路208の整流用のTFTや、論理回路に用いられるトランスミッションゲート(アナログスイッチとも呼ぶ)を構成するトランジスタに適用される。これらのTFTは、ソース電極又はドレイン電極に正負両方の電圧が印加されるため、ゲート電極の両側にLDDを設けることが好ましい。

また第1導電層903は、第2導電層902を用いてゲート配線を形成する場合、それらの両端を揃えるようにパターニングしてもよい。その結果、微細なゲート配線を形成することができる。またゲート電極とオーバーラップするLDDを自己整合的に形成する必要もない。

図9において、nチャネル型トランジスタ802は、ゲート電極の片側に不純物領域906の不純物濃度よりも低濃度にドープされた不純物領域907が半導体層905に形成されている。図14(B)で示すように、nチャネル型トランジスタ802のゲート電極909において、第1導電層903は、第2導電層902の片側に広がって形成されている。この場合も同様に、第2導電層902をマスクとして、第1導電層903を通して一導電型の不純物を添加することにより、自己整合的にLDDを形成することができる。

片側にLDDを有するトランジスタは、ソース及びドレイン電極間に正電圧のみ、もしくは負電圧のみが印加されるトランジスタに適用すればよい。具体的には、インバータ回路、NAND回路、NOR回路、ラッチ回路といった論理ゲートを構成するトランジスタや、センスアンプ、定電圧発生回路、電圧制御発振器(以下、VCO(Voltage Controlled Oscillator)とも呼ぶ。)といったアナログ回路を構成するトランジスタに適用すればよい。

図9において、容量素子804は、第1導電層903と半導体層905とでゲート絶縁層908を挟んで形成されている。容量素子804を形成する半導体層905には、不純物領域910と不純物領域911を備えている。不純物領域911は、半導体層905において第1導電層903と重なる位置に形成される。また、不純物領域910は配線904とコンタクトを形成する。不純物領域911は、第1導電層903を通して一導電型の不純物を添加することで、不純物領域910と不純物領域911に,同じ不純物を添加して導電性をもたせることができる。いずれにしても、容量素子804において、半導体層905は電極として機能させるので、一導電型の不純物を添加して低抵抗化しておくことが好ましい。また、第1導電層903は、図14(C)に示すように、第2導電層902を補助的な電極として利用することにより、電極として十分に機能させることができる。このように、第1導電層903と第2導電層902を組み合わせた複合的な電極構造とすることにより、容量素子804を自己整合的に形成することができる。

容量素子は、実施の形態1及び実施の形態2における電源回路208が有する保持容量、あるいは共振回路207が有する共振容量として用いられる。特に、共振容量は、容量素子の2端子間に正負両方の電圧が印加されるため、2端子間の電圧の正負によらず容量として機能することが必要である。

図9において、抵抗素子805は、第1導電層903によって形成されている。第1導電層903は30〜150nm程度の厚さに形成されるので、その幅や長さを適宜設定して抵抗素子を構成することができる。

抵抗素子は、実施の形態1及び実施の形態2における変調回路212が有する抵抗負荷として用いられる。また、VCOなどで電流を制御する場合の負荷としても用いられる場合がある。抵抗素子は、高濃度に不純物元素を含む半導体層や、膜厚の薄い金属層によって構成すればよい。抵抗値が膜厚、膜質、不純物濃度、活性化率などに依存する半導体層に対して、金属層は、膜厚、膜質で抵抗値が決定するため、ばらつきが小さく好ましい。

図9において、pチャネル型トランジスタ803は、半導体層905に不純物領域912を備えている。この不純物領域912は、配線904とコンタクトを形成するソース及びドレイン領域を形成する。ゲート電極909の構成は第1導電層903と第2導電層902が重畳した構成となっている。pチャネル型トランジスタ803はLDDを設けないシングルドレイン構造のトランジスタである。pチャネル型トランジスタ803を形成する場合、不純物領域912にはp型を付与する不純物として硼素などが添加される。一方、不純物領域912にリンを添加すればシングルドレイン構造のnチャネル型トランジスタとすることもできる。

半導体層905及びゲート絶縁層908の一方若しくは双方に対してマイクロ波で励起され、電子温度が2eV以下、イオンエネルギーが5eV以下、電子密度が1011〜1013cm−3程度である高密度プラズマ処理によって酸化又は窒化処理しても良い。このとき、基板温度を300〜450℃とし、酸化雰囲気(O2、N2Oなど)又は窒化雰囲気(N2、NH3など)で処理することにより、半導体層905とゲート絶縁層908の界面の欠陥準位を低減することができる。ゲート絶縁層908対してこの処理を行うことにより、この絶縁層の緻密化を図ることができる。すなわち、荷電欠陥の生成を抑えトランジスタのしきい値電圧の変動を抑えることができる。また、トランジスタを3V以下の電圧で駆動させる場合には、このプラズマ処理により酸化若しくは窒化された絶縁層をゲート絶縁層908として適用することができる。また、トランジスタの駆動電圧が3V以上の場合には、このプラズマ処理で半導体層905の表面に形成した絶縁層とCVD法(プラズマCVD法若しくは熱CVD法)で堆積した絶縁層とを組み合わせてゲート絶縁層908を形成することができる。また、同様にこの絶縁層は、容量素子の誘電体層としても利用することができる。この場合、このプラズマ処理で形成された絶縁層は、1〜10nmの厚さで形成され、緻密な膜であるので、大きな電荷容量を持つ容量素子を形成することができる。

図9及び図14を参照して説明したように、膜厚の異なる導電層を組み合わせることにより、さまざまな構成の素子を形成することができる。第1導電層のみが形成される領域と、第1導電層と第2導電層が積層されている領域は、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて形成することができる。すなわち、フォトリソグラフィー工程において、フォトレジストを露光する際に、フォトマスクの透過光量を調節して、現像されるレジストマスクの厚さを異ならせる。この場合、フォトマスクまたはレチクルに解像度限界以下のスリットを設けて上記複雑な形状を有するレジストを形成してもよい。また、現像後に約200℃のベークを行ってフォトレジスト材料で形成されるマスクパターンを変形させてもよい。

また、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いることにより、第1導電層のみが形成される領域と、第1導電層と第2導電層が積層されている領域を連続して形成することができる。図14(A)に示すように、第1導電層のみが形成される領域を半導体層上に選択的に形成することができる。このような領域は、半導体層上において有効であるが、それ以外の領域(ゲート電極と連続する配線領域)では必要がない。このフォトマスク若しくはレチクルを用いることにより、配線部分は第1導電層のみの領域を作らないで済むので、配線密度を実質的に高めることができる。

図9及び図14の場合には、第1導電層はタングステン(W)、クロム(Cr)、タンタル(Ta)、窒化タンタル(TaN)またはモリブデン(Mo)などの高融点金属、又は高融点金属を主成分とする合金もしくは化合物を30nm〜50nmの厚さで形成する。また、第2導電層はタングステン(W)、クロム(Cr)、タンタル(Ta)、窒化タンタル(TaN)またはモリブデン(Mo)などの高融点金属、又は高融点金属を主成分とする合金もしくは化合物で300nm〜600nmの厚さに形成する。例えば、第1導電層と第2導電層をそれぞれ異なる導電材料を用い、後に行うエッチング工程でエッチングレートの差が生じるようにする。一例として、第1導電層にTaNを用い、第2導電層としてタングステン膜を用いることができる。

本実施例では、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて、電極構造の異なるトランジスタ、容量素子、抵抗素子を、同じパターニング工程によって作り分けることができることを示している。これにより、回路の特性に応じて、形態の異なる素子を、工程を増やすことなく作り込み、集積化することができる。

以上のようなトランジスタにより、半導体装置を構成することで、高性能且つ低消費電力の半導体装置を、より軽量で安価に提供することができる。

本実施例は、実施の形態1、実施の形態2、実施の形態3、実施例1、実施例2および実施例3と自由に組み合わせて実施することが可能である。

本実施例では、本発明における半導体装置を用いたシステム例について、図15及び図16を用いて説明する。本実施例では、本発明における半導体装置を用いた、セキュリティー性に優れたパーソナルコンピュータの利用者認証システムについて説明する。

図15は、本実施例における利用者認証システムの概要図で、パーソナルコンピュータ1501、半導体装置1502である。パーソナルコンピュータ1501には、入力装置1503及びリーダ/ライタ1504が接続されている。

パーソナルコンピュータ1501及び半導体装置1502は、暗号用の共通鍵1505を有する。具体的には、パーソナルコンピュータ1501及び半導体装置1502のメモリに共通鍵1505のデータを各々格納する。共通鍵1505は、例えば64ビット〜128ビットのデータで、平文(暗号化する前のデータ)の暗号化及び暗号文の復号に用いられる。共通鍵は、正規に登録された利用者毎に異なる共通鍵が作成され、パーソナルコンピュータ1501は、全てを有している。すなわち、正規に登録された利用者数分の共通鍵をパーソナルコンピュータ1501は有している。一方、半導体装置1502は、正規に登録された利用者が所有し、当該の利用者に固有な共通鍵のみを有している。共通鍵は、他者に知られぬよう、保存しなければならない。

なお、本実施例では、暗号方式として共通鍵暗号方式(ISO/IEC 9798−2 Information technology−Security techniques−Entity authentication− Part 2 : Mechanisms using symmetric encipherment algorithmsの規格参照)を用いる場合の例について示すが、公開鍵暗号方式(ISO/IEC 9798−3 Information technology−Security techniques−Entity authentication− Part 3 : Mechanisms using digital signature techniquesの規格参照)など、他の暗号方式でも容易に適用できる。

パーソナルコンピュータ1501は、共通鍵1505を用いて、平文を暗号化する手段を有する。具体的には、暗号化アルゴリズムを実行するソフトウェアを搭載しているものとする。また、半導体装置1502は、共通鍵1505を用いて、暗号文を復号する手段を有する。具体的には、実施の形態1または実施の形態2で示した演算回路において、復号アルゴリズムを実行する。

以下、図16のフローチャートを用いて、本実施例における利用者認証システムの利用方法を説明する。

まず、利用希望者が入力装置1503を用いて、パーソナルコンピュータ1501における利用者名及びパスワードを入力する(利用者名入力1601)。パスワードは、正規の利用者が事前に登録しておく。パーソナルコンピュータ1501は、入力された利用者名から、該当する共通鍵を用いて、ある平文を暗号化する(暗号データ作成1602)。ここで、平文は、特定の意味を持ったデータでも、無意味なデータでも良い。次に、暗号データをリーダ/ライタ1504から送信する(暗号データ送信1603)。半導体装置1502は、暗号データを受信し、共通鍵1505を用いて暗号データを復号し(復号化処理1604)、復号データをリーダ/ライタに送信する(復号データ送信1605)。パーソナルコンピュータ1501は、復号データを、最初の平文と比較し(認証1606)、一致した場合のみ、利用希望者が正規に登録されている利用者であると認め、利用可能とする(平常利用1607)。

以上のような、本実施例における利用者認証システムでは、パスワードを知り、且つ本発明における半導体装置を所有していないとコンピュータを利用できない。従って、パスワードのみの認証よりセキュリティー性が非常に高い。また、利用者は、半導体装置を携帯していれば、従来のパスワードのみによる認証と、何ら変わりなくパーソナルコンピュータを利用でき、新たな負担は少ない。

なお、本発明は、パーソナルコンピュータの利用者認証について説明したが、正規に登録された利用者のみが利用できる他のシステムに対しても容易に適用できる。例えば、ATM(Automated Teller Machine 現金自動支払機)、CD(Cash Dispenser 現金自動払出機)などに、容易に適用できる。

以上のような構成とすることで、本発明における半導体装置を用いた、非常にセキュリティー性が高い利用者認証システムを安価に構築することができる。

なお、本実施例は、実施の形態1、実施の形態2、実施の形態3、実施例1、実施例2、実施例3および実施例4と自由に組み合わせて実施することが可能である。

(付記)以上、説明した通り、本発明の態様として以下のものが含まれる。

通信信号を送受信するアンテナを備え、通信信号を識別する受信回路と、暗号化されたデータの送受信において復号化/暗号化の処理を行う演算回路と、演算回路の演算結果を送信する送信回路と、通信信号の受信時に演算回路の動作を停止させ、演算回路の動作時に受信回路及び送信回路の動作を停止させる状態制御レジスタとを有する半導体装置。

通信信号を送受信するアンテナを備え、通信信号を識別する受信回路と演算処理のプログラムを格納する読み出し専用メモリと演算処理の内容を記憶する作業メモリとを有し、復号化されたデータの内容に従ってプログラムを実行してデータ処理を行う演算回路と、演算回路の演算結果を送信する送信回路と、通信信号の受信時に演算回路の動作を停止させ、演算回路の動作時に受信回路及び送信回路の動作を停止させる状態制御レジスタとを有する半導体装置。

通信信号を送受信するアンテナを備え、通信信号を識別する受信回路と、暗号化されたデータの送受信において復号化/暗号化の処理を行う演算回路と、演算回路の演算結果を送信する送信回路と、動作磁界が変動するときに受信回路を動作させると共に演算回路の動作を停止させ、動作磁界が変動しないときに受信回路を停止させるとともに演算回路を動作させる状態制御レジスタとを有する半導体装置。

通信信号を送受信するアンテナを備え、通信信号を識別する受信回路と演算処理のプログラムを格納する読み出し専用メモリと演算処理の内容を記憶する作業メモリとを有し、復号化されたデータの内容に従ってプログラムを実行してデータ処理を行う演算回路と、演算回路の演算結果を送信する送信回路と、動作磁界が変動するときに受信回路を動作させると共に演算回路の動作を停止させ、動作磁界が変動しないときに受信回路を停止させるとともに演算回路を動作させる状態制御レジスタとを有する半導体装置。

通信信号を識別する受信回路と、演算回路と、演算回路の演算結果を送信する送信回路と、演算回路、受信回路及び送信回路の動作を制御する状態制御レジスタを備えた半導体装置の駆動方法において、通信信号を復調しSOF信号と受信データとEOF信号を識別するステップと、EOF信号を受信したときに制御レジスタを演算処理状態に変化させるステップと、演算回路において、受信データに従って演算処理を行うステップと、演算処理が終了したときに制御レジスタを送信処理状態に変化させるステップと、演算処理結果を通信信号の形式に沿って加工し変調回路に出力するステップと、送信終了時に制御レジスタを受信処理状態に変化させるステップとを含むもの。

通信信号を識別する受信回路と、演算回路と、演算回路の演算結果を送信する送信回路と、演算回路、受信回路及び送信回路の動作を制御する状態制御レジスタを備えた半導体装置の駆動方法において、通信信号を復調しSOF信号と受信データとEOF信号を識別するステップと、EOF信号を受信したときに制御レジスタを演算処理状態に変化させるステップと、演算回路において、暗号化されたデータを復号化し、そのデータの内容に従って、あらかじめ決められた内容の演算処理を行うステップと、演算処理が終了したときに制御レジスタを送信処理状態に変化させるステップと、演算処理結果を通信信号の形式に沿って加工し変調回路に出力するステップと、送信終了時に制御レジスタを受信処理状態に変化させるステップとを含むもの。

本発明における半導体装置の概要図。

本発明における半導体装置における処理のフローチャート。

本発明における半導体装置の概要図。

本発明における半導体装置における処理のフローチャート。

ASK方式におけるデータ送受信時の通信信号を示す図。

本発明における半導体装置のレイアウトを示す図。

本発明における半導体装置のレイアウトを示す図。

本発明における半導体装置のレイアウトを示す図。

本発明における半導体装置の断面図。

本発明における半導体装置の断面図。

本発明における半導体装置のレイアウトを示す図。

本発明における半導体装置のレイアウトを示す図。

本発明における半導体装置のレイアウトを示す図。

本発明における半導体装置を構成する電気素子を示す図。

本発明における半導体装置を用いた利用者認証システムの概要図。

本発明における半導体装置を用いた利用者認証システムのフローチャート。

実施の形態1及び実施の形態2で示す半導体装置の動作を説明するタイミングチャート図。

符号の説明

101 通信信号

102 包絡線

201 半導体装置

202 演算回路

203 状態制御レジスタ

204 受信回路

205 送信回路

206 アンテナ

207 共振回路

208 電源回路

209 リセット回路

210 クロック回路

211 復調回路

212 変調回路

213 受信信号

214 送信信号

215 システムリセット信号

216 システムクロック信号

217 イネーブル信号

218 イネーブル信号

219 イネーブル信号

301 通信信号受信

302 状態制御レジスタ設定

303 演算処理

304 状態制御レジスタ設定

305 通信信号送信

306 状態制御レジスタ設定

401 CPU

402 RAM

403 ROM

404 CPUインターフェース

405 リセット信号

501 通信信号受信

502 状態制御レジスタ設定

503 演算処理

504 状態制御レジスタ設定

505 通信信号送信

506 状態制御レジスタ設定

610 半導体層

611 半導体層

620 マスクパターン

712 ゲート配線

713 ゲート配線

714 ゲート配線

721 マスクパターン

801 nチャネル型トランジスタ

802 nチャネル型トランジスタ

803 pチャネル型トランジスタ

804 容量素子

805 抵抗素子

815 配線

816 配線

817 配線

818 配線

819 配線

820 配線

821 nチャネル型トランジスタ

822 nチャネル型トランジスタ

823 nチャネル型トランジスタ

824 nチャネル型トランジスタ

825 pチャネル型トランジスタ

826 pチャネル型トランジスタ

827 マスクパターン

902 導電層

903 導電層

904 配線

905 半導体層

906 不純物領域

907 不純物領域

908 ゲート絶縁層

909 ゲート電極

910 不純物領域

911 不純物領域

912 不純物領域

1001 TFT部

1002 メモリ部

1010 絶縁基板

1011 下地膜

1012 半導体膜

1013 サイドウォール

1014 ゲート電極

1015 電極

1016 絶縁膜

1017 絶縁膜

1018 絶縁膜

1020 薄膜トランジスタ

1022 薄膜トランジスタ

1023 メモリ素子

1025 絶縁膜

1027 下部電極

1028 絶縁膜

1029 メモリ材料層

1030 上部電極

1031 絶縁膜

1051 コンタクトホール

1101 半導体パターン

1201 ゲート配線

1501 パーソナルコンピュータ

1502 半導体装置

1503 入力装置

1504 リーダ/ライタ

1505 共通鍵

1601 利用者名入力

1602 暗号データ作成

1603 暗号データ送信

1604 復号化処理

1605 復号データ送信

1606 認証

1607 平常利用