JP4762522B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4762522B2 JP4762522B2 JP2004312684A JP2004312684A JP4762522B2 JP 4762522 B2 JP4762522 B2 JP 4762522B2 JP 2004312684 A JP2004312684 A JP 2004312684A JP 2004312684 A JP2004312684 A JP 2004312684A JP 4762522 B2 JP4762522 B2 JP 4762522B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- ultrafine carbon

- semiconductor

- insulating film

- carbon fiber

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

ト精度、縮小投影露光による加工技術の精度、レジストの現像後形成されたレジストマスクの仕上り寸法、コンタクトホールを開口するために層間絶縁膜をエッチングするときの横方向のエッチング量等を精密に制御しなければならず、微細構造の半導体素子を有する半導体装置の製造を著しく困難なものとしている。

lO3レーザ、ガラスレーザー、ルビーレーザー、アレキサンドライドレーザー、または

Ti:サファイアレーザーである。

本実施形態では、実施形態1とは異なる構造の半導体素子を、図2を用いて示す。なお、図1と同様の部位に関しては、同じ符号を用いて説明し、各部位の詳細な説明を省略する。

本実施形態では、第1実施形態及び第2実施形態とは異なる構造の半導体素子を、図3を用いて示す。なお、図1と同様の部位に関しては、同じ符号を用いて説明し、各部位の詳細な説明を省略する。

本実施形態では、第1実施形態乃至第3実施形態とは異なる構造の半導体素子を、図4を用いて示す。なお、図1と同様の部位に関しては、同じ符号を用いて説明し、各部位の詳細な説明を省略する。

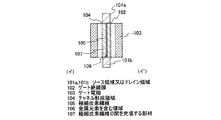

本実施形態では、第1実施形態乃至第4実施形態に示される半導体素子の作製方法について図5を用いて説明する。本実施形態では、第1実施形態で示される半導体素子の作製方法を示すが、第2実施形態乃至第4実施形態に示される半導体素子それぞれに適応することができる。

コートにて塗布することにより、極細炭素繊維の間を充填する。

本実施形態では、第1実施形態乃至第4実施形態に示される半導体素子の作製方法について図6を用いて説明する。本実施形態では、第5実施形態において、極細炭素繊維の間を充填する部材として、半導体膜を用いた例を示す。

本実施形態では、第1実施形態乃至第4実施形態に示される半導体素子の作製工程として、第5実施形態又は第6実施形態とは異なる工程を示す。本実施形態では、基板として、シリコン単結晶等の半導体材料又は半導体化合物の単結晶基板を用いた例を示す。なお、本実施形態は、ガラス基板等の絶縁表面を有する基板にも適応することができる。

本実施形態では、第1実施形態乃至第4実施形態に示される半導体素子の作製工程として、第7実施形態において、極細炭素繊維の間を充填する材料として絶縁膜を用いた構造の作製工程を示す。

とができる。電子機器としては、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。電子機器の1つであるカーナビゲーションを例に挙げ、本発明の素子が実際に電子機器に実装されている様子を図11(A)に示す。

ーディオROM1121、オーディオ用回路のクロック信号を作製したり、カウンタを使ってオーディオROMのアドレスを作製する機能を有するオーディオコントローラ1122、デジタル音声データからアナログ波形を作製したり、アナログ波形を増幅する機能を有するアンプ1123を有する。

Claims (13)

- 基板上に形成した導電性を有する第1の領域上に接して、選択的に金属元素を含む領域を形成し、

前記金属元素を含む領域上に接して、半導体を呈する極細炭素繊維を前記金属元素を含む領域を触媒として前記基板に対して垂直方向に形成し、

前記極細炭素繊維の間を充填する部材を形成し、

前記極細炭素繊維を包囲するゲート絶縁膜を形成し、

前記ゲート絶縁膜に接するゲート電極を形成し、

前記極細炭素繊維と接続する導電性を有する第2の領域を前記極細炭素繊維上に形成することを特徴とする半導体装置の作製方法。 - 基板上に形成した導電性を有する第1の領域上に接して、選択的に金属元素を含む領域を形成し、

前記金属元素を含む領域上に接して、半導体を呈する極細炭素繊維を前記金属元素を含む領域を触媒として前記基板に対して垂直方向に形成した後、半導体材料を形成し、

前記半導体材料に、レーザ光を照射して前記極細炭素繊維の間を半導体材料で充填し、

前記半導体材料の一部を除去した後、

前記極細炭素繊維を包囲するゲート絶縁膜を形成し、

前記ゲート絶縁膜に接するゲート電極を形成し、

前記極細炭素繊維と接続する導電性を有する第2の領域を前記極細炭素繊維上に形成することを特徴とする半導体装置の作製方法。 - 基板上に形成した導電性を有する第1の領域上に、第1の絶縁膜を介してゲート電極を筒状に形成し、

前記ゲート電極の内表面を覆う第2の絶縁膜を形成し、

前記第2絶縁膜の一部を除去して、前記導電性を有する第1の領域を露出した後、該導電性を有する第1の領域上に接して、金属元素を含む領域を前記第2の絶縁膜内に形成し、

前記金属元素を含む領域上に接して、半導体を呈する極細炭素繊維を前記金属元素を含む領域を触媒として前記基板に対して垂直方向に形成し、

前記極細炭素繊維の間を充填する部材を形成した後、前記極細炭素繊維に接続する導電性を有する第2の領域を前記極細炭素繊維上に形成することを特徴とする半導体装置の作製方法。 - 請求項1又は請求項3において、

前記極細炭素繊維の間を充填する部材は、半導体材料で形成されることを特徴とする半導体装置の作製方法。 - 請求項1又は請求項3において、

前記極細炭素繊維の間を充填する部材は、絶縁材料で形成されることを特徴とする半導体装置の作製方法。 - 請求項1又は請求項3において、

前記極細炭素繊維の間を充填する部材は、液滴吐出法で形成されることを特徴とする半導体装置の作製方法。 - 請求項5において、

前記絶縁材料は、比誘電率が4以下の低誘電率材料であることを特徴とする半導体装置の作製方法。 - 請求項2において、

前記レーザ光は、連続発振のレーザから照射されるレーザ光であることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項8のいずれか一項において、

前記極細炭素繊維の領域は、チャネル形成領域であることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項9のいずれか一項において、

前記金属元素を含む領域は、基板面に対して傾斜することを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項10のいずれか一項において、

前記金属元素は、ニッケル、鉄、コバルト、白金、ゲルマニウム、チタン、又はパラジウムから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物であることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項11のいずれか一項において、

前記導電性を有する第1の領域及び前記導電性を有する第2の領域は、ソース領域及びドレイン領域であることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項12のいずれか一項において、

前記極細炭素繊維は、グラファイトナノファイバ、カーボンナノファイバ、カーボンナノチューブ、チューブ状グラファイト、カーボンナノコーン、又はコーン状グラファイトであることを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004312684A JP4762522B2 (ja) | 2003-10-28 | 2004-10-27 | 半導体装置の作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003368159 | 2003-10-28 | ||

| JP2003368159 | 2003-10-28 | ||

| JP2004312684A JP4762522B2 (ja) | 2003-10-28 | 2004-10-27 | 半導体装置の作製方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010271734A Division JP5250615B2 (ja) | 2003-10-28 | 2010-12-06 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005159332A JP2005159332A (ja) | 2005-06-16 |

| JP2005159332A5 JP2005159332A5 (ja) | 2007-11-22 |

| JP4762522B2 true JP4762522B2 (ja) | 2011-08-31 |

Family

ID=34741101

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004312684A Expired - Fee Related JP4762522B2 (ja) | 2003-10-28 | 2004-10-27 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4762522B2 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7829883B2 (en) * | 2004-02-12 | 2010-11-09 | International Business Machines Corporation | Vertical carbon nanotube field effect transistors and arrays |

| US7135773B2 (en) * | 2004-02-26 | 2006-11-14 | International Business Machines Corporation | Integrated circuit chip utilizing carbon nanotube composite interconnection vias |

| WO2006038504A1 (ja) * | 2004-10-04 | 2006-04-13 | Matsushita Electric Industrial Co., Ltd. | 縦型電界効果トランジスタおよびその製造方法 |

| CN101687631A (zh) * | 2007-03-28 | 2010-03-31 | 昆南诺股份有限公司 | 纳米线电路结构 |

| EP2169721B1 (en) * | 2007-07-03 | 2019-09-04 | Panasonic Intellectual Property Management Co., Ltd. | Semiconductor device, semiconductor device manufacturing method and image display device |

| TW201001629A (en) * | 2008-04-11 | 2010-01-01 | Sandisk 3D Llc | Memory cell that includes a carbon nano-tube reversible resistance-switching element and methods of forming the same |

| JP2011187901A (ja) * | 2010-03-11 | 2011-09-22 | Canon Inc | 半導体デバイスの製造方法 |

| JP6250210B2 (ja) * | 2017-04-11 | 2017-12-20 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置 |

| CN113471298A (zh) * | 2021-06-23 | 2021-10-01 | Tcl华星光电技术有限公司 | 薄膜晶体管、显示面板及电子设备 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100360476B1 (ko) * | 2000-06-27 | 2002-11-08 | 삼성전자 주식회사 | 탄소나노튜브를 이용한 나노 크기 수직 트랜지스터 및 그제조방법 |

-

2004

- 2004-10-27 JP JP2004312684A patent/JP4762522B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005159332A (ja) | 2005-06-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4689218B2 (ja) | 半導体装置の作製方法 | |

| KR101013482B1 (ko) | 반도체 장치 및 그의 제작방법 | |

| US7067926B2 (en) | Semiconductor chip and method for manufacturing the same | |

| JP5073020B2 (ja) | 半導体装置の作製方法 | |

| US6911675B2 (en) | Active matrix display device and manufacturing method thereof | |

| TWI330396B (en) | Semiconductor device and method for manufacturing the same | |

| US7655560B2 (en) | Wiring board, manufacturing method thereof, semiconductor device and manufacturing method thereof | |

| JP2004004757A (ja) | 表示装置及びその作製方法 | |

| JP4762522B2 (ja) | 半導体装置の作製方法 | |

| JP2004349513A (ja) | 薄膜回路装置及びその製造方法、並びに電気光学装置、電子機器 | |

| JP5250615B2 (ja) | 半導体装置 | |

| JP4850168B2 (ja) | 半導体装置 | |

| JP4408042B2 (ja) | 半導体装置及びその作製方法 | |

| JP2005072573A (ja) | 配線基板及びその作製方法、並びに半導体装置及びその作製方法 | |

| US7923293B2 (en) | Method for manufacturing a semiconductor device wherein the electrical connection between two components is provided by capillary phenomenon of a liquid conductor material in a cavity therebetween | |

| JP2005056985A (ja) | 半導体装置の製造方法、半導体装置および電子機器 | |

| JP2003233326A (ja) | アクティブマトリクス型表示装置及びその作製方法 | |

| US20090141009A1 (en) | LCD Driver IC and Method for Manufacturing the Same | |

| JP4879467B2 (ja) | 半導体装置の作製方法 | |

| JP2005252112A (ja) | 薄膜トランジスタ及びその作製方法、並びに前記薄膜トランジスタを用いた電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071010 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071010 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101111 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101116 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20101119 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101203 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110412 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110518 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110607 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110608 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140617 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140617 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |