JP4737470B2 - Game machine - Google Patents

Game machine Download PDFInfo

- Publication number

- JP4737470B2 JP4737470B2 JP2009147748A JP2009147748A JP4737470B2 JP 4737470 B2 JP4737470 B2 JP 4737470B2 JP 2009147748 A JP2009147748 A JP 2009147748A JP 2009147748 A JP2009147748 A JP 2009147748A JP 4737470 B2 JP4737470 B2 JP 4737470B2

- Authority

- JP

- Japan

- Prior art keywords

- display

- data

- image

- transfer

- memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Pinball Game Machines (AREA)

- Display Devices Of Pinball Game Machines (AREA)

Description

本発明は、画像表示装置を備えた遊技機に関するものである。 The present invention relates to a gaming machine provided with an image display device.

パチンコ機やスロットマシンなどの遊技機には、遊技の進行に応じた動画像を液晶ディスプレイ(Liquid Crystal Display、以下、LCDという)などの画像表示装置に表示することによって、遊技の興趣を高めたものがある。これらの遊技機は、画像表示装置の他、遊技の進行を制御する主制御装置や、遊技の進行に応じた動画像を画像表示装置に表示させる表示制御装置などを備える。 For gaming machines such as pachinko machines and slot machines, the game has been enhanced by displaying moving images according to the progress of the game on an image display device such as a liquid crystal display (LCD). There is something. These gaming machines include an image display device, a main control device that controls the progress of the game, a display control device that displays a moving image according to the progress of the game on the image display device, and the like.

遊技機の表示制御装置は、主制御装置から出力された表示コマンドに基づいて画像表示装置における動画像の表示態様を制御する表示制御プロセッサと、この表示態様の制御に基づいて画像表示装置によって動画像表示が可能な映像信号を生成する画像表示プロセッサ(Video Display Processor、以下、VDPという)とを備え、表示制御プロセッサ側からVDP側へと種々のデータが転送される。これら転送されるデータは、近年の遊技機に要求される動画像表示の品質の高まりに伴って、比較的大きなデータ量となる場合がある。 The display control device of the gaming machine includes a display control processor that controls a display mode of a moving image on the image display device based on a display command output from the main control device, and a video by the image display device based on the control of the display mode. An image display processor (Video Display Processor, hereinafter referred to as VDP) that generates a video signal capable of image display is provided, and various data is transferred from the display control processor side to the VDP side. These transferred data may have a relatively large amount of data as the quality of moving image display required in recent gaming machines increases.

従来、データ量が比較的大きなデータについては、表示制御プロセッサの処理負担を軽減するため、表示制御プロセッサ側からVDP側へのデータ転送を、ダイレクトメモリアクセス(Direct Memory Access、以下、DMAという)転送によって行う遊技機があった。このDMA転送中には表示制御プロセッサの全ての処理が停止するため、実施中の動画像表示に対して表示制御プロセッサの停止が影響しないタイミングでDMA転送を行っていた。下記特許文献1には、表示制御プロセッサ側からVDP側へのDMA転送を行う遊技機が記載されている。

Conventionally, for data with a relatively large amount of data, direct memory access (hereinafter referred to as DMA) transfer is used to transfer data from the display control processor to the VDP in order to reduce the processing load on the display control processor. There was a gaming machine to do by. Since all processes of the display control processor are stopped during the DMA transfer, the DMA transfer is performed at a timing at which the stop of the display control processor does not affect the moving image display being performed.

遊技機特有の事情として、主制御装置は、表示制御プロセッサから信号を受け取るという形態では、表示コマンドが受信されたか否かを確認できない。そのため、DMA転送中に主制御装置からの表示コマンドの出力が開始され終了してしまった場合には、表示制御プロセッサは、その表示コマンドを受信することができず、取りこぼした表示コマンドに基づいた動画像表示の制御を行うことができない虞があり、設計に多くの時間を費やしていた。 As a situation peculiar to the gaming machine, the main control device cannot confirm whether or not the display command is received in the form of receiving a signal from the display control processor. Therefore, if the output of the display command from the main controller is started and ended during the DMA transfer, the display control processor cannot receive the display command and is based on the missed display command. There is a possibility that control of moving image display cannot be performed, and a lot of time has been spent on designing.

実施中の動画像表示とは無関係なタイミングで出力される表示コマンドとして、例えば、「あたり」または「はずれ」の表示を行う図柄の変動表示を実施する予定回数の報知(いわゆる保留表示)を画像表示装置で行う遊技機における、その保留表示に関する表示コマンドがある。この保留表示に関する表示コマンドは、遊技球が所定の入賞口に入賞した際に出力されるため、実施中の動画像表示とは無関係なタイミングで出力されることとなる。 As a display command output at a timing irrelevant to the moving image display being performed, for example, a notification of the scheduled number of times to perform the variable display of the symbol that displays “success” or “out” (so-called hold display) is displayed as an image. There is a display command related to the hold display in the gaming machine executed by the display device. Since the display command related to the hold display is output when the game ball wins a predetermined winning opening, it is output at a timing unrelated to the moving image display being performed.

本発明は、上記の問題を解決することを目的としてなされ、実施中の動画像表示とは無関係なタイミングで主制御装置から出力される表示コマンドの取りこぼしを回避しつつ、表示制御プロセッサ側からVDP側へのDMA転送を実現することができる遊技機を提供することを目的とする。 The present invention has been made in order to solve the above-mentioned problems, and avoids missing a display command output from the main controller at a timing irrelevant to the moving image display being performed, while the VDP from the display control processor side. An object of the present invention is to provide a gaming machine capable of realizing DMA transfer to the side.

上記した課題を解決するため、本発明の遊技機は、遊技の進行に応じて背景画像およびキャラクタ画像と共に複数の図柄画像を変動させて表示する画像表示装置を備え、前記複数の図柄画像の組み合わせに応じて遊技者にとって有利な遊技を実行する遊技機であって、

前記複数の図柄画像を変動させて表示するパターンを指示する変動コマンドを出力する主制御装置と、

前記主制御装置から前記変動コマンドを受け取り、該変動コマンドに基づいて前記画像表示装置に表示される動画像を制御する表示制御装置と

を備え、

前記表示制御装置は、

データをやり取りするバスに接続され、前記変動コマンドに応じた動画像フレームの描画を指示する描画指示データを生成する表示制御プロセッサと、

前記表示制御プロセッサから前記描画指示データを受け取り、該描画指示データに基づいて前記動画像フレームを描画する画像表示プロセッサと、

前記バスに接続され、データを記憶する第1および第2のメモリと、

前記バスに接続され、前記第1のメモリから前記第2のメモリへのデータのダイレクトメモリアクセス転送を行う転送コントローラと

を含み、

前記表示制御プロセッサは、前記動画像フレームの描画に用いられる外部画像データを生成し、該外部画像データを前記第1のメモリに書き込む手段を含み、

前記転送コントローラは、前記外部画像データが前記第1のメモリに書き込まれた場合、該外部画像データの前記第1のメモリから前記第2のメモリへのダイレクトメモリアクセス転送を、前記画像表示装置に対する垂直同期信号のブランク期間を契機に、前記主制御装置が一出力単位の前記変動コマンドを出力している時間より短い時間で転送可能な転送単位に分割して実行する手段を含み、

前記画像表示プロセッサは、前記描画指示データに基づいて、前記第2のメモリにダイレクトメモリアクセス転送された外部画像データを前記第2のメモリから読み出し、該外部画像データを用いて前記動画像フレームを描画する手段を含むことを特徴とする。ここで、一出力単位の一出力とは、主制御装置が表示制御プロセッサに対して一度に処理可能なデータ量の出力である。

In order to solve the above-described problems, the gaming machine of the present invention includes an image display device that displays a plurality of symbol images together with a background image and a character image as the game progresses, and a combination of the symbol images. A game machine that executes a game advantageous to the player according to

A main control device that outputs a change command for instructing a pattern to be displayed by changing the plurality of design images;

A display control device that receives the variation command from the main control device and controls a moving image displayed on the image display device based on the variation command;

With

The display control device includes:

A display control processor connected to a bus for exchanging data and generating drawing instruction data for instructing drawing of a moving image frame according to the variation command ;

An image display processor that receives the drawing instruction data from the display control processor and draws the moving image frame based on the drawing instruction data ;

First and second memories connected to the bus for storing data;

Connected to said bus, and transfer controller from the first memory performing direct memory access transfer of data to the second memory

Including

The display control processor includes means for generating external image data used for drawing the moving image frame and writing the external image data in the first memory,

When the external image data is written in the first memory, the transfer controller performs direct memory access transfer of the external image data from the first memory to the second memory to the image display device. Triggered by a blank period of the vertical synchronization signal, the main control unit includes a unit that divides and executes a transfer unit that can be transferred in a time shorter than a time in which the output command of one output unit is output,

The image display processor reads external image data transferred by direct memory access to the second memory from the second memory based on the drawing instruction data, and uses the external image data to read the moving image frame. It includes a means for drawing . Here, one output of one output unit is an output of a data amount that can be processed at a time by the main control device to the display control processor.

また、上記した課題を解決するため、上述の発明をDMA転送方法に適用しても良い。 In order to solve the above-described problems, the above-described invention may be applied to a DMA transfer method .

本発明の遊技機およびDMA転送方法によれば、一出力単位の表示コマンドが出力される時間よりも、一転送単位のDMA転送が行われる時間の方が短時間であるため、DMA転送中に表示コマンドの出力が開始され終了してしまう事態を回避することができる。その結果、DMA転送中に表示コマンドの出力が開始された場合であっても、そのDMA転送の一転送単位の終了後に再稼動する表示制御プロセッサは、その表示コマンドを受け取ることができる。したがって、実施中の動画像表示とは無関係なタイミングで主制御装置から出力される表示コマンドの取りこぼしを回避しつつ、表示制御プロセッサ側からVDP側へのDMA転送を実現することができる。 According to the gaming machine and the DMA transfer method of the present invention, the time during which the DMA transfer in one transfer unit is performed is shorter than the time in which the display command in one output unit is output. It is possible to avoid the situation where the output of the display command starts and ends. As a result, even when the display command output is started during the DMA transfer, the display control processor that is restarted after the end of one transfer unit of the DMA transfer can receive the display command. Therefore, it is possible to realize DMA transfer from the display control processor side to the VDP side while avoiding missing the display command output from the main control device at a timing unrelated to the moving image display being performed.

上記の構成を有する本発明の遊技機は、以下の態様を採ることもできる。例えば、前記画像表示プロセッサ、転送コントローラ、前記第2のメモリは、単一のチップに一体に回路形成されていても良い。 The gaming machine of the present invention having the above configuration can also take the following aspects . For example, the image display processor, the transfer controller, and the second memory may be integrally formed on a single chip.

また、前記外部画像は、前記背景画像、前記キャラクタ画像、前記図柄画像の少なくともいずれかの画像であっても良い。 The external image may be at least one of the background image, the character image, and the design image.

以上説明した本発明の構成および作用を一層明らかにするために、以下本発明を適用した遊技機の1つとしてパチンコ機について次の順序で説明する。なお、本明細書において、信号名の先頭に「#」が付されているものは、負論理であることを意味している。「ハイレベル」は2値信号の2つのレベルのうちの「1」レベルを意味し、「ローレベル」は「0」レベルを意味している。 In order to further clarify the configuration and operation of the present invention described above, a pachinko machine will be described in the following order as one of the gaming machines to which the present invention is applied. In the present specification, a signal name prefixed with “#” means negative logic. “High level” means the “1” level of the two levels of the binary signal, and “Low level” means the “0” level.

目次

A.実施例

A−(1).パチンコ機10の全体構成

A−(2).パチンコ機10が備える表示制御装置30の構成

A−(3).表示制御プロセッサ310における表示コマンドの受信

B.その他の実施形態

Table of Contents A. Example A- (1). Overall configuration of pachinko machine 10 A- (2). Configuration of

A.実施例:

A−(1).パチンコ機10の全体構成:

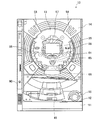

はじめに、本発明の実施例のパチンコ機10の全体構成について説明する。図1は、パチンコ機10の正面図である。パチンコ機10は、パチンコ店の島設備等に固定される外枠11、外枠11に嵌め込まれる内枠12、内枠12の中央上寄りに配置され遊技球による遊技が行われる遊技板13、遊技板13の前面に配置され中央部にガラス板を有するガラス枠14、遊技者による遊技板13への遊技球の発射の指示を受け付けるハンドル15、遊技球の貸し出しを処理するカードユニット90などを備える。

A. Example:

A- (1). Overall configuration of the pachinko machine 10:

First, the overall configuration of the

遊技板13の中央部には、動画像を表示する画像表示装置であるLCD35が設けられ、このLCD35の下方には、遊技球の入賞を受け付ける入賞口61が設けられている。この入賞口61は、入賞した遊技球を検知するスイッチ65、所定の場合に遊技球の導入経路を拡縮するソレノイド66を備える。パチンコ機10は、発光ダイオード(Light Emitting Diode、以下、LEDという)を内蔵し発光する電飾55,56,57,58,59を備える。電飾55,56は遊技板13の左右の端にそれぞれ設けられ、電飾57はLCD35の上部に設けられ、電飾58,59は、ガラス枠14の上部の左右にそれぞれ設けられている。内枠12の正面中央には、音声を出力するスピーカ45が内蔵されている。

An

次に、パチンコ機10の電気的な概略構成について説明する。図2は、パチンコ機10の電気的な概略構成を機能的に示すブロック図である。パチンコ機10は、遊技の進行を制御する主制御装置20を備え、この主制御装置20には、表示制御装置30,音声制御装置40,ランプ制御装置50,払出制御装置70などの各種制御装置の他、スイッチ65やソレノイド66などが電気的に接続されている。主制御装置20は、スイッチ65からの入力信号を受信するとともに、制御信号を出力してソレノイド66を駆動する。主制御装置20を始めとする種々の制御装置は、図1に示した内枠12の裏面(図示しない)に設けられている。

Next, an electrical schematic configuration of the

表示制御装置30は、遊技の進行に応じた動画像をLCD35に表示させる。なお、表示制御装置30の詳細については後述する。音声制御装置40は、主制御装置20の制御信号に基づいてスピーカ45における音声の出力を制御する。ランプ制御装置50は、主制御装置20の制御信号に基づいて電飾55,56,57,58,59の発光を制御する。払出制御装置70は、主制御装置20の制御信号に基づいて景品球としての遊技球の払い出しを行い、カードユニット90の制御信号に基づいて貸出球としての遊技球の払い出しを行う。なお、図1および図2には、電飾、スイッチ、ソレノイドの全てを示さないが、パチンコ機10は、それぞれを複数備える。また、LCD35およびスピーカ45を複数備えた構成としても良い。

The

次に、LCD35における動画像表示について説明する。図3は、LCD35における動画像表示の一例を示す説明図である。パチンコ機10は、スイッチ65において遊技球の入賞が検知されると、LCD35において図柄変動表示を行う。本実施例の図柄変動表示は、LCD35における中段部に、左特定図柄表示領域ML,中特定図柄表示領域MC,右特定図柄表示領域MRの3つの特定図柄表示領域が、この順に横並びに設けられている。それぞれの特定図柄表示領域には、「一」から「十」の10個の漢数字が描かれた特定図柄画像が、LCD35の上段から下段へ(図3中の矢印方向)、次々に表示された後、いずれかの特定図柄画像が確定表示される。この確定表示された3つの特定図柄画像が全て揃った場合には「あたり」を意味し、遊技者にとって有利な遊技が実行される。3つの特定図柄画像が揃わない場合には「はずれ」を意味し、通常の遊技が継続して実行される。なお、特定図柄画像の確定表示の形態は、横並びに限るものではなく、縦方向や斜め方向に並べても良い。また、特定図柄画像の数は、3つに限るものではなく、2つや3つ以上の特定図柄画像を並べても良い。また、「あたり」の確定表示の形態は、3つの特定図柄画像が全て揃う場合ではなく、特定の組み合わせで揃った場合としても良い。

Next, moving image display on the

図柄変動表示を実施中に、更にスイッチ65において遊技球の入賞が検知されると、最大4つまでの図柄変動表示を記憶し、実施中の図柄変動表示が終了した後、記憶された図柄変動表示を順次実施する。この図柄変動表示を実施する予定回数の報知である保留表示を行うため、LCD35の下段部には、保留表示領域RBが設けられている。本実施例の保留表示は、保留表示領域RBに横一列に4つの円図形が描かれ、1回の図柄変動表示を記憶する毎に、左側の円図形から順に色が反転する。なお、保留表示の形態としては、記憶する図柄変動表示の個数を数字で表しても良い。LCD35では、図柄変動表示や保留表示の他、種々のバックグラウンド画像BGやキャラクタ画像CRが、遊技の進行状態に応じて表示される。

If a winning of a game ball is further detected by the

A−(2).パチンコ機10が備える表示制御装置30の構成:

次に、本発明の実施例のパチンコ機10が備える表示制御装置30の構成について説明する。図4は、パチンコ機10が備える表示制御装置30の電気的な構成を示すブロック図である。

A- (2). Configuration of

Next, the configuration of the

パチンコ機10の表示制御装置30は、主制御装置20から表示コマンドを受信する。表示コマンドには、LCD35において複数の図柄を用いた図柄変動表示を行う際における図柄変動パターンや各特定図柄画像の種類などを指示する変動コマンドや、LCD35において図柄変動表示の保留表示を行う際における保留数などを指示する保留コマンドなどがある。表示コマンドに関して主制御装置20が表示制御装置30に対して出力する信号としては、表示コマンドを送信するデータ信号DATAと、表示コマンドの送信を実行中であることを伝えるセレクト信号#SELと、表示コマンドの書き込みのタイミングを伝える書き込み信号#WRとがある。

The

パチンコ機10の表示制御装置30は、主制御装置20から受け取った表示コマンドに基づいて、映像信号をLCD35に出力する。映像信号とは、LCD35によって動画像表示が可能な信号であり、赤(Red),緑(Green),青(Blue)の各信号から成るRGB信号や、RGB信号をLCD35において展開するための同期信号(SYNC信号)などの信号である。

The

パチンコ機10の表示制御装置30は、主制御装置20から出力された表示コマンドに基づいてLCD35における動画像の表示態様を制御する表示制御プロセッサ310と、この表示制御プロセッサ310の制御に基づいて映像信号を生成するVDP320とを備える。

The

表示制御装置30の表示制御プロセッサ310は、表示態様の制御に必要な動作を規定した制御プログラムを不揮発的に記憶する制御ROM316と、所定のデータを揮発的に記憶可能なSDRAM(Synchronous DRAM)314と、制御ROM316に記憶された制御プログラムをSDRAM314にロードし実行するCPU(Central Processing Unit)312とを備える。CPU312が回路形成されたチップと、SDRAM314が回路形成されたチップとは、MCM(Multi Chip Module)810として単一のパッケージに実装されている。

The

表示制御装置30は、表示制御プロセッサ310やVDP320の他、映像信号の生成に用いられる種々の画像データを不揮発的に記憶するキャラクタROM330と、所定のデータを揮発的に記憶可能なDRAM(Dynamic Random Access Memory)335と、SDRAM314からDRAM335への所定のデータのDMA転送を行うDMAコントローラ340とを備える。VDP320およびDMAコントローラ340,DRAM335は、VDP−ASIC(Application Specified IC)820として1つのチップに一体に回路形成されている。

In addition to the

上述したCPU312,SDRAM314,制御ROM316,VDP320,DMAコントローラ340,DRAM335,キャラクタROM330は、表示制御装置30に設けられたバス305にそれぞれ接続されている。

The

CPU312は、主制御装置20などの他の機器からの割り込みの受け付けを制御するINTフラグ313を有し、INTフラグ313がリセットされた状態(ローレベル)では「割り込み禁止状態」となり、INTフラグ313がセットされた状態(ハイレベル)では「割り込み許可状態」となる。つまり、「割り込み許可状態」のCPU312は、主制御装置20からセレクト信号#SELおよび書き込み信号#WRを受け、データ信号DATAに出力された表示コマンドを、バス305を介して受け取ることができる。一方、「割り込み禁止状態」のCPU312は、主制御装置20からの表示コマンドを受信することができない。

The

CPU312は、表示態様の制御処理を実行することによって、動画像の1フレーム毎の描画指示データを生成し、生成した描画指示データをVDP320に出力する。描画指示データとは、VDP320がキャラクタROM330などに記憶された画像データを用いてRGBデータを生成するためのデータであり、画像データのアドレスや表示位置,色などを指示するデータである。

The

CPU312は、表示態様の制御処理の合間に、外部画像データの生成処理を実行する。この外部画像データの生成処理とは、キャラクタROM330から所定の画像データを読み出し、その画像データにモーフィング処理などの画像処理を施し、その画像処理後の画像データを外部画像データとしてSDRAM314に書き込む処理である。なお、制御ROM316に制御プログラムの他に画像データが記憶されている場合には、外部画像データの生成処理において、キャラクタROM330に記憶された画像データではなく、制御ROM316に記憶された画像データを基に外部画像データを生成することとしても良い。

The

SDRAM314に記憶された外部画像データは、DMAコントローラ340によってDRAM335にDMA転送される。DRAM335に記憶された外部画像データは、VDP320によって読み出され、RGBデータの生成に用いられる。

The external image data stored in the

CPU312が外部画像データの生成処理を実行するため、キャラクタROM330の容量をいたずらに増加することなく、外部画像データを用いた新たな態様の動画表示を追加することができる。また、CPU312のソフトウェアを更新することによって、VDP320のハードウェアを開発し直すことなく、外部画像データを用いた新たな態様の動画表示を追加することができる。

Since the

DMAコントローラ340は、CPU312からのDMA転送データを記憶するレジスタ342を有する。図5は、DMAコントローラ340のレジスタ342の構成を模式的に示す説明図である。レジスタ342は、DMA転送先であるDRAM335のアドレスを記憶する転送先設定レジスタと、DMA転送元であるSDRAM314のアドレスを記憶する転送元設定レジスタと、DMA転送を行う外部画像データのデータ容量を記憶する総転送容量設定レジスタと、DMA転送を分割して行う際の一転送単位のデータ容量を記憶する単位転送容量設定レジスタとが設けられている。

The

このレジスタ342には、CPU312によってDMA転送データが書き込まれ、DMAコントローラ340は、CPU312からDMA転送の開始指示を受けると、レジスタ342に記憶されたDMA転送データに基づいてDMA転送を行う。DMAコントローラ340は、後述するように、主制御装置20が一出力単位の表示コマンドを出力している時間より短い時間で転送可能な転送単位に分割してDMA転送を行う。なお、一出力単位の一出力とは、主制御装置20がCPU312に対して一度に処理可能なデータ量の出力である。

DMA transfer data is written into the

DMAコントローラ340のレジスタ342に記憶されたDMA転送データを書き換えることによってDMA転送の分割単位を変更することができるため、パチンコ機10のシステム構成に応じて最適な転送単位でDMA転送を分割して行うことができる。なお、レジスタ342の各レジスタの構成は、上記の構成に限るものではなく、「総転送容量設定レジスタ」や「単位転送容量設定レジスタ」の一方を、DMA転送の分割数を記憶する「分割回数設定レジスタ」に代えた構成としても良い。

Since the DMA transfer division unit can be changed by rewriting the DMA transfer data stored in the

VDP320は、1フレームの描画指示データに基づいて、キャラクタROM330やDRAM335から画像データを読み出し、読み出した画像データを用いて1フレームの映像信号を生成しLCD35に出力する。LCD35は、1フレームの映像信号に基づいて1フレームの画像表示を行う。この1フレーム毎の画像表示を繰り返し行うことによって、LCD35では遊技の進行に応じた動画像の表示が行われる。前述のLCD35において特定図柄画像やバックグラウンド画像BG,キャラクタ画像CRを表示するためのRGBデータの生成には、キャラクタROMに予め記憶されている画像データの他、CPU312で生成された外部画像データ,VDP320で画像処理された画像データなどが用いられる。

The

A−(3).表示制御プロセッサ310における表示コマンドの受信:

次に、表示制御プロセッサ310における表示コマンドの受信について説明する。図6は、表示制御プロセッサ310における表示コマンドの受信の様子を示す説明図である。

A- (3). Reception of display command in display control processor 310:

Next, reception of a display command in the

図6に示すように、表示制御プロセッサ310のCPU312は、主制御装置20が送信した変動コマンド群を受信すると(タイミングt10〜t20)、その変動コマンド群に基づいた図柄変動表示を実現するための表示態様の制御を行う(タイミングt20〜t99)。この際、CPU312は、実現しようとする図柄変動表示に応じて、1フレーム毎の表示態様の制御の合間であるプランク期間中に、前述した外部画像データの生成を行う。ここで、変動コマンド群とは、1回の図柄変動表示に関する図柄変動パターンや各特定図柄画像の種類などを指示する複数の変動コマンドから成り、これらの変動コマンドは、主制御装置20から一出力単位毎に次々と送信される。

As shown in FIG. 6, when the

ブランク期間中に生成された外部画像データは、その後のブランク期間中に、DMAコントローラ340によってDMA転送される。外部画像データのDMA転送は、所定の転送単位に分割して行われ(詳細は後述する)、外部画像データの全データのDMA転送は、その外部画像データがVDP320によってRGBデータの生成に用いられる前に完了する。なお、本明細書において、DMA転送の中断とは、DMAコントローラ340が、DMA転送すべき全データのうち所定の転送単位分だけのDMA転送を行った後、CPU312にバス305を開放しDMA転送を止めることをいう。DMA転送の再開とは、DMA転送が中断された後、DMAコントローラ340が、再びCPU312からバス305の開放を受け、直前のDMA転送の中断までに転送されていないデータのDMA転送を引き続き行うことをいう。

The external image data generated during the blank period is DMA-transferred by the

ここで、フレーム(n)とフレーム(n+1)との間のブランク期間におけるDMA転送中に主制御装置20から保留コマンド群が送信される場合(タイミングt30〜t50)の保留コマンドの受信について詳細に説明する。図7は、図6におけるタイミングt30〜t50の詳細を示す説明図である。ここで、保留コマンド群とは、1回分の図柄変動表示の記憶が増えた際の保留表示に関する保留数などを指示する複数の保留コマンドから成り、これらの保留コマンドは、主制御装置20から一出力単位毎に次々と送信される。この保留コマンドは、実施中の動画像表示とは無関係なタイミングで主制御装置20から送信される。

Here, the reception of the hold command when the hold command group is transmitted from the

図7に示すように、CPU312が、フレーム(n)についての表示態様の制御を終えた後(タイミングt30)、中断されたDMA転送の再開をDMAコントローラ340に指示すると、CPU312のINTフラグ313はリセットされ、CPU312は「割り込み禁止状態」となる(タイミングt40)。転送再開の指示を受けたDMAコントローラ340は、中断していたDMA転送を再開し(タイミングt40)、DMA転送時間Ttの間に、前述したレジスタ342の設定値に基づいて算出されたワード数(例えば、16ビットや32ビット)のDMA転送を行った後、再びDMA転送を中断する(タイミングt40〜t43)。なお、DMA転送中には、CPU312は、バス305をDMAコントローラ340に開放し、全ての処理を停止した状態となる。

As shown in FIG. 7, after the

DMA転送中に主制御装置20から保留コマンド群の送信が開始されると、セレクト信号#SELがリセットされた後(タイミングt41)、コマンド出力時間Tcの間、保留コマンド群における最初の保留コマンドAが、データ信号DATAに出力されるとともに、書き込み信号#WRがリセットされる(タイミングt42〜t44)。DMA転送中は、INTフラグ313がリセットされており、CPU312は保留コマンドAを受信することができない。

When transmission of the pending command group is started from the

ここで、DMA転送時間Ttの値は、「DMA転送時間Tt<コマンド出力時間Tc」の関係とされている。したがって、DMA転送の開始直後に保留コマンドAが出力されたとしても、一転送単位のDMA転送のサイクルが終了した後に、保留コマンドAの出力が継続した状態となる(タイミングt43)。 Here, the value of the DMA transfer time Tt has a relationship of “DMA transfer time Tt <command output time Tc”. Therefore, even if the hold command A is output immediately after the start of the DMA transfer, the output of the hold command A is continued after the end of the DMA transfer cycle of one transfer unit (timing t43).

DMA転送の速度がStビットパーセカンド(bit per second、bps)の場合には、一転送単位のDMA転送では、「St×Tt」ビット(bit)のデータが転送される。つまり、DMAコントローラ340は、所定の転送単位として「St×Tt」ビット単位に分割してDMA転送を行う。なお、この所定の転送単位としては、SDRAM314とDRAM335との間で一度に処理可能なデータ量であるワード単位としても良いし、16ビットや32ビット単位などとしても良い。

When the DMA transfer speed is St bit second (bits per second, bps), data of “St × Tt” bits (bits) is transferred in the DMA transfer of one transfer unit. That is, the

DMAコントローラ340がDMA転送を中断すると、INTフラグ313がセットされ、CPU312が「割り込み許可状態」となる(タイミングt43)。その後、CPU312は、リセットされたセレクト信号#SELを受けて主制御装置20からの割り込みの受け付けを開始し、リセットされた書き込み信号#WRに従って、データ信号DATAに出力された保留コマンドAを受信する(タイミングt43〜t44)。

When the

その後、書き込み信号#WRがセットされるとともに、データ信号DATAにおける保留コマンドAの出力が終了しても(タイミングt44)、セレクト信号#SELはリセットされ続けるため、CPU312は、主制御装置20からの割り込みの受け付けを継続する(タイミングt44〜t45)。その後、コマンド出力時間Tcの間、保留コマンド群における次の保留コマンドBが、データ信号DATAに出力されるとともに、書き込み信号#WRがリセットされ、CPU312は、保留コマンドBを受信する。(タイミングt45〜t46)。

Thereafter, the write signal #WR is set, and even when the output of the hold command A in the data signal DATA is finished (timing t44), the select signal #SEL is continuously reset. The acceptance of the interrupt is continued (timing t44 to t45). Thereafter, during the command output time Tc, the next pending command B in the pending command group is output to the data signal DATA, the write signal #WR is reset, and the

その後、主制御装置20が保留コマンド群の送信を終え、セレクト信号#SELがセットされると、CPU312は、主制御装置20からの割り込みの受け付けを終了する(タイミングt47)。その後、CPU312は、受信した保留コマンドの解析や、完了していないDMA転送の再開などを行った後(タイミングt50)、受信した保留コマンドを反映させたフレーム(n+1)の表示態様の制御処理を行う。

Thereafter, when

次に、DMA転送の転送容量と所要時間の関係の一例について説明する。図8は、DMA転送の転送容量と所要時間の関係の一例を示す説明図である。なお、図7に示したDMA転送は、図8において分割して行われるDMA転送のうちの3番目に行われる一転送単位のDMA転送に相当する。 Next, an example of the relationship between the transfer capacity of DMA transfer and the required time will be described. FIG. 8 is an explanatory diagram showing an example of the relationship between the transfer capacity of DMA transfer and the required time. Note that the DMA transfer shown in FIG. 7 corresponds to the DMA transfer of one transfer unit that is thirdly performed among the DMA transfers that are divided in FIG.

本実施例では、主制御装置20は、保留コマンド群を80マイクロセカンド(以下、μsと表す)の期間中に出力し、その期間中に2つの保留コマンドA,Bをそれぞれ20μs間出力する。保留コマンドA,Bは、それぞれ1バイトのデータであり、この保留コマンドA,Bで構成される保留コマンド群は、合計2バイトのデータである。

In the present embodiment,

CPU312は、クロック周波数が133メガヘルツ(以下、MHzを表す)であり、287.4μsのブランク期間の間に外部画像データの生成やDMA転送の指示などの処理を行う。このブランク期間は、LCD35に対する垂直方向のSYNC信号のブランク期間に同期した期間である。なお、LCD35は、9インチの表示領域を有し、垂直表示ドットが328ドットであり、垂直総ドットが334ドットであり、水平表示ドットが536ドットであり、水平総ドットが624ドットであり、ドットクロック周波数が13.026MHzである。

The

DMAコントローラ340は、32ビット長のデータ容量あたり100ナノセカンド(以下、nsと表す)を1サイクルとして、SDRAM314からDRAM335へのDMA転送を実行する。

The

本実施例では、「DMA転送時間Tt<コマンド出力時間Tc」とするため、一転送単位の所要時間であるDMA転送時間Ttは、「コマンド出力時間Tc=20μs」よりも短い12.8μsに設定されている。この間に、DMAコントローラ340は、一転送単位の転送容量として、「((12.8μs)×((32ビット)/(100ns)))=4096ビット」、すなわち512バイトのデータをDMA転送することができる。なお、CPU312は、少なくとも「(20μs)−(12.8μs)=(7.2μs)」の間に保留コマンドAを受信することができる。

In this embodiment, since “DMA transfer time Tt <command output time Tc”, the DMA transfer time Tt, which is the time required for one transfer unit, is set to 12.8 μs, which is shorter than “command output time Tc = 20 μs”. Has been. During this period, the

例えば、データ容量が64×64バイト(すなわち4096バイト)の外部画像データをDMA転送する場合には、DMAコントローラ340は、一転送単位のDMA転送を8回実行することによって、その外部画像データのDMA転送を終えることができる。この場合には、DMA転送の合計所要時間は102.4μsであり、このDMA転送の途中に、保留コマンドの割り込み確認処理や、保留コマンドの受信処理を実行したとしても、1回のブランク期間である287.4μsの間に、その外部画像データのDMA転送を終えることができる。なお、分割したDMA転送の一部が、1回のブランク期間中に終えることができない場合には、次回以降のブランク期間に残りのDMA転送を行えば良い。

For example, when external image data having a data capacity of 64 × 64 bytes (that is, 4096 bytes) is DMA-transferred, the

DMAコントローラ340は、全データのDMA転送を終えると、DMA転送の完了をCPU312に通知する。その後、CPU312は、DMA転送の必要がある場合には、再びDMA転送の設定を行う。

When the DMA transfer of all data is completed, the

以上説明したパチンコ機10によれば、一出力単位の保留コマンドが出力される時間よりも、一転送単位のDMA転送が行われる時間の方が短時間であるため、DMA転送中に保留コマンドの出力が開始され終了してしまう事態を回避することができる。その結果、DMA転送中に保留コマンドの出力が開始された場合であっても、そのDMA転送の一転送単位の終了後に再稼動するCPU312は、その保留コマンドを受け取ることができる。したがって、実施中の動画像表示とは無関係なタイミングで主制御装置20から出力される保留コマンドの取りこぼしを回避しつつ、表示制御プロセッサ310側のSDRAM314からVDP320側のDRAM335へのDMA転送を実現することができる。

According to the

また、実施中の動画像表示とは無関係なタイミングで主制御装置20から出力される保留コマンドの取りこぼしを回避しつつ、表示制御プロセッサ310で生成したデータ量が比較的大きなビットマップデータなどの外部画像データをDMA転送することができる。

Also, external data such as bitmap data having a relatively large amount of data generated by the

また、CPU312は、DMAコントローラ340のレジスタ342に所定のDMA転送データを書き込むことによって、前述した一転送単位に分割してDMA転送をDMAコントローラに行わせることができる。そのため、主制御装置20やLCD35の仕様変更を実施する場合であっても、表示制御装置30におけるソフトウェアおよびハードウェアの大幅な仕様変更を行うことなく、変更後の仕様に適したDMA転送データの設定値を書き込むように制御プログラムを変更することによって、保留コマンドの取りこぼしを回避しつつDMA転送を実現することができる。その結果、主制御装置20やLCD35の仕様変更を実施する際の開発工数を減らすことができる。

In addition, the

B.その他の実施形態:

以上、本発明の実施の形態について説明したが、本発明はこうした実施の形態に何ら限定されるものではなく、本発明の趣旨を逸脱しない範囲内において様々な形態で実施し得ることは勿論である。例えば、本発明の表示制御装置30を搭載する遊技機は、パチンコ機に限るものではなく、スロットマシンなどの画像表示装置を備えた遊技機に適用しても良い。また、実施中の動画像表示とは無関係なタイミングで主制御装置20から出力される表示コマンドは、保留コマンドに限るものではないことは勿論である。また、CPU312のメインメモリや、VDP320側の外部画像データを記憶するメモリは、SDRAM314やDRAM335に限るものではなく、他のRAMを適用しても良い。また、画像表示装置は、LCDに限るものではなく、CRT(Cathode Ray Tube)ディスプレイ、EL(Electro Luminescent)ディスプレイなどであっても良い。

B. Other embodiments:

As mentioned above, although embodiment of this invention was described, this invention is not limited to such embodiment at all, Of course, it can implement with various forms within the range which does not deviate from the meaning of this invention. is there. For example, a gaming machine equipped with the

また、本実施例では、DMAコントローラ340は、CPU312からのDMA転送の開始指示を受けてDMA転送を開始するが、CPU312からのDMA転送データの書き込みを契機にDMA転送を開始するようにしても良い。この場合には、DMAコントローラ340は、垂直SYNC信号のブランク期間に基づいて、CPU312にバス305の開放要求を行うこととしても良い。これによって、CPU312はDMA転送データの書き込みの後に開始指示を行う必要がないため、CPU312の処理効率を向上させることができる。

In this embodiment, the

10...パチンコ機

11...外枠

12...内枠

13...遊技板

14...ガラス枠

15...ハンドル

20...主制御装置

30...表示制御装置

35...LCD

40...音声制御装置

45...スピーカ

50...ランプ制御装置

55,56,57,58,59...電飾

61...入賞

65...スイッチ

66...ソレノイド

70...払出制御装置

90...カードユニット

305...バス

310...表示制御プロセッサ

312...CPU

313...INTフラグ

314...SDRAM

316...制御ROM

320...VDP

330...キャラクタROM

335...DRAM

340...DMAコントローラ

342...レジスタ

DESCRIPTION OF

40 ...

313 ...

316 ... Control ROM

320 ... VDP

330 ... Character ROM

335 ... DRAM

340 ...

Claims (3)

前記複数の図柄画像を変動させて表示するパターンを指示する変動コマンドを出力する主制御装置と、

前記主制御装置から前記変動コマンドを受け取り、該変動コマンドに基づいて前記画像表示装置に表示される動画像を制御する表示制御装置と

を備え、

前記表示制御装置は、

データをやり取りするバスに接続され、前記変動コマンドに応じた動画像フレームの描画を指示する描画指示データを生成する表示制御プロセッサと、

前記表示制御プロセッサから前記描画指示データを受け取り、該描画指示データに基づいて前記動画像フレームを描画する画像表示プロセッサと、

前記バスに接続され、データを記憶する第1および第2のメモリと、

前記バスに接続され、前記第1のメモリから前記第2のメモリへのデータのダイレクトメモリアクセス転送を行う転送コントローラと

を含み、

前記表示制御プロセッサは、前記動画像フレームの描画に用いられる外部画像データを生成し、該外部画像データを前記第1のメモリに書き込む手段を含み、

前記転送コントローラは、前記外部画像データが前記第1のメモリに書き込まれた場合、該外部画像データの前記第1のメモリから前記第2のメモリへのダイレクトメモリアクセス転送を、前記画像表示装置に対する垂直同期信号のブランク期間を契機に、前記主制御装置が一出力単位の前記変動コマンドを出力している時間より短い時間で転送可能な転送単位に分割して実行する手段を含み、

前記画像表示プロセッサは、前記描画指示データに基づいて、前記第2のメモリにダイレクトメモリアクセス転送された外部画像データを前記第2のメモリから読み出し、該外部画像データを用いて前記動画像フレームを描画する手段を含む、遊技機。 A gaming machine that includes an image display device that displays a plurality of symbol images together with a background image and a character image according to the progress of the game, and that executes a game advantageous to the player according to the combination of the symbol images. There,

A main control device that outputs a change command for instructing a pattern to be displayed by changing the plurality of design images;

A display control device that receives the variation command from the main control device and controls a moving image displayed on the image display device based on the variation command;

With

The display control device includes:

A display control processor connected to a bus for exchanging data and generating drawing instruction data for instructing drawing of a moving image frame according to the variation command ;

An image display processor that receives the drawing instruction data from the display control processor and draws the moving image frame based on the drawing instruction data ;

First and second memories connected to the bus for storing data;

Connected to said bus, and transfer controller from the first memory performing direct memory access transfer of data to the second memory

Including

The display control processor includes means for generating external image data used for drawing the moving image frame and writing the external image data in the first memory,

When the external image data is written in the first memory, the transfer controller performs direct memory access transfer of the external image data from the first memory to the second memory to the image display device. Triggered by a blank period of the vertical synchronization signal, the main control unit includes a unit that divides and executes a transfer unit that can be transferred in a time shorter than a time in which the output command of one output unit is output,

The image display processor reads external image data transferred by direct memory access to the second memory from the second memory based on the drawing instruction data, and uses the external image data to read the moving image frame. A gaming machine including means for drawing.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009147748A JP4737470B2 (en) | 2009-06-22 | 2009-06-22 | Game machine |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009147748A JP4737470B2 (en) | 2009-06-22 | 2009-06-22 | Game machine |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003405460A Division JP4452862B2 (en) | 2003-12-04 | 2003-12-04 | Game machine and control method thereof |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009207922A JP2009207922A (en) | 2009-09-17 |

| JP2009207922A5 JP2009207922A5 (en) | 2010-04-15 |

| JP4737470B2 true JP4737470B2 (en) | 2011-08-03 |

Family

ID=41181613

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009147748A Expired - Fee Related JP4737470B2 (en) | 2009-06-22 | 2009-06-22 | Game machine |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4737470B2 (en) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7003027B2 (en) * | 2018-10-24 | 2022-01-20 | 株式会社藤商事 | Pachinko machine |

| JP7305738B2 (en) * | 2018-10-24 | 2023-07-10 | 株式会社藤商事 | game machine |

| JP7044684B2 (en) * | 2018-10-24 | 2022-03-30 | 株式会社藤商事 | Pachinko machine |

| JP7138543B2 (en) * | 2018-10-24 | 2022-09-16 | 株式会社藤商事 | game machine |

| JP7091223B2 (en) * | 2018-10-24 | 2022-06-27 | 株式会社藤商事 | Pachinko machine |

| JP6933625B2 (en) * | 2018-10-24 | 2021-09-08 | 株式会社藤商事 | Pachinko machine |

| JP6952675B2 (en) * | 2018-11-28 | 2021-10-20 | 株式会社藤商事 | Pachinko machine |

| JP6952674B2 (en) * | 2018-11-28 | 2021-10-20 | 株式会社藤商事 | Pachinko machine |

| JP6903627B2 (en) * | 2018-11-28 | 2021-07-14 | 株式会社藤商事 | Pachinko machine |

| JP7210296B2 (en) * | 2019-01-16 | 2023-01-23 | 株式会社藤商事 | game machine |

| JP7101649B2 (en) * | 2019-09-10 | 2022-07-15 | 株式会社藤商事 | Pachinko machine |

| JP7321333B2 (en) * | 2019-09-10 | 2023-08-04 | 株式会社藤商事 | game machine |

| JP7321334B2 (en) * | 2019-09-10 | 2023-08-04 | 株式会社藤商事 | game machine |

| JP7503917B2 (en) * | 2020-03-04 | 2024-06-21 | 株式会社藤商事 | Gaming Machines |

| JP7325462B2 (en) | 2021-02-25 | 2023-08-14 | 株式会社藤商事 | game machine |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6330951A (en) * | 1986-07-25 | 1988-02-09 | Fujitsu Ltd | Data transfer system for communication control processor |

| JPH08155120A (en) * | 1994-12-02 | 1996-06-18 | Sophia Co Ltd | Control device for game machine |

| JP2002186773A (en) * | 2000-12-20 | 2002-07-02 | Sankyo Kk | Device for game |

| JP4004243B2 (en) * | 2001-05-17 | 2007-11-07 | 株式会社ソフィア | Game machine |

-

2009

- 2009-06-22 JP JP2009147748A patent/JP4737470B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009207922A (en) | 2009-09-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4737470B2 (en) | Game machine | |

| JP5119425B2 (en) | Game machine | |

| JP6247867B2 (en) | Game machine | |

| JP2017158624A5 (en) | ||

| JP4452862B2 (en) | Game machine and control method thereof | |

| JP6231821B2 (en) | Game machine | |

| JP2005052422A (en) | Display controller for game machine, and the game machine | |

| JP6353202B2 (en) | Game machine | |

| JP2005027796A (en) | Game machine and image display device thereof | |

| JP2002239150A (en) | Game machine | |

| JP6276946B2 (en) | Game machine | |

| JP2006075457A (en) | Game machine | |

| JP4512796B2 (en) | Game machine | |

| JP2002210139A (en) | Game machine and game machine control program | |

| JP6231822B2 (en) | Game machine | |

| JP2010099512A (en) | Display controller for game machine, and game machine | |

| JPH08289961A (en) | Data transmission device for pachinko machine | |

| JP4837059B2 (en) | Game machine | |

| JP2017143852A (en) | Game machine | |

| JP6231973B2 (en) | Game machine | |

| JP4803762B2 (en) | Game machine | |

| JP2005168959A (en) | Game machine | |

| JP2001149558A (en) | Game machine and its display control method | |

| JP5285048B2 (en) | Pachinko machine | |

| JP5111899B2 (en) | Display control device for gaming machine |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090721 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100303 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110322 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110419 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140513 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |