以下、本発明の実施の形態を図面に基づいて詳細に説明する。尚、各実施形態においては、薄膜半導体装置として、トップゲート型の薄膜トランジスタを備えた薄膜半導体装置を例示し、その製造方法から順に実施形態を説明する。

<第1実施形態>

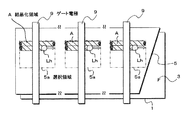

図1は第1実施形態の薄膜半導体装置の製造方法を示す断面工程図である。ここではこの図1に基づいて第1実施形態の製造方法を説明する。

先ず、図1(1)に示すように、薄膜半導体装置を形成する基板1を用意する。この基板1としては、非晶質基板のガラス、石英、サファイア基板、プラスチック基板、さらにはアルミニウムやステンレス等の金属基板等を用いる。そして、この基板1の一主面上に、当該基板1への熱伝導を防止するための絶縁性のバッファー層3を設ける。尚、基板1およびバッファー層3の詳細な構成については、別項目にて後述する。

次に、基板1の一主面側上に、バッファー層3を介して非晶質の半導体薄膜5を形成する。ここでは、成膜温度を低く抑えることが可能な成膜方法を採用することとし、例えば一般的なプラスチックの耐熱温度である250℃以下に成膜温度が抑えられる、PE−CVD(plasma enhancement-chemical vapor deposition)法による非晶質シリコンからなる半導体薄膜5の形成を行う。

PE−CVD法による半導体薄膜5の形成の一例を示す。

成膜ガスおよび流量:SiH4(10vol%)/H2=50sccm、

成膜雰囲気内圧力 :200mTorr、

基板温度 :130℃、

RFパワー :20W

成膜時間 :6.5分

以上により、膜厚50nmの半導体薄膜5を成膜する。この半導体薄膜5は、多量の水素が含有されたいわゆる水素化非晶質シリコン(a−Si:H)からなる。

尚、半導体薄膜5の形成は、成膜温度を低く抑えられる方法であれば上述したPE−CVD法に限定されることはなく、塗布法によって行っても良い。この場合、ポリシラン化合物を溶媒に混ぜた混合物を、バッファー層3を介して基板1上に塗布成膜し、その後、乾燥、アニールを施すことにより半導体薄膜5を形成する。そして、先のPE−CVD法や、ここで示した塗布法などの成膜温度が低く抑えられた成膜方法では、いずれの場合にも成膜条件により多少の変動はあるが、0.5atoms%〜15atoms%程度の水素を含有した水素化非晶質シリコン(a−Si:H)からなる半導体薄膜5が得られる。

次に、半導体薄膜5上にゲート絶縁膜7を形成する。このゲート絶縁膜7は、酸化シリコンからなるもので良く、通常のPE−CVDによる公知の方法で成膜可能であり、この他にも塗布型の絶縁層として公知のSOG等の成膜を行っても良い。

次に、ゲート絶縁膜7上にゲート電極9を形成する。ここでは、先ず、スパッタ法または蒸着法により、例えばアルミニウムからなる電極材料層を成膜し、次にリソグラフィー法によってこの電極材料層上にレジストパターンを形成する。その後、このレジストパターンをマスクに用いて電極材料層をエッチングすることにより、ゲート電極9をパターン形成する。尚、ゲート電極9の形成は、このような手順に限定されることはなく、例えば金属微粒子を塗布して印刷する手法であっても良い。

またゲート電極9の形成に続けて、ゲート電極9をマスクに用いてゲート絶縁膜7をパターンエッチングし、ゲート電極9の両脇に半導体薄膜5を露出させる。

次に、図1(2)に示すように、半導体薄膜5に対して、ゲート電極9をマスクとした自己整合的な不純物導入を行う。この不純物は、この半導体装置5を用いて構成される薄膜トランジスタのソース・ドレインを構成するものである。ここでは、イオンインプラ、プラズマドーピング等公知の手法を用いることができる。またこの他にも、市販の塗布型のドーパント溶液を用いて方法や、LIMPID(Laser-induced Melting of Predeposited Impurity Doping)法を適用しても良い。

例えば、LIMPID法を適用した不純物導入を行う場合には、先ず、不純物を含むドーピングガスのプラズマに半導体薄膜5を曝す。この際、例えばPE−CVD装置中にドーピングガスとしてPH3(0.5vol%)/H2:20sccmを流し、処理雰囲気内の圧力を475mTorr、基板温度を150℃、RFパワーを20Wに設定し、照射時間3分の処理を施す。これにより、ゲート電極9をマスクとして、半導体薄膜5の露出面上に選択的に不純物イオンを吸着させる。

以上の後、図1(3),図1(4)に示すように、ゲート電極9をマスクにして半導体薄膜5にレーザ光Lhを照射することにより、レーザ光Lhの照射部を結晶化して結晶化領域Aを形成するとともに、この結晶化領域Aにおける不純物を活性化させるアニール工程を行う。

このアニール工程においては、半導体薄膜5に対するレーザ光Lhの照射位置を、所定の移動速度vtで移動させる。この際、レーザ光Lhの照射は連続照射とする。これにより、半導体薄膜5中において水素イオンをガス化膨張させることなく、当該レーザ光Lhの照射部、すなわち結晶化領域Aから余剰水素を除去する。

ここで、半導体薄膜5に照射するレーザ光Lhの波長は、半導体薄膜5の膜厚とその吸収係数に基づき、半導体薄膜5の表面層のみで吸収されずに深さ方向広範囲にわたって吸収される程度に、比較的吸収係数が小さくなる波長が選択される。すなわち、厚さ50nmの非晶質シリコンからなる半導体薄膜5を例にとると、波長350nm〜470nmのレーザ光Lhが好ましく用いられる。これにより、半導体薄膜5の表面層のみでレーザ光Lhが吸収されて急激に昇温し、膜中に含まれる水素の膨張により半導体薄膜5が破壊されるアブレーションを防止する。

このような波長のレーザ光Lhの発振源としては、例えばGaN系の化合物半導体レーザ発振器、さらにはYAGレーザ発振器が用いられる。

また、半導体薄膜5に対するレーザ光Lhの照射位置の移動速度vtは、レーザ光Lhの照射によって加熱された半導体薄膜5の熱が基板1に影響を及ぼすことなく放熱されて半導体薄膜5が結晶化する程度に設定される。このため、半導体薄膜5の移動速度vtは、レーザ光Lhの照射エネルギーを考慮した値に設定され、例えば上述した例においてレーザ光のエネルギーが1J/cm2程度である場合、半導体薄膜5に対するレーザ光Lhの照射位置の移動速度vtを0.1m/秒〜10m/秒に設定する。

尚、半導体薄膜5に対するレーザ光Lhの照射位置の移動は相対的でよく、固定されたレーザ光Lhの照射位置に対して半導体薄膜5が形成された基板1側を移動させても良いし、固定された基板1に対してレーザ光Lhの照射位置を移動させても良い。また、基板1とレーザ光Lhの照射位置との両方を移動させても良い。

そして、半導体薄膜5に対するレーザ光Lhの照射スポット径は、溶融した半導体材料の冷却過程における核の生成確率から決められる。すなわち、レーザ光Lhの照射によって溶融した半導体材料部分においては、レーザ光Lhの照射位置の移動によって照射位置がずれた部分から順次冷却が開始される。そして、同時に冷却が開始された位置で、最も速く結晶の核が形成された部分から結晶が成長する。したがって、このときの核生成確率が1event/sec程度であれば、冷却開始部分から一方向に結晶成長が進むため、過剰な水素はレーザーのスキャン方向側一方向に押し出されていくことになる。

このため、上述した例においては、半導体薄膜5に対するレーザ光Lhの照射スポット径を10μmを越えない範囲とすることで、核生成確率を1event/sec程度に抑えることが好ましい。尚、生産性を考慮すると、照射スポット径はできるだけ大きいことが好まし。このことからすれば、照射スポット径は10μmを越えない範囲でできるだけ大きい値に設定されることとし、生産性を考慮した現実的なスポット径の下限は、1nm程度となる。

またさらに以上のようなレーザ光Lhは、半導体薄膜5に対して連続照射されるが、これにより、レーザ光Lhの照射部における余剰水素がレーザ光Lhの移動に伴って半導体薄膜5a中を移動し続け、結晶化領域A中から余剰水素が除去されることになる。そして、レーザ光Lhの照射終了端に余剰水素bを析出させる。尚、余剰水素bはボイドの状態で析出する。

ここで、半導体薄膜5に対するレーザ光Lhの連続照射とは、レーザ光Lhの移動に際して休止無く完全に連続である場合と共に、レーザ光Lhの照射によって溶融した半導体薄膜5部分の凝固が完全に完了しない程度の休止が入る場合を含むこととする。このため、このような条件を満たせば、照射時間よりも短い休止時間が入る場合も連続照射に含まれ、一例として半導体薄膜5部分への100nsの照射時間に対して10〜20ns程度の休止が入る場合も連続照射に含むこととする。尚、照射時間に対する休止時間は、半導体薄膜の材質および膜厚、レーザ光Lhのエネルギー密度、等によって適宜設計される。このような休止時間を入れることにより、レーザ光Lh照射による基板1への熱的影響を抑えることができる。尚、エキシマレーザ光は完全なパルス波であり、300Hz程度のパルス波であれば、25nsの照射時間に対して3300ns程度の休止が入ることになる。このため、エキシマレーザ光では、レーザ光Lhの照射によって溶融した半導体薄膜5部分の凝固が完全した状態で次のパルス照射が行われることになるため、上述したいわゆる「連続照射」を行うことはできない。

また以上のようなレーザ光Lhの照射は、薄膜トランジスタの形成部分を含む、半導体薄膜5に設定した選択領域5aのみに対して選択的に行うこととする。これにより、選択領域5aへのレーザ光Lhの照射による半導体薄膜5の部分的な発熱がその周囲に放熱され、基板1に対して発熱の影響を及ぼすことを防止する。尚、この選択領域5aとしては、薄膜トランジスタの形成部分以外に、この半導体薄膜5を用いて抵抗素子や容量素子などが形成される領域や、この半導体薄膜5を用いて配線が形成される領域であり、低抵抗化が必要な領域であることとする。

尚、照射スポット径が、各選択領域5aにおける結晶化領域Aの幅(例えばソース・ドレイン11の幅)に達しない場合には、選択領域5aに対して複数列のレーザ光Lh照射を行うこととする。

ここで特に、選択領域5aのうち、図示した薄膜トランジスタの形成部分に相当する選択領域5aにおける上記レーザ光Lhの照射は、マスクとなるゲート電極9に重なる位置をレーザ光Lhの照射開始位置とし、この照射開始位置からゲート電極9から選択領域5aの端部方向に向かってレーザ光Lhの照射位置を移動させることとする。

このため先ず、図1(3)に示すようにゲート電極9に重なる位置をレーザ光Lhの照射開始位置とし、この照射開始位置から選択領域5aの一方側端部に向かってレーザ光Lhの照射位置を所定の移動速度vtで移動させる。その後、図1(4)に示すように、再びゲート電極9に重なる位置をレーザ光Lhの照射開始位置とし、この照射開始位置から選択領域5aの他方側端部に向かってレーザ光Lhの照射位置を所定の移動速度vtで移動させる。

以上のようなレーザ光Lhの照射により、半導体薄膜5の選択領域5aを結晶化した結晶化領域Aを形成すると共に、結晶化領域5a中の不純物を活性化させ、さらに結晶化領域A中の余剰水素を除去する脱水素を行う。そして特に、ゲート電極9脇の選択領域5aは、ゲート電極9の両脇の半導体薄膜5部分を結晶化すると共にこの部分の不純物を活性化させ、さらに結晶化領域A中の余剰水素が除去されたソース・ドレイン11となる。また、ゲート電極9の下方には、レーザ光Lhを照射せずに水素化非晶質シリコン(a−Si:H)のまま残したチャネル部13が形成される。そしてこれにより、非晶質−結晶質混成の薄膜トランジスタTFTを得る。さらに、上述したようにゲート電極9に重なる位置をレーザ光Lhの照射開始位置としてレーザ光Lhを移動させることにより、ゲート電極9から離れたソース・ドレイン11の端部に余剰水素bを析出させる。

尚、以上のような半導体薄膜5に対するレーザ光Lhの照射は、複数の選択領域5aに対して同時に行う様にすることが好ましい。つまり、図2の平面図に示すように、基板1上に設定配列された複数の選択領域5aに対してレーザ光Lhを同時に多点照射することにより複数の結晶化領域Aを同時に形成することが、生産性を考慮した場合には好ましい方法である。

このようなレーザ光Lhの多点照射を実現するためには、レーザ光Lhの発振源として半導体レーザ発振器が好適に用いられる。半導体レーザ発振器は、エキシマレーザやYAGレーザなどの他のレーザ発振器と比較して非常に小型であるため、1つの装置内に複数配置が可能であり、かつ連続照射で定格40mWの出力が可能である。尚、このような半導体レーザ発振器を用いたレーザ装置の構成は、別項目にて後述する。

ところで、以上のようにレーザ光Lhを所定速度で移動させた連続照射では、図3の平面図に示すように、結晶化領域Aに半導体材料の結晶粒aが形成される。すなわち、結晶化領域Aにおいては、図中矢印で示すレーザ光Lhの移動方向に凸となる三日月形の結晶粒aが、レーザ光Lhの移動方向に沿って配列される。尚、図3においては、レーザ光Lh照射の2列分を図示している。

ここで、PE−CVD法で成膜した膜厚50nmの半導体薄膜5a(a−Si:H)に対して、移動速度vt=8.2m/秒で1J/cm2相当のエネルギーでレーザ光Lhを照射したところ、幅800nm×移動方向長さ100nm程度の三日月状の結晶粒aが並んだ多結晶膜が得られることが確認された。またレーザ光の照射終了端には、半導体薄膜5aの結晶領域Aの端部に余剰水素bがボイド状に析出した欠陥が見られた。

またレーザ光Lhの照射開始端にもレーザ光の移動と反対方向に凝固が進んだ領域に部分的に同様の欠陥が見られた。したがって、図1(3)、(4)を用いて説明したように、薄膜トランジスタの形成部分では、ゲート電極9に重なる位置をレーザ光Lhの照射開始位置とすることで、非晶質のチャネル部13と結晶化領域Aからなるソース・ドレイン11との境界付近に余剰水素bのボイドが析出することを防止している。

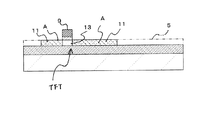

そして以上のようなレーザ光照射を行って後には、図4に示すように、半導体薄膜5を、その結晶化領域Aを残して所定形状にパターンエッチングする。またこれにより非晶質−結晶質混成の薄膜トランジスタTFTの素子分離を行う。この場合、図示したように、結晶化領域Aの端部(ソース・ドレイン11の端部)に析出させた余剰水素(b)をエッチングによって除去しても良く、また余剰水素(b)を結晶化領域Aの端部に残しても良い。

尚、図4を用いて説明した半導体薄膜5のパターニング工程で、余剰水素(b)を結晶化領域Aの端部に残すようにした場合には、ソース・ドレイン11の外側部分に余剰水素(b)によるバブル状の欠陥が数多く存在している構造の薄膜トランジスタが形成されることになる。

以上のようにして形成された薄膜トランジスタTFTをスイッチング素子として用いた表示装置として、例えば液晶表示装置を作製する場合には、さらに以下の工程を行う。

先ず、図5(1)に示すように、薄膜トランジスタTFTを覆う状態で、基板1上に層間絶縁膜21を形成する。次に、この層間絶縁膜21に薄膜トランジスタTFTのソース・ドレイン11に達する接続孔21aを形成する。そして、この接続孔21aを介してソース・ドレイン11に接続された配線23を、層間絶縁膜21上に形成する。

次いで、配線23を覆う状態で平坦化絶縁膜25を形成し、配線23に達する接続孔25aを平坦化絶縁膜25に形成する。次に、この接続孔25aと配線23を介してソース・ドレイン11に接続された画素電極27を、平坦化絶縁膜25上に形成する。この画素電極27は、液晶表示装置の表示タイプによって透明電極または反射電極として形成する。尚、図面は1画素の要部断面となっている。

その後、ここでの図示は省略したが、画素電極27を覆う配向膜を平坦化絶縁膜上に形成し、駆動基板29を完成させる。

その後、図5(2)に示すように、駆動基板29に対向配置させる対向基板31を用意する。この対向基板31は、透明基板33上に共通電極35を設け、さらにここでの図示を省略した配向膜で共通電極35を覆ってなる。尚、共通電極35は透明電極からなることとする。

そして、駆動基板29と対向基板31とを、画素電極27と共通電極35とを向かい合わせた状態で、スペーサ37を介して対向配置する。そして、スペーサ37によって所定間隔に保たれた基板29,31間に液晶相LCを充填封止し、液晶表示装置を完成させる。

尚、上記構成の駆動基板29を用いて有機EL表示装置を作製する場合には、駆動基板29に設けられた画素電極を陽極(または陰極)とし、この画素電極上に正孔注入層、発光層、電子輸送層などの必要機能を有する有機層を積層させ、さらに有機層上に共通電極を陰極(または陽極)として形成することとする。

以上のような製造方法によれば、図1(3)および(4)を用いて説明した半導体薄膜5を結晶化するためのアニール工程で、半導体薄膜5に対するレーザ光Lhの照射位置を所定速度で移動させながら連続照射することにより、レーザLh光の照射部における余剰水素bがレーザ光Lhの移動に伴って半導体薄膜5中を移動し続けることになる。つまり、膜中の水素は膜中を移動してレーザ光の照射部から除去されるのであり、最終的にはレーザ光Lhの照射端部に析出する。このため、半導体薄膜5中の水素が、レーザ光Lhの照射によって加熱され水素ガスとして膜中において膨張して放出され、これにより半導体薄膜5の膜破壊を起こすことが防止される。したがって、さらに活性化効率の高い結晶領域からなるソース・ドレイン11が得られる。

そしてレーザ光Lh照射の前処理として脱水素処理を行わなくても、膜破壊を防止しつつレーザ光Lhの照射部の結晶化が行われため、レーザ光Lhの照射においてマスクとなるゲート電極9下方の半導体薄膜部5分には、水素化非晶質シリコン(a−Si:H)がそのまま残される。したがって、キャリア移動度が保たれた非晶質のチャネル部13が得られる。

以上により、非晶質領域で構成されたチャネル部13におけるキャリア移動度が高く、しかも結晶化領域で構成されたソース・ドレイン11の活性化効率が高い、非晶質−結晶質混成の薄膜トランジスタTFTを、低温プロセスで得ることが可能である。

またこの結果、基板1としてプラスチック基板を用いることが可能になり、例えばロール・ツー・ロールでの設備費用を抑えた量産プロセスを実現することができる。尚、ロール・ツー・ロールプロセスでの製造を行う場合には、プラスチィックの基板1の厚さは1mm以下であることが望ましい。

しかも、上記のアニール工程では、レーザ光Lhの照射部(すなわち結晶化領域A)から余剰水素bが除去されるものの、結晶化領域A内には適量の水素が残存した状態となる。したがって、本アニール工程により、半導体薄膜5における結晶化領域A中の脱水素と水素化処理とを同時に行うことができる。このことから、高機能の膜半導体装置における製造プロセスの簡略化と、これによる生産性の向上を図ることが可能になる。

<第2実施形態>

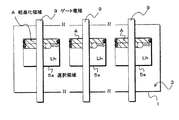

図6は第2実施形態の薄膜半導体装置の製造方法を示す断面工程図である。ここではこの図6に基づいて第2実施形態の製造方法を説明する。

先ず、図6(1)に示すように、第1実施形態において図1(1)を用いて説明したと同様にして、基板1上にバッファー層3を形成する。そして、このバッファー層3上に半導体薄膜パターン5aを形成する。ここでは、この半導体薄膜パターン5aは、第1実施形態で説明した選択領域(5a)と同一形状であることとする。ただし、半導体薄膜パターン5aは、第1実施形態で説明した選択領域(5a)を含む形状であれば良く、選択領域(5a)より大きくても良い。

このような半導体薄膜パターン5aは、成膜温度を低く抑えられる方法で形成されれば良く、第1実施形態と同様にして成膜した半導体薄膜をパターンエッチングして形成しても良い。また、例えば、第1実施形態で説明した塗布法を応用し、必要部分のみに半導体薄膜パターン5aを印刷形成しても良い。したがって、形成された半導体薄膜パターン5aは、第1実施形態の半導体薄膜(5)と同様に、水素を含有した水素化非晶質シリコン(a−Si:H)で構成されることなる。

その後、半導体薄膜パターン5aが形成された基板1の上部にゲート絶縁膜7を介してゲート電極9を形成する。この工程は、第1実施形態において図1(1)を用いて説明したと同様に行って良い。尚、ゲート電極9は、半導体薄膜パターン5aのうち、薄膜トランジスタが形成される半導体薄膜パターン5aの中央を横切るように形成されることとする。

次に、図6(2)に示すように、半導体薄膜パターン5aにゲート電極9をマスクとして自己整合的に不純物を導入する。この工程は、第1実施形態において図1(2)を用いて説明したと同様に行って良い。

その後、図6(3),(4)に示すように、ゲート電極9をマスクにして半導体薄膜パターン5aに対してレーザ光Lhを照射して結晶化するアニール工程を行う。このアニール工程は、第1実施形態において図1(3)および図1(4)を用いて説明したと同様に行い、半導体薄膜パターン5aにレーザ光Lhを照射することにより、レーザ光Lhの照射部を結晶化して結晶化領域Aを形成するとともに、この結晶化領域Aにおける不純物を活性化させ、また結晶化領域A中の余剰水素を除去する脱水素を行う。

そして特に、ゲート電極9脇の半導体薄膜パターン5aにおいては、ゲート電極9の両脇の半導体薄膜パターン5a部分を結晶化すると共にこの部分の不純物を活性化させ、さらに結晶化領域A中の余剰水素が除去されたソース・ドレイン11を形成する。また、ゲート電極9の下方には、レーザ光Lhを照射せずに水素化非晶質シリコン(a−Si:H)のまま残したチャネル部13を形成する。そしてこれにより、非晶質−結晶質混成の薄膜トランジスタTFTを得る。さらに、上述したようにゲート電極9に重なる位置をレーザ光Lhの照射開始位置としてレーザ光Lhを移動させることにより、ゲート電極9から離れたソース・ドレイン11の端部に余剰水素bを析出させる。

またこのアニール工程も、第1実施形態のアニール工程と同様に、複数の結晶化領域Aに対して同時に行う様にすることが好ましい。つまり、図7の平面図に示すように、基板1上に形成された複数の半導体薄膜パターン5aに対して、レーザ光Lhを同時に多点照射することにより複数の結晶化領域Aを同時に形成することが、生産性を考慮した場合には好ましい方法である。ただしこの場合、基板1に対するレーザ光Lh照射による熱的影響を防止するために、半導体パターン5aを外れて、基板1上のバッファー層3にレーザ光Lhが照射されることのないようにする。

また、以上の様にして形成された非晶質−結晶質混成の薄膜トランジスタTFTをスイッチング素子として用いた表示装置として、例えば液晶表示装置を作製する場合には、第1実施形態で図5を用いて説明したと同様の工程を行う。

以上のような第2実施形態の製造方法であっても、図6(3)、(4)を用いて説明した半導体薄膜パターン5aを結晶化するためのアニール工程を、第1実施形態のアニール工程と同様に行うことで、製造プロセスにおいての基板1に対する熱的影響を低く抑えることが可能になり、第1実施形態と同様の効果を得ることができる。

<基板>

次に、以上の第1実施形態および第2実施形態で代表される本発明の薄膜半導体装置の製造方法に用いられる基板1の構成を説明する。

上述したように、本発明の薄膜半導体装置の製造方法では、アニール工程での基板に対する熱的影響が低く抑えられるため、基板として用いられる材料に対して特に高い耐熱性が求められることはない。このため、基板としては、非晶質基板のガラス、石英、サファイア基板、プラスチック基板、さらにはアルミニウムおよびステンレスのような金属基板等、多様な材質が用いられる。

このうち、金属基板を用いる場合には、金属基板における薄膜半導体装置の形成面に、無機材料からなる絶縁性のバッファー層を形成し、これを基板1とする。バッファー層3としては、珪素酸化物や、珪素窒化物、珪素炭化物の他、Ti,Al,Zr,Hf等の酸化膜を用いても構わない。これらのバッファー層3の形成は、CVD、スパッタ、および蒸着等の公知の真空成膜技術によって行うことができる。また、バッファー層としては、無機系SOG膜や有機系SOG等の層間絶縁膜等として通常使用される絶縁層を用いることもできる。さらに金属膜の陽極酸化で形成される誘電体膜や、ゾルゲル法やMOD(Metal Organic Deposition)法等の公知の技術で成膜された膜であっても良い。

また、プラスチック基板を用いる場合には、上述した薄膜半導体装置の製造をロール・ツー・ロールプロセスで行うことが可能である。この場合、プラスチィックの基板1の厚さは1mm以下であることが望ましい。

プラスチック基板を構成する有機材料としては、PET(ポリエチレンテレフタレート)、ポリエチレンナフタレートあるいはポリカーボネートなどのポリエステル類、ポリプロピレンなどのポリオレフィン類、ポリフェニリンスルフィドなどのポリフェニリンスルフィド類、ポリアミド類、芳香族ポリアミド類、ポリエーテルケトン類またはポリイミド類、アクリル系樹脂、PMMA(ポリメタクリル酸メチル)などの高分子材料を用いることができる。この中でも特に、ポリエチレンテレフタレート、アセテート、ポリフェニリンスルフィド、ポリカーボネート、PES(ポリエーテルサルフォン),ポリスチレン,ナイロン,ポリプロピレン,ポリ塩化ビニル,アクリル系樹脂、PMMAなどの汎用的なプラスチック基板を好適に用いることができる。

以上のようなプラスチック基板の厚さは薄い方が好ましく、例えば200μm程度となっている。これにより薄膜半導体装置に柔軟性を付与すると共に、薄膜半導体装置の小型化および薄膜化を図るためである。

また、プラスチック基板を用いる場合には、薄膜半導体装置の形成面に有機系材料からなるコーティング層を介して、無機材料からなる絶縁性のバッファー層3を形成する。バッファー層3は、金属金属基板を用いた場合と同様に、珪素酸化物や、珪素窒化物、珪素炭化物の他、Ti,Al,Zr,Hf等の酸化膜を用いても構わない。そして、コーティング層は、例えば、厚さが10μm程度であり、基板本体であるプラスチック基板よりも熱膨張係数が小さな有機材料により構成されている。またこのコーティング層は、好ましくは、いわゆるハードコーティング材料といわれるような、比較的高温の200℃まである程度の硬化を維持し、高い緻密性と大きい硬度を有する材料を用いて構成されることとする。

このようなコーティング材料としては、光学的もしくは熱的なプロセスにより変形して生じる3次元縮重合によって結合している、アクリル樹脂、エポキシ樹脂、あるいはこれらを含む高分子材料が挙げられる。

このうち、アクリル樹脂を含むコーティング材料としては、アクリル樹脂系の高分子材料もしくはアクリル系樹脂と他の樹脂を含むような複合高分子系プラスチック材料が挙げられる。このようなコーティング材料として、例えば、各種の多官能性アクリレート化合物、例えばエチレングリコールジ(メタ)アクリレート、ネオペンチルグリコールジ(メタ)アクリレート、ビスフェノール−Aジ(メタ)アクリレート、トリメチロールプロパントリ(メタ)アクリレート、ペンタエリスリトールトリ(メタ)アクリレート、ジペンタエリストール等や、或いは2,2-ビス(4´−ヒドロキシフェニル)ヘキサフルオロプロパンまたはそのアルキレングリコールエーテルとイソシアナートアルキル(メタ)アクリレートとを反応させることによって製造する二官能性アクリレート化合物等などが好適に使われる。このとき共重合させられるコモノマーの種類は用途分野により異なり、共重合可能なモノマーはすべて使用できる。

これらのコーティング材料は通常、約100〜1000の分子量をもち単一の不飽和または二、三もしくはそれ以上の多不飽和部位を有するモノマーからなる。コーティング材料の組成は、99〜100重量パーセントが反応性成分と固体材料から成っているとよく、99.9〜100重量パーセントが反応性成分および固体材料から成っていると更によく、100重量パーセントが反応性成分および固体材料から成っていると最もよい。固体材料としてはポリマー性物質やコロイダルシリカのような非揮発性の固体材料がある。適切なポリマー材料としてはセルロースアセテートブチレートがある。

また、これらのコーティング材料としては、紫外線に露出されると100%が固形分に変換できるものが好ましい。これらの材料には、光照射による、コーティング材料の硬化を可能にするために必要な量の光開始剤を含有させてある。なお、レゾルシノールモノベンゾエートのような潜在性紫外線遮断材を一定量含有していてもよい。

一方、エポキシ樹脂を含むコーティング材料としては、有機ケイ素化合物およびその加水分解物のエポキシシランと総称される物質ならびに、その加水分解物からなるものが挙げられる。このようなコーティング材料として、例えば、γ−グリシドキシプロピルトリメトキシシラン、γ−グリシドキシプロピルトリエトキシシラン、γ−グリシドキシプロピルトリメトキシエトキシシラン、γ−グリシドキシプロピルトリアセトキシシラン、β−(3、4−エポキシシクロヘキシル)エチルトリメトキシシラン、β−(3、4−エポキシシクロヘキシル)エチルトリエトキシシラン、β−(3、4−エポキシシクロヘキシル)エチルトリメトキシエトキシシラン、β−(3、4−エポキシシクロヘキシル)エチルトリアセトキシシラン、γ−グリシドキシプロピルジメトキシメチルシラン、γ−グリシドキシプロピルジエトキシメチルシラン、γ−グリシドキシプロピルジメトキシエトキシメチルシラン、γ−グリシドキシプロピルジアセトキシメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルジメトキシメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルジエトキシメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルジメトキシエトキシメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルジアセトキシメチルシラン、γ−グリシドキシプロピルジメトキシエチルシラン、γ−グリシドキシプロピルジエトキシエチルシラン、γ−グリシドキシプロピルジメトキシエトキシエチルシラン、γ−グリシドキシプロピルジアセトキシエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルジメトキシエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルジエトキシエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルジメトキシエトキシエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルジアセトキシエチルシラン、γ−グリシドキシプロピルジメトキシイソプロピルシラン、γ−グリシドキシプロピルジエトキシイソプロピルシラン、γ−グリシドキシプロピルジメトキシエトキシイソプロピルシラン、γ−グリシドキシプロピルジアセトキシイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルジエトキシイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルジエトキシイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルジメトキシエトキシイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルジアセトキシイソプロピルシラン、γ−グリシドキシプロピルメトキシジメチルシラン、γ−グリシドキシプロピルエトキシジメチルシラン、γ−グリシドキシプロピルメトキシエトキシジメチルシラン、γ−グリシドキシプロピルアセトキシジメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシジメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルエトキシジメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシエトキシジメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルアセトキシジメチルシラン、γ−グリシドキシプロピルメトキシジエチルシラン、γ−グリシドキシプロピルエトキシジエチルシラン、γ−グリシドキシプロピルメトキシエトキシジエチルシラン、γ−グリシドキシプロピルアセトキシジエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシジエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルエトキシジエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシエトキシジエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルアセトキシジエチルシラン、γ−グリシドキシプロピルメトキシジイソプロピルシラン、γ−グリシドキシプロピルエトキシジイソプロピルシラン、γ−グリシドキシプロピルメトキシエトキシジイソプロピルシラン、γ−グリシドキシプロピルアセトキシジイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシジイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルエトキシジイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシエトキシジイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルアセトキシジイソプロピルシラン、γ−グリシドキシプロピルメトキシエトキシメチルシラン、γ−グリシドキシプロピルアセトキシメトキシメチルシラン、γ−グリシドキシプロピルアセトキシエトキシメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシエトキシメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシアセトキシメチルシラン、β−(3、4−エポキシシクロヘキシル)エチルエトキシアセトキシメチルシラン、γ−グリシドキシプロピルメトキシエトキシエチルシラン、γ−グリシドキシプロピルアセトキシメトキシエチルシラン、γ−グリシドキシプロピルアセトキシエトキシエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシエトキシエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシアセトキシエチルシラン、β−(3、4−エポキシシクロヘキシル)エチルエトキシアセトキシエチルシラン、γ−グリシドキシプロピルメトキシエトキシイソプロピルシラン、γ−グリシドキシプロピルアセトキシメトキシイソプロピルシラン、γ−グリシドキシプロピルアセトキシエトキシイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシエトキシイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルメトキシアセトキシイソプロピルシラン、β−(3、4−エポキシシクロヘキシル)エチルエトキシアセトキシイソプロピルシラン、グリシドキシメチルトリメトキシシラン、グリシドキシメチルトリエトキシシラン、α−グリシドキシエチルトリメトキシシラン、α−グリシドキシメチルトリメトキシシラン、β−グリシドキシエチルトリメトキシシラン、β−グリシドキシメチルトリメトキシシラン、α−グリシドキシプロピルトリメトキシシラン、α−グリシドキシプロピルトリエトキシシラン、β−グリシドキシプロピルトリメトキシシラン、β−グリシドキシプロピルトリエトキシシラン、γ−グリシドキシプロピルトリプロポキシシラン、γ−グリシドキシプロピルトリブトキシシラン、γ−グリシドキシプロピルトリフェノキシシラン、α−グリシドキシブチルトリメトキシシラン、α−グリシドキシブチルトリエトキシシラン、β−グリシドキシブチルトリメトキシシラン、β−グリシドキシブチルトリエトキシシラン、γ−グリシドキシブチルトリメトキシシラン、γ−グリシドキシブチルトリエトキシシラン、(3,4−エポキシシクロヘキシル)メチルトリメトキシシラン、(3,4−エポキシシクロヘキシル)メチルトリエトキシシラン、β−(3,4−エポキシシクロヘキシル)エチルトリプロポキシシラン、β−(3,4−エポキシシクロヘキシル)エチルトリプトキシシラン、β−(3,4−エポキシシクロヘキシル)エチルトリフェノキシシラン、γ−(3,4−エポキシシクロヘキシル)プロピルトリメトキシシラン、γ−(3,4−エポキシシクロヘキシル)プロピルトリエトキシシラン、δ−(3,4−エポキシシクロヘキシル)ブチルトリメトキシシラン、δ−(3,4−エポキシシクロヘキシル)ブチルトリエトキシシラン、グリシドキシメチルメチルジメトキシシラン、グリシドキシメチルメチルジエトキシシラン、α−グリシドキシエチルメチルジメトキシシラン、α−グリシドキシエチルメチルジエトキシシラン、β−グリシドキシエチルメチルジメトキシシラン、β−グリシドキシエチルメチルジエトキシシラン、α−グリシドキシプロピルメチルジメトキシシラン、α−グリシドキシプロピルメチルジエトキシシラン、β−グリシドキシプロピルメチルジメトキシシラン、β−グリシドキシプロピルメチルジエトキシシラン、γ−グリシドキシプロピルメチルジメトキシシラン、γ−グリシドキシプロピルメチルジエトキシシラン、γ−グリシドキシプロピルメチルジプロポキシシラン、γ−グリシドキシプロピルメチルジブトキシシラン、γ−グリシドキシプロピルメチルジメトキシエトキシシラン、γ−グリシドキシプロピルメチルジフェノキシシラン、γ−グリシドキシプロピルエチルジメトキシシラン、γ−グリシドキシプロピルエチルジエトキシシラン、γ−グリシドキシプロピルエチルジプロポキシシラン、γ−グリシドキシプロピルビニルジメトキシシラン、γ−グリシドキシプロピルビニルジエトキシシラン等が挙げられる。

以上例示したこれらのコーティング材料は、1種で使用してもよいが、目的に応じて2種以上を混合して使用してもよい。これらコーティング材料は、他のシラン化合物と混合して使用することも可能である。例えば、メチルトリメトキシシラン、メチルトリエトキシシラン、ビニルトリメトキシシラン、ビニルトリエトキシシラン、ビニルトリアセトキシシラン、ビニルトリメトキシエトキシシラン、γ−メタクリロキシプロピルトリメトキシシラン、アメノメチルトリメトキシシラン、3−アミノプロピルトリメトキシシラン、3−アミノプロピルトリエトキシシラン、フエニルトリメトキシシラン、フエニルトリエトキシシラン、γ−クロロプロピルトリメトキシシラン、γ−メルカプトプロピルトリエトキシシラン、3、3、3−トリフルオロプロピルトリメトキシシランなどの各種トリアルコキシシラン、トリアシロキシシランあるいはトリアルコキシアルコキシシラン化合物、ジメチルジメトキシシラン、ジフエニルジメトキシシラン、メチルフエニルジメトキシシラン、メチルビニルジメトキシシラン、ジメチルジエトキシシランなどのジアルコキシシラン化合物、メチルシリケート、エチルシリケート、イソプロピルシリケート、n−プロピルシリケート、n−ブチルシリケート、t−ブチルシリケート、sec−ブチルシリケートなど4官能のシラン化合物などが挙げられる。

以上、いわゆるハードコーティング材料といわれるような、3次元的な縮重合による結合により高い緻密性と高い高度をもつようなアクリル系樹脂の高分子材料、またはアクリル系樹脂と他の樹脂を含むような複合高分子系プラスチック材料や、有機ケイ素化合物およびその加水分解物のエポキシ系樹脂ならびに、その加水分解物からなるハードコーティング材料は無数に存在し、前述の材料群が一例に過ぎないことはいうまでもない。

有機高分子層(コーティング層)の形成方法としては、上述したアクリル樹脂、エポキシ樹脂、あるいはこれらを含む高分子材料に、必要に応じてフィラー、水あるいは有機溶媒を混合し、これをペイントシェーカー、サンドミル、パールミル、ボールミル、アトライター、ロールミル、高速インペラー分散機、ジェットミル、高速衝撃ミル、超音波分散機等によって分散し、コーティング材料とする。このときにハードコート材とプラスチック基板の密着性が悪い場合は、接着層を介して形成されていることが望ましい。接着層はプラスチックフィルム製造時に同時に表面に形成することもあるし、後から塗布することもある。

次に、このコーティング材料を、スピンコーティング法、エアドクターコーティング法、ブレードコーティング法、ナイフコーティング法、リバースコーティング法、トランスファロールコーティング、グラビアロールコーティング、キスコーティング、キャストコーティング法、スプレーコーティング法、スロットオリフィスコーティング法、カレンダーコーティング法、電着コーティング法、ディップコーティング法、ダイコーティング法等のコーティング法や、フレキソ印刷法等の凸版印刷法、ダイレクトグラビア印刷法やオフセットグラビア印刷法等の凹版印刷法、オフセット印刷法等の平板印刷法、スクリーン印刷法等の孔版印刷法などの印刷手法を用いて、片面または両面上に単層もしくは多層に分けて塗付する。なお、コーティング材料が溶媒を含んでいる場合は、塗付後に熱乾燥を行う。

次に必要に応じて、ポリシラザン系化合物を含む溶液又はシロキサン系化合物を含む溶液で、CH3基の含有量を0〜50wt%以下、好ましくは0〜30wt%の材料を、スピンコーティング法、エアドクターコーティング法、ブレードコーティング法、ナイフコーティング法、リバースコーティング法、トランスファロールコーティング、グラビアロールコーティング、キスコーティング、キャストコーティング法、スプレーコーティング法、スロットオリフィスコーティング法、カレンダーコーティング法、電着コーティング法、ディップコーティング法、ダイコーティング法等のコーティング法や、フレキソ印刷法等の凸版印刷法、ダイレクトグラビア印刷法やオフセットグラビア印刷法等の凹版印刷法、オフセット印刷法等の平板印刷法、スクリーン印刷法等の孔版印刷法などの印刷手法を用いて塗付させ、乾燥、熱処理又は紫外線照射等を行うことにより、無機系(一部有機成分を含む)のバッファー層を形成する。熱処理は必要に応じて、水蒸気雰囲気中で行うこともある。無機系(一部有機成分を含む)のバッファー層はハードコート材と合わせて強固な熱的バッファー層を形成し、基板表面側からの比較的高温での熱処理に対して熱的に強いフィルムとなりレーザ結晶化プロセス上非常に有利である。

<レーザ装置>

次に、以上の第1実施形態および第2実施形態で代表される本発明の薄膜半導体装置の製造方法に用いられるレーザ装置の概略構成の一例を、レーザ光の光路に沿って説明する。

先ず、このレーザ装置は、複数のGaN半導体レーザ発振器(以下単に発振器と記す)を備えている。そして、これらの発振器から発振された複数のレーザ光は、それぞれ別に設けられた、コリメートレンズ、ビーム成形用のアナモリフィックプリズム、走査ユニットをこの順に通過する。そして、各走査ユニットに入射した各レーザ光は、それぞれの対物レンズを通して基板1上の各選択領域に集光される。

このうち、走査ユニットの構造としては、例えば、ポリゴンミラー方式、ガルバノミラー方式、AOD方式、MEMS方式などが考えられ、f≡レンズを通した組み合わせで基板1上へレーザ光を集光させながら、レーザ光を走査させることができる。

またこの走査ユニットには、ハーフミラーを用いることで、アニール処理に用いるレーザ光と同じ光路に、半導体薄膜(a-Si:H)での吸収がほとんどない波長830nmのレーザ光を導入し、AFセンサーにこのレーザ光を取り込みフォーカスサーボを可能する。また同じく必要に応じてCCDで照射部分の光を取り込み、照射部分のアライメントが出来る機構を取り付けることとする。

走査ユニットの設置密度を上げるためには、走査ユニット部分のみを切りはなしてアナモリフィックプリズムを通過後に光ファイバーに導入し、ファイバー出口でコリメートレンズを通過させてから走査ユニットに入れることで、走査ユニットとAFサーボの機構だけを分離可能となるので、一つのユニットでのプロセスエリアを縮小でき生産性の向上を図ることができる。

ここで、対物レンズの実効的なNaを例えば0.6として設計した定格60mWのGaNを用いたレーザ装置において、さらに実質的な光学効率が0.5の場合、平均で17.7mW/cm2のエネルギー密度が可能となる。したがって、レーザ光の走査速度を8.2m/S程度まで上げられるとすると、半導体薄膜の一点を通過するレーザ光の通過時間(すなわち照射時間)は約100nsとなり、最大1.77J/cm2相当のエネルギーを照射可能であることがわかる。

尚、PE−CVD法で成膜した膜厚50nmの半導体薄膜(a−Si;H)に対して、この装置で1J/cm2相当のエネルギーを投入したところ、幅800nm×移動方向長さ100nm程度の三日月上の結晶粒が並んだ多結晶膜が得られることが確認された。またレーザ光の照射終了端には、半導体材料の凝固後に余剰水素ガスがボイド状に析出した欠陥が見られた。またレーザ光の照射開始端にもレーザ光の移動と反対方向に凝固が進んだ領域に部分的に同様の欠陥が見られた。以上は、第1実施形態でも述べた通りである。