JP4697384B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4697384B2 JP4697384B2 JP2004010063A JP2004010063A JP4697384B2 JP 4697384 B2 JP4697384 B2 JP 4697384B2 JP 2004010063 A JP2004010063 A JP 2004010063A JP 2004010063 A JP2004010063 A JP 2004010063A JP 4697384 B2 JP4697384 B2 JP 4697384B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- electrode

- semiconductor

- semiconductor region

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Electrodes Of Semiconductors (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

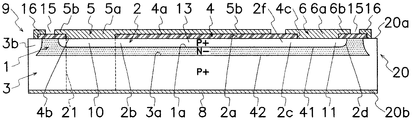

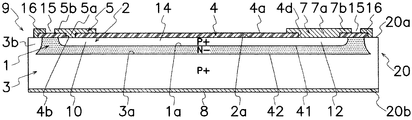

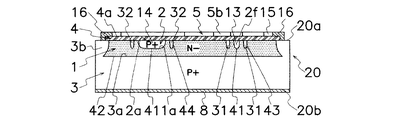

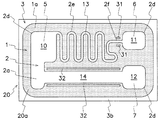

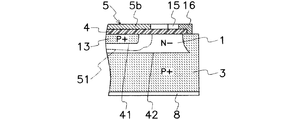

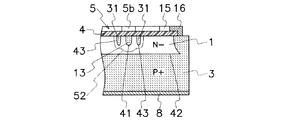

本実施の形態の半導体装置は、図1〜図3に示すように、N−型半導体領域を構成する第1の半導体領域(1)と、第1の半導体領域(1)とは異なる導電型により第1の半導体領域(1)の主面(1a)上に隣接して形成されたP+型半導体領域を構成する第2の半導体領域(2)と、第1の半導体領域(1)とは異なる導電型により第1の半導体領域(1)の主面(1a)とは反対側の他面に隣接して形成されたP+型半導体領域の第3の半導体領域(3)とを有する半導体層(20)を備え、半導体層(20)の主面(20a)とは反対側の底面(20b)には、接地電極(8)が形成される。従って、第2の半導体領域(2)と第3の半導体領域(3)とは互いに同一の導電型であり、第2の半導体領域(2)及び第3の半導体領域(3)と第1の半導体領域(1)とは異なる導電型である。図4及び図5に示すように、互いに離間して形成された第1〜第3の開口部(4b〜4d)を有する絶縁膜(4)は、半導体層(20)の主面(20a)を被覆する。

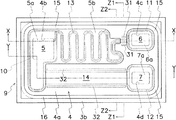

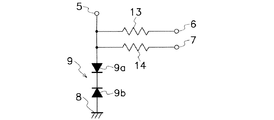

通常の動作時には第1及び第2の領域(10,11)間と第1及び第3の領域(10,12)間の抵抗素子が動作し、過電圧が印加された時は図6に示す双方向ダイオード(9)がオンしてバックメタルとしての接地電極(8)を通じて電流を流すことができる。第1の抵抗領域(13)及び第2の抵抗領域(14)の抵抗値は、第1及び第2の抵抗領域(13,14)を構成する第2の半導体領域(2)の幅、長さ及び深さ並びに不純物濃度により適宜設定し又は調整することができる。

図3に示すように、第1の半導体領域(1)と第1の電界緩和領域(31)との界面には第3のPN接合(43)が形成され、第1の半導体領域(1)と第2の電界緩和領域(32)との界面には第4のPN接合(44)が形成される。

[1] 互いに離間して形成される第1の電極(5)と第2の電極(6)との間及び第1の電極(5)と第3の電極(7)との間にそれぞれ介在する第2の半導体領域(2)を異なる抵抗値を有する抵抗素子として使用することができる。

[2] FLRとして機能する第1の電界緩和領域(31)と第2の電界緩和領域(32)によって、フィールドプレートによる電界集中緩和効果が補完され、PN接合(41)の全周にわたって、電界集中を良好に緩和できる曲率の大きい連続的な空乏層を形成することができる。このため、PN接合の高耐圧化を安定して図ることができる。また、フィールドプレート効果が及ばない領域をFLRで補完する構造としたため、高耐圧化構造を比較的小さな占有面積で構築することができる。

[3] 第1及び第2の領域(10,11)間で連続する複数の蛇行部(2e)及び直線状部(2f)を有する第1の抵抗領域(13)に大きな抵抗値を付与することができる。また、第1の抵抗領域(13)の直線状部(2f)から離間して第1の電界緩和領域(31)を形成するので、複数の蛇行部(2e)を互いに隣接して配置でき、半導体層(20)に対する第2の半導体領域(2)の占有面積を比較的小さくすることができる。

[4] 第1の電極(5)の延長部(5b)が蛇行部(2e)の曲部に起こる電界集中を良好に緩和するフィールドプレートとして作用するので、第2の半導体領域(2)を相対的に幅狭に且つ小さな曲率で形成することができ、高い抵抗値を有し且つ高耐圧の第1の抵抗領域(13)を比較的小さな占有面積で形成できる。

[5] 半導体層(20)の深さ方向に能動素子を形成し、半導体層(20)の主面(20a)と並行な方向に抵抗素子を形成するので、半導体装置を大型化せずに、高耐圧の半導体装置を形成できる。

[6] 一方のダイオード(9a)のアノード領域の一部として第1及び第2の抵抗領域(13,14)を作用させて、双方向ダイオードの電流容量を増大させることができる。

[7] 相対的に抵抗値の高い第1の抵抗領域(13)を屈曲形状で形成したので、1つの半導体層(20)内に抵抗値の高い第1の抵抗領域(13)と抵抗値の低い第2の抵抗領域(14)とを集積できると共に、その占有面積を十分に小さくすることができる。

Claims (5)

- 第1の半導体領域及び該第1の半導体領域とは異なる導電型により前記第1の半導体領域の表面の一部に形成される第2の半導体領域を有する半導体層と、

第1及び第2の開口部をもって前記半導体層の主面を被覆する絶縁膜と、

該絶縁膜を介して前記半導体層の主面上に互いに離間して形成される第1の電極及び第2の電極とを備え、

前記第2の半導体領域は、前記第1の開口部内の前記第1の電極に電気的に接続される第1の領域と、前記第2の開口部内の前記第2の電極に電気的に接続される第2の領域と、前記第1の領域と前記第2の領域との間に形成される抵抗領域とを有し、

前記第1の電極は、前記絶縁膜の第1の開口部内に配置されて前記第2の半導体領域の主面に接触する主電極部と、該主電極部に接続され且つ前記絶縁膜を介して前記第2の半導体領域の抵抗領域を被覆する延長部とを有し、

前記第2の電極は、前記絶縁膜の第2の開口部内に配置されて前記第2の半導体領域の主面に接触する主電極部を有し、

前記第2の半導体領域と同一の導電型の半導体領域から成る電界緩和領域を前記第2の半導体領域から離間して且つ前記第1の電極の延長部と前記第2の電極との間に形成し、前記電界緩和領域により、空乏層を連続的に形成して、前記第1の半導体領域と前記第2の半導体領域との界面に形成されるPN接合の電界集中を緩和することを特徴とする半導体装置。 - 前記第2の電極は、前記第2の半導体領域に並行に前記主電極部から延伸する延長部を有し、

該延長部は、前記絶縁膜を介して前記第1の半導体領域の主面を被覆する請求項1に記載の半導体装置。 - 前記絶縁膜を介して前記半導体層の主面上に前記第1の電極及び第2の電極から離間して形成される第3の電極と、前記半導体層の主面とは反対側の前記半導体層の底面に形成される接地電極とを備え、

前記半導体層は、前記第1の半導体領域とは異なる導電型により形成される第3の半導体領域を有し、

前記第2の半導体領域は、前記絶縁膜に形成される第3の開口部内の前記第3の電極に電気的に接続される第3の領域を有し、

前記第1の半導体領域と前記第2の半導体領域との界面に第1のPN接合を形成し、

前記第3の半導体領域内に形成される前記第1の半導体領域と前記第3の半導体領域との界面に第2のPN接合を形成し、

前記第1の電極から前記接地電極に向かう前記半導体層の深さ方向に双方向ダイオードを形成した請求項1又は2に記載の半導体装置。 - 前記第2の半導体領域は、前記第1の領域に接続される前記抵抗領域となる蛇行部と、該蛇行部と前記第2の領域との間に接続される直線状部とを有し、

前記第1の電極と第2の電極とは、前記蛇行部及び直線状部を通じて互いに電気的に接続され、

前記蛇行部は、前記絶縁膜を介して前記第1の電極の延長部により被覆され、

前記電界緩和領域は、前記直線状部の両側に且つ該直線状部から離間して前記第1の半導体領域内に形成される請求項3に記載の半導体装置。 - 前記第1の電極の延長部は、フィールドプレートを構成し、

前記電界緩和領域は、フィールド・リミッティング・リングを構成する請求項1〜4の何れか1項に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004010063A JP4697384B2 (ja) | 2004-01-19 | 2004-01-19 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004010063A JP4697384B2 (ja) | 2004-01-19 | 2004-01-19 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005203658A JP2005203658A (ja) | 2005-07-28 |

| JP4697384B2 true JP4697384B2 (ja) | 2011-06-08 |

Family

ID=34822893

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004010063A Expired - Fee Related JP4697384B2 (ja) | 2004-01-19 | 2004-01-19 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4697384B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4797484B2 (ja) * | 2005-07-21 | 2011-10-19 | サンケン電気株式会社 | Flr領域を有する半導体素子 |

| CN110518061B (zh) * | 2019-09-25 | 2024-12-27 | 天津华慧芯科技集团有限公司 | 基于平面s型结的耐高压元件及制造工艺 |

| JP7613965B2 (ja) * | 2021-03-19 | 2025-01-15 | 新電元工業株式会社 | 半導体装置 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5864059A (ja) * | 1981-10-14 | 1983-04-16 | Hitachi Ltd | 高耐圧抵抗素子 |

| JPH05291241A (ja) * | 1992-04-10 | 1993-11-05 | Honda Motor Co Ltd | 半導体装置 |

| JP3732908B2 (ja) * | 1996-12-27 | 2006-01-11 | 三洋電機株式会社 | 半導体集積回路 |

| JP2004296803A (ja) * | 2003-03-27 | 2004-10-21 | Sanken Electric Co Ltd | 半導体素子 |

-

2004

- 2004-01-19 JP JP2004010063A patent/JP4697384B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005203658A (ja) | 2005-07-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4399449A (en) | Composite metal and polysilicon field plate structure for high voltage semiconductor devices | |

| US4412242A (en) | Planar structure for high voltage semiconductor devices with gaps in glassy layer over high field regions | |

| JP4894097B2 (ja) | 半導体装置 | |

| CN113161418A (zh) | 半导体装置 | |

| JP2020043241A (ja) | 半導体装置 | |

| US5691555A (en) | Integrated structure current sensing resistor for power devices particularly for overload self-protected power MOS devices | |

| JP2004119870A (ja) | ダイオード | |

| JP4631268B2 (ja) | 半導体装置 | |

| US6703665B1 (en) | Transistor | |

| JP4432332B2 (ja) | 半導体素子及びその製造方法 | |

| US5323041A (en) | High-breakdown-voltage semiconductor element | |

| JP4416288B2 (ja) | 逆導通サイリスタ | |

| JP7113386B2 (ja) | 半導体装置 | |

| JP4697384B2 (ja) | 半導体装置 | |

| CN114388611B (zh) | 电力用半导体装置 | |

| EP0064614B1 (en) | Improved emitter structure for semiconductor devices | |

| JP4576805B2 (ja) | 絶縁ゲート型半導体素子及びその製造方法 | |

| JP4642767B2 (ja) | サージ保護用半導体装置 | |

| JP3551154B2 (ja) | 半導体素子 | |

| JP4029549B2 (ja) | 半導体装置 | |

| JP4797484B2 (ja) | Flr領域を有する半導体素子 | |

| JPH08130317A (ja) | 抵抗性フィ−ルドプレ−トを備えた半導体装置 | |

| JP7613965B2 (ja) | 半導体装置 | |

| JP5245280B2 (ja) | 半導体装置 | |

| JP2004296803A (ja) | 半導体素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061006 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101116 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110114 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110202 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110215 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4697384 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |