以下、本発明の一実施形態を図面を参照して説明する。

まず、遊技機の一例であるパチンコ遊技機の全体の構成について説明する。図1はパチンコ遊技機1を正面からみた正面図である。なお、ここでは、遊技機の一例としてパチンコ遊技機を示すが、本発明はパチンコ遊技機に限られず、例えばコイン遊技機等であってもよい。また、画像式の遊技機やスロット機に適用することもできる。

図1に示すように、パチンコ遊技機1は、額縁状に形成されたガラス扉枠2を有する。ガラス扉枠2の下部表面には打球供給皿3がある。打球供給皿3の下部には、打球供給皿3からあふれた景品球を貯留する余剰球受皿4と打球を発射する打球操作ハンドル(操作ノブ)5が設けられている。ガラス扉枠2の後方には、遊技盤6が着脱可能に取り付けられている。また、遊技盤6の前面には遊技領域7が設けられている。

遊技領域7の中央付近には、複数種類の図柄を可変表示するための可変表示部9と7セグメントLEDによる可変表示器10とを含む可変表示装置8が設けられている。この実施の形態では、可変表示部9には、「左」、「中」、「右」の3つの図柄表示エリアがある。可変表示装置8の側部には、打球を導く通過ゲート11が設けられている。通過ゲート11を通過した打球は、球出口13を経て始動入賞口14の方に導かれる。通過ゲート11と球出口13との間の通路には、通過ゲート11を通過した打球を検出するゲートスイッチ12がある。また、始動入賞口14に入った入賞球は、遊技盤6の背面に導かれ、始動口スイッチ17によって検出される。また、始動入賞口14の下部には開閉動作を行う可変入賞球装置15が設けられている。可変入賞球装置15は、ソレノイド16によって開状態とされる。

可変入賞球装置15の下部には、特定遊技状態(大当り状態)においてソレノイド21によって開状態とされる開閉板20が設けられている。この実施の形態では、開閉板20が大入賞口を開閉する手段となる。開閉板20から遊技盤6の背面に導かれた入賞球のうち一方(Vゾーン)に入った入賞球はVカウントスイッチ22で検出される。また、開閉板20からの入賞球はカウントスイッチ23で検出される。可変表示装置8の下部には、始動入賞口14に入った入賞球数を表示する4個の表示部を有する始動入賞記憶表示器18が設けられている。この例では、4個を上限として、始動入賞がある毎に、始動入賞記憶表示器18は点灯している表示部を1つずつ増やす。そして、可変表示部9の可変表示が開始される毎に、点灯している表示部を1つ減らす。

遊技盤6には、複数の入賞口19,24が設けられ、遊技球の入賞口19,24への入賞は入賞口スイッチ19a,24aによって検出される。遊技領域7の左右周辺には、遊技中に点滅表示される装飾ランプ25が設けられ、下部には、入賞しなかった打球を吸収するアウト口26がある。また、遊技領域7の外側の左右上部には、効果音を発する2つのスピーカ27が設けられている。遊技領域7の外周には、遊技効果LED28aおよび遊技効果ランプ28b,28cが設けられている。

そして、この例では、一方のスピーカ27の近傍に、景品球払出時に点灯する賞球ランプ51が設けられ、他方のスピーカ27の近傍に、補給球が切れたときに点灯する球切れランプ52が設けられている。さらに、図1には、パチンコ遊技台1に隣接して設置され、プリペイドカードが挿入されることによって球貸しを可能にするカードユニット50も示されている。

カードユニット50には、使用可能状態であるか否かを示す使用可表示ランプ151、カード内に記録された残額情報に端数(100円未満の数)が存在する場合にその端数を打球供給皿3の近傍に設けられる度数表示LEDに表示させるための端数表示スイッチ152、カードユニット50がいずれの側のパチンコ遊技機1に対応しているのかを示す連結台方向表示器153、カードユニット50内にカードが投入されていることを示すカード投入表示ランプ154、記録媒体としてのカードが挿入されるカード挿入口155、およびカード挿入口155の裏面に設けられているカードリーダライタの機構を点検する場合にカードユニット50を解放するためのカードユニット錠156が設けられている。

打球発射装置から発射された打球は、打球レールを通って遊技領域7に入り、その後、遊技領域7を下りてくる。打球が通過ゲート11を通ってゲートスイッチ12で検出されると、可変表示器10の表示数字が連続的に変化する状態になる。また、打球が始動入賞口14に入り始動口スイッチ17で検出されると、図柄の変動を開始できる状態であれば、可変表示部9内の図柄が回転を始める。図柄の変動を開始できる状態でなければ、始動入賞記憶を1増やす。

可変表示部9内の画像の回転は、一定時間が経過したときに停止する。停止時の画像の組み合わせが大当り図柄の組み合わせであると、大当り遊技状態に移行する。すなわち、開閉板20が、一定時間経過するまで、または、所定個数(例えば10個)の打球が入賞するまで開放する。そして、開閉板20の開放中に打球が特定入賞領域に入賞しVカウントスイッチ22で検出されると、継続権が発生し開閉板20の開放が再度行われる。継続権の発生は、所定回数(例えば15ラウンド)許容される。

停止時の可変表示部9内の画像の組み合わせが確率変動を伴う大当り図柄の組み合わせである場合には、次に大当りとなる確率が高くなる。すなわち、高確率状態という遊技者にとってさらに有利な状態となる。また、可変表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定時間だけ開状態になる。さらに、高確率状態では、可変表示器10における停止図柄が当り図柄になる確率が高められるとともに、可変入賞球装置15の開放時間と開放回数が高められる。

次に、パチンコ遊技機1の裏面に配置されている各基板について説明する。

図2に示すように、パチンコ遊技機1の裏面では、枠体2A内の機構板の上部に球貯留タンク38が設けられ、パチンコ遊技機1が遊技機設置島に設置された状態でその上方から遊技球が球貯留タンク38に供給される。球貯留タンク38内の遊技球は、誘導樋39を通って球払出機構(図示せず)に至る。

遊技機裏面側では、可変表示部9を制御する可変表示制御ユニット29、遊技制御用マイクロコンピュータ等が搭載された遊技制御基板(主基板)31が設置されている。また、球払出制御を行う払出制御用マイクロコンピュータ等が搭載された払出制御基板37、およびモータの回転力を利用して打球を遊技領域7に発射する打球発射装置が設置されている。さらに、装飾ランプ25、遊技効果LED28a、遊技効果ランプ28b,28c、賞球ランプ51および球切れランプ52に信号を送るためのランプ制御基板35、スピーカ27からの音声発生を制御するための音声制御基板70および打球発射装置を制御するための発射制御基板91も設けられている。なお、払出制御基板37には、エラー表示用LED374も搭載されている。

また、DC30V、DC21V、DC12VおよびDC5Vを作成する電源回路が搭載された電源基板910が設けられ、上方には、各種情報を遊技機外部に出力するための各端子を備えたターミナル基板160が設置されている。ターミナル基板160には、少なくとも、後述する球切れ検出スイッチ167の出力を導入して外部出力するための球切れ用端子、賞球個数信号を外部出力するための賞球用端子および球貸し個数信号を外部出力するための球貸し用端子が設けられている。また、中央付近には、主基板31からの各種情報を遊技機外部に出力するための各端子を備えた情報端子盤(外部情報出力装置)34が設置されている。

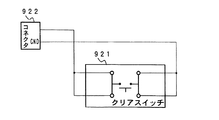

また、図2には、ランプ制御基板35および音声制御基板70からの信号を、枠側に設けられている遊技効果LED28a、遊技効果ランプ28b,28c、賞球ランプ51および球切れランプ52に供給するための電飾中継基板A77および度数表示LED等を搭載した残高表示基板74が示されている。また、この実施の形態では、各基板(例えば、主基板31、払出制御基板37)に含まれる変動データ記憶手段(例えば、バックアップRAM)に記憶されたバックアップデータをクリアするためのクリアスイッチ921が搭載されたスイッチ基板190が設けられている。なお、スイッチ基板190には、例えば主基板などの他の基板と接続されるコネクタ(図43、図44参照)が設けられている。さらに、図示はしないが、信号中継の必要に応じて他の中継基板も設けられる。

また、図3はパチンコ遊技機1の機構板を背面からみた背面図である。球貯留タンク38に貯留された遊技球は誘導樋39を通り、図3に示されるように、球切れ検出器(球切れスイッチ)187a,187bを通過して球供給樋186a,186bを経て球払出装置97に至る。球払出装置97から払い出された遊技球は、連絡口45を通ってパチンコ遊技機1の前面に設けられている打球供給皿3に供給される。連絡口45の側方には、パチンコ遊技機1の前面に設けられている余剰玉受皿4に連通する余剰玉通路46が形成されている。入賞にもとづく景品球が多数払い出されて打球供給皿3が満杯になり、ついには遊技球が連絡口45に到達した後さらに遊技球が払い出されると遊技球は、余剰玉通路46を経て余剰玉受皿4に導かれる。さらに遊技球が払い出されると、感知レバー47が満タンスイッチ48を押圧して満タンスイッチ48がオンする。その状態では、球払出装置97内のステッピングモータの回転が停止して球払出装置97の動作が停止するとともに打球発射装置34の駆動も停止する。

賞球払出制御を行うために、入賞口スイッチ(図示せず)、始動口スイッチ17およびVカウントスイッチ22からの信号が、主基板31に送られる。主基板31のCPU56は、始動口スイッチ17がオンすると6個の賞球払出に対応した入賞が発生したことを知る。また、カウントスイッチ23がオンすると15個の賞球払出に対応した入賞が発生したことを知る。そして、入賞口スイッチがオンすると10個の賞球払出に対応した入賞が発生したことを知る。なお、この実施の形態では、例えば、入賞口24に入賞した遊技球は、入賞口24からの入賞球流路に設けられている入賞口スイッチ24aで検出され、入賞口19に入賞した遊技球は、入賞口19からの入賞球流路に設けられている入賞口スイッチ19aで検出される。

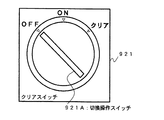

図4は、スイッチ基板190に搭載されたクリアスイッチ921の構成の一例を示す外観構成図である。クリアスイッチ921は、本例では、「OFF」、「ON」および「クリア」の選択切り換えがされる切換操作スイッチ921aを有する。クリアスイッチ921は、「OFF」が選択されているときは何らの信号も発生せずに動作停止中となっており、「ON」が選択されているときはハイレベルの信号を出力する。クリアスイッチ921は、この例では、遊技機1に対する電源供給のオン/オフ切換のためのスイッチ(後述する電源スイッチ920)と連動された構成とされている。従って、クリアスイッチ921で「OFF」が選択されているときには遊技機1の電源供給が停止された状態(遊技機の電源がオフの状態)にあり、「ON」および「クリア」が選択されているときには遊技機1が稼動している状態(遊技機の電源がオンの状態)にある。また、クリアスイッチ921は、「クリア」が選択されているときに、ローレベルのクリア信号を出力する。なお、クリアスイッチ921は、電源スイッチ920と連動されない構成とされていてもよい。

図5は、主基板31における回路構成の一例を示すブロック図である。なお、図5には、払出制御基板37、ランプ制御基板35、音制御基板70、発射制御基板91、表示制御基板80およびスイッチ基板190も示されている。主基板31には、プログラムに従ってパチンコ遊技機1を制御する基本回路53と、ゲートスイッチ12、始動口スイッチ17、Vカウントスイッチ22、カウントスイッチ23、球切れスイッチ187、入賞口スイッチ19a,24aおよび賞球カウントスイッチ301Aからの信号を基本回路53に与えるスイッチ回路58と、可変入賞球装置15を開閉するソレノイド16および開閉板20を開閉するソレノイド21等を基本回路53からの指令に従って駆動するソレノイド回路59とが搭載されている。なお、この実施の形態では、スイッチ回路58は、スイッチ基板190に搭載されたクリアスイッチ921からの信号をも基本回路53に与える。

また、基本回路53から与えられるデータに従って、大当りの発生を示す大当り情報、可変表示部9の画像表示開始に利用された始動入賞球の個数を示す有効始動情報、確率変動が生じたことを示す確変情報等をホール管理コンピュータ等のホストコンピュータに対して出力する情報出力回路64を含む。

基本回路53は、ゲーム制御用のプログラム等を記憶するROM54、ワークメモリとして使用される記憶手段の一例であるRAM55、プログラムに従って制御動作を行うCPU56およびI/Oポート部57を含む。この実施の形態では、ROM54,RAM55はCPU56に内蔵されている。すなわち、CPU56は、1チップマイクロコンピュータである。なお、1チップマイクロコンピュータは、少なくともRAM55が内蔵されていればよく、ROM54およびI/Oポート部57は外付けであっても内蔵されていてもよい。また、I/Oポート部57は、マイクロコンピュータにおける情報入出力可能な端子である。

さらに、主基板31には、電源投入時に基本回路53をリセットするためのシステムリセット回路65と、基本回路53から与えられるアドレス信号をデコードしてI/Oポート部57のうちのいずれかのI/Oポートを選択するための信号を出力するアドレスデコード回路67とが設けられている。なお、球払出装置97から主基板31に入力されるスイッチ情報もあるが、図5ではそれらは省略されている。

遊技球を打撃して発射する打球発射装置は発射制御基板91上の回路によって制御される駆動モータ94で駆動される。そして、駆動モータ94の駆動力は、操作ノブ5の操作量に従って調整される。すなわち、発射制御基板91上の回路によって、操作ノブ5の操作量に応じた速度で打球が発射されるように制御される。

なお、この実施の形態では、ランプ制御基板35に搭載されているランプ制御手段が、遊技盤に設けられている始動記憶表示器18、ゲート通過記憶表示器41および装飾ランプ25の表示制御を行うとともに、枠側に設けられている遊技効果ランプ・LED28a,28b,28c、賞球ランプ51および球切れランプ52の表示制御を行う。また、特別図柄を可変表示する可変表示部9および普通図柄を可変表示する可変表示器10の表示制御は、表示制御基板80に搭載されている表示制御手段によって行われる。

図6は、CPU56周りの一構成例を示すブロック図である。図6に示すように、第1の電源監視回路(第1の電源監視手段、あるいは電源監視手段)からの電圧低下信号が、CPU56のマスク不能割込端子(XNMI端子)に接続されている。第1の電源監視回路は、遊技機が使用する各種直流電源のうちのいずれかの電源の電圧を監視して電源電圧低下を検出する回路である。この実施の形態では、VSLの電源電圧を監視して電圧値が所定値以下になるとローレベルの電圧低下信号を発生する。VSLは、遊技機で使用される直流電圧のうちで最大のものであり、この例では+30Vである。従って、CPU56は、割込処理によって電源断の発生を確認することができる。なお、この実施の形態では、第1の電源監視回路は、後述する電源基板に搭載されており、割込処理によって電源断の発生が確認される。

図6には、システムリセット回路65も示されているが、この実施の形態では、システムリセット回路65は、第2の電源監視回路(第2の電源監視手段)も兼ねている。すなわち、リセットIC651は、電源投入時に、外付けのコンデンサの容量で決まる所定時間だけ出力をローレベルとし、所定時間が経過すると出力をハイレベルにする。すなわち、リセット信号をハイレベルに立ち上げてCPU56を動作可能状態にする。また、リセットIC651は、第1の電源監視回路が監視する電源電圧と等しい電源電圧であるVSLの電源電圧を監視して電圧値が所定値(第1の電源監視回路が電圧低下信号を出力する電源電圧値よりも低い値)以下になるとローレベルの電圧低下信号を発生する。従って、CPU56は、第1の電源監視回路からの電圧低下信号に応じて所定の電力供給停止時処理を行った後、システムリセットされる。なお、この実施の形態では、リセット信号と第2の電源監視回路からの電圧低下信号とは同一の信号である。

図6に示すように、リセットIC651からのリセット信号は、NAND回路947に入力されるとともに、反転回路(NOT回路)944を介してカウンタIC941のクリア端子に入力される。カウンタIC941は、クリア端子への入力がローレベルになると、発振器943からのクロック信号をカウントする。そして、カウンタIC941のQ5出力がNOT回路945,946を介してNAND回路947に入力される。また、カウンタIC941のQ6出力は、フリップフロップ(FF)942のクロック端子に入力される。フリップフロップ942のD入力はハイレベルに固定され、Q出力は論理和回路(OR回路)949に入力される。OR回路949の他方の入力には、NAND回路947の出力がNOT回路948を介して導入される。そして、OR回路949の出力が、CPU56のリセット端子に接続されている。このような構成によれば、電源投入時に、CPU56のリセット端子に2回のリセット信号(ローレベル信号)が与えられるので、CPU56は、確実に動作を開始する。

そして、例えば、第1の電源監視回路の検出電圧(電圧低下信号を出力することになる電圧)を+22Vとし、第2の電源監視回路の検出電圧を+9Vとする。そのように構成した場合には、第1の電源監視回路と第2の電源監視回路とは、同一の電源VSLの電圧を監視するので、第1の電圧監視回路が電圧低下信号を出力するタイミングと第2の電圧監視回路が電圧低下信号を出力するタイミングの差を所望の所定期間に確実に設定することができる。所望の所定期間とは、第1の電源監視回路からの電圧低下信号に応じて電力供給停止時処理を開始してから電力供給停止時処理が確実に完了するまでの期間である。

この例では、第1の電源監視手段が検出信号を出力することになる第1検出条件は+30V電源電圧が+22Vにまで低下したことであり、第2の電源監視手段が検出信号を出力することになる第2検出条件は+30V電源電圧が+9Vにまで低下したことになる。ただし、ここで用いられている電圧値は一例であって、他の値を用いてもよい。

ただし、監視範囲が狭まるが、第1の電圧監視回路および第2の電圧監視回路の監視電圧として+5V電源電圧を用いることも可能である。その場合にも、第1の電圧監視回路の検出電圧は、第2の電圧監視回路の検出電圧よりも高く設定される。

CPU56等の駆動電源である+5V電源から電力が供給されていない間、RAMの少なくとも一部は、電源基板から供給されるバックアップ電源によってバックアップされ、遊技機に対する電源が断しても内容は保存される。そして、+5V電源が復旧すると、システムリセット回路65からリセット信号が発せられるので、CPU56は、通常の動作状態に復帰する。そのとき、必要なデータがバックアップRAMに保存されているので、停電等からの復旧時に停電発生時の遊技状態に復帰することができる。

なお、図6では、電源投入時にCPU56のリセット端子に2回のリセット信号(ローレベル信号)が与えられる構成が示されたが、リセット信号の立ち上がりタイミングが1回しかなくても確実にリセット解除されるCPUを使用する場合には、符号941〜949で示された回路素子は不要である。その場合、リセットIC651の出力がそのままリセット端子に接続される。

この実施の形態で用いられるCPU56は、I/Oポート(PIO)およびタイマ/カウンタ回路(CTC)も内蔵している。PIOは、PB0〜PB3の4ビットおよびPA0〜PA7の1バイトのポートを有する。PB0〜PB3およびPA0〜PA7のポートは、入力/出力いずれにも設定できる。ただし、この実施の形態では内蔵PIOを使用しない。その場合には、例えば、全ポートを入力モードとして、全ポートをグラウンドレベルに接続する。なお、電源投入時に、PIOは自動的に入力モードに設定される。

また、図6に示すように、スイッチ基板190に搭載されたクリアスイッチ921の出力信号が、入力ポート570を介して入力される。なお、入力ポート570には、Vカウントスイッチ22などの他の各スイッチの出力信号も入力されている。このような構成によれば、クリアスイッチ921の切換により出力信号がクリア信号(ローレベル信号)とされていると、CPU56にクリア信号が与えられるので、CPU56により変動データ記憶手段の記憶内容が初期データとされる処理が行われるが、その詳細は後述する。

図7は、遊技機の電源基板910の一構成例を示すブロック図である。電源基板910は、主基板31、表示制御基板80、音声制御基板70、ランプ制御基板35および払出制御基板37等の電気部品制御基板と独立して設置され、遊技機内の各電気部品制御基板および機構部品が使用する電圧を生成する。この例では、AC24V、VSL(DC+30V)、DC+21V、DC+12VおよびDC+5Vを生成する。また、バックアップ電源となるコンデンサ916は、DC+5Vすなわち各基板上のIC等を駆動する電源のラインから充電される。

トランス911は、交流電源からの交流電圧を24Vに変換する。AC24V電圧は、コネクタ915に出力される。また、整流回路912は、AC24Vから+30Vの直流電圧を生成し、DC−DCコンバータ913およびコネクタ915に出力する。DC−DCコンバータ913は、+22V、+12Vおよび+5Vを生成してコネクタ915に出力する。コネクタ915は例えば中継基板に接続され、中継基板から各電気部品制御基板および機構部品に必要な電圧の電力が供給される。なお、トランス911の入力側には、遊技機に対する電源供給を停止したり開始させたりするための電源スイッチ920が設置されている。

DC−DCコンバータ913からの+5Vラインは分岐してバックアップ+5Vラインを形成する。バックアップ+5Vラインとグラウンドレベルとの間には大容量のコンデンサ916が接続されている。コンデンサ916は、遊技機に対する電力供給が遮断されたときの電気部品制御基板のバックアップRAM(電源バックアップされているRAMすなわち記憶内容保持状態となりうる記憶手段)に対して記憶状態を保持できるように電力を供給するバックアップ電源となる。また、+5Vラインとバックアップ+5Vラインとの間に、逆流防止用のダイオード917が挿入される。

なお、バックアップ電源として、+5V電源から充電可能な電池を用いてもよい。電池を用いる場合には、+5V電源から電力供給されない状態が所定時間継続すると容量がなくなるような充電池が用いられる。

また、電源基板910には、上述した第1の電源監視回路を構成する電源監視用IC902が搭載されている。電源監視用IC902は、VSL電源電圧を導入し、VSL電源電圧を監視することによって電源断の発生を検出する。具体的には、VSL電源電圧が所定値(この例では+22V)以下になったら、電源断が生ずるとして電圧低下信号を出力する。なお、監視対象の電源電圧は、各電気部品制御基板に搭載されている回路素子の電源電圧(この例では+5V)よりも高い電圧であることが好ましい。この例では、交流から直流に変換された直後の電圧であるVSLが用いられている。電源監視用IC902からの電圧低下信号は、主基板31や払出制御基板37等に供給される。

電源監視用IC902が電源断を検知するための所定値は、通常時の電圧より低いが、各電気部品制御基板上のCPUが暫くの間動作しうる程度の電圧である。また、電源監視用IC902が、CPU等の回路素子を駆動するための電圧(この例では+5V)よりも高く、また、交流から直流に変換された直後の電圧を監視するように構成されているので、CPUが必要とする電圧に対して監視範囲を広げることができる。従って、より精密な監視を行うことができる。さらに、監視電圧としてVSL(+30V)を用いる場合には、遊技機の各種スイッチに供給される電圧が+12Vであることから、電源瞬断時のスイッチオン誤検出の防止も期待できる。すなわち、+30V電源の電圧を監視すると、+30V作成の以降に作られる+12Vが落ち始める以前の段階でそれの低下を検出できる。よって、+12V電源の電圧が低下するとスイッチ出力がオン状態を呈するようになるが、+12Vより早く低下する+30V電源電圧を監視して電源断を認識すれば、スイッチ出力がオン状態を呈する前に電源復旧待ちの状態に入ってスイッチ出力を検出しない状態となることができる。

また、電源監視用IC902は、電気部品制御基板とは別個の電源基板910に搭載されているので、第1の電源監視回路から複数の電気部品制御基板に電圧低下信号を供給することができる。電圧低下信号を必要とする電気部品制御基板が幾つあっても第1の電源監視手段は1つ設けられていればよいので、各電気部品制御基板における各電気部品制御手段が後述する復帰制御を行っても、遊技機のコストはさほど上昇しない。

なお、図7に示された構成では、電源監視用IC902の検出出力(電圧低下信号)は、バッファ回路918,919を介してそれぞれの電気部品制御基板(例えば主基板31と払出制御基板37)に伝達されるが、例えば、1つの検出出力を中継基板に伝達し、中継基板から各電気部品制御基板に同じ信号を分配する構成でもよい。また、電圧低下信号を必要とする基板数に応じたバッファ回路を設けてもよい。

次に遊技機の動作について説明する。

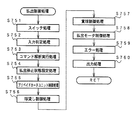

図8は、主基板31におけるCPU56が実行するメイン処理を示すフローチャートである。遊技機に対する電源が投入されると、メイン処理において、CPU56は、まず、必要な初期設定を行う(ステップS1)。

次いで、CPU56は、入力ポート570を介して入力されるクリアスイッチ921の出力信号の状態を、本例では1回だけ確認する(ステップS2)。クリアスイッチ921がオン(図4の「クリア」が選択されている状態)である場合には、ローレベルのクリア信号が出力されている。従って、CPU56は、クリアスイッチ921がオンとされていれば、通常の初期化処理を実行する(ステップS4)。

クリアスイッチ921は、この実施の形態では、電源スイッチ920のオンと同時に稼動状態(図4の「ON」が選択されている状態)となり、その後の判断により例えば直ちにオンとされる(例えば、図4の「ON」を経由してそのまま「クリア」に切り替られてオンとされる)。また、クリアスイッチ921は、電源スイッチ920押下後の例えば所定期間内にオンとされてもよい。なお、クリアスイッチ921が電源スイッチ920と連動された構成でない場合には、電源スイッチ920がオンする前にオンとされていてもよい。電源スイッチ920押下後にオン状態とされることを考慮して、ステップS2の判定前にディレイ時間をおいてもよい。また、CPU56がクリアスイッチ921の出力信号の状態を確認する時期は、電源が投入されたあとの所定期間内であれば何時であってもよい。また、CPU56がクリアスイッチ921の出力信号の状態を2回以上確認する構成としてもよい。

クリアスイッチ921がオンの状態でなければ(すなわち、図4の「クリア」でなく、「ON」が選択されている状態)、CPU56は、電源断時にバックアップRAM領域のデータ保護処理(例えばパリティデータの付加等の停電発生NMI処理)が行われたか否か確認する(ステップS3)。この実施の形態では、不測の電源断が生じた場合には、バックアップRAM領域のデータを保護するための処理が行われている。そのような保護処理が行われていた場合をバックアップありとする。バックアップなしを確認したら、CPU56は初期化処理を実行する(ステップS3,S4)。なお、この実施の形態では、バックアップRAM領域にバックアップデータがあるか否かは、電源断時にバックアップRAM領域に設定されるバックアップフラグの状態によって確認される。例えば、バックアップフラグ領域に「55H」が設定されていればバックアップあり(オン状態)を意味し、「55H」以外の値が設定されていればバックアップなし(オフ状態)を意味する。バックアップフラグ領域に設定されている「55H」は、停電発生NMI処理においてバックアップRAM領域のデータ保護処理が完了したときに設定されたデータであり、バックアップRAM領域のデータにもとづくパリティコードである。

バックアップRAM領域にバックアップデータがある場合には、CPU56は、バックアップRAM領域のデータチェック(例えばパリティチェック)を行う(ステップS5)。不測の電源断が生じた後に復旧した場合には、バックアップRAM領域のデータは保存されていたはずであるから、チェック結果は正常になる。チェック結果が正常でない場合には、内部状態を電源断時の状態に戻すことができないので、停電復旧時でない電源投入時に実行される初期化処理を実行する(ステップS6,S4)。

チェック結果が正常であれば、CPU56は、内部状態を電源断時の状態に戻すための遊技状態復旧処理を行う(ステップS7)。図9に示すように、バックアップフラグの値が「55H」に設定され、かつ、チェック結果が正常である場合に、ステップS7の遊技状態復旧処理が実行される。そして、バックアップRAM領域に保存されていたPC(プログラムカウンタ)の退避値がPCに設定され、そのアドレスに復帰する(ステップS8)。

通常の初期化処理の実行(ステップS4)が完了すると、メイン処理で、タイマ割込フラグの監視(ステップS10)の確認が行われるループ処理に移行する。なお、ループ内では、表示用乱数更新処理(ステップS9)も実行される。

なお、この実施の形態では、ステップS2でクリアスイッチ921がオンでない場合に、バックアップデータの有無が確認されていたが、逆に、バックアップデータの有無を確認した後、バックアップデータが存在する場合(さらに、バックアップ領域のチェックを行い、バックアップ領域のチェック結果が正常であったことが確認された場合であってもよい)にクリアスイッチ921の操作状態を確認するようにしてもよい。

また、この実施の形態では、ステップS3でバックアップデータの有無が確認された後、バックアップデータが存在する場合にステップS5でバックアップ領域のチェックが行われたが、逆に、バックアップ領域のチェック結果が正常であったことが確認された後、バックアップデータの有無の確認を行うようにしてもよい。また、バックアップデータの有無の確認、またはバックアップ領域のチェックの何れか一方の確認を行うことによって、停電復旧処理を実行するか否かを判定してもよい。

また、例えば停電復旧処理を実行するか否か判断する場合のパリティチェック(ステップS5)の際に、すなわち、遊技状態を復旧するか否か判断する際に、保存されていたRAMデータにおける特別プロセスフラグ等や始動入賞記憶数データによって、遊技機が遊技待機状態(図柄変動中でなく、大当り遊技中でなく、確変中でなく、また、始動入賞記憶がない状態)であることが確認されたら、遊技状態復旧処理を行わずに初期化処理を実行するようにしてもよい。

図10は、ステップS1の初期設定処理を示すフローチャートである。初期設定処理において、CPU56は、まず、割込禁止に設定する(ステップS1a)。割込禁止に設定すると、CPU56は、割込モードを割込モード2に設定し(ステップS1b)、スタックポインタにスタックポインタ指定アドレスを設定する(ステップS1c)。そして、CPU56は、内蔵デバイスレジスタの初期化を行う(ステップS1d)。また、内蔵デバイス(内蔵周辺回路)であるCTC(カウンタ/タイマ)およびPIO(パラレル入出力ポート)の初期化(ステップS1e)を行った後、RAMをアクセス可能状態に設定する(ステップS1f)。

この実施の形態で用いられているCPU56には、マスク可能な割込(INT)のモードとして以下の3種類のモードが用意されている。なお、マスク可能な割込が発生すると、CPU56は、自動的に割込禁止状態に設定するとともに、プログラムカウンタの内容をスタックにセーブする。

割込モード0:割込要求を行った内蔵デバイスがRST命令(1バイト)またはCALL命令(3バイト)をCPUの内部データバス上に送出する。よって、CPU56は、RST命令に対応したアドレスまたはCALL命令で指定されるアドレスの命令を実行する。リセット時に、CPU56は自動的に割込モード0になる。よって、割込モード1または割込モード2に設定したい場合には、初期設定処理において、割込モード1または割込モード2に設定するための処理を行う必要がある。

割込モード1:割込が受け付けられると、常に0038(h)番地に飛ぶモードである。

割込モード2:CPU56の特定レジスタ(Iレジスタ)の値(1バイト)と内蔵デバイスが出力する割込ベクタ(1バイト:最下位ビット0)から合成されるアドレスが、割込番地を示すモードである。すなわち、割込番地は、上位アドレスが特定レジスタの値とされ下位アドレスが割込ベクタとされた2バイトで示されるアドレスである。従って、任意の(飛び飛びではあるが)偶数番地に割込処理を設置することができる。各内蔵デバイスは割込要求を行うときに割込ベクタを送出する機能を有している。

よって、割込モード2に設定されると、各内蔵デバイスからの割込要求を容易に処理することが可能になり、また、プログラムにおける任意の位置に割込処理を設置することが可能になる。さらに、割込モード1とは異なり、割込発生要因毎のそれぞれの割込処理を用意しておくことも容易である。上述したように、この実施の形態では、初期設定処理のステップS1bにおいて、CPU56は割込モード2に設定される。

図11は、通常の初期化処理(ステップS4)の処理を示すフローチャートである。図11に示すように、初期化処理では、RAMのクリア処理が行われる(ステップS4a)。次いで、作業領域初期設定テーブルのアドレス値にもとづいて、所定の作業領域(例えば、普通図柄判定用乱数カウンタ、普通図柄判定用バッファ、特別図柄左中右図柄バッファ、払出コマンド格納ポインタなど)に初期値(初期データ)を設定する初期値設定処理(ステップS4b)が行われる。そして、2ms毎に定期的にタイマ割込がかかるようにCPU56に設けられているCTCのレジスタの設定が行われる(ステップS4c)。すなわち、初期値(初期データ)として2msに相当する値が所定のレジスタ(時間定数レジスタ)に設定される。そして、初期設定処理(ステップS1)において割込禁止(図10参照)とされているので、初期化処理を終える前に割込が許可される(ステップS4d)。

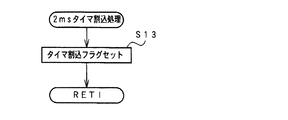

従って、この実施の形態では、CPU56の内蔵CTCが繰り返しタイマ割込を発生するように設定される。この実施の形態では、繰り返し周期は2msに設定される。そして、図12に示すように、タイマ割込が発生すると、CPU56は、タイマ割込フラグをセットする(ステップS13)。

CPU56は、ステップS10において、タイマ割込フラグがセットされたことを検出すると、タイマ割込フラグをリセットするとともに(ステップS11)、遊技制御処理を実行する(ステップS12)。以上の制御によって、この実施の形態では、遊技制御処理は2ms毎に起動されることになる。なお、この実施の形態では、タイマ割込処理ではフラグセットのみがなされ、遊技制御処理はメイン処理において実行されるが、タイマ割込処理で遊技制御処理を実行してもよい。

以上のように、この実施の形態では、クリアスイッチの操作状態に応じて電源断時の状態に復旧するか否かの判断が行われる。従って、例えば停電後の電源復旧時や遊技機の再稼動時などにおいて電源投入される際に、状況に応じた判断により、バックアップデータ記憶領域の内容にもとづいて電源断時の状態に復旧させ、あるいは初期データにもとづいて稼動を開始させることを選択することができる。従って、電源断が発生しても、遊技者に不利益がもたらされることを防止することができるとともに、遊技店での遊技機運用上の利便性を向上させることもできる。

図13は、ステップS12の遊技制御処理を示すフローチャートである。遊技制御処理において、CPU56は、まず、スイッチ回路58を介して、ゲートセンサ12、始動口センサ17、カウントセンサ23および入賞口スイッチ19a,24aの状態を入力し、各入賞口や入賞装置に対する入賞があったか否か判定する(スイッチ処理:ステップS21)。

次いで、パチンコ遊技機1の内部に備えられている自己診断機能によって種々の異常診断処理が行われ、その結果に応じて必要ならば警報が発せられる(エラー処理:ステップS22)。

次に、遊技制御に用いられる大当り判定用の乱数等の各判定用乱数を示す各カウンタを更新する処理を行う(ステップS23)。CPU56は、さらに、停止図柄の種類を決定する乱数等の表示用乱数を更新する処理を行う(ステップS24)。

さらに、CPU56は、特別図柄プロセス処理を行う(ステップS25)。特別図柄プロセス制御では、遊技状態に応じてパチンコ遊技機1を所定の順序で制御するための特別図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、特別図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。また、普通図柄プロセス処理を行う(ステップS26)。普通図柄プロセス処理では、7セグメントLEDによる可変表示器10を所定の順序で制御するための普通図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、普通図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。

また、CPU56は、払出制御基板37等に送出される制御コマンドをRAM55の所定の領域に設定して制御コマンドを送出する処理を行う(コマンド制御処理:ステップS27)。

次いで、CPU56は、例えばホール管理用コンピュータに供給される大当り情報、始動情報、確率変動情報などのデータを出力するデータ出力処理を行う(ステップS29)。

また、CPU56は、所定の条件が成立したときにソレノイド回路59に駆動指令を行う(ステップS30)。ソレノイド回路59は、駆動指令に応じてソレノイド16,21を駆動し、可変入賞球装置15または開閉板20を開状態または閉状態とする。

また、CPU56は、各入賞口への入賞を検出するためのスイッチ17,23,19a,24aの検出出力にもとづく賞球数の設定などを行う(ステップS31)。具体的には、入賞検出に応じて払出制御基板37に払出制御コマンドを出力する。払出制御基板37に搭載されている払出制御用CPU371は、払出制御コマンドに応じて賞球払出装置97Aを駆動する。

このように、メイン処理には遊技制御処理に移行すべきか否かを判定する処理が含まれ、CPU56の内部タイマが定期的に発生するタイマ割込にもとづくタイマ割込処理で遊技制御処理に移行すべきか否かを判定するためのフラグがセットされるので、遊技制御処理の全てが確実に実行される。つまり、遊技制御処理の全てが実行されるまでは、次回の遊技制御処理に移行すべきか否かの判定が行われないので、遊技制御処理中の全ての各処理が実行完了することは保証されている。

なお、ここでは、主基板31のCPU56が実行する遊技制御処理は、CPU56の内部タイマが定期的に発生するタイマ割込にもとづくタイマ割込処理でセットされるフラグに応じて実行されたが、定期的に(例えば2ms毎)信号を発生するハードウェア回路を設け、その回路からの信号をCPU56の外部割込端子に導入し、割込信号によって遊技制御処理に移行すべきか否かを判定するためのフラグをセットするようにしてもよい。

そのように構成した場合にも、遊技制御処理の全てが実行されるまでは、フラグの判定が行われないので、遊技制御処理中の全ての各処理が実行完了することが保証される。

図14は、電源基板910の電源監視回路からの電圧変化信号にもとづくNMIに応じて実行される停電発生NMI処理の一例を示すフローチャートである。停電発生NMI処理において、CPU56は、まず、停電時などの電源断時直前の割込許可/禁止状態をバックアップするために、割込禁止フラグの内容をパリティフラグに格納する(ステップS41)。次いで、割込禁止に設定する(ステップS42)。停電発生NMI処理ではRAM内容の保存を確実にするためにチェックサムの生成処理を行う。その処理中に他の割込処理が行われたのではチェックサムの生成処理が完了しないうちにCPUが動作し得ない電圧にまで低下してしまうことが考えられるので、まず、他の割込が生じないような設定がなされる。なお、停電発生NMI処理におけるステップS44〜S50は、電力供給停止時処理の一例である。

なお、割込処理中では他の割込がかからないような仕様のCPUを用いている場合には、ステップS42の処理は不要である。

次いで、CPU56は、バックアップフラグが既にセットされているか否か確認する(ステップS42)。バックアップフラグが既にセットされていれば、以後の処理を行わない。バックアップフラグがセットされていなければ、以下の電力供給停止時処理を実行する。すなわち、ステップS44からステップS50の処理を実行する。

まず、各レジスタの内容をバックアップRAM領域に格納する(ステップS44)。その後、バックアップフラグをセットする(ステップS45)。そして、バックアップRAM領域のバックアップチェックデータ領域に適当な初期値を設定し(ステップS46)、初期値およびバックアップRAM領域のデータについて順次排他的論理和をとったあと反転し(ステップS47)、最終的な演算値をバックアップパリティデータ領域に設定する(ステップS48)。また、RAMアクセス禁止状態にする(ステップS49)。さらに、全ての出力ポートをオフ状態にする(ステップS50)。電源電圧が低下していくときには、各種信号線のレベルが不安定になってRAM内容が化ける可能性があるが、このようにRAMアクセス禁止状態にしておけば、バックアップRAM内のデータが化けることはない。

次いで、CPU56は、ループ処理にはいる。すなわち、何らの処理もしない状態になる。従って、図6に示されたリセットIC651からのシステムリセット信号によって外部から動作禁止状態にされる前に、内部的に動作停止状態になる。よって、電源断時に確実にCPU56は動作停止する。その結果、上述したRAMアクセス禁止の制御および動作停止制御によって、電源電圧が低下していくことに伴って生ずる可能性がある異常動作に起因するRAMの内容破壊等を確実に防止することができる。

なお、この実施の形態では、停電発生NMI処理では最終部でプログラムをループ状態にしたが、ホールト(HALT)命令を発行するように構成してもよい。

また、レジスタの内容をRAM領域に格納した後にセットされるバックアップフラグは、上述したように、電源投入時において復旧すべきバックアップデータがあるか否か(停電からの復旧か否か)を判断する際に使用される。また、ステップS41からS50の処理は、CPU56がシステムリセット回路65からのシステムリセット信号を受ける前に完了する。換言すれば、システムリセット回路65からのシステムリセット信号を受ける前に完了するように、電圧監視回路の検出電圧の設定が行われている。

この実施の形態では、電力供給停止時処理開始時に、バックアップフラグの確認が行われる。そして、バックアップフラグが既にセットされている場合には電力供給停止時処理を実行しない。上述したように、バックアップフラグは、必要なデータのバックアップが完了し、その後電力供給停止時処理が完了したことを示すフラグである。従って、例えば、リセット待ちのループ状態で何らかの原因で再度NMIが発生したとしても、電力供給停止時処理が重複して実行されてしまうようなことはない。

ただし、割込処理中では他の割込がかからないような仕様のCPUを用いている場合には、ステップS43の判断は不要である。

図15は、バックアップパリティデータ作成方法の一例を説明するための説明図である。ただし、図15に示す例では、簡単のために、バックアップデータRAM領域のデータのサイズを3バイトとする。電源電圧低下にもとづく停電発生処理において、図15に示すように、バックアップチェックデータ領域に、初期データ(この例では00H)が設定される。次に、「00H」と「F0H」の排他的論理和がとられ、その結果と「16H」の排他的論理和がとられる。さらに、その結果と「DFH」の排他的論理和がとられる。そして、その結果(この例では「39H」)を反転して得られた値(この例では「C6H」)がバックアップパリティデータ領域に設定される。

電源が再投入されたときには、停電復旧処理においてパリティ診断が行われる。バックアップ領域の全データがそのまま保存されていれば、電源再投入時に、図15に示すようなデータがバックアップ領域に設定されている。

ステップS5の処理において、CPU56は、電源発生MNI処理にて実行された処理と同様の処理を行う。すなわち、バックアップチェックデータ領域に、初期データ(この例では00H)が設定され、「00H」と「F0H」の排他的論理和がとられ、その結果と「16H」の排他的論理和がとられる。さらに、その結果と「DFH」の排他的論理和がとられる。そして、その結果(この例では「39H」)を反転した最終演算結果を得る。バックアップ領域の全データがそのまま保存されていれば、最終的な演算結果は、「C6H」、すなわちバックアップチェックデータ領域に設定されているデータと一致する。バックアップRAM領域内のデータにビット誤りが生じていた場合には、最終的な演算結果は「C6H」にならない。

よって、CPU56は、最終的な演算結果とバックアップチェックデータ領域に設定されているデータとを比較して、一致すればパリティ診断正常とする。一致しなければ、パリティ診断異常とする。

以上のように、この実施の形態では、遊技制御手段には、遊技機の電源が断しても、所定期間電源バックアップされる変動データ記憶手段(この例ではバックアップRAM)が設けられ、電源投入時に、CPU56(具体的にはCPU56が実行するプログラム)は、変動データ記憶手段がバックアップ状態にあればバックアップデータにもとづいて遊技状態を回復させる遊技状態復旧処理(ステップS7)を行うように構成される。

その際、クリアスイッチ921がオン状態であれば、遊技状態復旧処理は実行されず、通常の初期化処理(ステップS4)が実行される。従って、遊技店員等は、電源スイッチ920の投入等にもとづく遊技機の電源投入時に、クリアスイッチ921を操作することによって、変動データ記憶手段に記憶されているバックアップデータにもとづく遊技状態復旧処理を実行するか否かを選択することができる。従って、電源断が発生しても遊技者に不利益がもたらされることを防止することができるとともに、遊技店での遊技機運用上の利便性を向上させることもできる遊技機が提供される。

なお、電源投入時に、変動データ記憶手段にバックアップデータが記憶されていない場合に実行される初期化処理と、変動データ記憶手段にバックアップデータが記憶されていてもクリアスイッチ921がオフ状態である場合に実行される初期化処理とは、プログラム上兼用されている(図8のステップS4参照)。従って、遊技店での運用上の利便性を向上させる制御を付加しても、プログラム容量はさほど増えない。

この実施の形態では、図7に示されたように電源基板910に電源監視回路が搭載され、図6に示されたように主基板31にシステムリセット回路65が搭載されている。そして、電源電圧が低下していくときに、システムリセット回路65がローレベルのシステムリセット信号を発生する時期は、電源監視回路(この例では電源監視用IC902)がローレベルのNMI割込信号を発生する時期よりも遅くなるように設定されている。さらに、システムリセット回路65からのローレベルのシステムリセット信号は、CPU56のリセット端子に入力されている。

すると、CPU56は、電源監視手段(電源監視用IC902)からの電圧低下信号にもとづいて停電発生処理(電力供給停止時処理)を実行した後にループ状態に入るのであるが、ループ状態において、リセット状態に入ることになる。すなわち、CPU56の動作が完全に停止する。+5V電源電圧値以下においては、CPU56の正常な動作が担保できない(即ち、動作の管理ができない状態が発生する)が、CPU56は正常に動作できる電源が供給されている状態でリセット状態になるので、不定データにもとづいて異常動作してしまうことは防止される。

このように、この実施の形態では、CPU56が、電源監視回路からの検出出力の入力に応じてループ状態に入るとともに、システムリセット回路65からの検出出力の入力に応じてシステムリセットされるように構成されている。従って、電源断時に確実なデータ保存が行われ、遊技者に不利益がもたらされることが防止される。

なお、この実施の形態では、電源監視用IC902と、システムリセット回路65は、同一の電源電圧を監視しているが、異なる電源電圧を監視してもよい。例えば、電源基板910の電源監視回路が+30V電源電圧を監視し、システムリセット回路65が+5V電源電圧を監視してもよい。そして、システムリセット回路65がローレベルのシステムリセット信号を発生するタイミングは電源監視回路がNMI割込信号を発生するタイミングに対して遅くなるように、システムリセット回路65のしきい値レベル(システムリセット信号を発生する電圧レベル)が設定される。例えば、しきい値は4.25Vである。4.25Vは、通常時の電圧より低いが、CPU56が暫くの間動作しうる程度の電圧である。なお、システムリセット回路65に設けられた遅延手段の遅延時間(例えばコンデンサの容量)を調整して、システムリセット回路65がローレベルのシステムリセット信号を発生するタイミングを電源監視回路がNMI割込信号を発生するタイミングに対して遅らせるようにしてもよい。

また、上記の実施の形態では、CPU56は、マスク不能割込端子(NMI端子)を介して電源基板からのNMI割込信号(電源監視手段からのNMI割込信号)を検知したが、NMI割込信号をマスク可能割込割込端子(IRQ端子)に導入してもよい。その場合には、割込処理(IRQ処理)で電力供給停止時処理が実行される。また、入力ポートを介して電源基板からのNMI割込信号を検知してもよい。その場合には、メイン処理において入力ポートの監視が行われる。

また、NMI割込信号に変えて、IRQ端子を介して電源基板からの割込信号を検知する場合に、メイン処理のステップS12における遊技制御処理の開始時にIRQ割込マスクをセットし、遊技制御処理の終了時にIRQ割込マスクを解除するようにしてもよい。そのようにすれば、遊技制御処理の開始前および終了後に割込がかかることになって、遊技制御処理が中途で中断されることはない。従って、払出制御コマンドを払出制御基板37に送出しているときなどにコマンド送出が中断されてしまうようなことはない。よって、停電が発生するようなときでも、払出制御コマンド等は確実に送出完了する。

また、この実施の形態では、停電発生処理(電力供給停止時処理)において、既にデータがバックアップされ電力供給停止時処理が既に実行されたことを示すバックアップフラグがセットされている場合には電力供給停止時処理を実行しないように構成されている。電源が断する過程では、再度NMIが発生する可能性がある。すると、停電発生処理においてバックアップフラグの確認を行わない場合には、再度発生したNMIによって再度電力供給停止時処理が実行される。

最初に実行された正規の電力供給停止時処理では、レジスタの内容をバックアップRAMに格納する処理が行われる(図14におけるステップS44参照)。最初に実行された正規の電力供給停止時処理後のリセット待ちの状態では電源電圧が徐々に低下していくので、レジスタの内容が破壊される可能性もある。すなわち、レジスタ値は、電源断が検出されたときの状態(最初にNMIが発生したとき)から変化している可能性がある。そのような状態で再度電力供給停止時処理が実行されると、電源断が検出されたときの状態のレジスタ値とは異なる値がバックアップRAMに格納されてしまう。すると、電源復旧時に実行される停電復旧処理において、電源断が検出されたときの状態のレジスタ値とは異なる値がレジスタに復旧されてしまう。その結果、電源断時の遊技状態とは異なる遊技状態が再現されてしまう可能性が生ずる。

以下、遊技状態復旧処理について説明する。

図16は、図8のステップS7に示された遊技状態復旧処理の一例を示すフローチャートである。この例では、CPU56は、バックアップRAMに保存されていた値を各レジスタに復元する(ステップS61)。そして、バックアップRAMに保存されていたデータにもとづいて停電時の遊技状態を確認して復帰させる(ステップS62)。例えば、バックアップRAMに保存されていたデータにもとづいて、ソレノイド回路59を介してソレノイド16やソレノイド21を駆動し、始動入賞口14や開閉板20の開閉状態の復旧を行う。また、電源断中でも保存されていた特別図柄プロセスフラグおよび普通図柄プロセスフラグの値に応じて、電源断時の特別図柄プロセス処理の進行状況および普通図柄プロセス処理の進行状況に対応した制御コマンドを、表示制御基板80、ランプ制御基板35および音声制御基板70に送出する(ステップS64)。

以上のように、遊技状態復旧処理では、復元された内部状態に応じて、各種電気部品の状態復元が行われるとともに、表示制御基板80、ランプ制御基板35および音声制御基板70に対して、制御状態を電源断時の状態に戻すための制御コマンド(電源断時の制御状態を生じさせるための制御コマンド)が送出される。そのような制御コマンドは、一般に、電源断前に最後に送出された1つまたは複数の制御コマンドである。

その結果、この実施の形態では、遊技状態復旧処理によって、以下のような状態復旧が可能である。

始動入賞口14および大入賞口(開閉板20)の状態が復元される。表示制御手段によって制御される普通図柄の表示状態(可変表示器10の表示状態)は、電源断時に変動中であった場合を除いて復元される。表示制御手段によって制御される特別図柄の表示状態(可変表示部9の表示状態)は、電源断時に変動中であった場合を除いて復元される。さらに、可変表示部9に表示される背景やキャラクタは、特別図柄変動中および大当り遊技中であった場合を除いて復元される。

特別図柄の変動中に電源断となった場合には、可変表示パターンの変動時間(例えば10秒)および既に実行した時間(例えば4秒)の情報がバックアップされる。そして、主基板31は、復旧時に、表示パターンを示す表示制御コマンドおよび停止図柄を示す表示制御コマンドを表示制御基板80に出力し、残り時間(上述の例では6秒)経過後に、図柄を停止させるため表示制御コマンドを出力する。従って、特別図柄の表示状態は、電源断時に特別図柄の変動中であった場合には、復旧時に、表示されていない残りの時間(上述の例では6秒)につき可変表示が実行される。なお、復旧時に表示制御基板80に対して出力される表示パターンを示す表示制御コマンドは、電源断前に出力された表示パターンを示す表示制御コマンドと同じものであってもよいが、「停電復旧中です」のような画像を表示させるためのコマンドとしてもよい。この場合、「停電復旧中です」の表示は、残りの時間(上述の例では6秒)表示される。なお、特別図柄の変動中に電源断となった場合の、普通図柄の表示状態にについても、上述と同様の制御が行われる。

なお、大当り遊技中に電源断となった場合にも、上述した特別図柄の変動中に電源断となった場合と同様に、ラウンド中あるいはラウンド間のインターバルの残り時間について、復旧時に、表示、音、ランプ、ソレノイド21などを制御するが、主基板31は、表示制御基板80に対して電源断前に出力した確定時の図柄(停止図柄)を指定する表示制御コマンドを出力する。これにより、ラウンド中あるいはラウンド間の大当り図柄による演出が可能となり(大当り図柄で大当り演出する機種について)、また、大当り終了後の変動開始時に表示する図柄も表示制御基板80が認識することができる。

ランプ制御手段が制御する装飾ランプ25、始動記憶表示器18、ゲート通過記憶表示器41、賞球ランプ51および球切れランプ52の表示状態が復元される。遊技効果ランプ・LED28a,28b,28cの表示状態は、特別図柄変動中および大当り遊技中であった場合を除いて復元される。ただし、電源断時に大当り遊技中であった場合には、各制御区間の最初の状態に復元可能である。各制御区間とは、例えば、大当り開始報知状態、大入賞口開放前状態、大入賞口開放中状態、大当り終了報知状態である。なお、特別図柄変動中に電源断となったあと復旧した場合には、上述した可変表示部9や可変表示装置10の表示制御と同様に、残り時間分だけ遊技効果ランプ・LED28a,28b,28cの表示状態を制御するようにしてもよいが、消灯または停電復旧時特有のパターンで点灯/点滅させるようにしてもよい。

音声制御手段が制御する音発生状態は、特別図柄変動中および大当り遊技中であった場合を除いて復元される。ただし、電源断時に大当り遊技中であった場合には、各制御区間の最初の状態に復元可能である。なお、特別図柄変動中に電源断となったあと復旧した場合には、上述した可変表示部9や可変表示装置10の表示制御と同様に、残り時間分だけ音発生状態を制御するようにしてもよいが、無音または停電復旧時特有の音声パターン(例えば「停電復旧中です」との音声)を出力するようにしてもよい。

なお、この実施の形態では、電源断からの復旧時に、主基板31の遊技制御手段から表示制御手段、ランプ制御手段および音声制御手段に対して状態復元のための制御コマンドが送出されるが、表示制御手段、ランプ制御手段および音声制御手段が電源バックアップされる場合には、主基板31からの制御コマンドを用いることなく、表示制御手段、ランプ制御手段および音声制御手段が独自に制御状態を復元するように構成してもよい。

また、後述するように、払出制御基板37に搭載されている払出制御手段は、電源バックアップされているので、電源断からの復旧時に、賞球払出状態および球貸し制御状態は、電源断時の状態に復旧する。この実施の形態では、発射制御基板は払出制御手段に接続されているので、発射制御基板91における制御状態も同様に復元される。

遊技状態を電源断時の状態に復帰させると、この実施の形態では、CPU56は、前回の電源断時の割込許可/禁止状態を復帰させるため、バックアップRAMに保存されていたパリティフラグの値を確認する(ステップS65)。パリティフラグがクリアであれば、割込許可設定を行う(ステップS66)。一方、パリティフラグがオンであれば、そのまま(ステップS1aで設定された割込禁止状態のまま)遊技状態復旧処理を終える。

なお、ここでは、遊技状態復旧処理が終了するとメイン処理にリターンするように遊技状態復旧処理プログラムが構成されているが、電力供給停止時処理において保存されているスタックポインタが指すスタックエリア(バックアップRAM領域にある)に記憶されているアドレス(電源断時のNMI割込発生時に実行されていたアドレス)に戻るようにしてもよい。

上述したように、初期設定処理を開始したあと、復旧処理を終える前まで、または初期化処理を終える前までの間は、割込禁止状態とする構成としたことで、割込みにより処理が中断されることを防止することができるため、初期設定、クリアスイッチ921の操作状態やバックアップデータ記憶領域の内容に応じて行われる電源断時の状態に復旧させるか否かの判断、および復旧処理(または初期化処理)を確実に完了させることができる。なお、上記のように復旧処理を終える前まで割込禁止状態とする構成とした場合であっても、電源断時の割込禁止/許可状態をパリティフラグによりバックアップしているため、復旧処理において電源断時の割込禁止/許可状態を確実に復旧させることができる。

なお、上記の実施の形態では、遊技制御手段において、データ保存処理および復旧処理が行われる場合について説明したが、払出制御手段、音声制御手段、ランプ制御手段および表示制御手段におけるRAMの一部も電源バックアップされ、払出制御手段、表示制御手段、音制御手段およびランプ制御手段も、上述したような処理を行ってもよい。ただし、払出制御手段、表示制御手段、音制御手段およびランプ制御手段は、復旧時にコマンド送出処理を行う必要はない。

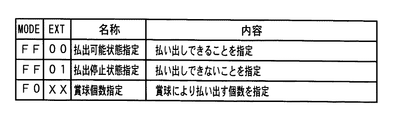

図17は、払出制御コマンドのコマンド形態の一例を示す説明図である。この実施の形態では、払出制御コマンドは2バイト構成であり、1バイト目はMODE(コマンドの分類)を表し、2バイト目はEXT(コマンドの種類)を表す。なお、図17に示されたコマンド形態は一例であって他のコマンド形態を用いてもよい。

図18は、払出制御コマンドの内容の一例を示す説明図である。図18に示された例において、コマンドFF00(H)は、払出可能状態を指定する払出制御コマンドである。コマンドFF01(H)は、払出停止状態を指定する払出制御コマンドである。また、コマンドF0XX(H)は、賞球個数を指定する払出制御コマンドである。2バイト目の「XX」が払出個数を示す。

払出制御手段は、主基板31の遊技制御手段からFF01(H)の払出制御コマンドを受信すると賞球払出および球貸しを停止する状態となり、FF00(H)の払出制御コマンドを受信すると賞球払出および球貸しができる状態になる。また、賞球個数を指定する払出制御コマンドを受信すると、受信したコマンドで指定された個数に応じた賞球払出制御を行う。

図19は、払出制御コマンドの送出形態の一例を示すタイミング図である。この実施の形態では、払出制御コマンドは2バイト構成であり、例えば、図19に示されるように、払出制御信号の1バイト目および2バイト目が出力されているときに、それぞれINT信号がオン(この例ではローレベル)になる。INT信号のオン期間は例えば1μs以上であり、1バイト目と2バイト目との間には例えば10μs以上の期間があけられる。なお、払出制御コマンドは、1バイト構成としてもよい。

なお、払出制御コマンドは、払出制御手段が認識可能に1回だけ送出される。認識可能とは、この例では、INT信号がオン状態になることであり、認識可能に1回だけ送出されるとは、この例では、払出制御信号の1バイト目および2バイト目のそれぞれに応じてINT信号が1回だけオン状態になることである。

なお、図20に示すように、払出制御コマンドを1バイト構成としてもよい。その場合、8ビットの払出制御信号CD〜CD7によって払出制御コマンドが出力される。そして、払出制御信号が出力されているときに、INT信号がオン(この例ではローレベル)になる。INT信号のオン期間は例えば1μs以上である。払出制御手段は、INT信号に応じた割込処理によって払出制御信号CD〜CD7を入力する。

次に、遊技制御手段以外の電気部品制御手段において各処理が行われる場合の例として、払出制御手段においてデータ保存や復旧などが行われる場合について説明する。

図21は、払出制御用CPU371周りの一構成例を示すブロック図である。図21に示すように、第1の電源監視回路(第1の電源監視手段)からの電圧低下信号が、バッファ回路960を介して払出制御用CPU371のマスク不能割込端子(XNMI端子)に接続されている。第1の電源監視回路は、遊技機が使用する各種直流電源のうちのいずれかの電源の電圧を監視して電源電圧低下を検出する回路である。この実施の形態では、VSLの電源電圧を監視して電圧値が所定値以下になるとローレベルの電圧低下信号を発生する。VSLは、遊技機で使用される直流電圧のうちで最大のものであり、この例では+30Vである。従って、払出制御用CPU371は、割込処理によって電源断の発生を確認することができる

払出制御用CPU371のCLK/TRG2端子には、主基板31からのINT信号が接続されている。CLK/TRG2端子にクロック信号が入力されると、払出制御用CPU371に内蔵されているタイマカウンタレジスタCLK/TRG2の値がダウンカウントされる。そして、レジスタ値が0になると割込が発生する。従って、タイマカウンタレジスタCLK/TRG2の初期値を「1」に設定しておけば、INT信号の入力に応じて割込が発生することになる。

払出制御基板37には、システムリセット回路975も搭載されているが、この実施の形態では、システムリセット回路975は、第2の電源監視回路(第2の電源監視手段)も兼ねている。すなわち、リセットIC976は、電源投入時に、外付けのコンデンサに容量で決まる所定時間だけ出力をローレベルとし、所定時間が経過すると出力をハイレベルにする。また、リセットIC976は、電源基板910に搭載されている第1の電源監視回路が監視する電源電圧と等しい電源電圧であるVSLの電源電圧を監視して電圧値が所定値(例えば+9V)以下になるとローレベルの電圧低下信号を発生する。従って、電源断時には、リセットIC976からの電圧低下信号がローレベルになることによって払出制御用CPU371がシステムリセットされる。なお、図21に示すように、電圧低下信号はリセット信号と同じ出力信号である。

リセットIC976が電源断を検知するための所定値は、通常時の電圧より低いが、払出制御用CPU371が暫くの間動作しうる程度の電圧である。また、リセットIC976が、払出制御用CPU371が必要とする電圧(この例では+5V)よりも高い電圧を監視するように構成されているので、払出制御用CPU371が必要とする電圧に対して監視範囲を広げることができる。従って、より精密な監視を行うことができる。

+5V電源から電力が供給されていない間、払出制御用CPU371の内蔵RAMの少なくとも一部は、電源基板から供給されるバックアップ電源がバックアップ端子に接続されることによってバックアップされ、遊技機に対する電源が断しても内容は保存される。そして、+5V電源が復旧すると、システムリセット回路975からリセット信号が発せられるので、払出制御用CPU371は、通常の動作状態に復帰する。そのとき、必要なデータがバックアップされているので、停電等からの復旧時には停電発生時の遊技状態に復帰することができる。

以上のように、この実施の形態では、電源基板910に搭載されている第1の電源監視回路が、遊技機で使用される直流電圧のうちで最も高い電源VSLの電圧を監視して、その電源の電圧が所定値を下回ったら電圧低下信号(電源断検出信号)を発生する。電源断検出信号が出力されるタイミングでは、IC駆動電圧は、まだ各種回路素子を十分駆動できる電圧値になっている。従って、IC駆動電圧で動作する払出制御基板37の払出制御用CPU371が所定の電力供給停止時処理を行うための動作時間が確保されている。

なお、ここでも、第1の電源監視回路は、遊技機で使用される直流電圧のうちで最も高い電源VSLの電圧を監視することになるが、電源断検出信号を発生するタイミングが、IC駆動電圧で動作する電気部品制御手段が所定の電力供給停止時処理を行うための動作時間が確保されるようなタイミングであれば、監視対象電圧は、最も高い電源VSLの電圧でなくてもよい。すなわち、少なくともIC駆動電圧よりも高い電圧を監視すれば、電気部品制御手段が所定の電力供給停止時処理を行うための動作時間が確保されるようなタイミングで電源断検出信号を発生することができる。

その場合、上述したように、監視対象電圧は、賞球カウントスイッチ301A等の遊技機の各種スイッチに供給される電圧が+12Vであることから、電源断時のスイッチオン誤検出の防止も期待できる電圧であることが好ましい。すなわち、スイッチに供給される電圧(スイッチ電圧)である+12V電源電圧が落ち始める以前の段階で、電圧低下を検出できることが好ましい。よって、少なくともスイッチ電圧よりも高い電圧を監視することが好ましい。

なお、図21に示すように、スイッチ基板190に搭載されたクリアスイッチ921の出力信号が、入力ポート372を介して入力される。なお、入力ポート372には、本例では、賞球カウントスイッチ301Aおよび球貸しカウントスイッチ301Bの各スイッチの出力信号も入力されている。このような構成によれば、クリアスイッチ921の切換により出力信号がクリア信号(ローレベル信号)とされていると、払出制御用CPU371にクリア信号が与えられるので、払出制御用CPU371により後述する初期化処理が行われる。

なお、図21に示された構成では、システムリセット回路975は、電源投入時に、コンデンサの容量で決まる期間のローレベルを出力し、その後ハイレベルを出力する。すなわち、リセット解除タイミングは1回だけである。しかし、図6に示された主基板31の場合と同様に、複数回のリセット解除タイミングが発生するような回路構成を用いてもよい。

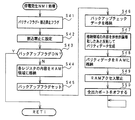

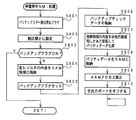

図22は、払出制御用CPU371のメイン処理を示すフローチャートである。メイン処理では、払出制御用CPU371は、まず、必要な初期設定を行う(ステップS701)。

図23は、ステップS701の初期設定処理を示すフローチャートである。初期設定処理において、払出制御用CPU371は、まず、割込禁止に設定する(ステップS701a)。次に、払出制御用CPU371は、割込モードを割込モード2に設定し(ステップS701b)、スタックポインタにスタックポインタ指定アドレスを設定する(ステップS701c)。また、払出制御用CPU371は、内蔵デバイスレジスタの初期化(ステップS701d)、CTC(カウンタ/タイマ)およびPIO(パラレル入出力ポート)の初期化(ステップS701e)を行ったあと、RAMをアクセス可能状態に設定する(ステップS701f)。

この実施の形態では、タイマ/カウンタ割込としてCH2,CH3のカウントアップにもとづく割込を使用する。CH2のカウントアップにもとづく割込は、上述したタイマカウンタレジスタCLK/TRG2の値が「0」になったときに発生する割込である。従って、ステップS701eにおいて、タイマカウンタレジスタCLK/TRG2に初期値「1」が設定される。また、CH3のカウントアップにもとづく割込は、CPUの内部クロックをカウントダウンしてレジスタ値が「0」になったら発生する割込であり、後述する2msタイマ割込として用いられる。具体的には、CH3のレジスタ値はシステムクロックの1/256周期で減算される。ステップS701eにおいて、CH3のレジスタには、初期値として2msに相当する値が設定される。なお、CH2に関する割込番地は0074Hであり、CH3に関する割込番地は0076Hである。

次いで、払出制御用CPU371は、入力ポート372を介して入力されるクリアスイッチ921の出力信号の状態を、本例では1回だけ確認する(ステップS702)。クリアスイッチ921がオン(図4の「クリア」とされている状態)である場合には、その出力がローレベルとされている。従って、払出制御用CPU371は、クリアスイッチ921がオンであれば、通常の初期化処理を実行する(ステップS704)。なお、クリアスイッチ921は、電源スイッチ920がオンする前にオンとされていてもよく、電源スイッチ920と同時にオンとされてもよい。さらに、電源スイッチ920押下後の例えば所定期間内にオンとされてもよい。電源スイッチ920押下後にオン状態とされることを考慮して、ステップS2の判定前にディレイ時間をおいてもよい。

クリアスイッチ921がオフ状態(図4の「ON」とされている状態)であれば、払出制御用CPU371は、払出制御用のバックアップRAM領域にバックアップデータが存在しているか否かの確認を行う(ステップS703)。すなわち、例えばバックアップRAM領域に形成されている後述する総合個数記憶または貸し球個数記憶(図26参照)などの記憶情報の有無を確認して、例えば未払出の賞球個数および貸し球個数に関するバックアップデータがないかどうか確認する。不測の電源断が生じた場合には、多くの場合何らかのデータがバックアップRAM領域に保存されており、バックアップRAM領域のデータは保存されていたはずであるから、後に復旧した場合の確認結果の多くはバックアップデータありとなる。バックアップデータなしという確認結果であれば、前回の電源オフ時に未払出の遊技球がなかったことになり、内部状態を電源断時の状態に戻す必要がないので、停電復旧時でない電源投入時に実行される初期化処理を実行する(ステップS703,S704)。なお、本例では、バックアップRAM領域にバックアップデータが存在しているか否かは、電源断時にバックアップRAM領域に設定されるバックアップフラグによって確認する。

バックアップRAM領域にバックアップデータが存在している場合には、この実施の形態では、払出制御用CPU371は、バックアップRAM領域のデータチェック(この例ではパリティチェック)を行う(ステップS705)。不測の電源断が生じた後に復旧した場合には、バックアップRAM領域のデータは保存されていたはずであるから、チェック結果は正常になる。チェック結果が正常でない場合には、内部状態を電源断時の状態に戻すことができないので、停電復旧時でない電源投入時に実行される初期化処理を実行する(ステップS706,S704)。

チェック結果が正常であれば、払出制御用CPU371は、内部状態を電源断時の状態に戻すための払出状態復旧処理を行う(ステップS707)。そして、バックアップRAM領域に保存されていたPC(プログラムカウンタ)の指すアドレスに復帰する(ステップS708)。

通常の初期化処理の実行(ステップS704)を終えると、払出制御用CPU371により実行されるメイン処理は、タイマ割込フラグの監視(ステップS709)の確認が行われるループ処理に移行する。

なお、この実施の形態では、ステップS702でクリアスイッチ921がオフである場合に、バックアップデータの有無が確認されていたが、逆に、バックアップデータの有無を確認した後、バックアップデータが存在する場合(さらに、バックアップ領域のチェックを行い、バックアップ領域のチェック結果が正常であったことが確認された場合であってもよい)にクリアスイッチ921の操作状態を確認するようにしてもよい。

また、この実施の形態では、ステップS703でバックアップデータの有無が確認された後、バックアップデータが存在する場合にステップS705でバックアップ領域のチェックが行われたが、逆に、バックアップ領域のチェック結果が正常であったことが確認された後、バックアップデータの有無の確認を行うようにしてもよい。また、バックアップデータの有無の確認、またはバックアップ領域のチェックの何れか一方の確認を行うことによって、停電復旧処理を実行するか否かを判定してもよい。

また、例えば停電復旧処理を実行するか否か判断する場合のパリティチェック(ステップS705)の際などに、すなわち、遊技状態を復旧するか否か判断する際に、保存されていたRAMデータにおける払出遊技球数データ等によって、遊技機が払出待機状態(払出途中でない状態)であることが確認されたら、払出状態復旧処理を行わずに初期化処理を実行するようにしてもよい。

通常の初期化処理では、図24に示すように、レジスタおよびRAMのクリア処理(ステップS901)が行われる(ステップS902)。そして、初期設定処理(ステップS701a)において割込禁止とされているので、初期化処理を終える前に割込が許可される(ステップS903)。

この実施の形態では、払出制御用CPU371の内部タイマ(CH3)が繰り返しタイマ割込を発生するように設定される。また、繰り返し周期は2msに設定される。そして、図25に示すように、タイマ割込が発生すると、払出制御用CPU371は、タイマ割込フラグをセットする(ステップS712)。なお、2msタイマ割込処理において、必要ならば、CH3のレジスタに対して初期値再設定が行われる。

払出制御用CPU371は、ステップS709において、タイマ割込フラグがセットされたことを検出すると、タイマ割込フラグをリセットするとともに(ステップS710)、払出制御処理を実行する(ステップS711)。以上の制御によって、この実施の形態では、払出制御処理は2ms毎に起動されることになる。なお、この実施の形態では、タイマ割込処理ではフラグセットのみがなされ、払出制御処理はメイン処理において実行されるが、タイマ割込処理で払出制御処理を実行してもよい。

払出制御用CPU371は、電源投入時に、クリア信号が入力されているか否かを確認するだけで、通常の初期化処理を行うか否か決定できる。すなわち、簡単な判断によって、未払出の遊技球について払出処理再開を行うことなく通常の運用を開始することができる。また、クリア信号が入力されていなければ、払出制御用CPU371は、バックアップRAMの保存データを確認することで、払出中の状態を復元するか否か決定できる。すなわち、簡単な判断によって、未払出の遊技球について払出処理再開を行うことができる。

また、本例では、払出制御用CPU371も、主基板31のCPU56と同様に、パリティチェックコードによって記憶内容保存の確実化を図っている。

以上のように、バックアップデータの有無により電源断時の払出状態に復旧するか否かの判断を行うようにしたことで、停電後の電源復旧時などにおいて電源投入された時に、バックアップデータ記憶領域の内容に応じて電源断時の状態に復旧させるか否かの判断を行うことができる。従って、バックアップデータにもとづく制御を実現することができるとともに、不必要な復旧処理の実行を防止することができる。

その際、クリアスイッチ921がオン状態であれば、遊技状態復旧処理(ステップS707)は実行されず、通常の初期化処理(ステップS704)が実行される。従って、遊技店員等は、電源スイッチ920の投入等にもとづく遊技機の電源投入時に、クリアスイッチ921を操作することによって、バックアップデータ記憶領域(変動データ記憶手段)に記憶されているバックアップデータにもとづく遊技状態復旧処理を実行するか否かを選択することができる。従って、電源断が発生しても遊技者に不利益がもたらされることを防止することができるとともに、遊技店での遊技機運用上の利便性を向上させることもできる遊技機が提供される。

なお、電源投入時に、変動データ記憶手段にバックアップデータが記憶されていない場合に実行される初期化処理と、変動データ記憶手段にバックアップデータが記憶されていてもクリアスイッチ921がオフ状態である場合に実行される初期化処理とは、プログラム上兼用されている(図22のステップS704参照)。従って、遊技店での運用上の利便性を向上させる制御を付加しても、プログラム容量はさほど増えない。

また、上述したように、バックアップデータの状態により電源断時の払出状態に復旧するか否かの判断を行うようにしたことで、停電後の電源復旧時などにおいて電源投入された時に、バックアップデータ記憶領域の内容の状態に応じて電源断時の状態に復旧させるか否かの判断を行うことができる。従って、遊技店員等がクリアスイッチ921を操作することによってバックアップデータにもとづく遊技状態復旧処理の実行を選択した場合に、正常なバックアップデータにもとづく制御を実現することができるとともに、異常が発生したバックアップデータにもとづく復旧処理の実行を防止することができる。

図26は、払出制御用CPU371が内蔵するRAMの使用例を示す説明図である。この例では、バックアップRAM領域に総合個数記憶(例えば2バイト)および貸し球個数記憶が形成されている。総合個数記憶は、主基板31の側から指示された払出個数の総数を記憶するものである。貸し球個数記憶は、未払出の球貸し個数を記憶するものである。

図27は、割込処理による払出制御コマンド受信処理を示すフローチャートである。主基板31からの払出制御用のINT信号は払出制御用CPU371のCLK/TRG2端子に入力されている。よって、主基板31からのINT信号がオン状態になると、払出制御用CPU371に割込がかかり、図27に示す払出制御コマンドの受信処理が開始される。この実施の形態では、受信した払出制御コマンドを格納するための12バイトの確定コマンドバッファ領域が設けられている。そして、受信した払出制御コマンドの格納位置を示すためにコマンド受信個数カウンタが用いられる。なお、払出制御コマンドは、2バイト構成であるから、実質的には6個の払出制御コマンドを確定コマンドバッファ領域に格納可能である。

払出制御コマンドの受信処理において、払出制御用CPU371は、まず、払出制御コマンドデータの入力に割り当てられている入力ポートからデータを読み込む(ステップS851)。そして、2バイト構成の払出制御コマンドのうちの1バイト目であるか否か確認する(ステップS852)。1バイト目であるか否かは、受信したコマンドの先頭ビットが「1」であるか否かで確認できる。先頭ビットが「1」であるのは、2バイト構成の払出制御コマンドのうちのMODEバイト(1バイト目)のはずである(図17参照)。先頭ビットが「1」であれば、有効な1バイト目を受信したとして、受信したコマンドを確定コマンドバッファ領域におけるコマンド受信個数カウンタが示す確定コマンドバッファに格納する(ステップS853)。

払出制御コマンドのうちの1バイト目でなければ、1バイト目を既に受信したか否か確認する(ステップS854)。既に受信したか否かは、受信バッファ(ステップS853における確定コマンドバッファ)に有効なデータが設定されているか否かで確認できる。

1バイト目を既に受信している場合には、受信した1バイトのうちの先頭ビットが「0」であるか否か確認する。そして、先頭ビットが「0」であれば、有効な2バイト目を受信したとして、受信したコマンドを、確定コマンドバッファ領域におけるコマンド受信個数カウンタ+1が示す確定コマンドバッファに格納する(ステップS855)。先頭ビットが「0」であるのは、2バイト構成の払出制御コマンドのうちのEXTバイト(2バイト目)のはずである(図17参照)。なお、ステップ845のYのあとの確認で、受信した1バイトのうちの先頭ビットが「0」でなければ、処理を終了する。

ステップS855において、2バイト目のコマンドデータを格納すると、コマンド受信個数カウンタに2を加算する(ステップS856)。そして、コマンド受信カウンタが12以上であるか否か確認し(ステップS857)、12以上であればコマンド受信個数カウンタをクリアする(ステップS858)。

図28は、ステップS710の払出制御処理を示すフローチャートである。払出制御処理において、払出制御用CPU371は、まず、中継基板72を介して入力ポート372bに入力される賞球カウントスイッチ301A、球貸しカウントスイッチ301Bがオンしたか否かを判定する(スイッチ処理:ステップS751)。

次に、払出制御用CPU371は、センサ(例えば、払出モータ289の回転数を検出するモータ位置センサ)からの信号入力状態を確認してセンサの状態判定などを行う(入力判定処理:ステップS752)。払出制御用CPU371は、さらに、受信した払出制御コマンドを解析し、解析結果に応じた処理を実行する(コマンド解析実行処理:ステップS753)。

次いで、払出制御用CPU371は、主基板31より受信した払出停止指示コマンドに応じて払出停止状態に設定し、あるいは受信した払出開始指示コマンドに応じて払出停止状態の解除を行う(ステップS754)。また、プリペイドカードユニット制御処理を行う(ステップS755)。

また、払出制御用CPU371は、球貸し要求に応じて貸し球を払い出す制御を行う(ステップS756)。さらに、払出制御用CPU371は、総合個数記憶に格納された個数の賞球を払い出す賞球制御処理を行う(ステップS757)。そして、払出制御用CPU371は、出力ポート372cおよび中継基板72を介して球払出装置97の払出機構部分における払出モータ289に向けて駆動信号を出力し、ステップS756の球貸し制御処理またはステップS757の賞球制御処理で設定された回転数分払出モータ289を回転させる払出モータ制御処理を行う(ステップS758)。

なお、この実施の形態では、払出モータ289としてステッピングモータが用いられ、払出モータ289を制御するために1−2相励磁方式が用いられる。従って、具体的には、払出モータ制御処理において、8種類の励磁パターンデータが繰り返し払出モータ289に出力される。また、この実施の形態では、各励磁パターンデータが4msずつ出力される。

次いで、エラー検出処理が行われ、その結果に応じてエラー表示LED374に所定の表示を行う(エラー処理:ステップS759)。検出されるエラーとして、例えば、次の8種類がある。

賞球経路エラー:賞球払出動作終了したとき、または払出モータ289が1回転したときに賞球カウントスイッチ301Aが1個も遊技球の通過を検出しなかったとき。エラー表示LED374に「0」が表示される。

球貸し経路エラー:球貸しの払出動作終了したとき、または払出モータ289が1回転したときに球貸しカウントスイッチ301Bが1個も遊技球の通過を検出しなかったとき。エラー表示LED374に「1」が表示される。

賞球カウントスイッチ球詰まりエラー:賞球カウントスイッチ301Aが0.5秒以上オンを検出したとき。エラー表示LED374に「2」が表示される。

球貸しカウントスイッチ球詰まりエラー:球貸しカウントスイッチ301Bが0.5秒以上オンを検出したとき。エラー表示LED374に「3」が表示される。

払出モータ球噛みエラー:払出モータ289が正常に回転しないとき。具体的には、払出モータ位置センサのオンが所定期間以上継続したり、オフが所定期間以上継続した場合。エラー表示LED374に「4」が表示される。なお、払出モータ球噛みエラーが生じた場合には、払出制御用CPU371は、50msの基準励磁相の出力を行った後、1−2相励磁の励磁パターンデータのうちの4種類の励磁パターンデータを8ms毎に出力することによる払出モータ289の逆回転と正回転を繰り返す。

プリペイドカードユニット未接続エラー:VL信号のオフが検出されたとき。エラー表示LED374に「5」が表示される。

プリペイドカードユニット通信エラー:規定のタイミング以外でプリペイドカードユニット50から信号出力されたことを検出したとき。エラー表示LED374に「6」が表示される。

払出停止状態:主基板31から払出停止を示す払出制御コマンドを受信したとき。エラー表示LED374に「7」が表示される。なお、主基板31から払出開始を示す払出制御コマンドを受信したときには、その時点から2002ms後に、払出停止状態から払出可能状態に復帰する。

さらに、外部接続端子(図示せず)から出力する情報信号を制御する処理を行う(出力処理:ステップS760)。なお、情報信号は、貸し球の払出一単位(例えば25個)ごとに所定時間オンとなり、続いて所定時間オフを出力する信号である。

図29は、電源基板910の電源監視回路からの電圧変化信号にもとづくNMIに応じて実行される停電発生NMI処理の一例を示すフローチャートである。なお、この実施の形態では、NMI割込番地は0066Hである。停電発生NMI処理において、払出制御用CPU371は、まず、割込禁止フラグの内容をパリティフラグに格納する(ステップS801)。次いで、割込禁止に設定する(ステップS802)。停電発生NMI処理では、本例では主基板31において実行された処理と同様に、RAM内容の保存を確実にするためのチェックサムの生成処理を行う。その処理中に他の割込処理が行われたのではチェックサムの生成処理が完了しないうちに払出制御用CPU371が動作し得ない電圧にまで低下してしまうことがことも考えられるので、まず、他の割込が生じないような設定がなされる。なお、停電発生NMI処理におけるステップS804〜S810は、電力供給停止時処理の一例である。

なお、割込処理中では他の割込がかからないような仕様のCPUを用いている場合には、ステップS802の処理は不要である。

次いで、払出制御用CPU371は、バックアップフラグが既にセットされているか否か確認する(ステップS803)。バックアップフラグが既にセットされていれば、以後の処理を行わない。バックアップフラグがセットされていなければ、以下の電力供給停止時処理を実行する。すなわち、ステップS804からステップS810の処理を実行する。

まず、各レジスタの内容をバックアップRAM領域に格納する(ステップS804)。その後、バックアップフラグをセットする(ステップS805)。そして、バックアップRAM領域のバックアップチェックデータ領域に適当な初期値を設定し(ステップS806)、初期値およびバックアップRAM領域のデータについて順次排他的論理和をとったあと反転し(ステップS807)、最終的な演算値をバックアップパリティデータ領域に設定する(ステップS808)。また、RAMアクセス禁止状態にする(ステップS809)。さらに、全ての出力ポートをオフ状態にする(ステップS810)。電源電圧が低下していくときには、各種信号線のレベルが不安定になってRAM内容が化ける可能性があるが、このようにRAMアクセス禁止状態にしておけば、バックアップRAM内のデータが化けることはない。

次いで、払出制御用CPU371は、ループ処理にはいる。すなわち、何らの処理もしない状態になる。従って、図21に示されたリセットIC976からのシステムリセット信号によって外部から動作禁止状態にされる前に、内部的に動作停止状態になる。よって、電源断時に確実に払出制御用CPU371は動作停止する。その結果、上述したRAMアクセス禁止の制御および動作停止制御によって、電源電圧が低下していくことに伴って生ずる可能性がある異常動作に起因するRAMの内容破壊等を確実に防止することができる。

なお、この実施の形態では、停電発生NMI処理では最終部でプログラムをループ状態にしたが、ホールト(HALT)命令を発行するように構成してもよい。

また、レジスタの内容をRAM領域に格納した後にセットされるバックアップフラグは、上述したように、電源投入時において復旧すべきバックアップデータがあるか否か(停電からの復旧か否か)を判断する際に使用される。また、ステップS801からS810の処理は、払出制御用CPU371がシステムリセット回路975からのシステムリセット信号を受ける前に完了する。換言すれば、システムリセット回路975からのシステムリセット信号を受ける前に完了するように、電圧監視回路の検出電圧の設定が行われている。

この実施の形態では、電力供給停止時処理開始時に、バックアップフラグの確認が行われる。そして、バックアップフラグが既にセットされている場合には電力供給停止時処理を実行しない。上述したように、バックアップフラグは、必要なデータのバックアップが完了し、その後電力供給停止時処理が完了したことを示すフラグである。従って、例えば、リセット待ちのループ状態で何らかの原因で再度NMIが発生したとしても、電力供給停止時処理が重複して実行されてしまうようなことはない。

ただし、割込処理中では他の割込がかからないような仕様のCPUを用いている場合には、ステップS803の判断は不要である。

また、この実施の形態では、払出制御用CPU371は、マスク不能外部割込端子(NMI端子)を介して電源基板からのNMI割込信号(電源監視手段からのNMI割込信号)を検知したが、NMI割込信号をマスク可能割込割込端子(IRQ端子)に導入してもよい。その場合には、IRQ処理によって図29に示された停電発生NMI処理が実行される。また、入力ポートを介してNMI割込信号を検知してもよい。その場合には、払出制御用CPU371が実行するメイン処理において、入力ポートの監視が行われる。

図30は、バックアップパリティデータ作成方法の一例を説明するための説明図である。ただし、図30に示す例では、簡単のために、バックアップデータRAM領域のデータのサイズを3バイトとする。電源電圧低下にもとづく停電発生処理において、図30に示すように、バックアップチェックデータ領域に、初期データ(この例では00H)が設定される。次に、「00H」と「F0H」の排他的論理和がとられ、その結果と「16H」の排他的論理和がとられる。さらに、その結果と「DFH」の排他的論理和がとられる。そして、その結果(この例では「39H」)を反転して得られた値(この例では「C6H」)がバックアップパリティデータ領域に設定される。

電源が再投入されたときには、停電復旧処理においてパリティ診断が行われる。バックアップ領域の全データがそのまま保存されていれば、電源再投入時に、図30に示すようなデータがバックアップ領域に設定されている。

ステップS705の処理において、払出制御用CPU371は、図29のステップS806およびステップS807にて実行された処理と同様の処理を行う。すなわち、バックアップチェックデータ領域に、初期データ(この例では00H)が設定され、「00H」と「F0H」の排他的論理和がとられ、その結果と「16H」の排他的論理和がとられる。さらに、その結果と「DFH」の排他的論理和がとられる。そして、その結果(この例では「39H」)を反転した最終演算結果を得る。バックアップ領域の全データがそのまま保存されていれば、最終的な演算結果は、「C6H」、すなわちバックアップチェックデータ領域に設定されているデータと一致する。バックアップRAM領域内のデータにビット誤りが生じていた場合には、最終的な演算結果は「C6H」にならない。

よって、払出制御用CPU371は、最終的な演算結果とバックアップチェックデータ領域に設定されているデータとを比較して、一致すればパリティ診断正常とする。一致しなければ、パリティ診断異常とする。

以上のように、この実施の形態では、払出制御手段には、遊技機の電源が断しても、所定期間電源バックアップされる記憶手段(この例ではバックアップRAM)が設けられ、電源投入時に、払出制御用CPU371(具体的には払出制御用CPU371が実行するプログラム)は、記憶手段がバックアップ状態にあればバックアップデータにもとづいて払出状態を回復させる払出状態復旧処理(ステップS707)を行うように構成される。

以下、払出状態復旧処理について説明する。

図31は、図22のステップS707に示された払出状態復旧処理の一例を示すフローチャートである。この例では、払出制御用CPU371は、バックアップRAMに保存されていた値をレジスタに復元する(ステップS861)。そして、バックアップRAMに保存されていたデータにもとづいて停電時の払出状態を復旧するための処理を行う。例えば、賞球中処理中フラグのセット等を行う。

払出状態を復帰させると、この実施の形態では、払出制御用CPU371は、前回の電源断時の割込許可/禁止状態を復帰させるため、バックアップRAMに保存されていたパリティフラグの値を確認する(ステップS862)。パリティフラグがクリアであれば、割込許可設定を行う(ステップS863)。一方、パリティフラグがオンであれば、そのまま(ステップS701aで設定された割込禁止状態のまま)払出状態復旧処理を終える。

なお、ここでは、払出状態復旧処理が終了すると払出制御メイン処理にリターンするように払出状態復旧処理プログラムが構成されているが、電力供給停止時処理において保存されているスタックポインタが指すスタックエリア(バックアップRAM領域にある)に記憶されているアドレス(電源断時のNMI割込発生時に実行されていたアドレス)に戻るようにしてもよい。

上述したように、初期設定処理を開始したあと、払出状態復旧処理を終える前まで、または初期化処理を終える前までは、割込禁止状態とする構成としたことで、割込みにより処理が中断されることを防止することができるため、初期設定、バックアップデータ記憶領域の内容に応じて行われる電源断時の払出状態に復旧させるか否かの判断、および復旧処理(または初期化処理)を確実に完了させることができる。なお、上記のように復旧処理を終える前まで割込禁止状態とする構成とした場合であっても、電源断時の割込禁止/許可状態をパリティフラグによりバックアップしているため、復旧処理において電源断時の割込禁止/許可状態を確実に復旧させることができる。

図32は、遊技機の電源断時の電源低下やNMI割込信号(ここでは、電源断信号)の様子を示すタイミング図である。遊技機に対する電力供給が断たれると、最も高い直流電源電圧であるVSLの電圧値は徐々に低下する。そして、この例では、+22Vにまで低下すると、電源基板910に搭載されている電源監視用IC902から電源断信号(電圧低下信号)が出力される(ローレベルになる)。

電源断信号は、電気部品制御基板(図32に示す例では主基板31および払出制御基板37)に導入され、CPU56および払出制御用CPU371のNMI端子に入力される。CPU56および払出制御用CPU371は、上述したNMI処理によって、所定の電力供給停止時処理を実行する。

VSLの電圧値がさらに低下して所定値(この例では+9V)にまで低下すると、主基板31や払出制御基板37に搭載されているリセットIC651の出力がローレベルになり、CPU56および払出制御用CPU371がシステムリセット状態になる。なお、CPU56および払出制御用CPU371は、システムリセット状態とされる前に、電力供給停止時処理を完了している。

VSLの電圧値がさらに低下してVcc(各種回路を駆動するための+5V)を生成することが可能な電圧を下回ると、各基板において各回路が動作できない状態となる。しかし、少なくとも主基板31や払出制御基板37では、電力供給停止時処理が実行され、CPU56および払出制御用CPU371がシステムリセット状態とされている。

リセットIC976が電源断を検知するための所定値は、通常時の電圧より低いが、払出制御用CPU371が暫くの間動作し得る程度の電圧である。また、リセットIC976が、払出制御用CPU371が必要とする電圧(この例では+5V)よりも高い電圧を監視するように構成されているので、払出制御用CPU371が必要とする電圧に対して監視範囲を広げることができる。従って、より精密な監視を行うことができる。

また、この実施の形態では、電源基板910に搭載されている電源監視回路が、遊技機で使用される直流電圧のうちで最も高い電源VSLの電圧を監視して、その電源の電圧が所定値を下回ったら電圧低下信号(電源断検出信号)を発生する。図32に示すように、電源断検出信号が出力されるタイミングでは、IC駆動電圧は、まだ各種回路素子を十分駆動できる電圧値になっている。従って、IC駆動電圧で動作する払出制御基板37の払出制御用CPU371が所定の電力供給停止時処理を行うための動作時間が確保されている。

なお、ここでも、電源監視回路は、遊技機で使用される直流電圧のうちで最も高い電源VSLの電圧を監視することになるが、電源断検出信号を発生するタイミングが、IC駆動電圧で動作する電気部品制御手段が所定の電力供給停止時処理を行うための動作時間が確保されるようなタイミングであれば、監視対象電圧は、最も高い電源VSLの電圧でなくてもよい。すなわち、少なくともIC駆動電圧よりも高い電圧を監視すれば、電気部品制御手段が所定の電力供給停止時処理を行うための動作時間が確保されるようなタイミングで電源断検出信号を発生することができる。

この場合、上述したように、監視対象電圧は、賞球カウントスイッチ301A等の遊技機の各種スイッチに供給される電圧が+12Vであることから、電源断時のスイッチオン誤検出の防止も期待できる電圧であることが好ましい。すなわち、スイッチに供給される電圧(スイッチ電圧)である+12V電源電圧が落ち始める以前の段階で、電圧低下を検出できることが好ましい。よって、少なくともスイッチ電圧よりも高い電圧を監視することが好ましい。

ただし、監視範囲が狭まるが、電圧監視回路および他の電圧監視回路の監視電圧として+5V電源電圧を用いることも可能である。その場合にも、電圧監視回路の検出電位は、他の電圧監視回路の検出電位よりも高く設定される。

以上説明したようにクリアスイッチ921の操作状態にもとづいて電源断時の状態に復旧するか否かの判断を行うようにしたことで、停電後の電源復旧時などの電源投入時に、バックアップデータ記憶領域の内容に応じて電源断時の状態に復旧させるか否かの判断を行うことができる。従って、バックアップデータにもとづく制御を実現することができるとともに、不必要な復旧処理の実行を防止することができる。

また、上述したようにクリアスイッチ921の操作状態にもとづいて電源断時の状態に復旧するか否かの判断を行うようにしたことで、主基板31に含まれる変動データ記憶手段(例えば、バックアップRAM)に賞球の払出数が記憶されているときに点灯する賞球未払出ランプを設けた構成としても、クリアスイッチ921の操作によって賞球の払出数をクリアすることができるため、主基板31の変動データ記憶手段に記憶されている賞球の払出数と払出制御基板37の総合個数記憶(図28参照)に記憶されている賞球の払出数との間の食い違いによって賞球未払出ランプが誤って点灯し続けてしまうことを回避することができる。

また、上述したようにバックアップデータの状態により電源断時の状態に復旧するか否かの判断を行うようにしたことで、停電後の電源復旧時などにおいて電源投入された時に、バックアップデータ記憶領域の内容の状態に応じて電源断時の状態に復旧させるか否かの判断を行うことができる。従って、正常なバックアップデータにもとづく制御を実現することができるとともに、異常が発生したバックアップデータにもとづく復旧処理の実行を防止することができる。

また、上述したように遊技機に対して交換可能に設けられている遊技盤側にスイッチ基板190を設け、このスイッチ基板190にクリアスイッチ921を搭載する構成としたことで、通常は機種変更に伴って交換される遊技盤にクリアスイッチを設ける構成とすることができ、複数機種で共用可能な本体側に搭載するのと比較して容易に開発することができる。

また、上述したように、初期設定処理を開始したあと、復旧処理を終える前まで、または初期化処理を終える前までの間(初期準備処理の間)は、割込禁止状態とする構成としたことで、割込みにより処理が中断されることを防止することができるため、初期設定、バックアップデータ記憶領域の内容に応じて行われる電源断時の状態に復旧させるか否かの判断、および復旧処理(または初期化処理)を確実に完了させることができる。なお、上記のように復旧処理を終える前まで割込禁止状態とする構成とした場合であっても、電源断時の割込禁止/許可状態をパリティフラグによりバックアップしているため、復旧処理において電源断時の割込禁止/許可状態を確実に復旧させることができる。この場合、上記初期準備処理に含まれる処理は一例であり、初期準備処理は、例えば初期設定処理を開始したあとバックアップデータにもとづく復旧を行うか否かを決定するまでの間の処理など、上述した処理の一部であってもよい。

なお、上述した各実施の形態では、電源投入後に変動データをクリアする構成としていたが、電源断中にバックアップRAMに記憶されている変動データをクリアする構成としてもよい。この場合、例えば図33に示すように、バックアップ電源を絶つためのクリアスイッチ921Aを設けるようにすればよい。

図33は、各電気部品制御基板へのバックアップ電源の供給に関する部分の構成例を示す回路図である。図33に示すように、主基板31や払出制御基板37などの電気部品制御基板は、CPU56や払出制御用CPU371などの駆動電源である+5V電源から電力が供給されていない間、電源基板910から本例では各コネクタ910,951,952を介してバックアップ電源が供給されるため、RAMの少なくとも一部がバックアップされている。この例では、図33に示すように、スイッチ基板190に搭載されたクリアスイッチ921Aが、電源基板910とコネクタ953を介して接続され、バックアップ電源が供給されている各電気部品制御基板と並列に接続されている。従って、バックアップ電源が供給されているときに、クリアスイッチ921Aがオンとされてスイッチ間が導通状態とされると、バックアップ電源であるコンデンサ916の電荷がクリアスイッチ921Aなどを介して放電され、バックアップ電源の供給が断たれる。この際、クリアスイッチ921Aと接地電位との間に介在する抵抗素子950により、瞬時の放電により蓄電用コンデンサ916が破壊されてしまうことが防止される。

このようにクリアスイッチ921Aを構成することで、駆動電源である+5V電源から電力が供給されていない間であっても、保存されている変動データをクリアすることができるため、電源が投入された場合に停電発生時の遊技状態に復帰されてしまうことを防止することができる。また、クリアスイッチ921Aを並列接続しただけの簡単な構成でバックアップデータをクリアすることができる。

なお、クリアスイッチ921Aは、上述したクリアスイッチ921により「クリア」が選択されるときに、クリアスイッチ921に連動してオンする構成としてもよい。この場合、例えば、クリアスイッチ921がオンに切り換えられると同時に、クリアスイッチ921Aがオンするような機構を設けるようにすればよい。このように構成すれば、一つのクリアスイッチにより、電源投入時であっても、待機中であっても、保存されている変動データをクリアすることができる。

また、上述した各実施の形態では、電源投入後の所定期間内にクリアスイッチ921の所定の操作状態が確認されたときにバックアップRAMをクリアする構成としていたが、遊技機1の稼働中にRAMをクリアする構成としてもよい。

この場合、例えばタイマ/カウンタ割込としてCH1(2msタイマ割込の設定がされるチャネル(例えば、CH0)とは別のチャネル)のカウントアップにもとづく割込を使用する。CH1のカウントアップにもとづく割込は、タイマカウンタレジスタCLK/TRG1の値が「0」になったときに発生する割込である。例えば図34に示すように、クリアスイッチ921の出力信号が、CPU56に内蔵されたCTCのCH1に対応した入力端子に入力されるように構成する。また、例えば初期設定処理(図10)のCTCの設定(ステップS1e)において、クリア信号の入力にもとづく割込がかかるように、CPU56に設けられているCTCのCH1に対応するレジスタCLK/TRG1の設定をしておく。すなわち、レジスタCLK/TRG1に、初期値(初期データ)として例えば「1」が設定される。そして、クリア信号の入力にもとづく割込処理(以下、CTC1割込処理という)により初期化処理が実行されるように設定しておく。

なお、この例では、図34に示すように、OR回路949の出力が、AND回路(論理積回路)955に入力されている。また、クリアスイッチ921の出力信号がタイマ956に入力されている。AND回路955の他方の入力端子には、タイマ956の出力信号が入力される。そして、AND回路955の出力が、CPU56のリセット端子に接続されている。

図35は、この例における払出制御用CPU371周りの構成の一例を示す図である。この例では、タイマ/カウンタ割込としてCH1のカウントアップにもとづく割込を使用する。CH1のカウントアップにもとづく割込は、タイマカウンタレジスタCLK/TRG1の値が「0」になったときに発生する割込である。図35に示すように、クリアスイッチ921の出力信号が、払出制御用CPU371に内蔵されたCTCのCH1に対応した入力端子に入力されるように構成する。また、例えば初期設定処理(図23)のCTCの設定(ステップS701e)において、クリア信号の入力にもとづく割込がかかるように、払出制御用CPU371に設けられているCTCのCH1に対応するレジスタCLK/TRG1の設定をしておく。すなわち、レジスタCLK/TRG1に、初期値(初期データ)として例えば「1」が設定される。そして、クリア信号の入力にもとづく割込処理により、主基板31における処理と同様に、初期化処理が実行されるように設定しておく。

なお、この例では、図35に示すように、システムリセット回路975の出力が、AND回路955aに入力されている。また、クリアスイッチ921の出力信号がタイマ956aに入力されている。AND回路955aの他方の入力端子には、タイマ956aの出力信号が入力される。そして、AND回路955aの出力が、払出制御用CPU371のリセット端子に接続されている。

このような構成において、クリアスイッチ921がオンされると、クリア信号がCPU56および払出制御用CPU371の入力端子に入力される。クリア信号が入力され、CTCのダウンカウント処理によりレジスタCLK/TRG1の設定値が0になると、CPU56は、CTC1割込処理を開始し、例えば図37に示すように本例ではステップS4と同様の初期化処理を実行して(ステップS14)、RAMに記憶されている変動データのクリアなどの処理を実行する。なお、払出制御用CPU371についても、上述したCPU56と同様に、CTC1割込処理において例えば図38に示すようにステップS704と同様の初期化処理を実行して(ステップS713)、RAMに記憶されている変動データのクリアなどの処理を実行する。

図36は、クリアスイッチ921、タイマ956,956aなどの出力信号と、遊技機における動作状態の一例を示すタイミング図である。なお、図36では、払出制御基板37における動作状態の様子も示されている。また、クリアスイッチ921がオンすると、本例ではクリア信号がタイマ956,956aにも入力される。クリア信号が入力すると、タイマ956,956aは、所定時間(例えば、RAMのクリア処理を終えるまでの時間)を計時して、その時間の経過後にローレベルのシステムリセット信号を出力する。すると、CPU56および払出制御用CPU371は、リセット状態(動作不能状態)となる。そして、クリアスイッチ921が「ON」に切り替えられると、クリアスイッチ921は、ハイレベルの信号を出力する。このハイレベル信号が入力すると、タイマ956,956aは、出力信号をハイレベルに立ち上げてCPU56および払出制御用CPU371の動作を開始させる。このように、本例では、遊技機の稼動中にRAMがクリアされると、システムリセットがかけられるように構成されている。

このように構成することで、遊技機の稼働中であっても、クリアスイッチをオンするだけでRAMに記憶されている変動データを初期データとすることができる。従って、電源投入後の所定期間を経過したあとであっても、RAMの内容を即時にクリアすることができ、RAMクリアの選択の自由度を向上させることができる。

なお、図34〜図38を参照して説明した他の例では、CTC1割込処理により初期化処理(ステップS14、ステップS713)を実行する構成としていたが、例えばCTC1割込処理においてステップS4またはステップS704にジャンプするように設定しておくようにしてもよい。

この場合、上述したようにクリアスイッチ921がオンされて、レジスタCLK/TRG1の設定値が0になると、例えば図39に示すように、CPU56は、CTC1割込処理を実行する。CTC1割込処理において、CPU56は、CTC1割込フラグ(本例では、クリアスイッチ921が操作され、RAMのクリア要求がされたことを示すフラグ)をセットする(ステップS15)。また、同様に、払出制御用CPU371は、例えば図40に示すように、CTC1割込処理において、払出制御用CPU371は、CTC1割込フラグをセットする(ステップS714)。

図41は、この例においてCPU56が実行するメイン処理の例を示すフローチャートである。図41に示すように、この例ではループ処理の中にCTC1割込フラグを確認する処理(ステップS16)が含まれている。すなわち、CPU56は、ステップS16において、CTC1割込フラグがセットされたことを検出すると、初期化処理を実行する(ステップS4)。なお、CTC1割込フラグのリセットは、例えばステップS4の初期化処理において行われる。また、この例において、ステップS2の判断を行わない構成としてもよい。

図42は、この例において払出制御用CPU371が実行するメイン処理の例を示すフローチャートである。図42に示すように、この例ではループ処理の中にCTC1割込フラグを確認する処理(ステップS715)が含まれている。すなわち、払出制御用CPU371は、ステップS715において、CTC1割込フラグがセットされたことを検出すると、初期化処理を実行する(ステップS704)。なお、CTC1割込フラグのリセットは、例えばステップS704の初期化処理において行われる。また、この例において、ステップS702の判断を行わない構成としてもよい。

このようにCTC1割込処理において初期化処理(ステップS4またはステップS704)にジャンプするように設定しておく構成とした場合であっても、遊技機の稼働中に、クリアスイッチをオンするだけでRAMに記憶されている変動データを初期データとすることができる。従って、電源投入後の所定期間を経過したあとであっても、RAMの内容を即時にクリアすることができ、RAMクリアの選択の自由度を向上させることができる。

また、上述した各実施の形態では、初期化処理においてRAMに記憶されている変動データを全てクリアする構成(ステップS4a参照)としていたが、RAMに記憶されている変動データのうちの一部をクリアするようにしてもよい。この場合、例えば価値付与の数量にかかわる変動データ(例えば、入賞にもとづき払い出される遊技球の数量などを示すデータ)をRAMに記憶されている変動データの一部としてクリアしたり、遊技状態にかかわる変動データ(例えば、大当りか否か、確変か否か、時短中か否かなどを示すデータ)をRAMに記憶されている変動データの一部としてクリアするようにすればよい。すなわち、クリアスイッチ921の操作にもとづくRAMのクリアにおいて、変動データのうちの一部のデータとして、例えば確変フラグや時短フラグのみがクリアされるようにしてもよい。なお、RAMの一部が初期化されたあとは、クリアされなかった変動データにもとづく遊技状態復旧処理(図16参照)が実行されるように構成される。

このように、変動データの一部をクリアすることができる構成としたことで、復旧させる必要のないデータを除く変動データにもとづいて遊技状態を復旧させることができる。なお、変動データの一部として価値付与の数量にかかわる変動データをクリアする構成とすれば、電源断前に得られていた遊技球を、電源投入後に不当に得ることを防止することができる。また、変動データの一部として遊技状態にかかわる変動データをクリアする構成とすれば、電源断前に得られていた例えば確変などの有利な遊技状態を、電源投入後に不当に得ることを防止することができ、あるいは不利な遊技状態を不当に与えてしまうことを防止することができる。

また、上述した各実施の形態においては、パチンコ遊技機1の裏面にスイッチ基板190が搭載された状態の例として、図2を参照して枠体2Aを含む裏面の状態について説明したが、さらに詳細には、上述した各実施の形態におけるスイッチ基板190は、例えば図43に示すように、遊技機1の裏面側の遊技盤6に設置されている。なお、図43には、例えば主基板などの他の基板と接続されるためのコネクタ922が開示されている。

また、上述した各実施の形態では、3点に切替可能なクリアスイッチの例について説明したが、クリアスイッチが押しボタン構造とされていてもよい。図44は、クリアスイッチを押しボタン構造とした場合の回路構成の例を示す回路図である。この場合、遊技機の電源がオンされている状態において、クリアスイッチ921が押下されていれば、クリア信号がコネクタ922を介して例えば主基板31などの各基板に対して送信される。また、クリアスイッチ921が押下されていなければ、ハイレベルの出力信号が送信される。

また、電源断中にバックアップRAMに記憶されている変動データをクリアする場合の例として、図33を参照して、バックアップ電源であるコンデンサ916の電荷を放電する構成を説明したが、バックアップ電源の供給線路を切断することによりバックアップ電源の供給を絶つようにしてもよい。図45は、各電気部品制御基板へのバックアップ電源の供給に関する部分の他の構成例を示す回路図である。通常の状態では、クリアスイッチ921Aを閉じて通電状態にしておく。従って、バックアップ電源が主基板31などに供給される。そして、クリアスイッチ921Aが操作されて線路が断たれると、主基板31などに対するバックアップ電源の供給が絶たれる。このように構成した場合であっても、同様に、電源断中にバックアップRAMに記憶されている変動データをクリアすることができる。

また、上述した各実施の形態では、電源監視手段は、電源基板および電気部品制御基板のいずれかに設置されたが、どこに設置されていてもよく、遊技機の構造上の都合等に応じて任意の位置に設置することができる。

そして、上記の各実施の形態では、記憶手段としてRAMを用いた場合を示したが、記憶手段として、電気的に書き換えが可能な記憶手段であればRAM以外のものを用いてもよい。

また、上述した各実施の形態では、遊技制御手段以外の他の電気部品制御手段として払出制御手段を例示したが、表示制御手段、音制御手段およびランプ制御手段についても、上述した制御を行うように構成してもよい。

また、上記の実施の形態では、電源監視回路は電源基板910に設けられたが、電源監視回路は主基板31や払出制御基板37などの電気部品制御基板に設けられていてもよい。なお、電源回路が搭載された電気部品制御基板が構成される場合には、電源基板には、電源監視回路は搭載されない。

また、上記の実施の形態では、クリアスイッチ921はスイッチ基板190に搭載されていたが、クリアスイッチ921は主基板31、払出制御基板37、あるいは電源基板910などの電気部品制御基板に設けられていてもよい。

また、上記の実施の形態では、スイッチ基板190は、クリアスイッチ921を搭載するための専用基板としていたが、例えば賞球カウントスイッチ301Aなどの出力信号を中継する中継基板としての役割をあわせ持つ構成としてもよい。

また、上記の実施の形態では、電源投入後の所定期間内にクリアスイッチ921の操作状態が所定の状態とされているか否かを確認することにより、変動データを初期データとするか否かの判断をしていたが、例えば電源投入後の所定期間内(例えば10秒以内)に始動口スイッチ17などの入賞検出スイッチがオンしたか否かを確認するようにしてもよい。この場合、クリアスイッチ921の操作状態の確認と同様の構成により、電源投入後の所定期間内に例えば遊技店の店員により入賞検出スイッチがオンされると、CPU56および払出制御用CPU371により入賞検出スイッチのオンが確認されるようにする。そして、入賞検出スイッチのオンが確認されると、CPU56および払出制御用CPU371が、例えばステップS4に示した通常の初期化処理を実行し、バックアップRAMに保持されている変動データを初期データとし、初期データにもとづいて遊技を開始させるように構成すればよい。

上記の各実施の形態のパチンコ遊技機1は、始動入賞にもとづいて可変表示部9に可変表示される特別図柄の停止図柄が所定の図柄の組み合わせになると所定の遊技価値が遊技者に付与可能になる第1種パチンコ遊技機であったが、始動入賞にもとづいて開放する電動役物の所定領域への入賞があると所定の遊技価値が遊技者に付与可能になる第2種パチンコ遊技機や、始動入賞にもとづいて可変表示される図柄の停止図柄が所定の図柄の組み合わせになると開放する所定の電動役物への入賞があると所定の権利が発生または継続する第3種パチンコ遊技機であっても、本発明を適用できる。

さらに、パチンコ遊技機に限られず、スロット機等においても、停電等による電源断時に、電源断直前のデータをバックアップRAM等に保存し、電源復旧時に保存データにもとづく制御再開処理を行うように構成されている場合などには本発明を適用することができる。例えば、スロット機に適用した場合には、内部フラグ(ビック、レギュラー、小役などのフラグ)やビック中などの状態の復旧の有無を選択することができる。

上記の実施の形態には、以下のような遊技機も開示されている。

所定の遊技を行うことが可能な遊技機であって、遊技機に設けられた電気部品を制御するための電気部品制御マイクロコンピュータを含む電気部品制御手段と、電気部品制御マイクロコンピュータが制御を行う際に発生する変動データを記憶する変動データ記憶手段(例えば、RAM)と、電源断時から少なくとも所定期間は電源断直前の変動データ記憶手段の記憶内容の保持が可能な記憶内容保持手段とを備え、電気部品制御マイクロコンピュータは、記憶内容保持手段により保持された変動データにもとづく電気部品の制御が可能であり、電気部品制御マイクロコンピュータによる電気部品の制御が可能な状態において、所定の操作状態とされたことに応じて変動データを消去することが可能なクリア手段(例えば、クリアスイッチ921)を設けたことを特徴とする遊技機。

そのような構成によれば、変動データを即時にクリアすることができるという効果がある。従って、必要に応じて遊技状態を初期状態とすることができる。また、遊技状態を継続させるか、あるいは初期状態とするかについて選択することができるため、例え電源断が発生しても遊技者に不利益がもたらされることを防止することができるとともに、遊技店での遊技機運用上の利便性を向上させることもできるという効果がある。

クリア手段は、所定の操作状態とされた場合に、電気部品制御マイクロコンピュータに対してクリア信号を出力し、電気部品制御マイクロコンピュータは、クリア信号に応じて変動データを初期化する変動データ初期化処理(例えば、初期化処理などの、RAMの記憶内容をクリアする処理を含む処理)を実行する遊技機。

そのような構成によれば、クリア手段を所定の操作状態とするたけの簡単な操作により、変動データを初期化することができ、初期データにもとづく遊技を実行させることができる。

電気部品制御マイクロコンピュータは、クリア信号に応じて割込処理を発生させ、変動データ初期化処理を実行する遊技機。

そのような構成によれば、割込処理により、簡易な構成で変動データ初期化処理を実行させることができる。

クリア手段は、例えば遊技盤に搭載されているスイッチ基板などの、遊技機の裏面側に設けられる遊技機。

そのような構成によれば、遊技者に操作されることを防止することができるため、遊技者により誤操作されることを防止することができる。

電気部品制御マイクロコンピュータは、価値付与を行うための価値付与手段を制御するものであり、クリア信号に応じて初期化される変動データには、少なくとも価値付与の数量(例えば、遊技球の払い出し数量や、画像式遊技機の場合の得点が意味する数量を示す概念である)を特定可能なデータが含まれる遊技機。

そのような構成によれば、電源断前に得られていた遊技媒体を、電源投入後に不当に得ることを回避することができる。

電気部品制御マイクロコンピュータは、遊技状態を制御するものであり、クリア信号に応じて初期化される変動データには、少なくとも遊技状態にかかわるデータ(例えば、確変か否か、特別図柄や普通図柄の変動時間の短縮、可変入賞球装置15の開放時間の延長や開放時間の増加等、通常の遊技状態よりも次回の大当りを発生させるまでの遊技媒体の使用量を抑制可能な状態、大当り状態か否かなどを示す例えばフラグなどのデータ)を含む遊技機。

そのような構成によれば、電源断前に得られていた例えば確変などの有利な遊技状態を、電源投入後に不当に得ることを回避することができ、あるいは不利な遊技状態を不当に与えてしまうことを回避することができる。

記憶内容保持手段は、バックアップ電源の供給により遊技機への電源供給が停止状態とされていても、変動データ記憶手段に記憶されている変動データを保持させる遊技機。

そのような構成によれば、簡単な構成で変動データを保持することができる。

クリア手段が所定の操作状態とされると、バックアップ電源の供給が停止される遊技機。

そのような構成によれば、電源供給の停止状態に、簡易な構成で変動データをクリアすることができる。

電気部品制御マイクロコンピュータに電源を供給する電源供給手段を備え、バックアップ電源を供給する記憶内容保持手段は、電源供給手段に設けられる遊技機。

そのような構成によれば、電源およびバックアップ電源を供給する電源供給手段を複数の機種で共用することができ、遊技機の開発効率の向上を図ることができる。