JP4635759B2 - 記憶素子及び記憶装置 - Google Patents

記憶素子及び記憶装置 Download PDFInfo

- Publication number

- JP4635759B2 JP4635759B2 JP2005208912A JP2005208912A JP4635759B2 JP 4635759 B2 JP4635759 B2 JP 4635759B2 JP 2005208912 A JP2005208912 A JP 2005208912A JP 2005208912 A JP2005208912 A JP 2005208912A JP 4635759 B2 JP4635759 B2 JP 4635759B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- electrode

- thin film

- memory element

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Semiconductor Memories (AREA)

Description

また、DRAMは、電源を切ると情報が消えてしまう揮発性メモリであり、頻繁にリフレッシュ動作、即ち書き込んだ情報(データ)を読み出し、増幅し直して、再度書き込み直す動作を行う必要がある。

これらのメモリの場合、電源を供給しなくても書き込んだ情報を長時間保持し続けることが可能になる。

また、これらのメモリの場合、不揮発性とすることにより、リフレッシュ動作を不要にして、その分消費電力を低減することができると考えられる。

このため、デザインルールの限界や製造プロセス上の限界まで素子を縮小化することは難しい。

この構成では、2つの電極のいずれか一方にイオン導電体中に含まれる金属を含ませることにより、2つの電極間に電圧を印加した場合に、電極中に含まれる金属がイオン導電体中にイオンとして拡散するため、これによりイオン導電体の抵抗値或いはキャパシタンス等の電気特性が変化する。

この特性を利用して、メモリデバイスを構成することが可能である(例えば特許文献1、非特許文献1参照)。

また、良質な結晶性を得るために、例えば700℃といった高温処理を行う必要があり、予め形成されているMOSトランジスタの特性を、熱により劣化させてしまう問題が生じる。

また、結晶成長を行うために、下地材料が限定され、例えば、単結晶材料を用いる必要が生じる。

また、本発明の記憶装置は、上記本発明の記憶素子と、第1の電極側に接続された配線と、第2の電極側に接続された配線とを有し、記憶素子が多数配置されて成るものである。

また、この状態から、一方の電極側に負電位を印加して記憶素子に負電圧をかけると、他方の電極側に析出していたCu,Ag,Znが再びイオン化して、元の状態に戻ることによって記憶用薄膜の抵抗値が元の高い状態に戻り、記憶素子の抵抗値も高くなるので、これにより記録した情報の消去を行うことが可能になる。

即ち、記憶素子に電圧を印加することにより、記憶素子の抵抗が変化して情報の記録が行われる。

また、短い電圧パルスによって安定して記録を行うことができるため、記録に要する時間を短縮して、記録動作の高速化を図ることができる。

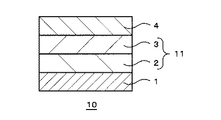

この記憶素子10は、下部電極1上にCu,Ag,Znのうちのいずれかの元素が含有された、イオン源層2が形成され、その上に記憶用薄膜3が形成され、この記憶用薄膜3上に上部電極4が形成されて構成されている。

上部電極4には、下部電極1と同様、通常の半導体配線材料が用いられる。

なお、このイオン源層2に、必要に応じて、Geや希土類元素等を添加することにより、耐熱性を向上することができる。

この記憶用薄膜3は、0.5nm〜10nm程度の膜厚で形成する。

このように、記憶用薄膜3の膜厚を薄くすることにより、通常絶縁材料である希土類酸化物等から成る記憶用薄膜3に電流を流すことが可能になる。

そして、この記憶用薄膜3は、他の層よりも抵抗値の変化が充分大きい。そのため、記憶素子10全体の抵抗値の変化は、主として記憶用薄膜3により影響される。

従って、記憶用薄膜3の抵抗値の変化を利用して、記憶素子10に情報の記録を行うことができる。

ここで、このとき、記憶素子10に印加する電圧を、正電圧(+)と定義して、以下同様に定義して説明する。

記憶素子10への正電圧の印加により、イオン源層2からCu,Ag,Znがイオン化して、記憶用薄膜3内を拡散していき、上部電極4側で電子と結合して析出する、或いは、記憶用薄膜3内部に拡散した状態で留まる。

すると、記憶用薄膜3内部にCu,Ag,Znを多量に含む電流パスが形成される、もしくは、記憶用薄膜3内部にCu,Ag,Znによる欠陥が多数形成されることによって、記憶用薄膜3の抵抗値が低くなる。記憶用薄膜3以外の各層は、記憶用薄膜3の記録前の抵抗値に比べて、元々抵抗値が低いので、記憶用薄膜3の抵抗値を低くすることにより、記憶素子10全体の抵抗値も低くすることができる。

その後、正電圧を除去して、記憶素子10にかかる電圧をなくすと、抵抗値が低くなった状態で保持される。これにより、情報を記録することが可能になる。一度だけ記録が可能な記憶装置、いわゆる、PROMに用いる場合には、この過程(記録過程)のみで記録が完結する。

この消去過程においては、下部電極1側が正負に、上部電極4側が負になるように、記憶素子10に対して負電圧(−)を印加する。

記憶素子10への負電圧の印加により、記憶用薄膜3内に形成されていた電流パス或いは不純物準位を構成していたCu,Ag,Znがイオン化して、記憶用薄膜3内を移動してイオン源層2側に戻る。

すると、記憶用薄膜3内からCu,Ag,Znによる電流パス、もしくは、欠陥が消滅して、記憶用薄膜3の抵抗値が高くなる。記憶用薄膜3以外の各層は元々抵抗値が低いので、記憶用薄膜3の抵抗値を高くすることにより、記憶素子10全体の抵抗値も高くすることができる。

その後、負電圧を除去して、記憶素子10にかかる電圧をなくすと、抵抗値が高くなった状態で保持される。これにより、記録された情報を消去することが可能になる。

即ち、記憶素子10の抵抗値の高低により、2値の情報を記憶させることができる。

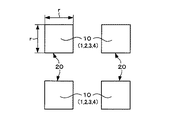

さらに、正方形状のメモリセル20の一辺の長さrを、記憶素子10の「素子サイズ」と規定する。

そして、記憶素子10の素子サイズ、即ちメモリセル20の一辺の長さrを70nm以下、より好ましくは50nm以下とする。

これにより、記憶素子に情報の記録を正しく安定して行うことができる。また、短い電圧パルスによって安定して記録を行うことができるため、記録に要する時間を短縮して、記録動作の高速化を図ることができる。

このように記憶素子10の抵抗値のばらつきを低減することができるため、エラーレートを小さくして、読み出し抵抗マージンを飛躍的に向上することができる。

図3Aに示すように、メモリセル20の平面形状を長方形(矩形)とした場合には、短辺の長さSを素子サイズとして規定する。

図3Bに示すように、メモリセル20の平面形状を円形状とした場合には、直径の長さ2Rを素子サイズとして規定する。

図3Cに示すように、メモリセル20の平面形状を楕円形状とした場合には、短軸長Bを素子サイズとして規定する。

長方形状や楕円形状のような場合には、長辺又は長軸の長さよりも、短辺又は短軸の長さの方が記憶素子の抵抗値のばらつきへの影響が大きいため、短辺又は短軸の長さを素子サイズとして規定する。

この記憶装置は、複数のワード線WLと、これらワード線WLと直交する複数のビット線BLとを有し、ワード線WLとビット線BLとの各交点に、図1及び図2に示したような記憶素子10(1,2,3,4)が配置されてメモリセル20が形成され、このメモリセル20が多数配置されることにより、メモリセルアレイが形成されている。図4では、3×3個のメモリセル20がマトリクス状に配列された構成のメモリセルアレイを示している。

また、素子サイズが50nm以下である構成の記憶素子10を用いて記憶装置を構成することにより、読み出し抵抗マージンを大きくすることができることから、読み出し時のエラーの発生が少なく、記録された情報の読み出しを安定して行うことができる。

即ち、安定して動作する、信頼性の高い記憶装置を実現することができる。

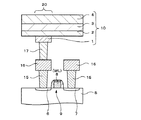

この記憶装置は、基板5、例えばシリコン基板上に、ソース領域6、ドレイン領域7、ゲート電極8から成るトランジスタ(MOSトランジスタ)9を有する。ゲート電極8はワード線WLを構成している。そして、ソース領域6には、プラグ層15・金属配線層16・プラグ層17を介して、図1及び図2に示した構成の記憶素子10の下部電極1が接続されている。ドレイン領域7には、プラグ層15を介して金属配線層16が接続されている。また、記憶素子10の上部電極4が、図示しないビット線BLに接続される。

そして、図5に示す構成のメモリセルを多数形成することにより、記憶装置(メモリ)が構成される。

例えば、下部電極1の平面形状を正方形状として、その一辺の長さrを70nm以下、より好ましくは50nm以下とする。

また、素子サイズが50nm以下である構成の記憶素子10を用いて記憶装置を構成することにより、読み出し抵抗マージンを大きくすることができることから、読み出し時のエラーの発生が少なく、記録された情報の読み出しを安定して行うことができる。

即ち、安定して動作する、信頼性の高い記憶装置を実現することができる。

記憶用薄膜3が希土類元素と酸素とを有して成り、絶縁性を有するので、隣接するメモリセル20と記憶用薄膜3を共通に形成しても、導通することがない。

これにより、共通に形成した層ではパターニングの精度を高くする必要がなくなることから、素子サイズを微細化しやすくなる利点を有する。

続いて、本発明の記憶素子を実際に作製して、その特性を調べた。

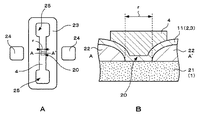

実際の記憶装置では、図4や図5に示したように、アレイ状に記憶素子を配列させていたり、記憶素子部以外にもトランジスタ等の回路素子が存在したりするが、ここでは、記憶素子の読み出し抵抗マージンを調べる目的で、図6Aに平面図、図6Bに図6AのA−A´断面図をそれぞれ示す特性評価用テストデバイス(特性評価用素子)を作製して、特性の測定・評価を行った。

そして、積層膜11と下部電極21とが接続された部分がメモリセル20となり、この部分の形状が図6Aに示すように正方形状となっている。

また、記憶素子の積層膜11(2,3)は、メモリセル20の周囲を含み、図6Aに示す縦長の素子形成領域23に形成されている。上部電極4は、素子形成領域23に沿って縦長に形成されている。素子形成領域23の左右に下部電極接続用端子パッド24が形成され、上部電極4の両端に上部電極接続用端子パッド25が形成されている。

まず、厚さ2mmのシリコン基板上に下部電極21(1)として膜厚100nmのW膜を、絶縁層22としてSiO2を、順次成膜した。

その後、フォトリソグラフィを用いて、メモリセルとなる部分と下部電極接続用端子パッドとなる部分とを除く、それ以外の部分をマスクにより覆って、絶縁層22のSiO2を選択的にエッチングした。このとき、メモリセルとなる部分、即ち下部電極21上の絶縁層22の開口の平面形状を正方形状として、正方形の一辺の長さrが、それぞれ30nm,50nm,100nm,150nmである4種類の開口を、同一ウエハのシリコン基板に各種類それぞれ多数形成した。

次に、この積層膜11(2,3)に対して、フォトリソグラフィを用いて、素子形成領域23となる横200μm×縦600μmの範囲をマスクした後に、Arプラズマにより、積層膜11(2,3)をエッチングした。

さらに、上部電極4及び端子パッド24,25となる部分以外を、フォトリソグラフィを用いてマスクした後に、DCマグネトロンスパッタ法を用いて、電極材料を成膜した。そして、公知のリフトオフ法によりマスクを除去して、それぞれ電極材料から成る、上部電極4、下部電極接続用端子パッド24、上部電極接続用端子パッド25を形成した。上部電極4としては、膜厚20nmのCr膜・膜厚100nmのCu膜・膜厚100nmのAu膜の積層膜を形成した。

このようにして、正方形状のメモリセル20の一辺の長さrが、それぞれ30nm,50nm,100nm,150nmである4種類の特性評価用テストデバイスを、シリコン基板に各種類それぞれ多数作製した。

次に、作製した特性評価用テストデバイスを用いて、記憶素子10の特性を調べた。

正方形状のメモリセル20の一辺の長さrが異なる4種類の特性評価用テストデバイスを、各種類それぞれ72個、合計288個選び、各特性評価用テストデバイスについて、2.5Vのパルス電圧を印加して書き込みを行った。

そして、各種類の72個の特性評価用テストデバイスにおいて、書き込み動作の後の抵抗値を測定し、書き込みが成功して低抵抗状態となった素子の比率、即ち書き込み成功率を求めた。

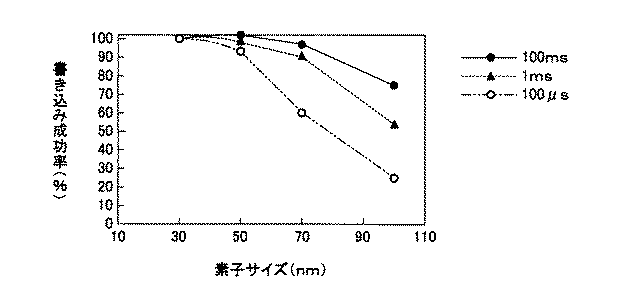

上述した方法による書き込み成功率の算出を、100m秒(100ms)、1m秒(1ms)、100μ秒(100μs)の3種類のパルス幅のパルス電圧について、それぞれ行った。

測定結果として、それぞれのパルス幅における、素子サイズ(メモリセル20の一辺の長さr)と書き込み成功率との関係を図7に示す。

そして、パルス幅を短くして1m秒にしたときに、書き込み成功率を90%以上にするためには、素子サイズを70nm以下とする必要があることがわかる。

また、パルス幅をさらに短くして100μ秒としたときに、書き込み成功率を90%以上にするためには、素子サイズを50nm以下とする必要があることがわかる。

正方形状のメモリセル20の一辺の長さrが異なる4種類の特性評価用テストデバイスを、各種類それぞれ120個、合計480個選び、各特性評価用テストデバイスについて、消去状態即ち高抵抗状態の抵抗値RHighと、書き込み状態即ち低抵抗状態の抵抗値RLOWとを測定した。

具体的には、高抵抗状態とした記憶素子10に書き込み閾値電圧よりも小さい読み出し電圧を印加して抵抗値を測定し、さらに書き込み電圧を印加して記憶素子10を低抵抗状態とした後に、高抵抗状態と同一の読み出し電圧を印加して抵抗値を測定した。なお、前述した書き込みの失敗が生じると、読み出し抵抗マージンを正しく算出することができないため、書き込み電圧として、パルス電圧ではなく、2.5Vの一定電圧を印加して、書き込みの失敗が生じないようにした。

そして、各種類の120個の特性評価用テストデバイスにおいて、これらの抵抗値RHigh,RLOWの平均値及び分散を求めた。

ここで、読み出し抵抗マージンを、以下の式(1)のように定義する。

Margin:読み出し抵抗マージン

Avg(RHigh):消去状態(高抵抗状態)における抵抗値の平均値

Avg(RLow):書き込み状態(低抵抗状態)における抵抗値の平均値

σ(RHigh):消去状態(高抵抗状態)における抵抗値の分散

σ(RLow):書き込み状態(低抵抗状態)における抵抗値の分散

Max{A,B}:A,Bの最大値

そして、高抵抗状態の抵抗値及び低抵抗状態の抵抗値が、いずれも正規分布であると仮定すると、読み出し抵抗マージンが6以上であれば、99%以上の動作率となる。

素子サイズ(メモリセル20の一辺の長さr)と動作マージンとの関係を図8に示す。

Claims (4)

- 第1の電極と、

第2の電極と、

前記第1の電極及び前記第2の電極の間に挟まれ、酸化ガドリニウム膜から成る記憶用薄膜と、

前記第1の電極及び前記第2の電極の間に挟まれ、前記記憶用薄膜と接して設けられ、Cu,Ag,Znから選ばれるいずれかのイオンとなる元素が含まれたイオン源層とを含み、

素子の平面形状が正方形状であり、正方形の一辺の長さが50nm以下である

記憶素子。 - 前記イオン源層がCuGeTeGd膜である、請求項1に記載の記憶素子。

- 第1の電極と、第2の電極と、前記第1の電極及び前記第2の電極の間に挟まれ、酸化ガドリニウム膜から成る記憶用薄膜と、前記第1の電極及び前記第2の電極の間に挟まれ、前記記憶用薄膜と接して設けられ、Cu,Ag,Znから選ばれるいずれかのイオンとなる元素が含まれたイオン源層とを含み、素子の平面形状が正方形状であり、正方形の一辺の長さが50nm以下である記憶素子と、

前記第1の電極側に接続された配線と、

前記第2の電極側に接続された配線とを有し、

前記記憶素子が多数配置されて成る

記憶装置。 - 前記記憶素子の前記イオン源層がCuGeTeGd膜である、請求項3に記載の記憶装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005208912A JP4635759B2 (ja) | 2005-07-19 | 2005-07-19 | 記憶素子及び記憶装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005208912A JP4635759B2 (ja) | 2005-07-19 | 2005-07-19 | 記憶素子及び記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007027499A JP2007027499A (ja) | 2007-02-01 |

| JP4635759B2 true JP4635759B2 (ja) | 2011-02-23 |

Family

ID=37787854

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005208912A Expired - Fee Related JP4635759B2 (ja) | 2005-07-19 | 2005-07-19 | 記憶素子及び記憶装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4635759B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5194667B2 (ja) * | 2007-09-14 | 2013-05-08 | ソニー株式会社 | 可変抵抗素子および記憶装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE69812425T2 (de) * | 1997-12-04 | 2004-01-15 | Axon Technologies Corp | Programmierbare metallisierungsstruktur mit oberflächennaher verfestigung undherstellungsverfahren dafür |

| CN1175423C (zh) * | 1999-02-11 | 2004-11-10 | 亚利桑那州立大学董事会 | 微电子可编程结构及其形成与编程方法 |

| US6693821B2 (en) * | 2001-06-28 | 2004-02-17 | Sharp Laboratories Of America, Inc. | Low cross-talk electrically programmable resistance cross point memory |

| EP1501124B1 (en) * | 2002-04-30 | 2011-06-08 | Japan Science and Technology Agency | Solid electrolyte switching devices, fpga and memory devices using the same, and method of manufacturing the same |

| JP2005167064A (ja) * | 2003-12-04 | 2005-06-23 | Sharp Corp | 不揮発性半導体記憶装置 |

-

2005

- 2005-07-19 JP JP2005208912A patent/JP4635759B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007027499A (ja) | 2007-02-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4529654B2 (ja) | 記憶素子及び記憶装置 | |

| JP4848633B2 (ja) | 記憶素子及び記憶装置 | |

| US9767899B2 (en) | Access signal conditioning for memory cells in an array | |

| US7145791B2 (en) | Memory device having variable resistive memory element | |

| JP5397668B2 (ja) | 記憶素子および記憶装置 | |

| JP4396621B2 (ja) | 記憶素子及び記憶装置 | |

| US20090224224A1 (en) | Nonvolatile memory element, nonvolatile memory apparatus, nonvolatile semiconductor apparatus, and method of manufacturing nonvolatile memory element | |

| US8148711B2 (en) | Nonvolatile memory element, manufacturing method thereof, and nonvolatile semiconductor apparatus using nonvolatile memory element | |

| JP2009141225A (ja) | 可変抵抗素子、可変抵抗素子の製造方法、不揮発性半導体記憶装置 | |

| JP2006040946A (ja) | 記憶素子 | |

| JPWO2007023569A1 (ja) | 不揮発性半導体記憶装置及びその書き込み方法 | |

| JP2012128892A (ja) | 記憶装置 | |

| JP4465969B2 (ja) | 半導体記憶素子及びこれを用いた半導体記憶装置 | |

| CN100524510C (zh) | 存储器件和半导体器件 | |

| CN111668367B (zh) | 存储装置 | |

| JP5007502B2 (ja) | 記憶素子の製造方法 | |

| JP5194640B2 (ja) | 記憶素子および記憶装置 | |

| JP4742971B2 (ja) | 記憶素子及び記憶装置 | |

| JP4635759B2 (ja) | 記憶素子及び記憶装置 | |

| JP4816314B2 (ja) | 記憶素子及び記憶装置 | |

| JP5257573B2 (ja) | 記憶素子および記憶装置 | |

| JP4760606B2 (ja) | 記憶素子及び記憶装置 | |

| JP2007157941A (ja) | 記憶素子及び記憶装置 | |

| JP5360145B2 (ja) | 記憶素子及び記憶装置 | |

| JP2006319263A (ja) | 記憶素子の製造方法、記憶装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080609 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100805 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100817 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101006 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101108 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |