JP4635676B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4635676B2 JP4635676B2 JP2005088139A JP2005088139A JP4635676B2 JP 4635676 B2 JP4635676 B2 JP 4635676B2 JP 2005088139 A JP2005088139 A JP 2005088139A JP 2005088139 A JP2005088139 A JP 2005088139A JP 4635676 B2 JP4635676 B2 JP 4635676B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- protrusion

- conductive layers

- adjacent conductive

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H10W90/724—

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

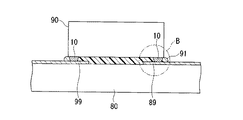

図8は従来技術に係る半導体装置の説明図であり、図8(a)は図8(b)のJ−J線における半導体装置の側面断面図であり、図8(b)は半導体装置の底面図である。図8に示すように、半導体装置90の電極22から離間して樹脂突起12を設け、その電極22および樹脂突起12を覆うように導電層20を設けて、突起電極10を形成する技術が提案されている(例えば、特許文献1参照)。この場合、樹脂突起12の弾性変形により実装時のストレスを吸収して、実装品質の安定化に寄与することができる。また突起電極10の小型化が容易であり、電極22の狭ピッチ化にも対応することができる。

この構成によれば、隣接する導電層の間における突起体の輪郭に沿って、隣接する導電層の間を遠回りするように残渣が発生する。この残渣の長さが、隣接する導電層の間の最短距離より長くなるので、残渣に沿った電界強度が低下する。これにより、マイグレーションの発生を抑制することができる。

この構成によれば、隣接する導電層の間における突起体の輪郭の長さを、隣接する導電層の間の最短距離より長くすることができる。

この構成によれば、突起体を効率的に除去することが可能になり、突起体の輪郭に残渣が発生する可能性を低減することができる。

この構成によれば、突起体の輪郭に沿って発生する残渣が、隣接する導電層と接しない。したがって、マイグレーションの発生を回避することができる。

この構成によれば、突起体の輪郭に残渣が発生しても、マイグレーションの発生を抑制することができる。

この構成によれば、隣接する導電層の間に配置された突起体を、簡単かつ確実に除去することができる。

最初に、本発明の第1実施形態について説明する。

(電気光学装置)

図1は、電気光学装置の一実施形態である液晶表示装置を示す模式図である。図示の液晶表示装置100は、本発明の半導体装置(液晶駆動用ICチップ)90を、液晶パネル110に実装して構成されている。また液晶表示装置100には、必要に応じて、図示しない偏光板、反射シート、バックライト等の付帯部材が適宜に設けられる。

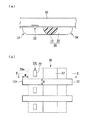

図3は第1実施形態に係る半導体装置の説明図であり、図3(a)は図2のB部における半導体装置の拡大図である。また図3(a)は図3(b)のD−D線における半導体装置の側面断面図であり、図3(b)は半導体装置の底面図である。

図3に示す半導体装置90は、例えばシリコン基板上に適宜の電子回路を形成してなる集積回路チップである。半導体装置90の能動面(図示下面)には、Al(アルミニウム)層などで構成されたパッド24が形成されている。このパッド24は、例えばTi(チタン)層やTiN(窒化チタン)層、AlCu(アルミニウム/銅)層、TiN層(キャップ層)などを順に積層した構造であってもよい。

次に、第1実施形態に係る半導体装置の製造方法につき、図3ないし図5を用いて説明する。図4および図5は、第1実施形態に係る半導体装置の製造方法の説明図である。なお図4(a)は図4(b)のE−E線における半導体装置の側面断面図であり、図4(b)は半導体装置の底面図である。また図5(a)は図5(b)のF−F線における半導体装置の側面断面図であり、図5(b)は半導体装置の底面図である。

次に、本発明の第2実施形態に係る半導体装置の製造方法につき、図6を用いて説明する。図6は第2実施形態に係る半導体装置の製造方法の説明図であり、図6(a)は図6(b)のH−H線における半導体装置の側面断面図であり、図6(b)は半導体装置の底面図である。なお図6は、第1実施形態の図5に相当する製造工程図である。図6に示す第2実施形態に係る半導体装置の製造方法は、隣接する導電層20の間における中間体132の輪郭132aが導電層20と接しないように中間体132を形成する点で、第1実施形態と相違している。なお第1実施形態と同様の構成となる部分については、その詳細な説明を省略する。

図7は、本発明に係る電子機器の一例を示す斜視図である。この図に示す携帯電話1300は、上述した電気光学装置を小サイズの表示部1301として備え、複数の操作ボタン1302、受話口1303、及び送話口1304を備えて構成されている。

上述した電気光学装置は、上記携帯電話に限らず、電子ブック、パーソナルコンピュータ、ディジタルスチルカメラ、液晶テレビ、ビューファインダ型あるいはモニタ直視型のビデオテープレコーダ、カーナビゲーション装置、ページャ、電子手帳、電卓、ワードプロセッサ、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた機器等々の画像表示手段として好適に用いることができ、いずれの場合にも信頼性に優れた電子機器を提供することができる。

Claims (6)

- 半導体装置の能動面に形成する複数の電極から離間して、前記能動面に突起体を形成する工程と、

前記各電極の表面から前記突起体の表面にかけて、複数の導電層を形成する工程と、

隣接する前記導電層の間に配置された前記突起体の一部である中間体を除去して、複数の突起電極を形成する工程と、を有する半導体装置の製造方法であって、

隣接する前記導電層の間における前記導電層の形成領域外側に延設する前記中間体の端部の前記能動面から立ち上がる輪郭の長さが、隣接する前記導電層の間の最短距離より長くなるように、前記突起体を形成することを特徴とする半導体装置の製造方法。 - 隣接する前記導電層の間に配置される前記突起体の端部は、前記隣接する導電層の形成領域の外側まで延設することを特徴とする請求項1に記載の半導体装置の製造方法。

- 隣接する前記導電層の間に配置される前記突起体の角部には、丸面取りを施すことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

- 複数の電極から離間して突起体を形成する工程と、

前記各電極の表面から前記突起体の表面にかけて複数の導電層を形成する工程と、

隣接する前記導電層の間に配置された前記突起体の一部である中間体を除去して、複数の突起電極を形成する工程と、を有する半導体装置の製造方法であって、

隣接する前記導電層の間における前記中間体の端部の輪郭が、隣接する前記導電層と接しないように、前記突起体を形成することを特徴とする半導体装置の製造方法。 - 前記突起体は樹脂材料で構成し、前記突起体の除去はプラズマ処理によって行うことを特徴とする請求項1ないし請求項4のいずれかに記載の半導体装置の製造方法。

- 隣接する前記導電層の間に配置された前記突起体の除去は、前記導電層をマスクとしてプラズマ処理することによって行うことを特徴とする請求項1ないし請求項5のいずれかに記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005088139A JP4635676B2 (ja) | 2005-03-25 | 2005-03-25 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005088139A JP4635676B2 (ja) | 2005-03-25 | 2005-03-25 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006269895A JP2006269895A (ja) | 2006-10-05 |

| JP4635676B2 true JP4635676B2 (ja) | 2011-02-23 |

Family

ID=37205507

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005088139A Expired - Fee Related JP4635676B2 (ja) | 2005-03-25 | 2005-03-25 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4635676B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4858161B2 (ja) * | 2006-12-26 | 2012-01-18 | セイコーエプソン株式会社 | 半導体装置及び電子デバイスの製造方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000353716A (ja) * | 1999-06-14 | 2000-12-19 | Matsushita Electronics Industry Corp | 半導体装置およびその製造方法ならびに半導体装置が実装されたモジュール |

| JP3969295B2 (ja) * | 2002-12-02 | 2007-09-05 | セイコーエプソン株式会社 | 半導体装置及びその製造方法と回路基板及び電気光学装置、並びに電子機器 |

| JP2004260074A (ja) * | 2003-02-27 | 2004-09-16 | Seiko Epson Corp | 半導体装置、半導体装置の製造方法及びその実装方法、回路基板並びに電子機器 |

-

2005

- 2005-03-25 JP JP2005088139A patent/JP4635676B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006269895A (ja) | 2006-10-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3994989B2 (ja) | 半導体装置、回路基板、電気光学装置および電子機器 | |

| JP3969295B2 (ja) | 半導体装置及びその製造方法と回路基板及び電気光学装置、並びに電子機器 | |

| JP2008060526A (ja) | チップフィルムパッケージ、及びこれを含むディスプレイパネルアセンブリ | |

| JP3873986B2 (ja) | 電子部品、実装構造体、電気光学装置および電子機器 | |

| JP4218622B2 (ja) | 半導体装置の製造方法 | |

| KR20090041317A (ko) | 반도체장치 및 그의 제작방법 | |

| JP4165495B2 (ja) | 半導体装置、半導体装置の製造方法、回路基板、電気光学装置、電子機器 | |

| JP2009031362A (ja) | 配線基板、その製造方法、及び表示装置 | |

| JP4651367B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP4151634B2 (ja) | 半導体装置とその製造方法、回路基板、電気光学装置および電子機器 | |

| JP2005109110A (ja) | 半導体装置とその製造方法、回路基板、電気光学装置、及び電子機器 | |

| TWI487439B (zh) | 撓性電路板及包括該撓性電路板的顯示裝置暨撓性電路板的製造方法 | |

| JP4554983B2 (ja) | 液晶表示装置 | |

| JP4635676B2 (ja) | 半導体装置の製造方法 | |

| US6853080B2 (en) | Electronic device and method of manufacturing the same, and electronic instrument | |

| JP2006196728A (ja) | 電子部品、電気光学装置、及び電子機器 | |

| JP2011233624A (ja) | 半導体素子及び該半導体素子を備える電子機器 | |

| JP4655052B2 (ja) | 半導体装置、回路基板、電気光学装置および電子機器 | |

| JP2010157770A (ja) | 半導体装置、回路基板、電気光学装置および電子機器 | |

| JP2006093265A (ja) | 半導体装置、回路基板、電気光学装置および電子機器 | |

| JP4862390B2 (ja) | 電子基板の製造方法 | |

| JP4665631B2 (ja) | 電子基板とその製造方法及び電気光学装置の製造方法並びに電子機器の製造方法 | |

| JP4720992B2 (ja) | 半導体装置 | |

| JP2007042777A (ja) | 半導体装置とその製造方法、回路基板、電気光学装置、及び電子機器 | |

| JP4656191B2 (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080307 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20080311 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100308 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100406 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100521 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20100521 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100513 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100629 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100712 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101108 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |