本発明は、半導体素子を有する半導体装置の作製方法に関するものである。

従来、薄膜トランジスタ(以下「TFT」ともいう。)やMOSトランジスタに代表される半導体素子によって構成される所謂アクティブマトリクス駆動方式の表示パネル、又は半導体集積回路は、フォトマスクを使った光露光工程(以下、フォトリソグラフィー工程と示す。)により、レジストマスクを形成した後、各種薄膜を選択的にエッチングすることにより製造されている。

フォトリソグラフィー工程は、レジストを基板全面に塗布しプリベークを行った後、フォトマスクを介して紫外線等をレジストに照射して露光し、現像してレジストマスクを形成する。この後、該レジストマスクをマスクとして、半導体領域や配線となるべき部分以外に存在する薄膜(半導体材料、絶縁体材料、又は導電体材料で形成される薄膜)をエッチング除去して、半導体領域や配線を形成している。

特開2000−188251号公報

しかしながら、従来のフォトリソグラフィ工程を用いて半導体膜をエッチングして、所望の形状の半導体領域を形成する場合、半導体膜表面にレジストを塗布する。このとき、半導体膜表面がレジストに直接さらされるため、レジストに含まれる酸素、炭素、重金属元素等の不純物により、半導体膜が汚染されるという問題がある。この汚染により、半導体膜中に不純物元素が混入してしまい、半導体素子の特性が低下する。特に、TFTにおいては、トランジスタ特性のバラツキ及び低下の原因となるという問題がある。

また、フォトリソグラフィー工程を用いた配線や半導体領域の形成工程において、レジストの材料の大部分が無駄になると共に、配線や半導体領域を形成するための工程数が多く、スループットが低下する。

本発明は、このような状況に鑑みなされたものであり、レジストを用いずとも所望の形状の半導体領域を有する半導体素子の形成方法を提供する。また、少ない工程数で、コスト削減が可能な半導体装置の作製方法を提供する。また、原料の削減によりコスト削減が可能な半導体装置の作製方法を提供する。また、スループットの向上が可能で、量産性の高い半導体装置の作製方法を提供する。また、バラツキの少ない半導体装置の作製方法を提供する。

本発明は、半導体膜の一部を酸化して酸化物層を形成した後、該酸化物層をマスクとして半導体膜をエッチングして、所望の形状を有する半導体領域を形成すること要旨とする。

半導体膜上にマスクとして機能する酸化物層を形成する方法として、半導体膜に透光部及び遮光部を有するマスクを介してレーザ光を照射する方法がある。

また、半導体膜上にマスクとして機能する酸化物層を形成する方法として、半導体膜の一部に保護材を貼付けて半導体膜の一部を露出し、該露出部を酸化力を有する酸化剤に浸漬し酸化して酸化物層を形成する方法がある。

また、本発明の一は、基板上に半導体膜を形成し、前記半導体膜上に形成される第1の酸化物層の一部上に第2の酸化物層を形成した後、前記第1の酸化物層の露出部を除去し、前記第2の酸化物層をマスクとして前記半導体膜をエッチングして、半導体領域を形成することを特徴とする。

また、本発明の一は、基板上に半導体膜を形成し、前記半導体膜上に形成される第1の酸化物層を除去した後、前記半導体膜の一部上に前記第2の酸化物層を形成し、前記第2の酸化物層をマスクとして前記半導体膜をエッチングして、半導体領域を形成することを特徴とする。

半導体膜上に第2の酸化物層を形成する方法として、半導体膜に透光部及び遮光部を有するマスクを介してレーザ光を照射する方法がある。

また、半導体膜上に第2の酸化物層を形成する方法として、半導体膜の一部に保護材を貼付けて半導体膜の一部を露出し、該露出部を、酸化力を有する酸化剤に浸漬し酸化して第2の酸化物層を形成する方法がある。

半導体膜上に形成された酸化物層は、半導体膜の表面が酸化された酸化珪素膜である。該酸化物層と半導体膜とは、エッチング工程において、選択比を取ることが可能である。この結果、酸化物層をマスクとして半導体膜を選択的にエッチングすることが可能である。

半導体膜のエッチング方法としては、ドライエッチング法、ウエットエッチング法が挙げられる。ドライエッチング法としては、Cl2、BCl3、SiCl4もしくはCCl4などを代表とする塩素系ガス、CF4、SF6、NF3、CHF3、ClF3などを代表とするフッ素系ガスから選択された一以上のガスを用いてエッチングすることができる。また、上記塩素系ガス及びフッ素系から選択された一以上のガス及びO2を用いてエッチングすることができる。また、ウエットエッチング法としては、ヒドラジンや、テトラメチルアンモニウムハイドロオキサイド(TMAH、化学式:(CH3)4NOH)を含む水溶液などアルカリ溶液を用いてエッチングすることができる。

また、レーザ光のビームスポット形状は、線状、矩形状、又は面状であることが好ましい。

また、本発明の一は、当該半導体領域を活性層として有する半導体素子、及び当該半導体素子で構成される半導体装置である。半導体素子としては、TFT、記憶素子、ダイオード、光電変換素子、容量素子、抵抗素子等が挙げられる。また、TFTとしては、順スタガ型TFT、逆スタガ型TFT(チャネルエッチ型TFT又はチャネル保護型TFT)、トップゲートTFTのコプレナー型TFTがあげられる。

また、本発明において、半導体装置としては、半導体素子で構成された集積回路、表示装置、無線タグ、ICタグ等が挙げられる。表示装置としては、代表的には液晶表示装置、発光表示装置、DMD(Digital Micromirror Device;デジタルマイクロミラーデバイス)、PDP(Plasma Display Panel;プラズマディスプレイパネル)、FED(Field Emission Display;フィールドエミッションディスプレイ)、電気泳動表示装置(電子ペーパー)等の表示装置があげられる。

なお、本発明において、表示装置とは、表示素子を用いたデバイス、即ち画像表示デバイスを指す。また、表示パネルにコネクター、例えばフレキシブルプリント回路配線基板(FPC:Flexible Printed Circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass)方式によりIC(集積回路)やCPUが直接実装されたモジュールも全て表示装置に含むものとする。

本発明では、透光部及び遮光部を有するマスク、又は保護材用いて半導体膜の一部に、酸化物層を形成し、該酸化物層をマスクとして半導体膜をエッチングすることが可能である。このため、公知のレジストを用いたフォトリソグラフィー工程を用いずとも、所定の場所に、所望の形状を有する半導体領域を形成することが可能である。

また、線状レーザ光、矩形状レーザ光、面状レーザ光等のビームスポットの面積の大きなレーザ光を半導体膜に照射することで、短時間で酸化物層で形成される複数のマスクを形成した後、所望の形状を有する半導体領域を形成することが可能である。このため、半導体装置を量産性高く作製することが可能である。

また、レジスト塗布による半導体膜への不純物元素の混入を避けつつ、所望の形状の半導体素子を形成することが可能であり、ばらつきが少なく、且つ高集積化された半導体装置を、量産性高く作製することが可能である。また、レジストを用いたフォトリソグラフィー工程を経ずとも、所望の形状を有する半導体領域を形成することが可能であるため、少ない工程数で、且つ原料の削減が可能である。この結果、コスト削減が可能である。

また、配線等を形成する際に、液滴吐出法を用いることによって、それらの膜の材料を含む液滴の吐出口であるノズルと、基板との相対的な位置を変化させて任意の場所に液滴を吐出できる。また、ノズル径、液滴の吐出量、及びノズルと吐出物が形成される基板との移動速度の相対的な関係によって、形成する膜パターンの厚さや太さを調整できる。このため、一辺が1〜2mを越えるような大面積の基板上においても、所望の箇所に膜パターンを精度良く形成することができる。また、隣り合う膜パターンとの不整合が生じないため、歩留まりを向上させることができる。この結果、少ない工程数で、歩留まり高く半導体装置を作製することが可能である。

さらには、上記の作製工程により形成された半導体装置を有する液晶テレビジョン並びにELテレビジョンを、低コストで作製することができる。

以下、発明を実施するための最良の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は本実施の形態の記載内容に限定して解釈されるものではない。また、各図面において共通の部分は同じ符号を付して詳しい説明を省略する。

(実施の形態1)

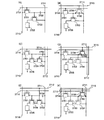

本実施の形態においては、レーザ光(以下、レーザビームとも示す。)を照射して、所望の形状を有する半導体領域の形成工程を図1、図22、図24、及び図25を用いて説明する。

図1に示すように、基板101上に第1の絶縁層102を形成し、第1の絶縁層上に半導体膜103を形成する。このとき、半導体膜103表面が酸素に曝されると、半導体膜の表面が酸化され、第2の絶縁層104が形成される。なお、このように半導体膜の表面が酸化されて形成された第2の絶縁層104は、自然酸化膜とも呼ばれる。

基板101としては、ガラス基板、石英基板、アルミナなどのセラミック等絶縁物質で形成される基板、プラスチック基板、シリコンウェハ、金属板等を用いることができる。また、基板101がガラス基板の場合、320mm×400mm、370mm×470mm、550mm×650mm、600mm×720mm、680mm×880mm、1000mm×1200mm、1100mm×1250mm、1150mm×1300mmのような大面積基板を用いることができる。

プラスチック基板の代表例としては、PET(ポリエチレンテレフタレート)、PEN(ポリエチレンナフタレート)、PES(ポリエーテルサルスルホン)、ポリプロピレン、ポリプロピレンサルファイド、ポリカーボネイト、ポリエーテルイミド、ポリフェニレンサルファイド、ポリフェニレンオキサイド、ポリサルフォン、またはポリフタールアミドからなるプラスチック基板、直径数nmの無機粒子が分散された有機材料で形成される基板等が挙げられる。また、基板の表面は平面である必要はなく、凹凸又は曲面を有するものでもよい。

第1の絶縁層102は、プラズマCVD法またはスパッタリング法などの薄膜形成法を用い、窒化シリコン、酸化シリコン、その他の珪素を含む絶縁膜の単層又は積層構造で形成する。また、基板からの不純物のブロッキング効果、及び半導体領域との界面特性の点から、第1の絶縁層を基板に接する側から窒化珪素膜(窒化酸化珪素膜)、酸化珪素膜、及び窒化珪素膜(窒化酸化珪素膜)の積層構造とすることが好ましい。

半導体膜103としては、非晶質半導体、非晶質状態と結晶状態とが混在したセミアモルファス半導体(SASとも表記する)、及び非晶質半導体中に0.5nm〜20nmの結晶粒を観察することができる微結晶半導体から選ばれたいずれかの状態を有する膜を形成する。特に、0.5nm〜20nmの結晶を粒観察することができる微結晶状態はいわゆるマイクロクリスタル(μc)と呼ばれている。

半導体膜は、シリコン、シリコン・ゲルマニウム(SiGe)等を主成分として形成することが可能である。また、上記主成分の他に、リン、ヒ素、ボロン等のアクセプター型元素又はドナー型元素が含まれていても良い。半導体膜の膜厚は、10〜150nm、好ましくは30〜70nmであることが望ましい。

第2の絶縁層104は、半導体膜が大気中の酸素と触れ、反応して形成された酸化珪素膜である。このため、第2の絶縁層104の膜厚は薄く、膜厚5〜15nm、代表的には、10nmである。

次に、第3の絶縁層121を形成する。第3の絶縁層121は、酸化物層、代表的には、半導体酸化物層である。第3の絶縁層121の形成方法としては、透光部及び遮光部を有するマスク(以下、フォトマスクと示す。)を介してレーザ光を照射する方法、酸化力を有する酸化剤に半導体膜を浸漬する方法等を用いることができる。なお、第3の絶縁層121は、第2の絶縁層の一部の膜厚が厚くなった領域である。

レーザ光111が照射されない領域は、第2の絶縁層のまま残存する。第3の絶縁層の周囲で露出する第2の絶縁層を第4の絶縁層122と示す。レーザ光の照射時の雰囲気は、酸素雰囲気、又は空気雰囲気で行う。

ここで、フォトマスクについて図25を用いて説明する。図25(A)は、透光性を有する材料で形成される透光部1002と、遮光性を有する材料で形成される遮光部1001とが、隣接して形成されるマスクである。

透光性を有する材料とは、紫外光、可視光、又は赤外光の波長を有する光、好ましくは400nmから700nmの光(可視光)を透過することが可能な材料である。代表的には、ガラス基板、石英基板、サファイヤ基板や、アクリル樹脂、エポキシ樹脂、ユリア樹脂、不飽和ポリエステル、酢酸ビニル樹脂、ポリビニルアセタール、ポリスチレン、メタクリル樹脂、プロピレン、ポリカーボネイト等の透光性を有する樹脂で形成された基板、更には表面に結晶性珪素膜が形成される上記基板等が挙げられる。

一方、遮光性を有する材料とは、遮光性を有する材料、即ち紫外光、可視光、又は赤外光の波長を有する光、好ましくは400nmから700nmの光(可視光)を吸収することが可能な材料である。代表的には、顔料や色素が分散又は溶解された樹脂、ポリイミド、フラン樹脂、フェノール樹脂、その他の紫外光、可視光、又は赤外光の波長を有する光を吸収する樹脂が挙げられる。

図25(B)は、透光性を有する基板1012上に遮光性を有する層1011を形成したマスクである。透光性を有する基板1012としては、図25(A)の透光性を有する材料で形成される基板が挙げられる。また、遮光性を有する層としては、チタン(Ti)、アルミニウム(Al)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、銅(Cu)、クロム(Cr)、ニオブ(Nb)、鉄(Fe)、ニッケル(Ni)、コバルト(Co)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、銀(Ag)、金(Au)、白金(Pt)、カドミウム(Cd)、亜鉛(Zn)、ゲルマニウム(Ge)、ジルコニウム(Zr)、バリウム(Ba)から選ばれた元素、または該元素を主成分とする合金材料、窒素化合物、酸素化合物、炭素化合物、ハロゲン化合物の単層、またはこれらの積層を用いることができる。

図25(C)は、遮光性を有する基板1021に開口部1022を設けたマスクであり、代表的には、アルミニウムや、ステンレスで形成される基板に開口部を設けることで形成できる。

ここでは、図1(B)及び図22(A)に示すように、フォトマスク112の上からレーザ光111を照射して、透光部を透過したレーザ光が、半導体膜又は半導体膜表面に形成された第2の絶縁層104に照射される。この結果、図1(C)に示すように、レーザ光が照射された領域では、レーザ光のエネルギーにより、第2の絶縁層104や半導体膜103が酸化され、第3の絶縁層121が形成される。第3の絶縁層121の膜厚は、第2の絶縁層104の膜厚の2倍以上であることが好ましい。また、第3の絶縁層121は、緻密な絶縁層であることが好ましく、第2の絶縁層と比較してエッチングレートが小さく、代表的にはエッチングレートが半分以下の絶縁層であることが好ましい。

なお、第2の絶縁層にレーザ光を照射する前に、半導体膜103の膜中の水素濃度を低減しておくことが好ましい。代表的には、水素濃度を低減して半導体膜を成膜することがあげられる。また、半導体膜103を加熱して水素出しを行っても良い。水素濃度の低減や水素出しを行うことで、半導体膜にレーザ光を照射したときに生じる水素の脱離、及びそれに伴う半導体膜の表面粗さを低減することが可能である。

レーザ発振器1003としては、紫外光、可視光、又は赤外光を発振することが可能なレーザ発振器を用いることができる。レーザ発振器としては、KrF、ArF、XeCl、Xe等のエキシマレーザ発振器、He、He−Cd、Ar、He−Ne、HF等の気体レーザ発振器、YAG、YVO4、YLF、YAlO3などの結晶にCr、Nd、Er、Ho、Ce、Co、Ti又はTmをドープした結晶を使った固体レーザ発振器、GaN、GaAs、GaAlAs、InGaAsP等の半導体レーザ発振器を用いることができる。なお、固体レーザ発振器においては、基本波の第2高調波〜第5高調波を適用するのが好ましい。

また、レーザ発振器から射出されるレーザ光としては、連続発振又はパルス発振のレーザ光を用いることができる。

また、レーザ光のビームスポット(被照射体の表面において実際にレーザ光が照射される照射領域)は、長さ100mm以上の線状、数cm角の矩形状、又は正方形又はそれに近い長方形であり、1回のショットで照射することが可能な面状であることが好ましい。このようなスポット形状のレーザ光を照射することにより、レーザ光の照射のスループットを高めることができ、量産性を高めることが可能である。

なお、ここでいう「線状」は、厳密な意味で「線」を意味しているのではなく、アスペクト比の大きい長方形(もしくは長楕円形)を意味する。例えば、アスペクト比が2以上(好ましくは10〜10000)のものを線状と呼ぶが、線状が矩形状に含まれることに変わりはない。

また、レーザ光111は、半導体膜103及び第2の絶縁層104の表面が活性化し、反応しやすくなり、第2の絶縁層表面、又は半導体膜と第2の絶縁層との間で絶縁層が形成される程度の強度に制御することが好ましい。この結果、レーザ光を照射した後の半導体膜103は完全溶融せず、非晶質半導体膜、SAS、又はμcである。

次に、図1(D)に示すように、第4の絶縁層122を除去し、半導体膜の一部を露出することで、第3の絶縁層を半導体膜上に残存させる。

第4の絶縁層122の除去方法としては、ウエットエッチング、又はドライエッチング等の公知の手法により除去する。このとき、第3の絶縁層121が残存するように、適宜エッチング条件を制御する。

次に、図1(E)に示すように、第3の絶縁層121をマスクとして、半導体膜103をエッチングして、所望の形状を有する半導体領域132を形成することができる。半導体膜103のエッチング方法としては、ドライエッチング法、ウエットエッチング法が挙げられる。ドライエッチング法としては、Cl2、BCl3、SiCl4もしくはCCl4などを代表とする塩素系ガス、CF4、SF6、NF3、CHF3、ClF3などを代表とするフッ素系ガスから選択された一以上のガスを用いてエッチングすることができる。また、上記塩素系ガス及びフッ素系から選択された一以上のガス及びO2を用いてエッチングすることができる。また、ウエットエッチング法としては、ヒドラジンや、テトラメチルアンモニウムハイドロオキサイド(TMAH、化学式:(CH3)4NOH)を含む水溶液などアルカリ溶液を用いてエッチングすることができる。

なお、このときの斜視図を図22(B)に示す。

以上の工程により、レジストを用いずとも所望の形状を有する半導体領域を形成することができる。

(実施の形態2)

本実施の形態では、実施の形態1とは異なる工程により、所望の形状を有する半導体領域の形成する工程を、図2を用いて説明する。本実施の形態では、実施の形態1と比較して、第2の絶縁層の除去工程と、第3の絶縁層の形成工程との順序が異なる。

図2(A)に示すように、実施の形態1と同様に、基板101上に第1の絶縁層102を形成し、第1の絶縁層上に半導体膜103を形成する。このとき、半導体膜103表面において、半導体膜103の表面が酸化され、第2の絶縁層104が形成される。

次に、図2(B)に示すように、第2の絶縁層104をウエットエッチング法、ドライエッチング法等により除去し、半導体膜103を露出する。

次に、図2(C)に示すように、半導体膜103の一部に、実施の形態1と同様にフォトマスク112を介してレーザ光111を照射して、図2(D)に示すように、半導体膜103上に第3の絶縁層141を形成する。第3の絶縁層141は、酸化物層であり、代表

的には半導体酸化物層があげられる。第3の絶縁層141の膜厚は、後に半導体膜103をエッチングするマスクとして機能するため、第3の絶縁層141の膜厚は、第2の絶縁層104の膜厚の2倍以上であることが好ましい。また、第3の絶縁層141は、緻密な絶縁層であることが好ましく、第2の絶縁層と比較してエッチングレートが小さく、代表的にはエッチングレートが半分以下の絶縁層であることが好ましい。

次に、図2(E)に示すように、第3の絶縁層141をマスクとして、半導体膜103をエッチングして、半導体領域132を形成する。

以上の工程により、レジストを用いずとも所望の形状を有する半導体領域を形成することができる。

(実施の形態3)

本実施の形態では、実施の形態1又は実施の形態2とは結晶状態が異なる半導体領域を形成する工程を、図3を用いて説明する。なお、本実施の形態では、実施の形態1の工程順序を用いて説明するが、実施の形態2の工程順序を用いることも可能である。

図3(A)に示すように、実施の形態1と同様に、基板101上に第1の絶縁層102を形成し、第1の絶縁層上に半導体膜103を形成する。このとき、半導体膜103表面において、半導体膜103の表面が酸化され、第2の絶縁層104が形成される。

次に、図3(B)に示すように、第2の絶縁層104の一部に、フォトマスク112を介してレーザ光111を照射する。このとき、レーザ光の強度を制御することで、半導体膜103のレーザ光が照射された領域が溶融する。また、溶融した半導体膜の領域152の周囲では、溶融しない半導体膜153が残存する。

この後、溶融した半導体を自然冷却することで、図3(C)に示すように、レーザ光の照射により、半導体膜が酸化され第3の絶縁層162が形成されると共に、結晶性を有する半導体領域161が形成される。第3の絶縁層162は、酸化物層、代表的には半導体酸化物層である。

また、第3の絶縁層162の周囲には、第2の絶縁層が残存する。ここでは、第3の絶縁層162の周囲に残存した第2の絶縁層を第4の絶縁層163と示す。ここでは、第3の絶縁層162の膜厚は、第4の絶縁層163の膜厚の2倍以上であることが好ましい。また、第3の絶縁層162は、緻密な絶縁層であることが好ましく、第2の絶縁層と比較してエッチングレートが小さく、代表的にはエッチングレートが半分以下の絶縁層であることが好ましい。

次に、図3(D)に示すように、第4の絶縁層163をウエットエッチング法、ドライエッチング法等により除去し、半導体膜103を露出する。この工程により、マスクとして機能する第3の絶縁層162を形成することが可能である。なお、第3の絶縁層162が残存するように、適宜エッチング条件を制御する。

次に、図3(E)に示すように、第3の絶縁層162をマスクとして、半導体膜103をエッチングして、所望の形状を有する半導体領域171を形成する。半導体膜103のエッチング方法としては、実施の形態1に示すドライエッチング、ウエットエッチング等を適宜用いる。ここでは、第3の絶縁層162をマスクとしてエッチングするため、結晶性を有する半導体領域171が残存する。

以上の工程により、レジストを用いずとも所望の形状を有し、且つ結晶性を有する半導体領域を形成することができる。

(実施の形態4)

本実施の形態では、半導体素子の作製方法について図4を用いて説明する。本実施の形態では、半導体素子の代表例として、逆スタガ型TFTのチャネルエッチ型TFTを用いて説明する。また、以下の実施の形態4乃至実施の形態7では、実施の形態2を用いて半導体素子を形成する工程を説明するが、これに限定させることなく実施の形態1又は実施の形態3を適宜用いることが可能である。

図4(A)に示すように、基板201上に第1の導電層202を形成する。第1の導電層202は、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Ge、Zr、Ba等の金属、又は金属窒化物、若しくは透明導電膜として用いられるITO(酸化インジウム酸化スズ合金)、酸化ケイ素を組成物として有するITO、有機インジウム、有機スズ、酸化亜鉛(ZnO)等を適宜選択して形成する。第1の導電層202の形成方法としては、液滴吐出法、印刷法、電解メッキ法、PVD法、CVD法を適宜選択する。

PVD法またはCVD法を用いて第1の導電層を形成する場合、液滴吐出法による感光性材料の滴下、またはフォトリソグラフィー工程、レーザビーム直接描画装置を用いた感光性材料の露光及び現像等によって、導電膜上にマスクを形成し、該マスクを用いて導電膜を所望の形状にエッチングして第1の導電層を形成する。

また、液滴吐出法で第2の導電層を形成する場合、吐出口(以下、ノズルと示す。)から上記金属の粒子が有機樹脂に溶解又は分散された組成物を吐出する。有機樹脂は、金属粒子のバインダー、溶媒、分散剤、及び被覆剤として機能する有機樹脂から選ばれた一つ又は複数を用いることができる。代表的には、ポリイミド、アクリル、ノボラック樹脂、メラミン樹脂、フェノール樹脂、エポキシ樹脂、珪素樹脂、フラン樹脂、ジアリルフタレート樹脂等の公知の有機樹脂が挙げられる。

なお、組成物の粘度は5〜20mPa・sが好適である。これは、乾燥が起こることを防止し、吐出口から金属粒子を円滑に吐出できるようにするためである。また、表面張力は40mN/m以下が好ましい。なお、用いる溶媒や用途に合わせて、組成物の粘度等は適宜調整するとよい。

組成物に含まれる金属粒子の径は、各ノズルの径や所望のパターン形状などに依存するが、ノズルの目詰まり防止や高精細なパターンの作製のため、なるべく小さい方が好ましく、好適には粒径0.1μm以下が好ましい。金属粒子は、電解法、アトマイズ法又は湿式還元法等の公知の方法で形成されるものであり、その粒子サイズは、一般的に約0.5nm〜10μmである。ただし、ガス中蒸発法で形成すると、分散剤で保護されたナノ分子は約7nmと微細である。またこのナノ粒子は、被覆剤を用いて各粒子の表面を覆うと、溶剤中に凝集がなく、室温で安定に分散し、液体とほぼ同じ挙動を示す。

組成物を吐出する工程は、減圧下で行っても良い。これは、組成物を吐出して被処理物に着弾するまでの間に、該組成物の有機樹脂が揮発し、金属粒子の焼成の工程において、レーザ光のエネルギー密度を弱めることができるためである。

本実施の形態においては、液滴吐出法を用いて、基板201上に数nmの銀粒子が分散されたAgペーストを選択的に吐出し、焼成して、銀粒子が焼成された第1の導電層202を形成する。第1の導電層202は、導電体である微粒子が3次元に不規則に重なり合って形成されている。即ち、3次元凝集体粒子で構成されている。このため、表面は微細な凹凸を有する。また、第1の導電層202の加熱温度及び時間により、微粒子が焼成され粒子の粒径が増大するため、表面の高低差が大きい層となる。なお、微粒子が溶融した領域は、多結晶構造となる場合もある。この場合、マスクパターンを用いたエッチング工程が不要となるので、作製工程を大幅に簡略化することができる。

次に、第1の導電層202上にゲート絶縁膜として機能する第1の絶縁層221、第1の半導体膜222、導電性を有する第2の半導体膜223を形成する。

第1の絶縁層221はプラズマCVD法またはスパッタリング法などの薄膜形成法を用い、窒化シリコン、酸化シリコン、その他の珪素を含む絶縁膜の単層又は積層構造で形成する。また、第1の絶縁層を第1の導電層に接する側から、窒化珪素膜(窒化酸化珪素膜)、酸化珪素膜、及び窒化珪素膜(窒化酸化珪素膜)の積層構造とすることが好ましい。この構造では、ゲート電極が、窒化珪素膜と接しているため、酸化による劣化を防止することができる。

第1の半導体膜222は、非晶質半導体、SAS、μc、及び結晶性半導体から選ばれたいずれかの状態を有する膜で形成する。いずれも、シリコン、シリコン・ゲルマニウム(SiGe)等を主成分とし、膜厚は、好ましくは10〜100、更に好ましくは20〜60nmとする。

結晶性半導体膜は、非晶質半導体膜を又はSASを、加熱又はレーザ照射により結晶化して形成することができる。また、直接、結晶性半導体膜を形成してもよい。

更には、非晶質半導体膜上に、チタン(Ti)、ニッケル(Ni)、タングステン(W)、モリブデン(Mo)、コバルト(Co)、ジルコニウム(Zr)、タンタル(Ta)、バナジウム(V)、ニオブ(Nb)、クロム(Cr)、白金(Pt)、パラジウム(Pd)等の金属触媒を添加し加熱して結晶性半導体膜を形成しても良い。但し、該手法により結晶性半導体膜を形成する場合、後の工程により金属触媒を除去することが好ましい。この除去方法としては、結晶質半導体膜の一部に不純物(代表的には、アルゴン、リン、希ガス)を添加し、加熱して該不純物が添加された領域に触媒元素を移動させる手法、結晶性半導体膜表面に上記不純物を有する半導体膜を形成し加熱して、不純物を有する半導体膜に触媒元素を移動させる手法等がある。

第2の半導体膜223は、導電性を有する非晶質半導体、SAS、μcで形成する。nチャネル型のTFTを形成する場合には、15属の元素、代表的にはリンまたはヒ素を添加する。また、pチャネルTFTを形成する場合には、13属の元素、代表的にはボロンを添加する。第2の半導体膜は、珪化物気体にボロン、リン、ヒ素のような13属又は15属の元素を有する気体を加えたプラズマCVD法で成膜する。

次に、第2の半導体膜223の表面に形成された酸化膜を除去した後、第2の半導体膜の一部に、フォトマスク225を介してレーザ光224を照射する。この結果、図4(B)に示すように、第2の絶縁層231を形成する。ここでは、第2の半導体膜223の一部が、レーザ光のエネルギーにより酸化され、第2の絶縁層としては酸化珪素膜が形成される。また、第2の半導体膜は、完全溶融せず、非晶質半導体、SAS、又はμcである。

次に、図4(C)に示すように、第2の絶縁層231をマスクとして、第2の半導体膜223をエッチングし、第2の半導体領域232を形成する。次に、第2の絶縁層231をマスクとして用いて第1の半導体膜222をエッチングして、第1の半導体領域233を形成する。この後、第2の絶縁層231を除去する。

次に、図4(D)に示すように、第1の半導体膜及び第2の半導体膜は、実施の形態1で示した第1の半導体膜のエッチング方法を適宜用いてエッチングすることができる。

次に、図4(E)に示すように、第2の半導体領域232上にソース電極及びドレイン電極として機能する第2の導電層241、242を、導電性材料を用いて形成する。第2の導電層241、242は、本実施の形態の第1の導電層202で示した第1の導電層の材料及び形成方法を適宜用いることができる。ここでは、数nmの銀粒子が分散された溶液Agペーストを選択的に吐出し、焼成して第2の導電層241、242を形成する。

次に、第2の導電層241、242をマスクとして、第1の半導体領域232の露出部をエッチングして分断してソース領域及びドレイン領域として機能する第3の半導体領域251、252を形成する。この工程において、一部がエッチングされた第1の半導体領域233を第4の半導体領域253と示す。第4の半導体領域253は、チャネル領域として機能する。

なお、第4の半導体領域がSASや結晶性半導体膜で形成されている場合、本実施の形態のように、ソース領域及びドレイン領域として機能する第3の半導体領域が、ゲート電極として機能する第1の導電層を覆っている構造のほかに、第3の半導体領域の端部と第1の導電層の端部が一致しているいわゆるセルフアライン構造とすることができる。さらには、第3の半導体領域が第1の導電層を覆わず、一定の距離を隔てて形成されている構造とすることができる。この構造の場合、オフ電流を低減することができるため、該TFTを表示装置のスイッチング素子として用いた場合、コントラストを向上させることができる。さらに、第4の半導体領域が域複数の第1の導電層を覆ういわゆるマルチゲート電極構造のTFTとしても良い。この場合も、オフ電流を低減することができる。

次に、第2の導電層241、242及び第4の半導体領域253上に、パッシベーション膜を成膜することが好ましい。パッシベーション膜は、プラズマCVD法又はスパッタリング法などの薄膜形成法を用い、窒化珪素、酸化珪素、窒化酸化珪素、酸化窒化珪素、酸化窒化アルミニウム、または酸化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素(CN)、その他の絶縁性材料を用いて形成することができる。

以上の工程により、所望の形状の半導体領域を有するチャネルエッチ型TFTを作製することができる。また、ばらつきが少なく、且つ高集積化された半導体装置を作製することが可能である。

(実施の形態5)

本実施の形態では、半導体素子としてボトムゲートTFTにおいて、チャネル保護型TFTを、図5を用いて説明する。

図5(A)に示すように、実施の形態4と同様の工程により基板201上にゲート電極として機能する第1の導電層202を形成した後、ゲート絶縁膜として機能する第1の絶縁層221、第1の半導体膜222を形成する。次に、第1の半導体膜222上であって、且つ第1の導電層202に重畳する領域に保護膜301を形成する。

保護膜301は、耐熱性高分子材料を用いて形成することが好ましく、芳香環及び複素環を主鎖にもち、脂肪族部分が少なく、且つ高極性のヘテロ原子基を含む高分子を液滴吐出法により吐出して形成することが好ましい。そのような高分子物質の代表例としてはポリイミド又はポリベンゾイミダゾールなどが挙げられる。ポリイミドを用いる場合には、ポリイミドを含む溶液を、吐出口から第2の半導体膜223上に吐出し、200℃で30分焼成して保護膜301を形成することができる。

次に、第2の半導体膜(導電性を有する半導体膜)323を成膜する。なお、第2の半導体膜323は、実施の形態2の第2の半導体膜223と同様の材料及び作製方法により形成することができる。

次に、第2の半導体膜323の表面に形成された酸化膜を除去した後、第2の半導体膜323の一部にフォトマスク225を介してレーザ光224を照射する。この結果、図5(B)に示すように、第2の絶縁層331が形成される。ここでは、第2の半導体膜323の一部が、レーザ光のエネルギーにより酸化され、第2の絶縁層としては酸化珪素膜が形成される。

次に、図5(C)に示すように、第2の絶縁層331をマスクとして、第2の半導体膜323をエッチングし、第1の半導体領域332を形成する。次に、実施の形態4と同様の手法により、第2の絶縁層331をマスクとして用いて第1の半導体膜222をエッチングして、第2の半導体領域233を形成する。この後、第2の絶縁層331を除去する。

次に、図5(D)に示すように、第2の導電層341を、導電性材料を用いて形成する。第2の導電層341としては、実施の形態4で示した第1の導電層202に示した材料及び方法を適宜用いる。ここでは、スパッタリング法によりモリブデン膜、アルミニウム膜、及びモリブデン膜の積層構造で形成される第2の導電層341を成膜する。

次に、第2の導電層341上に感光性材料342を吐出又は塗布したのち、乾燥させる。感光性材料は、紫外光から赤外光に感光する材料ネガ型感光性材料又はポジ型感光性材料を用いる。

感光性材料としては、エポキシ樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の感光性を示す樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、ポリイミドなどの感光性を示す有機材料等を用いることができる。また、代表的なポジ型感光性材料として、ノボラック樹脂と感光剤であるナフトキノンジアジド化合物を有する感光性材料が挙げられ、代表的なネガ型感光性材料として、ベース樹脂、ジフェニルシランジオール及び酸発生剤などを有する感光性材料が挙げられる。本実施の形態では、ネガ型感光性材料を用いる。

次に、感光性材料342にレーザビーム直接描画装置を用いてレーザ光343を照射し露光した後、現像する。この結果、図5(E)に示すような、マスク351を形成する。

次に、図5(F)に示すように、マスク351を用いて、第2の導電層をエッチングしてソース電極及びドレイン電極として機能する第3の導電層352を形成する。また、マスク351を用いて第1の半導体領域332をエッチングしてソース領域及びドレイン領域として機能する第3の半導体領域353を形成する。この工程により、保護膜301が露出される。

なお、ソース電極及びドレイン電極として機能する第3の導電層352の形成方法は、本実施の形態に限られず実施の形態4に示される第2の導電層241、242の形成工程を用いても良い。また、本実施の形態のソース電極及びドレイン電極として機能する第3の導電層352の形成工程を、実施の形態4の第2の導電層241、242に適用しても良い。

この後、実施の形態4と同様に、第3の導電層352上に、パッシベーション膜を成膜することが好ましい。

以上の工程により、所望の形状の半導体領域を有するチャネル保護型TFTを作製することができる。また、ばらつきが少なく、且つ高集積化された半導体装置を作製することが可能である。

(実施の形態6)

本実施の形態においては、トップゲートTFTの中でも順スタガ型TFTの作製方法について、図6を用いて説明する。

図6(A)に示すように、基板201上に第1の導電層411、412を形成する。この材料及び作製方法は、実施の形態4の第1の導電層202と同様のものを適宜用いることができる。

次に、第1の導電層上に導電性を有する第1の半導体膜413を成膜する。第1の半導体膜413は、実施の形態4に示される第2の半導体膜223と同様の材料及び作製方法により作製することができる。

次に、第1の半導体膜413の表面に形成された酸化膜を除去した後、第1の半導体膜413の一部にフォトマスク225を介してレーザ光224を照射して、図6(B)に示すような第1のマスクとして機能する第1の絶縁層421、422を形成する。

次に、第1の絶縁層421、422をマスクとして用いて第1の半導体膜をエッチングして、図6(C)に示すような第1の半導体領域423、424を形成する。なお、第1の半導体領域はソース領域及びドレイン領域として機能する。次に、第2の半導体膜431を成膜する。第2の半導体膜431は、実施の形態4に示される第1の半導体膜222と同様の材料及び手法を適宜用いて作製することが可能である。

次に、第2の半導体膜431の一部にレーザ光432を照射して、図6(D)に示すような、第2のマスクとして機能する第2の絶縁層441を形成する。

次に、TMAH(テトラメチルアンモニウムハイドロオキサイド)を用いて、第2の半導体膜の露出部をエッチングして、図6(E)に示すように第2の半導体領域451を形成する。第2の半導体領域451は、チャネル領域として機能する。

次に、第2の絶縁層441上に、ゲート電極として機能する第2の導電層452を形成する。第2の導電層452は、実施の形態4の第1の導電層202と同様の材料及び手法を用いて形成する。また、第2の絶縁層441はゲート絶縁膜として機能する。なお、第2の絶縁層441を除去した後、新たに実施の形態4の第1の絶縁層221と同様の手法及び材料を適宜用いて、ゲート絶縁膜として機能する絶縁層を形成しても良い。

以上の工程により、所望の形状の半導体領域を有するチャネル順スタガ型TFTを作製することができる。また、ばらつきが少なく、且つ高集積化された半導体装置を作製することが可能である。

(実施の形態7)

本実施の形態ではトップゲートTFTの中でもコプレナー型TFTの作製方法について、図7を用いて説明する。

図7(A)に示すように、基板201上に第1の絶縁層501を成膜する。第1の絶縁層501は、基板からの不純物が後に形成される半導体領域に拡散するのを防止するためのブロッキング膜として機能する。このため、第1の絶縁層501としては、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などで形成する。第1の絶縁層501は単層膜または2層以上積層させた構造で形成する。

次に、第1の絶縁層501上に半導体膜502を形成する。次に、半導体膜502の表面に形成された酸化膜を除去した後、半導体膜502の所定の領域に、実施の形態4と同様に、フォトマスク225を介してレーザ光224を照射して、図7(B)に示すような第2の絶縁層511を形成する。

次に、図7(C)に示すように、第2の絶縁層511をマスクとして、TMAHを用いて半導体膜502をエッチングして、半導体領域512を形成する。

次に、図7(D)に示すように、第3の絶縁層521を除去する。次に、半導体領域512及び第1の絶縁層501上にゲート絶縁膜として機能する第3の絶縁層521を成膜する。第2の絶縁層531としては、実施の形態4に示した第1の絶縁層221と同様の材料及び作製方法を用いて形成することができる。

次に、第1の導電層522を形成する。第1の導電層522としては、実施の形態4に示す第1の導電層202と同様の材料及び手法を用いて形成する。なお、第1の導電層522は、ゲート電極として機能する。

次に、図7(E)に示すように、第1の導電層522をマスクとして半導体領域512に不純物を添加する。次に、水素を含む絶縁膜を成膜した後、400〜550度に加熱して半導体領域に添加された不純物元素の活性化し、また半導体領域の水素化を行って、不純物領域(ソース領域及びドレイン領域)541、542を形成する。また、第1の導電層522に覆われる半導体領域は、チャネル領域543として機能する。なお、活性化又は水素化の工程として、加熱処理の代わりに、GRTA法、LRTA法、レーザー・アニール法を用いることもできる。

なお、本実施の形態では、シングルゲート電極構造のTFTを示したが、これに限らずマルチゲート電極構造のものでもよい。また、セルフアライン構造のTFTを示したが、これに限らず低濃度ドレイン(LDD:Lightly Doped Drain)構造若しくはGOLD(Gate Overlapped LDD)構造のTFTを用いることができる。LDD構造は、チャネル領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に低濃度に不純物元素を添加した領域を設けたものであり、この領域をLDD領域と呼んでいる。この構造のTFTは、オフ電流値を低減することができる。GOLD構造は、ゲート絶縁膜を介してLDD領域をゲート電極と重ねて配置させた構造であり、ドレイン近傍の電解を緩和してホットキャリア注入による劣化を防ぐ効果がある。

次に、基板上に第4の絶縁層544を形成する。第4の絶縁層の材料としては、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシリカガラスに代表されるシロキサンポリマー系材料を出発材料として形成された珪素、酸素、水素からなる化合物のうちSi−O−Si結合を含む無機シロキサンポリマー、又はアルキルシロキサンポリマー、アルキルシルセスキオキサンポリマー、水素化シルセスキオキサンポリマー、水素化アルキルシルセスキオキサンポリマーに代表される珪素に結合される水素がメチルやフェニルのような有機基によって置換された有機シロキサンポリマーの絶縁材料を用いることができる。形成方法としては、CVD法、塗布法、印刷法等公知の手法を用いて形成する。なお、塗布法で形成することにより、第4の絶縁層の表面を平坦化することが可能であり、後の画素電極の形成に適している。ここでは、塗布法により第4の絶縁層544を形成する。

次に、液滴吐出法によりマスクパターンを形成し、該マスクパターンを用いて第4の絶縁層544及び第3の絶縁層521の一部を除去して、半導体領域の不純物領域541、542の一部を露出して、開口部を形成する。次に、開口部に実施の形態4の第1の導電層202と同様の手法を適宜用いて、第2の導電層545、546を形成する。第2の導電層545、546はソース電極及びドレイン電極として機能する。

以上の工程により、所望の形状の半導体領域を有するコプレナー型TFTを作製することができる。また、ばらつきが少なく、且つ高集積化された半導体装置を作製することが可能である。

(実施の形態8)

ここでは、保護材を用いて半導体膜の一部を酸化する工程を図24を用いて説明する。

図24(A)は、第1の絶縁層102、半導体膜103が形成された基板101の一部に、保護材として粘着テープ(以下、マスクキングテープと示す。)を貼付けた時の斜視図である。マスキングテープの代表例としては、耐アルカリ又は耐酸性を有する有機材料のテープ又はシートであり、代表的にはポリエステル、ポリエチレンテレフタレート等の材質に粘着剤が設けられたものを用いればよい。

半導体膜の表面に形成された第2の絶縁膜を除去した後、半導体膜103及び基板101の一部をマスクキングテープ601で覆い、基板101を、酸化力を有する酸化剤に浸漬する。この結果、図24(B)に示すように、半導体膜103の表面に第2の絶縁層631が形成される。酸化力を有する酸化剤の代表例としては、過酸化水素水(H2O2)、硝酸(HNO3)、オゾン(O3)等が挙げられる。

次に、マスキングテープをはがした後、第2の絶縁層631をマスクとして半導体膜103をエッチングすることで、半導体領域632が形成される。

マスキングテープを用いることで、広い領域においてマスクとして機能する絶縁層を一度の処理で形成することが可能であるため、量産性を向上させることが可能である。

なお、本実施の形態は実施の形態2に沿って、半導体膜表面に形成される第2の絶縁層を除去した後、マスクとして機能する第3の絶縁層を形成したが、実施の形態1に示すように、第2の絶縁層を除去せずにマスクとして機能する第3の絶縁層を形成した後、第2の絶縁層の一部を除去してもよい。

次に、アクティブマトリクス基板及びそれを有する表示パネルの作製方法について図8〜図11を用いて説明する。本実施例では、表示パネルの代表例の一つとして、液晶表示パネルを用いて説明する。図11は、アクティブマトリクス基板の上面図であり、接続端子部のA−B及び画素部のC−Dに対応する断面構造を図8〜10に模式的に示す。

図8(A)に示すように、基板801表面上に第1の導電層802、803を形成する。第1の導電層は、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Si、Ge、Zr、Ba等の金属粒子と有機樹脂で形成される組成物を吐出し、焼成して形成する。第1の導電層802は後のゲート線として機能し、第1の導電層803は後のゲート電極として機能する。ここでは、基板801として、旭硝子社製AN100ガラス基板を用いる。また、液滴吐出法を用いてAg(銀)粒子が分散された組成物を吐出し、加熱して第1の導電層802、803を形成する。

次に、CVD法によりゲート絶縁膜804を成膜する。ゲート絶縁膜804としては、膜厚50nmの窒化珪素膜を成膜した後、50nmの酸化窒化珪素膜(SiON(O>N))を成膜する。

次に、第1の半導体膜805及びn型を呈する第2の半導体膜806を成膜する。第1の半導体膜805としては、膜厚150nmのアモルファスシリコン膜を成膜する。次に、アモルファスシリコン膜の表面の酸化膜を除去した後、第2の半導体膜806として、同様の手法により膜厚50nmのセミアモルファスシリコン膜を成膜する。ここでは、CVD法により第1の半導体膜及び第2の半導体膜を成膜する。

次に、第2の半導体膜の表面の酸化膜を除去した後、第2の半導体膜806の一部にフォトマスク808を介してレーザ光807を照射して、図8(B)に示すように、第2の半導体膜の表面に酸化珪素膜811を形成する。

次に、図8(C)に示すように、酸化珪素膜811をマスクとして用いて第2の半導体膜806をエッチングして第1の半導体領域812を形成する。また、同様に第1の半導体膜をエッチングして、第2の半導体領域813を形成する。ここでは、第1の半導体膜及び第2の半導体膜を、流量比がCF4:O2=10:9の混合ガスを用いてエッチングする。この後、酸化珪素膜811を剥離する。

次に、図9(A)に示すように、第2の導電層821、822を液滴吐出法で形成する。第2の導電層821、822は、それぞれ後のソース線(ソース電極)と、ドレイン電極として機能する。ここでは、第2の導電層821、822は、Ag(銀)粒子が分散された組成物を吐出し、200度30分加熱して形成する。

なお、上記工程に代えて、導電層を液滴吐出法により第1の半導体領域上に吐出し焼成する。次に、感光性材料を導電層上に塗布又は吐出し焼成し、レーザビーム直接描画装置から照射されたレーザ光を用いて感光性材料の一部を露光し現像してマスクを形成し、該マスクを用いて第2の導電層821、822を形成してもよい。この場合、微細な構造のマスクを形成することが可能であり、ソース線(ソース電極)と、ドレイン電極との距離を狭めることが可能である。

次に、第2の導電層821、822をマスクとして、第1の半導体領域をエッチングして第3の半導体領域を形成する。第3の半導体領域823、824は、ソース領域及びドレイン領域、またはコンタクト層として機能する。このとき、第2の半導体領域もエッチングされる。エッチングされた第2の半導体領域である第4の半導体領域825は、チャネル領域として機能する。

次に、図9(B)に示すように、第2の導電層822上に画素電極として機能する第3の導電層831を形成する。第3の導電層831の材料の代表例としては、透光性を有する導電膜、又は反射性を有する導電膜が挙げられる。透光性を有する導電膜の材料としては、酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、ガリウムを添加した酸化亜鉛(GZO)、酸化珪素を含む酸化インジウムスズ等が挙げられる。また、反射性を有する導電膜の材料としては、アルミニウム(Al)、チタン(Ti)、銀(Ag)、タンタル(Ta)などの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含む金属材料、若しくは該金属の窒化物である窒化アルミニウム、窒化チタン、窒化タンタルなどが挙げられる。また、第3の導電層831の形成方法としては、スパッタリング法、蒸着法、CVD法、塗布法等を適宜用いる。ここでは、第3の導電層831として、液滴吐出法により膜厚110nmの酸化珪素を含む酸化インジウムスズ(ITO)を成膜する。

以上の工程により、アクティブマトリクス基板を形成することができる。なお、図9(B)の断面構造A−B及びC−Dに対応する上面構造を図11に示すので同時に参照する。

次に、図9(B)に示すように、保護膜832を成膜する。保護膜832としては、シリコンターゲット、及びスパッタリングガスとしてアルゴン並びに酸素(流量比Ar:O2=1:1)を用いたスパッタリング法により、膜厚100nmの酸化珪素膜を形成した後、スパッタリングガスとしてアルゴン並びに窒素(流量比Ar:N2=1:1)を用いたスパッタリング法により、膜厚100nmの窒化珪素膜を成膜する。

次に、保護膜832を覆うように印刷法やスピンコート法により、絶縁膜を成膜し、ラビングを行って配向膜833を形成する。なお、配向膜833は、斜方蒸着法により形成することもできる。

次に、図10(A)に示すように、配向膜883及び第2の画素電極(対向電極)882が設けられた対向基板881において、画素部の周辺の領域に液滴吐出法により閉ループ状のシール材871を形成する。シール材871には、フィラーが混入されていてもよく、さらに、対向基板881にはカラーフィルタや遮蔽膜(ブラックマトリクス)などが形成されていても良い。

次に、ディスペンサ式(滴下式)により、シール材871で形成された閉ループ内側に、液晶材料を滴下したのち、真空中で、配向膜883及び第2の画素電極(対向電極)882が設けられた対向基板881とアクティブマトリクス基板とを貼り合わせ、紫外線硬化を行って、液晶材料が充填された液晶層884を形成する。なお、液晶層884を形成する方法として、ディスペンサ式(滴下式)の代わりに、対向基板を貼り合わせてから毛細管現象を用いて液晶材料を注入するディップ式(汲み上げ式)を用いることができる。

次に、ゲート線、ソース線の接続端子部における配向膜833、保護膜832、ゲート絶縁膜804の一部を除去して、ゲート線、ソース線の接続端子を露出する。

次に、図10(B)に示すように、接続導電層885を介して配線基板、代表的にはFPC(Flexible Printed Circuit)、(ゲート線として機能する第3の導電層に接続される配線基板886)を貼り付ける。さらに、配線基板と接続端子部との接続部を封止樹脂で封止することが好ましい。この構造により、断面部からの水分が画素部に侵入し、劣化することを防ぐことができる。

以上の工程により液晶表示パネルを作製することができる。なお、静電破壊防止のための保護回路、代表的にはダイオードなどを、接続端子とソース線(ゲート線)の間または画素部に設けてもよい。この場合、上記したTFTと同様の工程で作製し、画素部のゲート配線層とダイオードのドレイン又はソース配線層とを接続することにより、静電破壊を防止することができる。

なお、実施の形態1乃至実施の形態8のいずれをも本実施例に適用することができる。

図12(A)は、TN(Twisted Nematic)モード、IPS(In−Plane−Switching)モード、MVA(Multi−domain Vertical Alignment)モード、ASM(Axially Symmetric aligned Micro−cell)モード、OCB(Optical Compensated Bend)モード等であり、かつ白色ライト及びカラーフィルタを用いてカラー表示をする液晶モジュールの断面図を示す。

図12(A)に示すように、アクティブマトリクス基板1601と対向基板1602とが、シール材1600により固着され、それらの間には画素部1603と液晶層1604とが設けられ表示領域を形成している。

着色層1605は、カラー表示を行う場合に必要であり、RGB方式の場合は、赤、緑、青の各色に対応した着色層が各画素に対応して設けられている。アクティブマトリクス基板1601と対向基板1602との外側には、偏光板1606、1607が配設されている。また、偏光板1606の表面には、保護膜1616が形成されており、外部からの衝撃を緩和している。

アクティブマトリクス基板1601に設けられた接続端子1608には、FPC1609を介して配線基板1610が接続されている。配線基板1610には、画素駆動回路(ICチップ、ドライバIC等)、コントロール回路や電源回路などの外部回路1612が組み込まれている。

冷陰極管1613、反射板1614、及び光学フィルム1615、インバータ(図示しない。)はバックライトユニットであり、これらが光源となって液晶表示パネルへ光を投射する。液晶パネル、光源、配線基板、FPC等は、ベゼル1617で保持及び保護されている。

図12(B)は、フィールドシーケンシャルモードのように、カラーフィルタを用いず、R(赤)、G(緑)、B(青)の光を発する冷陰極管またはダイオードを用い、且つ時間分割により画像を合成しカラー表示を行うことが可能な液晶モジュールの断面図である。図12(A)と比較して、カラーフィルタを有さない。また、ここでは、R(赤)、G(緑)、B(青)それぞれに発光する冷陰極管1621〜1623が反射板1614内に設けられている。また、これらの冷陰極管の発光を制御するコントローラ(図示しない。)が設けられている。さらに、液晶層1624は、強誘電性液晶が充填され、高速動作が可能であるため、時間分割を用いて画像を合成することが可能である。

なお、OCBモードのような液晶配向を用いて時間分割により画像を合成しても良い。

本実施例では、表示パネルの代表例の一つである発光表示パネルの作製方法について図13〜図15を用いて説明する。画素部の上面構造を図15に示し、図13及び図14は、図15の画素部のA−B(スイッチング用TFT)、及びC−D(駆動用TFT)に対応する断面構造を模式的に示したものである。

図13(A)に示すように、基板901上に第1の絶縁層902を膜厚100〜1000nmで形成する。ここでは、第1の絶縁層として、プラズマCVD法を用いた膜厚100nmの窒化酸化シリコン膜と減圧熱CVD法を用いた膜厚50nmの酸化窒化シリコン膜を積層させて形成する。

次に、非晶質半導体膜903を膜厚10〜100nmで形成する。ここでは減圧熱CVD法を用いて膜厚50nmの非晶質シリコン膜を形成する。次に、非晶質半導体膜903の表面に形成された酸化膜を除去した後、非晶質半導体膜の一部にフォトマスク905を介してレーザ光904を照射して図13(B)に示すような酸化珪素膜911、912を形成する。このとき、レーザ光が照射された領域において、非晶質半導体膜の一部が溶融した後、冷却され結晶化される。このとき、結晶化された半導体領域を913、914と示し、結晶化された半導体領域の周囲に残存する非晶質の半導体領域を915と示す。

次に、酸化珪素膜911、912をマスクとして、非晶質の半導体領域915をエッチングして、図13(C)に示すような結晶性を有する半導体領域921、922を形成する。次に、ゲート絶縁膜として機能する第2の絶縁層923を形成する。ここでは、CVD法により酸化珪素膜を成膜する。

次いで、TFTのチャネル領域となる領域にp型またはn型の不純物元素を低濃度に添加するチャネルドープ工程を全面または選択的に行う。このチャネルドープ工程は、TFTしきい値電圧を制御するための工程である。なお、ここではジボラン(B2H6)を質量分離しないでプラズマ励起したイオンドープ法でボロンを添加する。なお、質量分離を行うイオンインプランテーション法を用いてもよい。

次に、ゲート電極として機能する第1の導電層924〜926、および容量配線として機能する第1の導電層927を形成する。ここでは、液滴吐出法によりAgペーストと吐出し、レーザ光を照射して焼成し、第1の導電層924〜927を形成する。

次いで、第1の導電層924〜927をマスクとして、自己整合的にリンを半導体領域に添加して、高濃度不純物領域930〜934を形成する。高濃度不純物領域のリンの濃度が1×1020〜1×1021/cm3(代表的には2×1020〜5×1020/cm3)となるように調整する。なお、結晶性を有する半導体領域921、922のうち、第1の導電層924〜927と重なる領域はチャネル領域となる。

次いで、第1の導電層924〜927を覆う第3の絶縁層935を形成する。ここでは、水素を含む絶縁膜を成膜する。この後、半導体領域に添加された不純物元素の活性化および半導体領域の水素化を行う。水素を含む絶縁膜は、スパッタリング法により得られる窒化酸化珪素膜(SiNO膜)を用いる。

次いで、半導体領域に達する開口部を形成した後、第2の導電層941〜944を形成する。第2の導電層941はソース線として機能し、第2の導電層942は第1の接続配線として機能し、第2の導電層943は電源線及び容量配線として機能し、第2の導電層944は第2の接続配線として機能する。本実施例ではモリブデン膜と、アルミニウムーシリコン合金膜と、モリブデン膜をスパッタ法で連続して形成した3層構造の積層膜を成膜した後、所望の形状にエッチングして第3の導電層を形成する。

次に、図14(A)に示すように、第4の絶縁層951を形成する。第4の絶縁層としては、平坦化が可能な絶縁層が好ましい。平坦化が可能な絶縁層としては、実施の形態7で示される第4の絶縁層544と同様の材料及び手法を適宜用いることができる。ここではアクリル樹脂を成膜する。なお、第4の絶縁層として、黒色顔料、色素などの可視光を吸収する材料を溶解又は分散させてなる有機材料を用いることで、後に形成される発光素子の迷光の吸収が第4の絶縁層に吸収され、各画素のコントラスト向上が可能である。

次に、第4の絶縁層に公知のフォトリソグラフィー及びエッチングにより開口部を設けると共に、第2の導電層(第2の接続配線)944の一部を露出する。次に、第3の導電層952を形成する。第3の導電層は、第1の画素電極として機能する。第3の導電層952としては、反射導電膜と透光性導電膜を積層して成膜する。ここでは、1〜20%のニッケルを含むアルミニウム膜と酸化珪素を有するITOをスパッタリング法で積層する。なお、1〜20%のニッケルを含むアルミニウムは、酸化物であるITOと接しても電食しないため好ましい。この後、反射導電膜と透光性導電膜の一部をエッチングして、第3の導電層952を形成する。

なお、図14(A)の断面構造A−B及びC−Dに対応する上面構造を図15に示すので同時に参照する。

次に、第3の導電層952の端部を覆って、隔壁(障壁、土手などとも呼ばれる)となる第5の絶縁層961を形成する。第5の絶縁層は、感光性または非感光性の有機材料(ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジストまたはベンゾシクロブテン)、またはSOG膜(例えば、アルキル基を含むSiOx膜)を膜厚0.8μm〜1μmの範囲で用いる。第5の絶縁層として、感光性の材料を用いて形成すると、その側面は曲率半径が連続的に変化する形状となり、上層の薄膜が段切れせずに形成されるため好ましい。

また、第5の絶縁層として、上記有機材料に、色素、黒色顔料等の可視光を吸収する材料を溶解又は分散して、遮光性を有する絶縁物としてもよい。この場合、第5の絶縁層は、ブラックマトリックスとして機能するため、後に形成される発光素子からの迷光を吸収することができる。この結果、各画素のコントラストが向上する。さらには、第4の絶縁層951も遮光性を有する絶縁物で設けることによって、第5の絶縁層961とのトータルで遮光の効果を得ることができる。

次に、蒸着法、塗布法、液滴吐出法などにより、第3の導電層952表面及び第5の絶縁層961の端部上に発光物質を含む層962を形成する。この後、発光物質を含む層962上に、第2の画素電極として機能する第4の導電層963を形成する。ここでは、酸化珪素を含むITOをスパッタリング法により成膜する。この結果、第3の導電層、発光物質を含む層、及び第4の導電層により発光素子を形成することができる。発光素子を構成する導電層及び、発光物質を含む層の各材料は適宜選択し、各膜厚も調整する。

なお、発光物質を含む層962を形成する前に、大気圧中で200℃の熱処理を行い第5の絶縁層961中若しくはその表面に吸着している水分を除去する。また、減圧下で200〜400℃、好ましくは250〜350℃に熱処理を行い、そのまま大気に晒さずに発光物質を含む層962を真空蒸着法や、減圧下の液滴吐出法で形成することが好ましい。

上記のような材料で形成した発光素子は、順方向にバイアスすることで発光する。発光素子を用いて形成する表示装置の画素は、単純マトリクス方式、若しくはアクティブマトリクス方式で駆動することができる。いずれにしても、個々の画素は、ある特定のタイミングで順方向バイアスを印加して発光させることとなるが、ある一定期間は非発光状態となっている。この非発光時間に逆方向のバイアスを印加することで発光素子の信頼性を向上させることができる。発光素子では、一定駆動条件下で発光強度が低下する劣化や、画素内で非発光領域が拡大して見かけ上輝度が低下する劣化モードがあるが、順方向及び逆方向にバイアスを印加する交流的な駆動を行うことで、劣化の進行を遅くすることができ、発光装置の信頼性を向上させることができる。

次に、発光素子を覆って、水分の侵入を防ぐ透光性保護層964を形成する。透光性保護層964としては、スパッタ法またはCVD法により得られる窒化珪素膜、酸化珪素膜、酸化窒化珪素膜(SiNO膜(組成比N>O)またはSiON膜(組成比N<O))、炭素を主成分とする薄膜(例えばDLC膜、CN膜)などを用いることができる。

以上の工程により、発光表示パネルを作製することができる。なお、静電破壊防止のための保護回路、代表的にはダイオードなどを、接続端子とソース配線層(ゲート配線層)の間または画素部に設けてもよい。この場合、上記したTFTと同様の工程で作製し、画素部のゲート配線層とダイオードのドレイン配線層又はソース配線層とを接続することにより、静電破壊を防止することができる。

上記実施例において適用可能な発光素子の形態を、図16を用いて説明する。

図16(A)は第1の画素電極11を透光性の酸化物導電性材料で形成した例であり、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成している。その上に正孔注入層(HIL)若しくは正孔輸送層(HTL)41、発光層(EM)42、電子輸送層(ETL)若しくは電子注入層(EIL)43を積層した発光物質を含む層16を設けている。第2の画素電極17は、LiFやMgAgなどアルカリ金属又はアルカリ土類金属を含む第1の電極層33とアルミニウムなどの金属材料で形成する第2の電極層34で形成している。この構造の画素は、図中に矢印で示したように第1の画素電極11側から光を放射することが可能となる。

図16(B)は第2の画素電極17側から光を放射する例を示し、第1の画素電極11はアルミニウム、チタンなどの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含む金属材料で形成する第1の電極層35と、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成する第2の電極層32で形成している。その上に正孔注入層若しくは正孔輸送層41、発光層42、電子輸送層若しくは電子注入層43を積層した発光物質を含む層16を設けている。第2の画素電極17は、LiFやCaF2などのアルカリ金属又はアルカリ土類金属を含む第3の電極層33とアルミニウムなどの金属材料で形成する第4の電極層34で形成するが、いずれの層も100nm以下の厚さとして光を透過可能な状態としておくことで、第2の画素電極17側から光を放射することが可能となる。

図16(E)は、両方向、即ち第1の電極側及び第2の電極側から光を放射する例を示し、第1の画素電極11に、透光性を有し且つ仕事関数の大きい導電膜を用い、第2の画素電極17に、透光性を有し且つ仕事関数の小さい導電膜を用いる。代表的には、第1の画素電極11を、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成し、第2の画素電極17を、それぞれ100nm以下の厚さのLiFやCaF2などのアルカリ金属又はアルカリ土類金属を含む第3の電極層33とアルミニウムなどの金属材料で形成する第4の電極層34で形成すればよい。また、第1の画素電極11上に、正孔注入層若しくは正孔輸送層41、発光層42、電子輸送層若しくは電子注入層43を積層した発光物質を含む層16を設けている。

図16(C)は第1の画素電極11側から光を放射する例を示し、かつ、発光物質を含む層を電子輸送層若しくは電子注入層43、発光層42、正孔注入層若しくは正孔輸送層41の順に積層した構成を示している。第2の画素電極17は、発光物質を含む層16側から酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成する第2の電極層32、アルミニウム、チタンなどの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含む金属材料で形成する第1の電極層35で形成している。第1の画素電極11は、LiFやCaF2などのアルカリ金属又はアルカリ土類金属を含む第3の電極層33とアルミニウムなどの金属材料で形成する第4の電極層34で形成するが、いずれの層も100nm以下の厚さとして光を透過可能な状態としておくことで、第1の画素電極11から光を放射することが可能となる。

図16(D)は第2の画素電極17側から光を放射する例を示し、かつ、発光物質を含む層を電子輸送層若しくは電子注入層43、発光層42、正孔注入層若しくは正孔輸送層41の順に積層した構成を示している。第1の画素電極11は図16(A)の第2の画素電極17と同様な構成とし、膜厚は発光物質を含む層で発光した光を反射可能な程度に厚く形成している。第2の画素電極17は、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で構成している。この構造において、正孔注入層若しくは正孔輸送層41を無機物である金属酸化物(代表的には酸化モリブデン若しくは酸化バナジウム)で形成することにより、第2の画素電極17を形成する際に導入される酸素が供給されて正孔注入性が向上し、駆動電圧を低下させることができる。

図16(F)は、両方向、即ち第1の画素電極及び第2の画素電極から光を放射する例を示し、第1の画素電極11に、透光性を有し且つ仕事関数の小さい導電膜を用い、第2の画素電極17に、透光性を有し且つ仕事関数の大きい導電膜を用いる。代表的には、第1の画素電極11を、それぞれ100nm以下の厚さのLiFやCaF2などのアルカリ金属又はアルカリ土類金属を含む第3の電極層33とアルミニウムなどの金属材料で形成する第4の電極層34で形成し、第2の画素電極17を、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成すればよい。また、第1の画素電極11上に、発光物質を含む層を電子輸送層若しくは電子注入層43、発光層42、正孔注入層若しくは正孔輸送層41の順に積層した構成を示している。

上記実施例で示す発光表示パネルの画素回路、及びその動作構成について、図17を用いて説明する。発光表示パネルの動作構成は、ビデオ信号がデジタルの表示装置において、画素に入力されるビデオ信号が電圧で規定されるのものと、電流で規定されるものとがある。ビデオ信号が電圧によって規定されるものには、発光素子に印加される電圧が一定のもの(CVCV)と、発光素子に印加される電流が一定のもの(CVCC)とがある。また、ビデオ信号が電流によって規定されるものには、発光素子に印加される電圧が一定のもの(CCCV)と、発光素子に印加される電流が一定のもの(CCCC)とがある。本実施例では、CVCV動作をする画素を図17(A)及び(B)用いて説明する。また、CVCC動作をする画素を図17(C)〜(F)を用いて説明する。

図17(A)及び(B)に示す画素は、列方向にソース線3710及び電源線3711、行方向にゲート線3714が配置される。また、スイッチング用TFT3701、駆動用TFT3703、容量素子3702及び発光素子3705を有する。

なお、スイッチング用TFT3701及び駆動用TFT3703は、オンしているときは線形領域で動作する。また駆動用TFT3703は発光素子3705に電圧を印加するか否かを制御する役目を有する。両TFTは同じ導電型を有していると作製工程上好ましく、本実施例ではpチャネル型TFTとして形成する。また駆動用TFT3703には、エンハンスメント型だけでなく、ディプリーション型のTFTを用いてもよい。また、駆動用TFT3703のチャネル幅Wとチャネルと長Lの比(W/L)は、TFTの移動度にもよるが1〜1000であることが好ましい。W/Lが大きいほど、TFTの電気特性が向上する。

図17(A)、(B)に示す画素において、スイッチング用TFT3701は、画素に対するビデオ信号の入力を制御するものであり、スイッチング用TFT3701がオンとなると、画素内にビデオ信号が入力される。すると、容量素子3702にそのビデオ信号の電圧が保持される。

図17(A)において、電源線3711がVssで発光素子3705の対向電極がVddの場合、即ち図16(C)及び(D)の場合、発光素子の対向電極は陽極であり、駆動用TFT3703に接続される電極は陰極である。この場合、駆動用TFT3703の特性バラツキによる輝度ムラを抑制することが可能である。

図17(A)において、電源線3711がVddで発光素子3705の対向電極がVssの場合、即ち図16(A)及び(B)の場合、発光素子の対向電極は陰極であり、駆動用TFT3703に接続される電極は陽極である。この場合、Vddより電圧の高いビデオ信号をソース線3710に入力することにより、容量素子3702にそのビデオ信号の電圧が保持され、駆動用TFT3703が線形領域で動作するので、TFTのバラツキによる輝度ムラを改善することが可能である。

図17(B)に示す画素は、TFT3706とゲート線3715を追加している以外は、図17(A)に示す画素構成と同じである。

TFT3706は、新たに配置されたゲート線3715によりオン又はオフが制御される。TFT3706がオンとなると、容量素子3702に保持された電荷は放電し、駆動用TFT3703がオフとなる。つまり、TFT3706の配置により、強制的に発光素子3705に電流が流れない状態を作ることができる。そのためTFT3706を消去用TFTと呼ぶことができる。従って、図17(B)の構成は、全ての画素に対する信号の書き込みを待つことなく、書き込み期間の開始と同時又は直後に点灯期間を開始することができるため、発光のデューティ比を向上することが可能となる。

上記動作構成を有する画素において、発光素子3705の電流値は、線形領域で動作する駆動用TFT3703により決定することができる。上記構成により、TFTの特性のバラツキを抑制することが可能であり、TFT特性のバラツキに起因した発光素子の輝度ムラを改善して、画質を向上させた表示装置を提供することができる。

次に、CVCC動作をする画素を図17(C)〜(F)を用いて説明する。図17(C)に示す画素は、図17(A)に示す画素構成に、電源線3712、電流制御用TFT3704が設けられている。

図17(E)に示す画素は、駆動用TFT3703のゲート電極が、行方向に配置された電源線3712に接続される点が異なっており、それ以外は図17(C)に示す画素と同じ構成である。つまり、図17(C)、(E)に示す両画素は、同じ等価回路図を示す。しかしながら、列方向に電源線3712が配置される場合(図17(C))と、行方向に電源線3712が配置される場合(図17(E))とでは、各電源線は異なるレイヤーの導電膜で形成される。ここでは、駆動用TFT3703のゲート電極が接続される配線に注目し、これらを作製するレイヤーが異なることを表すために、図17(C)、(E)として分けて記載する。

なお、スイッチング用TFT3701は線形領域で動作し、駆動用TFT3703は飽和領域で動作する。また駆動用TFT3703は発光素子3705に流れる電流値を制御する役目を有し、電流制御用TFT3704は飽和領域で動作し発光素子3705に対する電流の供給を制御する役目を有する。

図17(D)及び(F)示す画素はそれぞれ、図17(C)及び(E)に示す画素に、消去用TFT3706とゲート線3715を追加している以外は、図17(C)及び(E)に示す画素構成と同じである。

なお、図17(A)及び(B)に示される画素でも、CVCC動作をすることは可能である。また、図17(C)〜(F)に示される動作構成を有する画素は、図17(A)及び(B)と同様に、発光素子の電流の流れる方向によって、Vdd及びVssを適宜変えることが可能である。

上記構成を有する画素は、電流制御用TFT3704が線形領域で動作するために、電流制御用TFT3704のVgsの僅かな変動は、発光素子3705の電流値に影響を及ぼさない。つまり、発光素子3705の電流値は、飽和領域で動作する駆動用TFT3703により決定することができる。上記構成により、TFTの特性バラツキに起因した発光素子の輝度ムラを改善して、画質を向上させた表示装置を提供することができる。

特に、非晶質半導体等を有する薄膜トランジスタを形成する場合、駆動用TFTの半導体膜の面積を大きくすると、TFTのバラツキの低減が可能であるため好ましい。また、図17(A)及び図17(B)に示す画素は、図17(C)〜(F)に示す画素と比較し、TFTの数が少ないため開口率を増加させることが可能である。

なお、容量素子3702を設けた構成を示したが、本発明はこれに限定されず、ビデオ信号を保持する容量がゲート容量などで、まかなうことが可能な場合には、容量素子3702を設けなくてもよい。

また、薄膜トランジスタの半導体領域が非晶質半導体膜で形成される場合は、しきい値がシフトしやすいため、しきい値を補正する回路を画素内又は画素周辺に設けることが好ましい。

このようなアクティブマトリクス型の発光装置は、画素密度が増えた場合、各画素にTFTが設けられているため低電圧駆動でき、有利であると考えられている。一方、一列毎にTFTが設けられるパッシブマトリクス型の発光装置を形成することもできる。パッシブマトリクス型の発光装置は、各画素にTFTが設けられていないため、高開口率となる。

また、本発明の表示装置において、画面表示の駆動方法は特に限定されず、例えば、点順次駆動方法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、表示装置のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であってもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

以上のように、多様な画素回路を採用することができる。

本実施例では、表示パネルの一例として、発光表示パネルの外観について、図18を用いて説明する。図18(A)は、第1の基板と、第2の基板との間を第1のシール材1205及び第2のシール材1206によって封止されたパネルの上面図であり、図18(B)は、図18(A)のA−A’における断面図に相当する。

図18(A)において、点線で示された1201はソース線駆動回路、1202は画素部、1203はゲート線駆動回路である。本実施例において、ソース線駆動回路1201、画素部1202、及びゲート線駆動回路1203は第1のシール材及び第2のシール材で封止されている領域内にある。第1のシール材としては、フィラーを含む粘性の高いエポキシ系樹脂を用いるのが好ましい。また、第2のシール材としては、粘性の低いエポキシ系樹脂を用いるのが好ましい。また、第1のシール材1205及び第2のシール材はできるだけ水分や酸素を透過しない材料であることが望ましい。

また、画素部1202と第1のシール材1205との間に、乾燥剤を設けてもよい。さらには、画素部において、ゲート線又はソース線上に乾燥剤を設けてもよい。乾燥剤としては、酸化カルシウム(CaO)や酸化バリウム(BaO)等のようなアルカリ土類金属の酸化物のような化学吸着によって水(H2O)を吸着する物質を用いるのが好ましい。但し、これに限らずゼオライトやシリカゲル等の物理吸着によって水を吸着する物質を用いても構わない。

乾燥剤をゲート線やソース線と重畳する領域に設けることで、また、透湿性の高い樹脂に乾燥剤の粒状の物質を含ませた状態で第2の基板1204に固定することで、開口率を低下せずに表示素子への水分の侵入及びそれに起因する劣化を抑制することができる。

ここで、透湿性の高い樹脂としては、アクリル樹脂、エポキシ樹脂、シロキサンポリマー、ポリイミド、PSG(リンガラス)、BPSG(ボロンリンガラス)等の有機物、無機物を用いることができる。

なお、1210は、ソース線駆動回路1201及びゲート線駆動回路1203に入力される信号を伝送するための接続配線であり、外部入力端子となるFPC(フレキシブルプリント配線)1209から、接続配線1208を介してビデオ信号やクロック信号を受け取る。

次に、断面構造について図18(B)を用いて説明する。第1の基板1200上には駆動回路及び画素部が形成されており、TFTを代表とする半導体素子を複数有している。駆動回路としてソース線駆動回路1201と画素部1202とを示す。なお、ソース線駆動回路1201はnチャネル型TFT1221とpチャネル型TFT1222とを組み合わせたCMOS回路が形成される。

本実施例においては、同一基板上にソース線駆動回路、ゲート線駆動回路、及び画素部のTFTが形成されている。このため、発光表示パネルの容積を縮小することができる。

また、画素部1202はスイッチング用TFT1211と、駆動用TFT1212とそのドレインに電気的に接続された反射性を有する導電膜からなる第1の画素電極(陽極)1213を含む複数の画素により形成される。

また、これらのTFT1211、1212、1221、1222の層間絶縁膜1220としては、無機材料(酸化シリコン、窒化シリコン、酸化窒化シリコンなど)、有機材料(ポリイミド、ポリアミド、ポリイミドアミド、ベンゾシクロブテン)、またはシロキサンポリマーを主成分とする材料を用いて形成することができる。

また、第1の画素電極(陽極)1213の両端には絶縁物(隔壁、障壁、土手などと呼ばれる)1214が形成される。絶縁物1214に形成する膜の被覆率(カバレッジ)を良好なものとするため、絶縁物1214の上端部または下端部に曲率を有する曲面が形成されるようにする。

また、第1の画素電極(陽極)1213上には、有機化合物材料の蒸着を行い、発光物質を含む層1215を選択的に形成する。また、発光物質を含む層1215上に第2の画素電極1216を形成する。

発光物質を含む層1215は実施例4に示される構造を適宜用いることができる。

こうして、第1の画素電極(陽極)1213、発光物質を含む層1215、及び第2の画素電極(陰極)1216からなる発光素子1217が形成される。発光素子1217は、第2の基板1204側に発光する。

また、発光素子1217を封止するために保護積層1218を形成する。保護積層は、第1の無機絶縁膜と、応力緩和膜と、第2の無機絶縁膜との積層からなっている。次に、保護積層1218と第2の基板1204とを、第1のシール材1205及び第2のシール材1206で接着する。なお、組成物を吐出する装置を用いて第2のシール材を滴下することが好ましい。シール材をディスペンサから滴下、又は吐出させてシール材をアクティブマトリクス基板上に塗布した後、真空中で、第2の基板とアクティブマトリクス基板とを貼り合わせ、紫外線硬化を行って封止することができる。

接続配線1208とFPC1209とは、異方性導電膜又は異方性導電樹脂1227で電気的に接続されている。さらに、各配線層と接続端子との接続部を封止樹脂で封止することが好ましい。この構造により、断面部からの水分が発光素子に侵入し、劣化することを防ぐことができる。

なお、第2の基板1204と、保護積層1218との間には、不活性ガス、例えば窒素ガスを充填した空間を有してもよい。水分や酸素の侵入の防止を高めることができる。

また、第2の基板1204に着色層を設けることができる。この場合、画素部に白色発光が可能な発光素子を設け、RGBを示す着色層を別途設けることでフルカラー表示することができる。また、画素部に青色発光が可能な発光素子を設け、色変換層などを別途設けることによってフルカラー表示することができる。さらには、各画素部、赤色、緑色、青色の発光を示す発光素子を形成し、且つ着色層を用いることもできる。このような表示モジュールは、各RBGの色純度が高く、高精細な表示が可能となる。

また、第2の基板1204表面には、偏光板及び位相差板を設けても良い。

また、第1の基板1200又は第2の基板1204の一方、若しくは両方にフィルム又は樹脂等の基板を用いて発光表示パネルを形成してもよい。このように対向基板を用いず封止すると、表示装置の軽量化、小型化、薄膜化を向上させることができる。

更には、発光表示パネルに電源回路、コントローラ等の外部回路を接続して、発光表示モジュールを形成することが可能である。

なお、実施の形態1乃至実施の形態8のいずれをも本実施例に適用することができる。

また、表示パネルとして、液晶表示パネル、発光表示パネルの例を示し、表示モジュールとして液晶表示モジュール及び発光表示モジュールの例を示したが、これに限られるものではなく、DMD(Digital Micromirror Device;デジタルマイクロミラーデバイス)、PDP(Plasma Display Panel;プラズマディスプレイパネル)、FED(Field Emission Display;フィールドエミッションディスプレイ)、電気泳動表示装置(電子ペーパー)等の表示パネル又は表示モジュールに適宜適用することができる。

本実施例では、上記実施例に示した表示パネルへの駆動回路の実装について、図19を用いて説明する。

図19(A)に示すように、画素部1401の周辺にソース線駆動回路1402、及びゲート線駆動回路1403a、1403bを実装する。図19(A)では、ソース線駆動回路1402、及びゲート線駆動回路1403a、1403b等として、公知の異方性導電接着剤、及び異方性導電フィルムを用いた実装方法、COG方式、ワイヤボンディング方法、並びに半田バンプを用いたリフロー処理等により、基板1400上にICチップ1405を実装する。ここでは、COG方式を用いる。そして、FPC(フレキシブルプリントサーキット)1406を介して、ICチップと外部回路とを接続する。

なお、ソース線駆動回路1402の一部、例えばアナログスイッチを基板上に形成し、かつその他の部分を別途ICチップで実装してもよい。

また、図19(B)に示すように、SASや結晶性半導体でTFTを形成する場合、画素部1401とゲート線駆動回路1403a、1403b等を基板上に形成し、ソース線駆動回路1402等を別途ICチップとして実装する場合がある。図19(B)において、ソース線駆動回路1402として、COG方式により、基板1400上にICチップ1405を実装する。そして、FPC1406を介して、ICチップと外部回路とを接続する。

なお、ソース線駆動回路1402の一部、例えばアナログスイッチを基板上に形成し、かつその他の部分を別途ICチップで実装してもよい。

さらに、図19(C)に示すように、COG方式に代えて、TAB方式によりソース線駆動回路1402等を実装する場合がある。そして、FPC1406を介して、ICチップと外部回路とを接続する。図19(C)において、ソース線駆動回路をTAB方式により実装しているが、ゲート線駆動回路をTAB方式により実装してもよい。

ICチップをTAB方式により実装すると、基板に対して画素部を大きく設けることができ、狭額縁化を達成することができる。

ICチップは、シリコンウェハを用いて形成するが、ICチップの代わりにガラス基板上に回路を形成したIC(以下、ドライバICと表記する)を設けてもよい。ICチップは、円形のシリコンウェハからICチップを取り出すため、母体基板形状に制約がある。一方ドライバICは、母体基板がガラスであり、形状に制約がないため、生産性を高めることができる。そのため、ドライバICの形状寸法は自由に設定することができる。例えば、ドライバICの長辺の長さを15〜80mmとして形成すると、ICチップを実装する場合と比較し、必要な数を減らすことができる。その結果、接続端子数を低減することができ、製造上の歩留まりを向上させることができる。

ドライバICは、基板上に形成された結晶質半導体を用いて形成することができ、結晶質半導体は連続発振型のレーザ光を照射することで形成するとよい。連続発振型のレーザ光を照射して得られる半導体膜は、結晶欠陥が少なく、大粒径の結晶粒を有する。その結果、このような半導体膜を有するトランジスタは、移動度や応答速度が良好となり、高速駆動が可能となり、ドライバICに好適である。

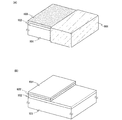

図20(A)に、本発明の一つであるIDチップの一形態を、斜視図で示す。2101は集積回路、2102はアンテナに相当し、アンテナ2102は集積回路2101に接続されている。2103は基板、2104はカバー材に相当する。集積回路2101及びアンテナ2102は、基板2103上に形成されており、カバー材2104は集積回路2101及びアンテナ2102を覆うように基板2103と重なっている。なお、カバー材2104は必ずしも用いる必要はないが、集積回路2101及びアンテナ2102をカバー材2104で覆うことで、IDチップの機械的強度を高めることができる。また、集積回路上をアンテナが覆っていても良い。即ち、集積回路の占有面積とアンテナの占有面積が、等しくともよい。

集積回路2101を上記実施の形態又は上記実施例で示す半導体素子で構成することで、ばらつきの少ないIDチップを歩留まり高く作製することが可能である。

図20(B)に、本発明の一つであるICカードの一形態を、斜視図で示す。2105は集積回路、2106はアンテナに相当し、アンテナ2106は集積回路2105に接続されている。2108はインレットシートとして機能する基板、2107、2109はカバー材に相当する。集積回路2105及びアンテナ2106はインレットシート2108上に形成されており、インレットシート2108は2つのカバー材2107、2109の間に挟まれている。なお本発明のICカードは、集積回路2105に接続された表示装置を有していても良い。

集積回路2105を、上記実施の形態又は上記実施例で示す半導体素子で構成することで、ばらつきの少ないICカードを歩留まり高く作製することが可能である。

本発明の一つである非接触型のRFID(Radio Frequency Identification)タグ、無線タグ等に代表されるIDチップの典型的なブロック図を図21に示す。図21には、認証データ等の固定データを読み出す簡単な機能を有する構成を示した。同図において、IDチップ1301は、アンテナ1302、高周波回路1303、電源回路1304、リセット回路1305、クロック発生回路1306、データ復調回路1307、データ変調回路1308、制御回路1309、不揮発性メモリ(NVMと表記)1310、ROM1311によって構成されている。

本実施例においては、電源回路1304、リセット回路1305、クロック発生回路1306、データ復調回路1307、データ変調回路1308、制御回路1309のいずれかに、上記実施の形態または上記実施例に示した半導体素子を用いることが可能である。以上より、IDチップを効率よく作製することが可能となる。

また、図21に示した回路は全てガラス基板上、もしくはフレキシブル基板上、半導体基板上に形成されている。アンテナ1302はガラス基板上、もしくはフレキシブル基板上、半導体基板上に形成されていてもよいし、基板の外部にあり、基板内部の半導体集積回路と接続されるものであってもよい。

高周波回路1303はアンテナ1302よりアナログ信号を受信し、またデータ変調回路1308より受け取ったアナログ信号をアンテナ1302から出力させる回路である。電源回路1304は受信信号から定電源を生成する回路、リセット回路1305はリセット信号を生成する回路、クロック発生回路1306はクロック信号を発生する回路、データ復調回路1307は受信した信号からデータを抽出する回路、データ変調回路1308は制御回路から受け取ったデジタル信号をもとにアンテナへ出力するアナログ信号を生成、あるいは、アンテナ特性を変化させる回路であり、以上の回路からアナログ部が構成される。

一方、制御回路1309は受信した信号から抽出したデータを受け取って、データ読み出しを行う。具体的には、NVM1310やROM1311のアドレス信号を生成して、データの読み出しを行い、読み出したデータをデータ変調回路に送る。以上の回路からデジタル部が構成されている。

実施の形態や実施例に示される半導体装置を有する電子機器として、テレビジョン装置(単にテレビ、又はテレビジョン受信機ともよぶ)、デジタルカメラ、デジタルビデオカメラ、携帯電話装置(単に携帯電話機、携帯電話ともよぶ)、PDA等の携帯情報端末、携帯型ゲーム機、コンピュータ用のモニター、コンピュータ、カーオーディオ等の音響再生装置、家庭用ゲーム機等の記録媒体を備えた画像再生装置等が挙げられる。その具体例について、図23を参照して説明する。

図23(A)に示す携帯情報端末は、本体9201、表示部9202等を含んでいる。表示部9202は、実施の形態1〜7、及び実施例1〜9で示すものを適用することができる。本発明の一である表示装置を用いることにより、高画質な表示が可能な携帯情報端末を安価に提供することができる。

図23(B)に示すデジタルビデオカメラは、表示部9701、表示部9702等を含んでいる。表示部9701は、実施の形態1〜7、及び実施例1〜9で示すものを適用することができる。本発明の一である表示装置を用いることにより、高画質な表示が可能なデジタルビデオカメラを安価に提供することができる。

図23(C)に示す携帯端末は、本体9101、表示部9102等を含んでいる。表示部9102は、実施の形態1〜7、及び実施例1〜9で示すものを適用することができる。本発明の一である表示装置を用いることにより、高画質な表示が可能な携帯端末を安価に提供することができる。

図23(D)に示す携帯型のテレビジョン装置は、本体9301、表示部9302等を含んでいる。表示部9302は、実施の形態1〜7、及び実施例1〜9で示すものを適用することができる。本発明の一である表示装置を用いることにより、高画質な表示が可能な携帯型のテレビジョン装置を安価に提供することができる。このようなテレビジョン装置は携帯電話などの携帯端末に搭載する小型のものから、持ち運びをすることができる中型のもの、また、大型のもの(例えば40インチ以上)まで、幅広く適用することができる。

図23(E)に示す携帯型のコンピュータは、本体9401、表示部9402等を含んでいる。表示部9402は、実施の形態1〜7、及び実施例1〜9で示すものを適用することができる。本発明の一である表示装置を用いることにより、高画質な表示が可能な携帯型のコンピュータを安価に提供することができる。

図23(F)に示すテレビジョン装置は、本体9501、表示部9502等を含んでいる。表示部9502は、実施の形態1〜7、及び実施例1〜9で示すものを適用することができる。本発明の一である表示装置を用いることにより、高画質な表示が可能なテレビジョン装置を安価に提供することができる。

上記に挙げた電子機器において、二次電池を用いているものは、消費電力を削減した分、電子機器の使用時間を長持ちさせることができ、二次電池を充電する手間を省くことができる。

本発明に係る半導体領域の作製工程を説明する断面図。

本発明に係る半導体領域の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する上面図。

本発明に係る液晶表示モジュールの構成を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する断面図。

本発明に係る半導体装置の作製工程を説明する上面図。

本発明に適用可能な発光素子の形態を説明する図。

本発明に適用可能な発光素子の回路を説明する図。

本発明の発光表示パネルの構成を説明する上面図及び断面図。

本発明に係る表示装置の駆動回路の実装方法を説明する上面図。

本発明の半導体装置の一例を説明する斜視図。

本発明の半導体装置の一例を説明するブロック図。

本発明に係る半導体領域の作製工程を説明する斜視図。

電子機器の一例を説明する図。

本発明に係る半導体領域の作製工程を説明する斜視図。

本発明に適用可能なマスクを説明する断面図。