JP4531194B2 - Electro-optical device and electronic apparatus - Google Patents

Electro-optical device and electronic apparatus Download PDFInfo

- Publication number

- JP4531194B2 JP4531194B2 JP2000112782A JP2000112782A JP4531194B2 JP 4531194 B2 JP4531194 B2 JP 4531194B2 JP 2000112782 A JP2000112782 A JP 2000112782A JP 2000112782 A JP2000112782 A JP 2000112782A JP 4531194 B2 JP4531194 B2 JP 4531194B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- film

- gate electrode

- gate insulating

- tft

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000012535 impurity Substances 0.000 claims description 84

- 238000007667 floating Methods 0.000 claims description 41

- 239000000463 material Substances 0.000 claims description 37

- 230000015572 biosynthetic process Effects 0.000 claims description 36

- 239000012212 insulator Substances 0.000 claims description 11

- 239000010408 film Substances 0.000 description 416

- 239000010410 layer Substances 0.000 description 92

- 239000000758 substrate Substances 0.000 description 76

- 238000000034 method Methods 0.000 description 74

- 239000004973 liquid crystal related substance Substances 0.000 description 57

- 239000011159 matrix material Substances 0.000 description 47

- 239000013078 crystal Substances 0.000 description 45

- 239000004065 semiconductor Substances 0.000 description 38

- 239000003990 capacitor Substances 0.000 description 35

- 230000008569 process Effects 0.000 description 29

- 238000007254 oxidation reaction Methods 0.000 description 28

- 230000003647 oxidation Effects 0.000 description 26

- 238000003860 storage Methods 0.000 description 25

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 21

- 239000011229 interlayer Substances 0.000 description 21

- 230000003287 optical effect Effects 0.000 description 21

- 229910052698 phosphorus Inorganic materials 0.000 description 21

- 239000011574 phosphorus Substances 0.000 description 21

- 238000012937 correction Methods 0.000 description 20

- 229910021419 crystalline silicon Inorganic materials 0.000 description 20

- 238000010438 heat treatment Methods 0.000 description 20

- 230000006870 function Effects 0.000 description 19

- 239000012298 atmosphere Substances 0.000 description 18

- 229910052581 Si3N4 Inorganic materials 0.000 description 17

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 17

- 229910052710 silicon Inorganic materials 0.000 description 17

- 239000010703 silicon Substances 0.000 description 17

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 17

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 17

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 16

- 229910052814 silicon oxide Inorganic materials 0.000 description 14

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 12

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 12

- 229910052796 boron Inorganic materials 0.000 description 12

- 238000010586 diagram Methods 0.000 description 12

- 229910052760 oxygen Inorganic materials 0.000 description 12

- 239000001301 oxygen Substances 0.000 description 12

- 238000002161 passivation Methods 0.000 description 12

- 229920005989 resin Polymers 0.000 description 12

- 239000011347 resin Substances 0.000 description 12

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 11

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 10

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 10

- 229910052782 aluminium Inorganic materials 0.000 description 10

- 239000000969 carrier Substances 0.000 description 10

- 238000002425 crystallisation Methods 0.000 description 10

- 230000008025 crystallization Effects 0.000 description 10

- 230000000694 effects Effects 0.000 description 10

- 229910052739 hydrogen Inorganic materials 0.000 description 10

- 239000001257 hydrogen Substances 0.000 description 10

- 229910021417 amorphous silicon Inorganic materials 0.000 description 9

- 238000002347 injection Methods 0.000 description 9

- 239000007924 injection Substances 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 9

- 238000005070 sampling Methods 0.000 description 9

- 239000000872 buffer Substances 0.000 description 8

- 150000001875 compounds Chemical class 0.000 description 8

- 229910052759 nickel Inorganic materials 0.000 description 8

- 230000004044 response Effects 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- 238000000137 annealing Methods 0.000 description 7

- 230000007547 defect Effects 0.000 description 7

- 230000006866 deterioration Effects 0.000 description 7

- 239000007789 gas Substances 0.000 description 7

- 229910003437 indium oxide Inorganic materials 0.000 description 7

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 7

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 7

- 238000012545 processing Methods 0.000 description 7

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 238000005516 engineering process Methods 0.000 description 6

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 6

- 238000005247 gettering Methods 0.000 description 6

- 230000003071 parasitic effect Effects 0.000 description 6

- 229920003023 plastic Polymers 0.000 description 6

- 239000004033 plastic Substances 0.000 description 6

- 125000006850 spacer group Chemical group 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- 229910052715 tantalum Inorganic materials 0.000 description 6

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 6

- 239000010409 thin film Substances 0.000 description 6

- 230000003197 catalytic effect Effects 0.000 description 5

- 238000004891 communication Methods 0.000 description 5

- 239000000945 filler Substances 0.000 description 5

- 229910052751 metal Inorganic materials 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 229910052757 nitrogen Inorganic materials 0.000 description 5

- 230000001590 oxidative effect Effects 0.000 description 5

- 230000010287 polarization Effects 0.000 description 5

- 229920001721 polyimide Polymers 0.000 description 5

- 230000001681 protective effect Effects 0.000 description 5

- 230000009467 reduction Effects 0.000 description 5

- 239000003566 sealing material Substances 0.000 description 5

- 238000000926 separation method Methods 0.000 description 5

- 239000000243 solution Substances 0.000 description 5

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- 238000005468 ion implantation Methods 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- 238000000059 patterning Methods 0.000 description 4

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 4

- 229910001887 tin oxide Inorganic materials 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- 238000004627 transmission electron microscopy Methods 0.000 description 4

- 239000012808 vapor phase Substances 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- LYCAIKOWRPUZTN-UHFFFAOYSA-N Ethylene glycol Chemical compound OCCO LYCAIKOWRPUZTN-UHFFFAOYSA-N 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- 238000001994 activation Methods 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 238000005401 electroluminescence Methods 0.000 description 3

- 230000001747 exhibiting effect Effects 0.000 description 3

- 238000002173 high-resolution transmission electron microscopy Methods 0.000 description 3

- 238000005984 hydrogenation reaction Methods 0.000 description 3

- 238000005499 laser crystallization Methods 0.000 description 3

- 239000012299 nitrogen atmosphere Substances 0.000 description 3

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- 239000010453 quartz Substances 0.000 description 3

- 239000000565 sealant Substances 0.000 description 3

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 3

- 229910001936 tantalum oxide Inorganic materials 0.000 description 3

- 238000007740 vapor deposition Methods 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- 229920002799 BoPET Polymers 0.000 description 2

- 238000004435 EPR spectroscopy Methods 0.000 description 2

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- 239000005041 Mylar™ Substances 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- 239000004983 Polymer Dispersed Liquid Crystal Substances 0.000 description 2

- 229910020286 SiOxNy Inorganic materials 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- 230000001133 acceleration Effects 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 239000010407 anodic oxide Substances 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 239000003054 catalyst Substances 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000011109 contamination Methods 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 238000002003 electron diffraction Methods 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 238000005224 laser annealing Methods 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 239000003550 marker Substances 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- 230000000737 periodic effect Effects 0.000 description 2

- 239000012071 phase Substances 0.000 description 2

- 229910000073 phosphorus hydride Inorganic materials 0.000 description 2

- 238000002294 plasma sputter deposition Methods 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 239000002985 plastic film Substances 0.000 description 2

- 229920006255 plastic film Polymers 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920006267 polyester film Polymers 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 230000008054 signal transmission Effects 0.000 description 2

- 238000009751 slip forming Methods 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 230000002269 spontaneous effect Effects 0.000 description 2

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- -1 tungsten nitride Chemical class 0.000 description 2

- IUOOGQJPAJDLFV-UHFFFAOYSA-N 2,3-dihydroxybutanedioic acid;ethane-1,2-diol Chemical compound OCCO.OC(=O)C(O)C(O)C(O)=O IUOOGQJPAJDLFV-UHFFFAOYSA-N 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910001316 Ag alloy Inorganic materials 0.000 description 1

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 1

- 229910000733 Li alloy Inorganic materials 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 229910000861 Mg alloy Inorganic materials 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910001362 Ta alloys Inorganic materials 0.000 description 1

- 229910001080 W alloy Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- QGZKDVFQNNGYKY-UHFFFAOYSA-N ammonia Natural products N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 1

- 235000011114 ammonium hydroxide Nutrition 0.000 description 1

- 238000002048 anodisation reaction Methods 0.000 description 1

- 238000007743 anodising Methods 0.000 description 1

- 230000005620 antiferroelectricity Effects 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- NGPGDYLVALNKEG-UHFFFAOYSA-N azanium;azane;2,3,4-trihydroxy-4-oxobutanoate Chemical compound [NH4+].[NH4+].[O-]C(=O)C(O)C(O)C([O-])=O NGPGDYLVALNKEG-UHFFFAOYSA-N 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 239000010406 cathode material Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910010293 ceramic material Inorganic materials 0.000 description 1

- 238000012512 characterization method Methods 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- XCJYREBRNVKWGJ-UHFFFAOYSA-N copper(II) phthalocyanine Chemical compound [Cu+2].C12=CC=CC=C2C(N=C2[N-]C(C3=CC=CC=C32)=N2)=NC1=NC([C]1C=CC=CC1=1)=NC=1N=C1[C]3C=CC=CC3=C2[N-]1 XCJYREBRNVKWGJ-UHFFFAOYSA-N 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000007850 fluorescent dye Substances 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- RBTKNAXYKSUFRK-UHFFFAOYSA-N heliogen blue Chemical compound [Cu].[N-]1C2=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=NC([N-]1)=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=N2 RBTKNAXYKSUFRK-UHFFFAOYSA-N 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 229910000041 hydrogen chloride Inorganic materials 0.000 description 1

- IXCSERBJSXMMFS-UHFFFAOYSA-N hydrogen chloride Substances Cl.Cl IXCSERBJSXMMFS-UHFFFAOYSA-N 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 239000011133 lead Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 239000001989 lithium alloy Substances 0.000 description 1

- PQXKHYXIUOZZFA-UHFFFAOYSA-M lithium fluoride Chemical compound [Li+].[F-] PQXKHYXIUOZZFA-UHFFFAOYSA-M 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 230000006386 memory function Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 239000000178 monomer Substances 0.000 description 1

- 229910000069 nitrogen hydride Inorganic materials 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000010926 purge Methods 0.000 description 1

- 230000008439 repair process Effects 0.000 description 1

- SBEQWOXEGHQIMW-UHFFFAOYSA-N silicon Chemical compound [Si].[Si] SBEQWOXEGHQIMW-UHFFFAOYSA-N 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical class [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000007790 solid phase Substances 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000000725 suspension Substances 0.000 description 1

- 238000012719 thermal polymerization Methods 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 239000011135 tin Substances 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

- 235000012431 wafers Nutrition 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Thin Film Transistor (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

【0001】

【発明の属する技術分野】

本願発明は半導体素子(半導体薄膜を用いた素子)を基板上に作り込んで形成された電気光学装置及びその電気光学装置を有する電子機器(電子デバイス)に関する。典型的には基板上に薄膜トランジスタ(以下、TFTという)を形成してなる液晶表示装置若しくはEL表示装置並びにそのような表示装置をディスプレイ(表示部)として有する電子機器に関する。

【0002】

【従来の技術】

近年、基板上にTFTを形成する技術が大幅に進歩し、アクティブマトリクス型表示装置への応用開発が進められている。特に、ポリシリコン膜を用いたTFTは、従来のアモルファスシリコン膜を用いたTFTよりも電界効果移動度(モビリティともいう)が高いので、高速動作が可能である。そのため、従来、基板外の駆動回路で行っていた画素の制御を、画素と同一の基板上に形成した駆動回路で行うことが可能となっている。

【0003】

このようなアクティブマトリクス型表示装置は、同一基板上に様々な回路や素子を作り込むことで製造コストの低減、表示装置の小型化、歩留まりの上昇、スループットの低減など、様々な利点が得られるとして注目されている。

【0004】

しかし、アクティブマトリクス型表示装置の基板上には様々な機能を有する回路や素子部が形成される。従って、回路又は素子をTFTで形成するにあたって、それぞれの回路又は素子が必要とするTFTの性能も異なってくる。例えば、シフトレジスタ回路などの駆動回路には動作速度の早いTFTが求められ、画素部のスイッチング素子にはオフ電流値(TFTがオフ動作にある時に流れるドレイン電流値)の十分に低いTFTが求められる。

【0005】

このような場合、同一構造のTFTだけでは全ての回路又は素子が求める性能を確保することが困難となり、アクティブマトリクス型表示装置の性能を向上させる上で大きな弊害となる。

【0006】

さらに、アクティブマトリクス型表示装置を電子機器の一部として用いる場合、先の画素や駆動回路以外にも様々な回路を必要とする。特に、画像情報を一時記憶させるためのメモリ部を同一基板上に形成することは、アクティブマトリクス型表示装置の用途を拡大する上で重要である。

【0007】

【発明が解決しようとする課題】

本願発明は同一基板上に画素部と駆動回路部とを有するアクティブマトリクス型の電気光学装置において、TFTで形成される回路又は素子が求める性能に応じて適切な構造のTFTを用い、動作性能及び信頼性の高い電気光学装置を提供することを課題とする。

【0008】

具体的には、同一基板上に画素部、駆動回路部及びメモリ部をそれぞれ適切な構造のTFTでもって形成した動作性能及び信頼性の高い電気光学装置を提供することを課題とする。

【0009】

そして、アクティブマトリクス型の電気光学装置にメモリ機能を付加することでその性能を向上させ、表示装置の画質を向上させることを課題とする。さらに、本願発明の電気光学装置をディスプレイとして用いた電子機器の品質を向上させることを課題とする。

【0010】

【課題を解決するための手段】

本願発明の構成は、

LDD領域の一部又は全部がゲート絶縁膜を挟んでゲート電極と重なるように形成されたnチャネル型TFTを有する駆動回路部と、

LDD領域がゲート絶縁膜を挟んでゲート電極と重ならないように形成された画素TFTを有する画素部と、

メモリトランジスタを有するメモリ部と、

を同一の絶縁体上に有することを特徴とする。

【0011】

また、他の発明の構成は、

LDD領域の一部又は全部が第2ゲート絶縁膜を挟んでゲート電極と重なるように形成されたnチャネル型TFTを有する駆動回路部と、

LDD領域が第2ゲート絶縁膜を挟んでゲート電極と重ならないように形成された画素TFTを有する画素部と、

活性層、第1ゲート絶縁膜、浮遊ゲート電極、第3ゲート絶縁膜及び制御ゲート電極を含むメモリトランジスタを有するメモリ部と、

を同一の絶縁体上に有することを特徴とする。

【0012】

また、他の発明の構成は、

LDD領域の一部又は全部が第2ゲート絶縁膜を挟んでゲート電極と重なるように形成されたnチャネル型TFTを有する駆動回路部と、

LDD領域が第2ゲート絶縁膜を挟んでゲート電極と重ならないように形成された画素TFTを有する画素部と、

活性層、第1ゲート絶縁膜、浮遊ゲート電極、第3ゲート絶縁膜及び制御ゲート電極を含むメモリトランジスタを有するメモリ部と、

を同一の絶縁体上に有し、

前記第3ゲート絶縁膜は前記nチャネル型TFTのゲート電極及び前記画素TFTのゲート電極を覆っていることを特徴とする。

【0013】

また、他の発明の構成は、

LDD領域の一部又は全部が第2ゲート絶縁膜を挟んでゲート電極と重なるように形成されたnチャネル型TFTを有する駆動回路部と、

LDD領域が第2ゲート絶縁膜を挟んでゲート電極と重ならないように形成された画素TFTを有する画素部と、

活性層、第1ゲート絶縁膜、浮遊ゲート電極、第3ゲート絶縁膜及び制御ゲート電極を含むメモリトランジスタを有するメモリ部と、

を同一の絶縁体上に有し、

前記浮遊ゲート電極、前記nチャネル型TFTのゲート電極及び前記画素TFTのゲート電極は同一材料からなり、且つ、前記第3ゲート絶縁膜に覆われていることを特徴とする。

【0014】

また、他の発明の構成は、

LDD領域の一部又は全部が第2ゲート絶縁膜を挟んでゲート電極と重なるように形成されたnチャネル型TFTを有する駆動回路部と、

LDD領域が第2ゲート絶縁膜を挟んでゲート電極と重ならないように形成された画素TFTを有する画素部と、

活性層、第1ゲート絶縁膜、浮遊ゲート電極、第3ゲート絶縁膜及び制御ゲート電極を含むメモリトランジスタを有するメモリ部と、

を同一の絶縁体上に有し、

前記第3ゲート絶縁膜は前記浮遊ゲート電極を形成する材料の酸化物であることを特徴とする。

【0015】

また、他の発明の構成は、

LDD領域の一部又は全部が第2ゲート絶縁膜を挟んでゲート電極と重なるように形成されたnチャネル型TFTを有する駆動回路部と、

LDD領域が第2ゲート絶縁膜を挟んでゲート電極と重ならないように形成された画素TFTを有する画素部と、

活性層、第1ゲート絶縁膜、浮遊ゲート電極、第3ゲート絶縁膜及び制御ゲート電極を含むメモリトランジスタを有するメモリ部と、

を同一の絶縁体上に有し、

前記浮遊ゲート電極、前記nチャネル型TFTのゲート電極及び前記画素TFTのゲート電極は同一材料からなり、且つ、前記第3ゲート絶縁膜は前記浮遊ゲート電極を形成する材料の酸化物であることを特徴とする。

【0016】

【発明の実施の形態】

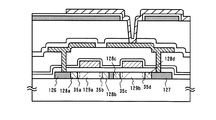

本願発明の実施形態について図1を用いて説明する。図1は同一基板上(同一の絶縁表面上もしくは同一の絶縁体上)にメモリ部、駆動回路部及び画素部を一体形成したアクティブマトリクス基板(液晶又はEL層を形成する前のTFT形成側基板)の断面図を示している。

【0017】

なお、メモリ部は不揮発性メモリ、ここではEEPROM(Electric Erasable Programmable Read Only Memory)で形成され、図1ではそのメモリセルに形成される一つのメモリトランジスタ(メモリセルトランジスタともいう)を例示する。実際には複数のメモリセルが集積化されてメモリ部を形成する。

【0018】

本願発明には集積度の高いフラッシュメモリ(フラッシュEEPROM)を用いるのが望ましい。従って、本明細書中では特に断りのない限り、不揮発性メモリとしてフラッシュメモリを扱う。また、フラッシュメモリはセクター毎にデータ消去を行う不揮発性メモリであるが、各メモリトランジスタのソース配線は共通化されているので本明細書中では共通ソース配線という。

【0019】

また、駆動回路部を形成する具体例としてCMOS回路を示す。実際には、CMOS回路を基本回路としてシフトレジスタ、レベルシフタ、ラッチ、バッファ等が形成され、それらが集積化されて駆動回路部を形成する。

【0020】

また、画素部を形成する具体例として画素TFT及び保持容量を示す。実際にはマトリクス状に配列された複数の画素のそれぞれに画素TFTと保持容量とが形成される。

【0021】

図1において、101は絶縁表面を有し耐熱性の高い基板であり、石英基板、シリコン基板、セラミックス基板もしくは金属基板を用いれば良い。どの基板を用いる場合においても、必要に応じて下地膜(好ましくは珪素(シリコン)を含む絶縁膜)を設けて絶縁表面を形成すれば良い。なお、本明細書において「珪素を含む絶縁膜」とは、具体的には酸化珪素膜、窒化珪素膜若しくは窒化酸化珪素膜(SiOxNyで示される)など珪素、酸素若しくは窒素を所定の割合で含む絶縁膜を指す。

【0022】

そして、基板101上に各半導体素子301〜304が形成される。ここで各区半導体素子301〜304のそれぞれについて図1を用いて説明を行う。

【0023】

まずメモリトランジスタ301はソース領域102、ドレイン領域103、低濃度不純物領域(LDD領域ともいう)104及びチャネル形成領域105を含む活性層、第1ゲート絶縁膜106、浮遊ゲート電極107、第3ゲート絶縁膜11、制御ゲート電極108、そして第1層間絶縁膜12を介して形成された共通ソース配線109、ビット配線(ドレイン配線)110を有して形成される。

【0024】

ソース領域102は浮遊ゲート電極107に捕獲されたキャリア(電子)を共通ソース配線109に引き抜くための領域であり消去領域とも言える。なお、図1ではチャネル形成領域105との間にLDD領域104を設けているが、形成しなくても良い。また、ドレイン領域103は電気的に孤立した浮遊ゲート電極107にキャリアを注入するための領域であり書き込み領域とも言える。さらに、ドレイン領域103はメモリトランジスタ301に記憶されたデータをビット配線110に読み出すための読み出し領域としても機能する。

【0025】

このドレイン領域103は第1ゲート絶縁膜106を介して浮遊ゲート電極107と重なるように設けられる。重なりの距離は0.1〜0.5μm(好ましくは0.1〜0.2μm)でよく、これ以上重ねてしまうと寄生容量が大きくなりすぎるので好ましくない。また、浮遊ゲート電極107にキャリアを捕獲する際、その制御は第3ゲート絶縁膜11を介して浮遊ゲート電極107上に設けられた制御ゲート電極108で行われる。

【0026】

なお、第1ゲート絶縁膜106としてはトンネル電流(ファウラノルドハイム電流)が流れる程度に薄い絶縁膜(膜厚が3〜20nm、好ましくは5〜10nm)を用いる必要があるため、活性層を酸化して得られた酸化膜(活性層が珪素ならば酸化珪素膜)を用いることが好ましい。勿論、膜厚の均一性と膜質さえ良ければ、CVD法やスパッタ法等の気相法で第1ゲート絶縁膜を形成することもできる。

【0027】

また、第3ゲート絶縁膜11としては比誘電率の高い絶縁膜を用いるのが好ましく、図1では図示されていないが酸化珪素膜/窒化珪素膜/酸化珪素膜の積層構造でなる絶縁膜を用いている。この場合、第3ゲート絶縁膜11の一部に窒化珪素膜が含まれているので、他の半導体素子302〜304に対しては外部からの可動イオンや水分の侵入を防ぐパッシベーション膜としても効果も得られる。また、浮遊ゲート電極107を酸化して得られた酸化膜(浮遊ゲート電極がタンタル膜ならば酸化タンタル膜)を用いることも可能である。

【0028】

次に、CMOS回路を形成するNチャネル型TFT302は、ソース領域112、ドレイン領域113、LDD領域114及びチャネル形成領域115を含む活性層、第2ゲート絶縁膜13、ゲート電極116、ソース配線117、ドレイン配線118を有して形成される。この時、第2ゲート絶縁膜13の膜厚は50〜150nm(好ましくは80〜120nm)とし、メモリトランジスタ301に用いた第1ゲート絶縁膜106の膜厚よりも厚いものを用いる。

【0029】

このNチャネル型TFTの特徴は、ドレイン領域113とチャネル形成領域115との間にLDD領域114が設けられ、且つ、LDD領域114が第2ゲート絶縁膜13を介してゲート電極116に重なっている点である。このような構造はホットキャリア注入による劣化を防ぐ上で非常に効果的である。但し、LDD領域とゲート電極との間で寄生容量を形成してしまうので、ソース領域112とチャネル形成領域115との間には設けない方が好ましい。

【0030】

また、この時LDD領域114の長さは0.1〜2μm(好ましくは0.3〜0.5μm)にすれば良い。長すぎては寄生容量を大きくしてしまい、短すぎてはホットキャリア注入による劣化を防止する効果が弱くなってしまう。

【0031】

次に、CMOS回路を形成するPチャネル型TFT303は、ソース領域120、ドレイン領域121及びチャネル形成領域122を含む活性層、第2ゲート絶縁膜13、ゲート電極123、ソース配線124、ドレイン配線118を有して形成される。この時、第2ゲート絶縁膜はNチャネル型TFT302と同一の絶縁膜を用い、ドレイン配線はNチャネル型TFT302と共通である。

【0032】

次に、画素部を形成する画素TFT304は、ソース領域126、ドレイン領域127、LDD領域128a〜128d、チャネル形成領域129a、129b及び不純物領域130を含む活性層、第2ゲート絶縁膜13、ゲート電極131a、131b、ソース配線132、ドレイン配線133を有して形成される。

【0033】

この時、画素TFT304においては、LDD領域128a〜128dは、第2ゲート絶縁膜13を介してゲート電極131a、131bと重ならないように設けることが好ましい。なお、チャネル形成領域とLDD領域との間にオフセット領域(チャネル形成領域と同一組成の半導体層でなり、ゲート電圧が印加されない領域)を設けることはさらに好ましい。

【0034】

前述のNチャネル型TFT302に用いた構造は確かにホットキャリア対策として効果があるが、その反面、オフ電流値(TFTがオフ動作にある時に流れるドレイン電流値)が大きくなってしまうという現象が見られる。この現象は駆動回路(サンプリング回路は除く)ではさほど問題にならないが、画素TFTでは致命的な欠点となってしまう。そのため、本願発明では図1のような構造の画素TFTを用いてオフ電流値を低減している。また、不純物領域130もオフ電流値を低減する上で非常に効果がある。

【0035】

また、画素TFT上には全素子共通のパッシベーション膜14が設けられ、その上に樹脂膜など平坦性の高い絶縁膜(第2層間絶縁膜)15が形成される。そして、第2層間絶縁膜15の上には金属膜でなる遮蔽膜134、遮蔽膜134を酸化して得られた酸化物135及び第2層間絶縁膜に形成されたコンタクトホールを介して画素TFT304に接続された画素電極136が形成される。

【0036】

なお、137が隣接する他の画素の画素電極であり、画素電極136は酸化物135を介して遮蔽膜135と重なることによって保持容量138を形成している。即ち、図1に示した構造の特徴の一つとして、保持容量138が光遮蔽膜及び電界遮蔽膜として機能しうる点が挙げられる。ただし、本願発明は図1に示した保持容量の構造に限定されるものではない。

【0037】

以上のように、メモリトランジスタ301、CMOS回路を形成するNチャネル型TFT302、CMOS回路を形成するPチャネル型TFT303、画素TFT304をそれぞれ求める性能に応じて適切な構造とすることで、アクティブマトリクス型表示装置の動作性能及び信頼性が大幅に向上する。

【0038】

さらに、複雑な工程を追加することなく、駆動回路部や画素部とともにメモリ部を同一基板上に形成することが可能であるため、従来のアクティブマトリクス型表示装置よりもさらに高性能なアクティブマトリクス型表示装置を形成することが可能となる。

【0039】

また、上記メモリ部、駆動回路部若しくは画素部以外に、その他の信号処理回路をも形成しうる。その他の信号処理回路としては、信号分割回路、D/Aコンバータ、γ補正回路、昇圧回路、差動増幅回路などが挙げられる。

【0040】

以上の構成でなる本願発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

【0041】

〔実施例1〕

本発明の実施例について図2〜図5を用いて説明する。本実施例では同一基板上に画素部、画素部を駆動するための駆動回路部及び画素部への信号情報を一時的に記憶するメモリ部とを同時に作製する方法について説明する。最終的には図1に示した構造のアクティブマトリクス基板を作製する。

【0042】

図2(A)において、基板201には、石英基板やシリコン基板を使用することが望ましい。本実施例では石英基板を用いた。その他にも金属基板の表面に絶縁膜を形成したものを基板としても良い。本実施例の場合、800℃以上の温度に耐えうる耐熱性を要求されるので、それを満たす基板であればどのような基板を用いても構わない。

【0043】

そして、基板201のTFTが形成される表面には、20〜100nm(好ましくは40〜80nm)の厚さの非晶質構造を含む半導体膜202を減圧熱CVD方、プラズマCVD法またはスパッタ法で形成する。なお、本実施例では60nm厚の非晶質珪素膜を形成するが、後に熱酸化工程があるのでこの膜厚が最終的なTFTの活性層の膜厚になるわけではない。

【0044】

また、非晶質構造を含む半導体膜としては、非晶質半導体膜、微結晶半導体膜があり、さらに非晶質シリコンゲルマニウム膜などの非晶質構造を含む化合物半導体膜を用いても良い。さらに、基板上に下地膜と非晶質珪素膜とを大気解放しないで連続的に形成することも有効である。そうすることにより基板表面の汚染が非晶質珪素膜に影響を与えないようにすることが可能となり、作製されるTFTの特性バラツキを低減させることができる。

【0045】

次に、非晶質珪素膜202上に珪素(シリコン)を含む絶縁膜でなるマスク膜203を形成し、パターニングによって開口部204a、204bを形成する。この開口部は、次の結晶化工程の際に結晶化を助長する触媒元素を添加するための添加領域となる。(図2(A))

【0046】

なお、珪素を含む絶縁膜としては、酸化珪素膜、窒化珪素膜、窒化酸化珪素膜を用いることができる。窒化酸化珪素膜は、珪素、窒素及び酸素を所定の量で含む絶縁膜であり、SiOxNyで表される絶縁膜である。窒化酸化珪素膜はSiH4、N2O、NH3等を原料ガスとして作製することが可能であり、含有する窒素濃度を5〜50atomic%の範囲で変えることができる。

【0047】

また、このマスク膜203のパターニングを行うと同時に、後のパターニング工程の基準となるマーカーパターンを形成しておく。マスク膜203をエッチングする際に非晶質シリコン膜202も僅かにエッチングされるが、この段差が後にマスク合わせの時にマーカーパターンとして用いることができる。

【0048】

次に、特開平10−247735号公報に記載された技術に従って、結晶構造を含む半導体膜を形成する。同公報記載の技術は、非晶質構造を含む半導体膜の結晶化に際して、結晶化を助長する触媒元素(ニッケル、コバルト、ゲルマニウム、錫、鉛、パラジウム、鉄、銅から選ばれた一種または複数種の元素)を用いる結晶化手段である。

【0049】

具体的には、非晶質構造を含む半導体膜の表面に触媒元素を保持させた状態で加熱処理を行い、非晶質構造を含む半導体膜を、結晶構造を含む半導体膜に変化させるものである。なお、結晶化手段としては、特開平7−130652号公報の実施例1に記載された技術を用いても良い。また、結晶質構造を含む半導体膜には、いわゆる単結晶半導体膜も多結晶半導体膜も含まれるが、同公報で形成される結晶構造を含む半導体膜は結晶粒界を有している。

【0050】

なお、同公報では触媒元素を含む層をマスク膜上に形成する際にスピンコート法を用いているが、触媒元素を含む薄膜をスパッタ法や蒸着法といった気相法を用いて成膜する手段をとっても良い。

【0051】

また、非晶質シリコン膜は含有水素量にもよるが、好ましくは400〜550℃で1時間程度の加熱処理を行い、水素を十分に脱離させてから結晶化させることが望ましい。その場合、含有水素量を5atom%以下とすることが好ましい。

【0052】

結晶化工程は、まず400〜500℃で1時間程度の熱処理工程を行い、水素を膜中から脱離させた後、500〜650℃(好ましくは550〜600℃)で6〜16時間(好ましくは8〜14時間)の熱処理を行う。

【0053】

本実施例では、触媒元素としてニッケルを用い、570℃で14時間の熱処理を行う。その結果、開口部204a、204bを起点として概略基板と平行な方向(矢印で示した方向)に結晶化が進行し、巨視的な結晶成長方向が揃った結晶構造を含む半導体膜(本実施例では結晶質珪素膜)205a〜205dが形成される。(図2(B))

【0054】

次に、結晶化の工程で用いたニッケルを結晶質珪素膜から除去するゲッタリング工程を行う。本実施例では、先ほど形成したマスク膜203をそのままマスクとして15族に属する元素(本実施例ではリン)を添加する工程を行い、開口部204a、204bで露出した結晶質珪素膜に1×1019〜1×1020atoms/cm3の濃度でリンを含むリン添加領域(以下、ゲッタリング領域という)206a、206bを形成する。(図2(C))

【0055】

次に、窒素雰囲気中で450〜650℃(好ましくは500〜550℃)、4〜24時間(好ましくは6〜12時間)の熱処理工程を行う。この熱処理工程により結晶質珪素膜中のニッケルは矢印の方向に移動し、リンのゲッタリング作用によってゲッタリング領域206a、206bに捕獲される。即ち、結晶質珪素膜中からニッケルが除去されるため、ゲッタリング後の結晶質珪素膜207a〜207dに含まれるニッケル濃度は、1×1017atms/cm3以下、好ましくは1×1016atms/cm3以下にまで低減することができる。

【0056】

次に、マスク膜203を除去し、結晶質珪素膜207a〜207d上に後の不純物添加時のために保護膜208を形成する。保護膜208は100〜200nm(好ましくは130〜170nm)の厚さの窒化酸化珪素膜または酸化珪素膜を用いると良い。この保護膜208は不純物添加時に結晶質珪素膜が直接プラズマに曝されないようにするためと、微妙な濃度制御を可能にするための意味がある。

【0057】

そして、その上にレジストマスク209a、209bを形成し、保護膜208を介してp型を付与する不純物元素(以下、p型不純物元素という)を添加する。p型不純物元素としては、代表的には13族に属する元素、典型的にはボロンまたはガリウムを用いることができる。この工程(チャネルドープ工程という)はTFTのしきい値電圧を制御するための工程である。なお、ここではジボラン(B2H6)を質量分離しないでプラズマ励起したイオンドープ法でボロンを添加する。勿論、質量分離を行うイオンインプランテーション法を用いても良い。

【0058】

この工程により1×1015〜1×1018atoms/cm3(代表的には5×1016〜5×1017atoms/cm3)の濃度でp型不純物元素(本実施例ではボロン)を含む不純物領域210a〜210cを形成する。なお、本明細書中では上記濃度範囲でp型不純物元素を含む不純物領域(但し、リンは含まれていない領域)をp型不純物領域(b)と定義する。(図2(D))

【0059】

次に、レジストマスク209a、209bを除去し、結晶質珪素膜をパターニングして島状の半導体層(以下、活性層という)211〜214を形成する。なお、活性層211〜214は、ニッケルを選択的に添加して結晶化することによって、非常に結晶性の良い結晶質シリコン膜で形成されている。具体的には、棒状または柱状の結晶が、特定の方向性を持って並んだ結晶構造を有している。また、結晶化後、ニッケルをリンのゲッタリング作用により除去又は低減しており、活性層211〜214中に残存する触媒元素の濃度は、1×1017atms/cm3以下、好ましくは1×1016atms/cm3以下である。(図2(E))

【0060】

また、pチャネル型TFTの活性層213は意図的に添加された不純物元素を含まない領域であり、nチャネル型TFTの活性層211、212、214はp型不純物領域(b)となっている。本明細書中では、この状態の活性層211〜214は全て真性または実質的に真性であると定義する。即ち、TFTの動作に支障をきたさない程度に不純物元素が意図的に添加されている領域が実質的に真性な領域と考えて良い。

【0061】

次に、プラズマCVD法またはスパッタ法により10〜100nm厚の珪素を含む絶縁膜を形成する。本実施例では、30nm厚の窒化酸化珪素膜を形成する。この珪素を含む絶縁膜は積層構造で用いても構わない。そして、パターニングを行い、駆動回路部及び画素部となる領域のみ残して他の領域は除去し、活性層211を露呈させる。

【0062】

次に、800〜1150℃(好ましくは900〜1000℃)の温度で15分〜8時間(好ましくは30分〜2時間)の熱処理工程を、酸化性雰囲気下で行う(熱酸化工程)。本実施例では酸素雰囲気中に3体積%の塩化水素を添加した雰囲気中で950℃80分の熱処理工程を行う。なお、図2(D)の工程で添加されたボロンはこの熱酸化工程の間に活性化される。(図3(A))

【0063】

なお、酸化性雰囲気としては、ドライ酸素雰囲気でもウェット酸素雰囲気でも良いが、半導体層中の結晶欠陥の低減にはドライ酸素雰囲気が適している。また、本実施例では酸素雰囲気中にハロゲン元素を含ませた雰囲気としたが、100%酸素雰囲気で行っても構わない。

【0064】

こうして露呈された活性層211の表面には熱酸化膜(酸化珪素膜)215が3〜20nm(好ましくは5〜10nm)の膜厚で形成される。この熱酸化膜215は最終的にメモリトランジスタのチャネル形成領域と浮遊ゲート電極との間に形成される第1ゲート絶縁膜となる。

【0065】

また、同時に珪素を含む絶縁膜116とその下の活性層211〜214との界面においても酸化反応が進行する。本願発明ではそれを考慮して最終的に形成される絶縁膜216の膜厚が50〜150nm(好ましくは80〜120nm)となるように調節する。この珪素を含む絶縁膜216は最終的に駆動回路部及び画素部を形成するTFTのゲート絶縁膜であり、第2ゲート絶縁膜と呼ぶ。

【0066】

また、本実施例の熱酸化工程では、60nm厚の活性層のうち25nmが酸化されて活性層211〜214の膜厚は45nmとなる。これが最終的に完成したTFTの活性層の膜厚となる。また、30nm厚の珪素を含む絶縁膜に対して50nm厚の熱酸化膜が加わるので、最終的に第2ゲート絶縁膜216の膜厚は110nmとなる。

【0067】

次に、新たにレジストマスク217a〜217cを形成する。そして、n型を付与する不純物元素(以下、n型不純物元素という)を添加してn型を呈する不純物領域218、219を形成する。なお、n型不純物元素としては、代表的には15族に属する元素、典型的にはリンまたは砒素を用いることができる。(図3(B))

【0068】

この不純物領域218、219は、後にメモリトランジスタ及びCMOS回路のNチャネル型TFTにおいて、LDD領域として機能させるための不純物領域である。なお、ここで形成された不純物領域にはn型不純物元素が2×1016〜5×1019atoms/cm3(代表的には5×1017〜5×1018atoms/cm3)の濃度で含まれている。本明細書中では上記濃度範囲でn型不純物元素を含む不純物領域をn型不純物領域(b)と定義する。

【0069】

なお、ここではフォスフィン(PH3)を質量分離しないでプラズマ励起したイオンドープ法でリンを1×1018atoms/cm3の濃度で添加する。勿論、質量分離を行うイオンインプランテーション法を用いても良い。

【0070】

また、この工程ではメモリトランジスタとなる領域とCMOS回路のnチャネル型TFTとなる領域とでゲート絶縁膜の膜厚が異なる。従って、両者を2回の添加工程に分けて行っても良いし、不純物添加時の深さ方向の濃度プロファイルを調節して、218及び219で示される領域にほぼ同濃度でリンが添加されるようにすることが望ましい。

【0071】

次に、レジストマスク217a〜217cを除去し、新たにレジストマスク220a〜220cを形成する。そして、n型不純物元素を添加してn型を呈する不純物領域221、222を形成する。なお、n型不純物元素としては、代表的には15族に属する元素、典型的にはリンまたは砒素を用いることができる。(図3(C))

【0072】

この不純物領域221、222は、後にメモリトランジスタにおいて、ソース領域及びドレイン領域として機能させるための不純物領域である。なお、ここで形成された不純物領域にはn型不純物元素が1×1020〜1×1021atoms/cm3(代表的には2×1020〜5×1021atoms/cm3)の濃度で含まれている。本明細書中では上記濃度範囲でn型不純物元素を含む不純物領域をn型不純物領域(a)と定義する。

【0073】

なお、ここではフォスフィン(PH3)を質量分離しないでプラズマ励起したイオンドープ法でリンを3×1020atoms/cm3の濃度で添加する。勿論、質量分離を行うイオンインプランテーション法を用いても良い。

【0074】

次に、600〜1000℃(好ましくは700〜800℃)の不活性雰囲気中で熱処理を行い、図3(B)の工程で添加されたリンを活性化する。本実施例では800℃1時間の熱処理を窒素雰囲気中で行う。(図3(D))

【0075】

この時、同時にリンの添加時に損傷した活性層の結晶性及び活性層とゲート絶縁膜との界面を修復することが可能である。この活性化工程は電熱炉を用いたファーネスアニールが好ましいが、ランプアニールやレーザーアニールといった光アニールでも良いし、ファーネスアニールと併用しても良い。

【0076】

この工程によりn型不純物領域(a)222、n型不純物領域(b)218、219の境界部、即ち、n型不純物領域(a)又はn型不純物領域(b)の周囲に存在する真性又は実質的に真性な領域(勿論、p型不純物領域(b)も含む)との接合部が明確になる。このことは、後にTFTが完成した時点において、LDD領域とチャネル形成領域とが非常に良好な接合部を形成しうることを意味する。

【0077】

次に、200〜400nm(好ましくは250〜350nm)の厚さで第1ゲート電極223〜225、226a、226bを形成する。第1ゲート電極223〜225、226a、226bを形成する際は、同時に第1ゲート電極同士を電気的に接続する第1ゲート配線も形成される。但し、第1ゲート電極223はどのゲート電極とも電気的に接続されず、後にメモリトランジスタの浮遊ゲート電極として機能する。(図3(E)

【0078】

実際にはメモリ部に形成される複数のメモリトランジスタ全てに浮遊ゲート電極が形成されるが、個々に電気的に孤立した状態、即ちフローティング状態としてある。こうすることで電荷蓄積層として機能するのである。

【0079】

ゲート電極223〜225、226a、226bの材料としては、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、クロム(Cr)、シリコン(Si)から選ばれた元素、または前記元素を主成分とする導電膜(代表的には窒化タンタル膜、窒化タングステン膜、窒化チタン膜)、または前記元素を組み合わせた合金膜(代表的にはMo−W合金膜、Mo−Ta合金膜、タングステンシリサイド膜等)を用いることができる。

【0080】

なお、本実施例では50nm厚の窒化タンタル(TaN)膜と、350nm厚のタンタル(Ta)膜を積層して用いる。また、第1ゲート電極の下に珪素膜を2〜20nm程度の厚さで形成しておくことは有効である。これによりその上に形成されるゲート電極の密着性の向上と酸化防止とを図ることができる。

【0081】

この時、メモリトランジスタに形成されるゲート電極223はn型不純物領域(a)221、222及びn型不純物領域(b)218の一部とゲート絶縁膜215を介して重なるように形成する。また、CMOS回路のNチャネル型TFTに形成されるゲート電極224はn型不純物領域(b)219の一部とゲート絶縁膜216を介して重なるように形成する。なお、ゲート電極226a、226bは断面では二つに見えるが実際は電気的に接続されている。

【0082】

次に、レジストマスク227a、227bを形成し、p型不純物元素(本実施例ではボロン)を添加して高濃度にボロンを含む不純物領域228、229を形成する。本実施例ではジボラン(B2H6)を用いたイオンドープ法(勿論、イオンインプランテーション法でも良い)により3×1020〜3×1021atoms/cm3(代表的には5×1020〜1×1021atoms/cm3)濃度でボロンを添加する。なお、本明細書中では上記濃度範囲でp型不純物元素を含む不純物領域をp型不純物領域(a)と定義する。(図4(A))

【0083】

なお、ここでp型不純物元素を添加する前に、レジストマスク227a、227b及びゲート電極225をマスクとして、ゲート絶縁膜をエッチングして活性層を露呈させておいても良い。こうすることで加速電圧とドーズ量を小さくすることができ、工程のスループットを上げることができる。

【0084】

次に、レジストマスク227a、227bを除去し、レジストマスク230a〜230dを形成する。そして、n型不純物元素(本実施例ではリン)を添加して高濃度にリンを含む不純物領域231〜235を形成する。この工程は図3(C)の工程と同様に行えば良く、添加するリン濃度は1×1020〜1×1021atoms/cm3(代表的には2×1020〜5×1021atoms/cm3)とすれば良い。従って、不純物領域231〜235をn型不純物領域(a)と呼んでも構わない。(図4(B))

【0085】

また、不純物領域231〜235が形成された領域には既に前工程で添加されたリンまたはボロンが含まれるが、十分に高い濃度でリンが添加されることになるので、前工程で添加されたリンまたはボロンの影響は考えなくて良い。

【0086】

なお、ここでn型不純物元素を添加する前に、レジストマスク230a〜230d及びゲート電極224をマスクとして、ゲート絶縁膜をエッチングして活性層を露呈させておいても良い。こうすることで加速電圧とドーズ量を小さくすることができ、工程のスループットを上げることができる。

【0087】

次に、レジストマスク230a〜230dを除去し、ゲート電極223〜225、226a、226bをマスクとして自己整合的にn型不純物元素(本実施例ではリン)を添加する。こうして形成された不純物領域236〜239には前記n型不純物領域(b)の1/2〜1/10(代表的には1/3〜1/4)の濃度(但し、前述のチャネルドープ工程で添加されたボロン濃度よりも5〜10倍高い濃度、代表的には1×1016〜5×1018atoms/cm3、典型的には3×1017〜3×1018atoms/cm3、)でリンが添加されるように調節する。なお、本明細書中では上記濃度範囲でn型不純物元素を含む不純物領域(但し、p型不純物領域を除く)をn型不純物領域(c)と定義する。(図4(C))

【0088】

なお、この工程ではゲート電極で隠された部分を除いて全ての不純物領域にも1×1016〜5×1018atoms/cm3の濃度でリンが添加されているが、非常に低濃度であるため各不純物領域の機能には影響を与えない。また、n型不純物領域(b)236〜239には既にチャネルドープ工程で1×1015〜1×1018atoms/cm3の濃度のボロンが添加されているが、この工程ではp型不純物領域(b)に含まれるボロンの5〜10倍の濃度でリンが添加されるので、この場合もボロンはn型不純物領域(b)の機能には影響を与えないと考えて良い。

【0089】

次に、それぞれの濃度で添加されたn型又はp型不純物元素を活性化するために熱処理工程を行った。この工程はファーネスアニール法、レーザーアニール法、ランプアニール法のいずれか又はそれらを併用して行うことができる。ファーネスアニール法で行う場合は、不活性雰囲気中において500〜800℃、好ましくは550〜600℃で行えば良い。本実施例では550℃、4時間の熱処理を行い、不純物元素を活性化する。(図4(D))

【0090】

なお、本実施例では窒化タンタル膜とタンタル膜でなる積層膜をゲート電極材料として用いているが、タンタル膜は非常に酸化に弱い。従って、この活性化工程は極力酸素を含まない不活性雰囲気中で行う必要がある。具体的には、酸素が1ppm以下(好ましくは0.1ppm以下)の不活性雰囲気中が好ましい。

【0091】

本実施例では、100%窒素雰囲気で550℃4時間の熱処理を行うが、その際、酸化が進行しない程度に十分に低い温度(100〜200℃)で基板を炉内へ投入し、十分に長い時間(30分〜1時間)の窒素パージ期間をおいた後に熱処理を行う。そして、基板を取り出す際にも上記十分に低い温度まで炉内温度が下がった後で大気解放するよう注意する。

【0092】

こうして細心の注意を払って熱処理(活性化工程)を行えば、ゲート電極の表面は僅かに窒化するものの酸化反応は防ぐことができ、大幅に抵抗が増加するような不具合は生じない。

【0093】

次に、第1ゲート電極223〜225、226a、226bを覆って第3ゲート絶縁膜240を形成する。なお、実際にゲート絶縁膜として機能するのは第1ゲート電極223の上にあたる部分だけであるが、説明の便宜上、特に区別しないで呼ぶことにする。

【0094】

この第3ゲート絶縁膜240は公知の気相法で形成すれば良いが、膜質の良い薄膜を得るために本実施例では減圧熱CVD法により形成する。また、本実施例では酸化珪素膜で窒化珪素膜を挟んだ三層構造の積層膜を第3ゲート絶縁膜として用いる。膜厚はトータルで15〜50nm(好ましくは20〜40nm)とすれば良い。本実施例では酸化珪素膜(膜厚:10nm)/窒化珪素膜(膜厚:20nm)/酸化珪素膜(膜厚:10nm)とするが、これに限定する必要はなく、カップリング比を考慮して決定すれば良い。

【0095】

そして、第3ゲート絶縁膜240を介して、第1ゲート電極223と重なる位置に第2ゲート電極241を形成する。この第2ゲート電極241は後にメモリトランジスタの制御ゲート電極として機能する。膜厚は200〜400nmの範囲で選択すれば良い。(図5(A))

【0096】

第2ゲート電極(制御ゲート電極)241の材料としては、第1ゲート電極と同様の材料を用いることができるが、これ以降の工程では高い450℃以上に温度が上がることがないので、その温度に耐えうる耐熱性を有する導電膜であれば、いかなる材料を用いても良い。特に、低抵抗なアルミニウム又は銅を含む金属膜が好ましい。

【0097】

次に、第1層間絶縁膜242を形成する。第1層間絶縁膜242としては、珪素を含む絶縁膜、具体的には窒化珪素膜、酸化珪素膜、窒化酸化珪素膜またはそれらを組み合わせた積層膜で形成すれば良い。また、膜厚は400nm〜1.5μmとすれば良い。本実施例では、プラズマCVD法を用いて1μm厚の酸化珪素膜を形成する。

【0098】

次に、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜4時間の熱処理を行い、活性層の水素化を行う。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる水素化処理)を行っても良い。

【0099】

次に、それぞれのTFTのソース領域又はドレイン領域に達するコンタクトホールが形成され、共通ソース配線243、ビット配線244、ソース配線245〜247、ドレイン配線248、249を形成する。なお、CMOS回路を形成するためにドレイン配線248はNチャネル型TFTとPチャネル型TFTとの間で共通である。また、図示していないが、本実施例ではこの配線を、Ti膜を200nm、Tiを含むアルミニウム膜500nm、TiN膜100nmをスパッタ法で連続して形成した三層構造の積層膜とする。(図5(B))

【0100】

さらに、TFTを外部汚染から保護する保護膜(パッシベーション膜ともいう)250として、珪素を含む絶縁膜を50〜500nm(代表的には200〜300nm)の厚さで形成する。本実施例では300nm厚の窒化酸化珪素膜を用い、パッシベーション膜の形成に先立ってH2、NH3等水素を含むガスを用いてプラズマ処理を行った後に成膜する。

【0101】

この前処理によりプラズマで励起された水素が第1層間絶縁膜中に供給される。この状態で熱処理(300〜420℃の温度)を行うことで、パッシベーション膜250おの膜質を改善するとともに、第1層間絶縁膜中に添加された水素が下層側に拡散するため、効果的に活性層を水素化することができる。

【0102】

なお、この熱処理工程のあと、後に画素電極とドレイン配線を接続するためのコンタクトホールを形成する位置において、パッシベーション膜250に開口部(図示せず)を形成しておいても良い。また、この工程を行う際、画素内の画像表示領域のパッシベーション膜を除去しておくと透過型液晶表示装置においては透過光量が増加して明るい画像が得られる。

【0103】

次に、有機樹脂からなる第2層間絶縁膜251を約1μmの厚さに形成する。有機樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜や有機系SiO化合物などを用いることもできる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300℃で焼成して形成する。

【0104】

次に、画素部となる領域において、第2層間絶縁膜251上に遮蔽膜252を形成する。なお、本明細書中では光と電磁波を遮るという意味で遮蔽膜という文言を用いる。遮蔽膜252はアルミニウム(Al)、チタン(Ti)、タンタル(Ta)から選ばれた元素でなる導電膜またはいずれかの元素を主成分とする導電膜で100〜300nmの厚さに形成する。本実施例では1wt%のチタンを含有させたアルミニウム膜を125nmの厚さに形成する。

【0105】

なお、第2層間絶縁膜251上に酸化珪素膜等の絶縁膜を5〜50nm形成しておくと、この上に形成する遮蔽膜の密着性を高めることができる。この効果は窒化チタン膜等の導電膜を用いても得られる。また、有機樹脂で形成した第2層間絶縁膜251の表面にCF4ガスを用いたプラズマ処理を施すと、表面改質により膜上に形成する遮蔽膜の密着性を向上させることができる。

【0106】

また、このチタンを含有させたアルミニウム膜を用いて、遮蔽膜だけでなく他の接続配線を形成することも可能である。例えば、駆動回路内で回路間をつなぐ接続配線を形成できる。但し、その場合は遮蔽膜または接続配線を形成する材料を成膜する前に、予め第2層間絶縁膜にコンタクトホールを形成しておく必要がある。

【0107】

次に、遮蔽膜252の表面に陽極酸化法またはプラズマ酸化法(本実施例では陽極酸化法)により20〜100nm(好ましくは30〜50nm)の厚さの酸化物(陽極酸化物)253を形成する。本実施例では遮蔽膜252としてアルミニウムを主成分とする膜を用いたため、酸化物253として酸化アルミニウム膜(アルミナ膜)が形成される。

【0108】

この陽極酸化処理に際して、まず酒石酸エチレングリコール溶液を作製する。これは15%の酒石酸アンモニウム水溶液とエチレングリコールとを2:8で混合した溶液であり、これにアンモニア水を加え、pHが7±0.5となるように調節する。そして、この溶液中に陰極となる白金電極を設け、遮蔽膜252が形成されている基板を溶液に浸し、遮蔽膜252を陽極として、一定(数mA〜数十mA)の直流電流を流す。

【0109】

溶液中の陰極と陽極との間の電圧は陽極酸化物の成長に従い時間と共に変化するが、定電流のまま100V/minの昇圧レートで電圧を上昇させて、到達電圧45Vに達したところで陽極酸化処理を終了させる。このようにして遮蔽膜252の表面には厚さ約50nmの酸化物253を形成することができる。また、その結果、遮蔽膜252の膜厚は90nmとなる。

【0110】

なお、ここで示した陽極酸化法に係わる数値は一例にすぎず、作製する素子の大きさ等によって当然最適値は変化しうるものである。

【0111】

また、ここでは陽極酸化法を用いて遮蔽膜表面のみに絶縁膜を設ける構成としたが、絶縁膜をプラズマCVD法、熱CVD法またはスパッタ法などの気相法によって形成しても良い。その場合も膜厚は20〜100nm(好ましくは30〜50nm)とすることが好ましい。また、酸化珪素膜、窒化珪素膜、窒化酸化珪素膜、DLC等の炭素膜、酸化タンタル膜若しくは有機樹脂膜を用いても良い。又は、これらを組み合わせた積層膜を用いても良い。

【0112】

次に、第2層間絶縁膜251、パッシベーション膜250にドレイン配線249に達するコンタクトホールを形成し、画素電極254を形成する。なお、画素電極255は隣接する他の画素の画素電極である。画素電極254、255は、透過型液晶表示装置とする場合には透明導電膜を用い、反射型の液晶表示装置とする場合には金属膜を用いれば良い。ここでは透過型の液晶表示装置とするために、酸化インジウムと酸化スズとの化合物膜(ITO膜)を110nmの厚さにスパッタ法で形成する。

【0113】

また、この時、画素電極254と遮蔽膜252とが酸化物253を介して重なり、保持容量(キャパシタンス・ストレージ)256を形成する。なお、この場合、遮蔽膜252をフローティング状態(電気的に孤立した状態)か固定電位、好ましくはコモン電位(データとして送られる画像信号の中間電位)に設定しておくことが望ましい。

【0114】

こうして同一基板上に、メモリ部、駆動回路部及び画素部を有するアクティブマトリクス基板が完成する。図5(C)に示すアクティブマトリクス基板は図1で説明したアクティブマトリクス基板と同じ構造である。

【0115】

本願発明では、メモリ部、駆動回路部及び画素部が要求する性能に応じて各回路又は素子を形成するTFTの構造を最適化し、電気光学装置の動作性能及び信頼性を向上させることができる。具体的には、駆動回路部には動作速度若しくはホットキャリア対策を重視したTFT構造を用い、画素部にはオフ電流値動作の低減を重視したTFT構造を用いる。また、メモリ部には工程数の増加を最小限に抑えつつ、メモリトランジスタを形成する。

【0116】

ここでアクティブマトリクス型液晶表示装置の場合について図1を参照して説明する。

【0117】

まず、メモリトランジスタ301は浮遊ゲート電極107と制御ゲート電極108とを有する二層ゲート構造のTFTをメモリトランジスタとして用いる。このメモリトランジスタの書き込み動作は、チャネル形成領域105とドレイン領域103との接合部に発生したホットキャリアが浮遊ゲート電極107に注入されて行われる。そして、消去動作は、浮遊ゲート電極107とソース領域102との間に流れるFN(ファウラノルドハイム)電流によって行われる。

【0118】

また、LDD領域104はソース領域102とチャネル形成領域105との間のバンド間トンネル電流を防止するための緩衝領域であり、信頼性向上と消費電流低減の効果がある。このLDD領域104の長さ(幅)は0.1〜2.0μm、代表的には0.5〜1.5μmとすれば良い。

【0119】

また、nチャネル型TFT302は高速動作を重視するシフトレジスタ、レベルシフタ、バッファなどの駆動回路に適している。即ち、チャネル形成領域115とドレイン領域113との間のみにゲート電極に重なったLDD領域114を形成することで、できるだけ抵抗成分を低減させつつホットキャリア対策を講じた構造となっている。

【0120】

ドレイン領域側のみにLDD領域を設ければ足りるのは、上記駆動回路の場合、ソース領域とドレイン領域の機能が変わらず、キャリア(電子)の移動する方向が一定だからである。但し、必要に応じてチャネル形成領域を挟んでLDD領域を形成することもできる。即ち、ソース領域とチャネル形成領域の間、及びドレイン領域とチャネル形成領域との間に形成することも可能である。なお、このLDD領域114の長さ(幅)は0.1〜2.0μm、好ましくは0.5〜1.5μmとすれば良い。

【0121】

また、画素TFT304は低オフ電流動作を重視した画素部に適している。即ち、LDD領域128a〜128dをゲート電極131a、131bに重ならないように形成することで低オフ電流動作を実現している。また、メモリ部や駆動回路部に形成されるLDD領域よりも低い不純物濃度のLDD領域を用いることで、さらに低いオフ電流値とする構造となっている。さらに、不純物領域130がオフ電流値の低減に大きく寄与している。

【0122】

なお、画素TFT304に設けられるLDD領域128a〜128bの長さ(幅)は0.5〜3.5μm、代表的には2.0〜2.5μmとすれば良い。

【0123】

また、本実施例では保持容量の誘電体として比誘電率が7〜9と高い酸化アルミニウム膜を用いたことで、所望の容量を形成するために必要な保持容量の専有面積を少なくすることができる。さらに、本実施例のように画素TFT上に形成される遮蔽膜を保持容量の一方の電極とすることで、アクティブマトリクス型液晶表示装置の画像表示部の開口率を向上させることができる。

【0124】

なお、本発明は本実施例に示した保持容量の構造に限定される必要はない。例えば、本出願人による特願平9−316567号出願、特願平9−273444号出願または特願平10−254097号出願に記載された構造の保持容量を用いることもできる。

【0125】

〔実施例2〕

本実施例では、実施例1で形成したアクティブマトリクス基板(図5(C)に示される)に対してセル組み工程を行い、アクティブマトリクス型液晶表示装置を作製する場合について図6を用いて説明する。

【0126】

図6に示すように、図5(C)の状態の基板に対し、配向膜601を形成する。本実施例では配向膜としてポリイミド膜を用いる。また、対向基板602には、透明導電膜からなる対向電極603と、配向膜604とを形成する。なお、対向基板には必要に応じてカラーフィルターや遮蔽膜を形成しても良い。

【0127】

次に、配向膜を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するように調節する。そして、画素部と、駆動回路部が形成されたアクティブマトリクス基板と対向基板とを、公知のセル組み工程によってシール材やスペーサ(共に図示せず)などを介して貼りあわせる。その後、両基板の間に液晶605を注入し、封止剤(図示せず)によって完全に封止する。液晶には公知の液晶材料を用いれば良い。このようにして図6に示すアクティブマトリクス型液晶表示装置が完成する。

【0128】

次に、このアクティブマトリクス型液晶表示装置の構成を、図7の斜視図を用いて説明する。本願発明の液晶表示装置はアクティブマトリクス基板701に形成された画素部702と、ソース配線駆動回路(画像信号伝送用回路)703と、ゲート配線駆動回路(走査信号伝送用回路)704とを有する。なお、707はアクティブマトリクス基板に対向して設けられた対向基板である。

【0129】

画素部702には、図1に示した画素TFT304を含む複数の画素がマトリクス状に配列されている。また、前記画素TFTはソース配線駆動回路703から延長されるソース配線と、ゲート配線駆動回路704から延長されるゲート配線との交点に接続されている。

【0130】

また、アクティブマトリクス基板701にはFPC(フレキシブルプリントサーキット)705が接続され、画像信号やクロック信号等の情報を含む信号が液晶表示装置に入力される。

【0131】

さらに、アクティブマトリクス基板701には図1に示したメモリトランジスタ301を集積化したメモリ部706が形成される。メモリ部706は選択トランジスタとメモリトランジスタとを一つのセルに含むメモリセルを集積化させた不揮発性メモリとしても良いが、複数のメモリトランジスタのビット線を共通化させたフラッシュメモリの方が高集積化には適している。

【0132】

〔実施例3〕

実施例2に示したアクティブマトリクス型液晶表示装置において、ソース配線駆動回路703には代表的にはシフトレジスタ、レベルシフタ、バッファ、サンプリング回路(サンプル及びホールド回路)が含まれる。これはアナログ信号を処理する場合の例であるが、デジタル信号を処理する場合には、サンプリング回路に代わってラッチ、D/Aコンバータが含まれる。また、ゲート配線駆動回路の場合はシフトレジスタ、レベルシフタ、バッファを含む。

【0133】

ここでシフトレジスタは駆動電圧が3.5〜16V(代表的には5V又は10V)であり、回路を形成するCMOS回路に使われるNチャネル型TFTは図1において302で示した構造が適している。また、レベルシフタやバッファは駆動電圧が14〜16Vと高くなるが、シフトレジスタと同様に図1に示したNチャネル型TFT302を含むCMOS回路が適している。なお、レベルシフタやバッファの場合、ゲート電極をダブルゲート構造、トリプルゲート構造といったマルチゲート構造とすることは回路の信頼性を向上させる上で有効である。

【0134】

ところが、ソース配線駆動回路に含まれるサンプリング回路は、駆動電圧は14〜16Vであるが、ソース領域とドレイン領域が反転する上、オフ電流値を低減する必要があるのでホットキャリア対策と低オフ電流値対策の両方を講じなければならない。

【0135】

そこで本実施例ではサンプリング回路として図8に示した構造のNチャネル型TFT205を用いる。なお、図8ではnチャネル型TFTしか図示されていないが、実際にサンプリング回路を形成する時はnチャネル型TFTとpチャネル型TFTとを組み合わせて形成すると大電流を流しやすくなり好ましい。

【0136】

本実施例でサンプリング回路として用いるnチャネル型TFTの構造は、ソース領域21、ドレイン領域22、LDD領域23a、23b及びチャネル形成領域24を含む活性層、第2ゲート絶縁膜13、ゲート電極25、ソース配線26、ドレイン配線27を有してなる。なお、ソース領域とドレイン領域(若しくはソース配線とドレイン配線)は動作によって反転する。

【0137】

このnチャネル型TFT205の最も大きな特徴は、LDD領域23a、23bがチャネル形成領域24を挟んで設けられ、且つ、そのLDD領域が第2ゲート絶縁膜13を介してゲート電極25に重なる領域と重ならない領域とを有する点にある。

【0138】

即ち、LDD領域23a、23bのうちゲート電極25に重なっている領域は、図1に示したnチャネル型TFT302のLDD領域114と同様に、ホットキャリア注入による劣化を低減する。また、LDD領域23a、23bのうちゲート電極25に重ならない領域は、図1に示した画素TFT304のLDD領域128a〜128dと同様に、オフ電流値を低減する。

【0139】

以上のような構造を有するnチャネル型TFTをサンプリング回路に用いることでホットキャリアによる劣化が少なく、オフ電流値の低いスイッチング動作を行うことができる。なお、この時、ゲート電極に重なったLDD領域の長さ(幅)は0.3〜3.0μm、代表的には0,5〜1.5μm、ゲート電極に重ならないLDD領域の長さ(幅)は1.0〜3.5μm、代表的には1.5〜2.0μmとすれば良い。

【0140】

なお、本実施例に示したnチャネル型TFT205の構造は、図2〜5に示した工程に従えば特別な工程を付加することなく形成することができる。また、実施例2に示したアクティブマトリクス型液晶表示装置のサンプリング回路に本実施例の構造を用いることは有効である。

【0141】

〔実施例4〕

本実施例1に従って作製したTFTの活性層(特にチャネル形成領域)は結晶格子に連続性を持つ特異な結晶構造の結晶質珪素膜で形成される。このような結晶質珪素膜に関する詳細は、本出願人による特願平10−044659号、特願平10−152316号、特願平10−152308号または特願平10−152305号の出願を参照すれば良い。以下、本出願人が実験的に調べた結晶構造の特徴について概略を説明する。なお、この特徴は、本実施例によって完成されたTFTの活性層を形成する半導体膜の特徴と一致する。

【0142】

上記結晶質珪素膜は、微視的に見れば複数の針状又は棒状の結晶(以下、棒状結晶という)が集まって並んだ結晶構造を有する。このことはTEM(透過型電子顕微鏡法)による観察で容易に確認できる。

【0143】

また、電子線回折法を利用すると結晶質珪素膜の表面(チャネルを形成する部分)に多くの{110}面を確認することができる。このことは、電子線回折写真で分析を行えば{110}面に対応する回折斑点がきれいに現れるので容易に確認することができる。また、各斑点は同心円上に±1°程度の分布(広がり)を持っていることも確認できる。

【0144】

また、X線回折法(厳密にはθ−2θ法を用いたX線回折法)を用いて配向比率を算出してみると{220}面の配向比率が0.7以上(典型的には0.85以上)であることが確認されている。なお、配向比率の算出方法は特開平7−321339号公報に記載された手法を用いる。

【0145】

また、個々の棒状結晶が接して形成する結晶粒界をHR−TEM(高分解能透過型電子顕微鏡法)により観察すると、結晶粒界において結晶格子に連続性があることを確認できる。これは観察される格子縞が結晶粒界において連続的に繋がっていることから容易に確認することができる。

【0146】

なお、結晶粒界における結晶格子の連続性は、その結晶粒界が「平面状粒界」と呼ばれる粒界であることに起因する。本明細書における平面状粒界の定義は、「Characterization of High-Efficiency Cast-Si Solar Cell Wafers by MBIC Measurement ;Ryuichi Shimokawa and Yutaka Hayashi,Japanese Journal of Applied Physics vol.27,No.5,pp.751-758,1988」に記載された「Planar boundary 」である。

【0147】

上記論文によれば、平面状粒界には双晶粒界、特殊な積層欠陥、特殊なtwist 粒界などが含まれる。この平面状粒界は電気的に不活性であるという特徴を持つ。即ち、結晶粒界でありながらキャリアの移動を阻害するトラップとして機能しないため、実質的に存在しないと見なすことができる。

【0148】

特に結晶軸(結晶面に垂直な軸)が〈110〉軸である場合、{211}双晶粒界はΣ3の対応粒界とも呼ばれる。Σ値は対応粒界の整合性の程度を示す指針となるパラメータであり、Σ値が小さいほど整合性の良い粒界であることが知られている。例えば、二つの結晶粒の間に形成された結晶粒界では、両方の結晶の面方位が{110}である場合、{111}面に対応する格子縞がなす角をθとするとθ=70.5°の時にΣ3の対応粒界となることが知られている。

【0149】

本実施例を実施して得た結晶質珪素膜において、結晶軸が〈110〉である二つの結晶粒の間に形成された結晶粒界をHR−TEMで観察すると、隣接する結晶粒の各格子縞が約70.5°の角度で連続しているものが多い。従って、その結晶粒界はΣ3の対応粒界、即ち{211}双晶粒界であると推測できる。

【0150】

実際に本実施例の結晶質珪素膜を詳細にTEMを用いて観察すれば、結晶粒界の殆ど(90%以上、典型的には95%以上)がΣ3の対応粒界、典型的には{211}双晶粒界であると推測される。

【0151】

この様な結晶構造(正確には結晶粒界の構造)は、結晶粒界において異なる二つの結晶粒が極めて整合性よく接合していることを示している。即ち、結晶粒界において結晶格子が連続的に連なり、結晶欠陥等に起因するトラップ準位を非常に作りにくい構成となっている。従って、この様な結晶構造を有する半導体薄膜は実質的に結晶粒界が存在しない見なすことができる。

【0152】

またさらに、800〜1150℃という高い温度での熱処理工程(実施例1における熱酸化工程に相当する)によって結晶粒内に存在する欠陥(スタッキングフォールト)が殆ど消滅していることがTEM観察によって確認されている。これはこの熱処理工程の前後で積層欠陥等の数が大幅に低減していることからも明らかである。

【0153】

この欠陥数の差は電子スピン共鳴分析(Electron Spin Resonance :ESR)によってスピン密度の差となって現れる。現状では本実施例の結晶質珪素膜のスピン密度は少なくとも 5×1017spins/cm3以下(典型的には 3×1017spins/cm3以下)であることが判明している。ただし、この測定値は現存する測定装置の検出限界に近いので、実際のスピン密度はさらに低いと予想される。

【0154】

以上の事から、実施例1に従って作製した結晶質珪素膜は結晶粒内の欠陥が極端に少なく、結晶粒界が実質的に存在しないと見なせるため、単結晶珪素膜又は実質的な単結晶珪素膜と考えて良い。

【0155】

〔実施例5〕

画素部の各画素に設けられる保持容量は画素電極に接続されていない方の電極(本願発明の場合は遮蔽膜)を固定電位としておくことで保持容量を形成することができる。その場合、遮蔽膜をフローティング状態(電気的に孤立した状態)かコモン電位(データとして送られる画像信号の中間電位)に設定しておくことが望ましい。

【0156】

そこで本実施例では遮蔽膜を固定電位とする場合の接続方法について図9を用いて説明する。なお、基本構造は図1で説明した画素部と同様であるので、同一部位には同じ符号を用いて説明する。

【0157】

図9(A)において、304は実施例1と同様にして作製された画素TFT(nチャネル型TFT)であり、134は保持容量の一方の電極として機能する遮蔽膜である。画素部の外側に延長された遮蔽膜901は第2層間絶縁膜15、パッシベーション膜14に設けられたコンタクトホール902を介してコモン電位を与える電流供給線903と接続している。従って、この場合には遮蔽膜901を形成する前に第2層間絶縁膜159、パッシベーション膜158をエッチングしてコンタクトホールを形成しておく工程が必要となる。この電流供給線903はソース配線またはドレイン配線と同時に形成しておけば良い。

【0158】

このように画素部の外側において、遮蔽膜901とコモン電位を与える電流供給線903とを電気的に接続することで、遮蔽膜134をコモン電位に保持することができる。

【0159】

次に、図9(B)において、304は実施例1と同様にして作製された画素TFTであり、134は保持容量の一方の電極として機能する遮蔽膜である。画素部の外側まで延在した遮蔽膜904は、905で示される領域において導電膜906と酸化物907を介して重なる。この導電膜906は画素電極136と同時に、酸化物907は酸化物135と同時に形成される。

【0160】

そして、この導電膜906は第3層間絶縁膜15、パッシベーション膜14に設けられたコンタクトホール908を介してコモン電位を与える電流供給線909と接続している。この時、領域905では遮蔽膜904、酸化物907、導電膜906でなるコンデンサが形成される。このコンデンサの容量が十分に大きい場合(1走査ライン分の全画素に接続された全保持容量の合計容量の10倍程度の場合)、領域905で形成された静電結合によって遮蔽膜904及び134の電位変動を低減することができる。

【0161】

また、図9(B)の構造を採用する場合は、アクティブマトリクス型液晶表示装置の駆動方法としてはソースライン反転駆動を採用することが好ましい。ソースライン反転駆動ならば画素電極に印加される電圧極性が1フレーム毎に反転するので、時間的に平均化すれば遮蔽膜134に蓄積される電荷量は殆どゼロとなる。即ち、非常に電位変動の小さい状態を維持できるので、安定した保持容量を形成することができる。

【0162】

このように図9(B)の構造を採用することで、工程数を増やすことなく遮蔽膜をコモン電位に保持することが可能となる。

【0163】

なお、本実施例の構成は、実施例1の作製工程を一部変更するだけで実現可能であり、その他の工程は実施例1と同様の工程で良い。従って、実施例2に示したアクティブマトリクス型液晶表示装置に適用することは可能である。また、実施例3、4に示したいずれの構成とも自由に組み合わせることが可能である。

【0164】

〔実施例6〕

本実施例では図1とは異なる構造のアクティブマトリクス基板を作製した場合について説明する。説明には図10を用いる。なお、本実施例は図1に示した構造の一部を変更した例であるので、同一箇所には図1と同じ符号を用いる。また、変更のない部分に関しては図1に対応するので説明は省略する。

【0165】

まず、図10(A)に示したアクティブマトリクス基板は、第3ゲート絶縁膜として酸化物31を用いる。この酸化物31は浮遊ゲート電極107を酸化して得られた酸化膜であり、本実施例では酸化タンタル膜である。酸化方法は、熱酸化法、陽極酸化法若しくはプラズマ酸化法のいずれかの手段によれば良いが、膜質を良くするためには熱酸化法が好ましい。また、形成する膜厚は、実施例1と同様に3〜20nm(好ましくは5〜10nm)とすれば良い。

【0166】

なお、この時同時に駆動回路部及び画素部に形成されるTFTのゲート電極116、123、131a、131bのそれぞれの表面にも酸化物32、33、34a、34bが形成される。但し、駆動回路部若しくは画素部をマスキングして酸化工程を行うことによりメモリトランジスタの浮遊ゲート電極のみに酸化物を形成することも可能である。勿論、陽極酸化法を用いる場合には、浮遊ゲート電極のみに選択的に電流を流すことで選択的に酸化物を形成することもできる。

【0167】

また、この酸化工程は実施例1において、図4(B)の工程と図4(C)の工程の間に行うことが望ましい。なぜならばゲート電極131a、131bの表面が酸化物34a、34bで覆われた状態で図4(C)の工程を行うことにより、図11に示すようなオフセット領域35a〜35dが形成されるからである。なお、図11は図10(A)に示した画素TFTの一部(ドレイン領域付近)を拡大した断面図である。

【0168】

この場合、図11に示すように、チャネル形成領域129a、129bとn型不純物領域(c)でなるLDD領域128a〜128dの間にオフセット領域35a〜35bが存在する。このオフセット領域35a〜35bの長さは、ほぼ酸化物34a、34bの膜厚(ここでいう膜厚は厳密にはゲート電極の側壁に形成されている部分の膜厚)に一致する。

【0169】

但し、リンを添加する際の回り込みによってオフセット領域35a〜35bの長さは酸化物34a、34bの膜厚よりも短くなることは言うまでもない。

【0170】

本願発明では、このオフセット領域35a〜35bの長さがゼロ若しくは1〜200nm(好ましくは20〜100nm、さらに好ましくは30〜70nm)とする。この長さは酸化物34a、34bの膜厚で制御できる。

【0171】

図10(A)に示したような構造の画素TFTは、オフ電流値を極めて低い値にすることが可能である。即ち、ソース−ドレイン間の電圧が14V、ゲート電圧が−17.5VといったようにTFTが完全にオフ動作にある時、5pA以下(好ましくは1pA以下)といったオフ電流値を達成しうる。

【0172】

また、図10(B)の構造は、図10(A)と似ているが制御ゲート電極36をソース配線109やドレイン配線110と同時に形成する点に特徴がある。このような構造は、ソース配線とソース領域(若しくはドレイン配線とドレイン領域)とを接続するためのコンタクトホールを形成する際に、浮遊ゲート電極107の上方にも開口部を設けておけば実現できる。

【0173】

なお、この開口部の形成は第1層間絶縁膜12と第3ゲート絶縁膜31とのエッチングの選択比が大きいほど良い。

【0174】

また、図10(A)と同様に画素TFTはチャネル形成領域129a、129bとn型不純物領域(c)でなるLDD領域128a〜128dの間にオフセット領域35a〜35bが存在する。効果については図10(A)の説明で既に行ったのでここでは省略する。

【0175】

なお、本実施例の構成は実施例1において第3ゲート絶縁膜240の成膜工程を、熱酸化工程、陽極酸化工程若しくはプラズマ酸化工程に置き換えるだけで実施可能であり、実施例2〜5に記載されたいずれの構成とも自由に組み合わせることが可能である。

【0176】

〔実施例7〕

本実施例では図1とは異なる構造のアクティブマトリクス基板を作製した場合について説明する。説明には図12を用いる。なお、本実施例は図1に示した構造の一部を変更した例であるので、同一箇所には図1と同じ符号を用いる。また、変更のない部分に関しては図1に対応するので説明は省略する。

【0177】

図12に示したアクティブマトリクス基板は、第1ゲート絶縁膜として減圧熱CVD法により形成された絶縁膜1201を用いる。本実施例では成膜ガスとしてSiH4ガス(流量0.3×10-6m3/s)とN2Oガス(流量1.5×10-5m3/s)を用い、成膜温度を800℃、成膜圧力を40Paとして成膜すれば良い。また、膜厚は、実施例1と同様に3〜20nm(好ましくは5〜10nm)とすれば良い。勿論、第1ゲート絶縁膜1201を成膜した後、実施例1と同様の熱酸化工程を行っても良い。

【0178】

本実施例を実施した場合、画素部では第2ゲート絶縁膜13と第1ゲート絶縁膜1201との積層膜(上記熱酸化工程を行った場合は熱酸化膜も含む)がゲート絶縁膜として機能することになる。

【0179】

なお、本実施例は実施例1において第1ゲート絶縁膜1201の成膜工程を加える以外は特に変更すべき工程はないので、実施例1を参考にすれば容易に実施することが可能である。また、実施例2〜実施例6のいずれの構成とも自由に組み合わせて実施することが可能である。

【0180】

〔実施例8〕

本発明は基板としてガラスもしくはプラスチックを用いた場合においても実施することは可能である。勿論、この場合はガラスもしくはプラスチックからなる基板の耐熱性を考慮してTFTを形成しなくてはならない。

【0181】

活性層となる結晶質珪素膜を形成するには、レーザー結晶化技術もしくは固相成長技術(熱結晶化技術)とレーザー結晶化技術との併用により非晶質珪素膜の結晶化を行うことが好ましい。レーザー結晶化技術を用いればプラスチック基板もしくはプラスチックフィルムの上にも結晶質珪素膜を形成しうる。

【0182】

また、第1ゲート絶縁膜、第2ゲート絶縁膜及び第3ゲート絶縁膜はプラズマCVD法もしくはスパッタ法で形成する。特に、ECR(Electron Cyclotron Resonance)プラズマCVD法やリモートプラズマCVD法は活性層に与えるダメージを抑えつつ高品質な絶縁膜を形成することができるため好ましい。

【0183】

なお、本実施例は実施例1において第1ゲート絶縁膜、第2ゲート絶縁膜及び第3ゲート絶縁膜の成膜工程を変更する以外は特に変更すべき工程はないので、実施例1を参考にすれば容易に実施することが可能である。また、実施例2〜実施例6のいずれの構成とも自由に組み合わせて実施することが可能である。

【0184】

〔実施例9〕

本実施例では本願発明においてメモリ部を形成しうる不揮発性メモリの回路構成について説明する。具体的には、図7に示した液晶表示装置(液晶モジュール)において、メモリ部706をNOR型フラッシュメモリとした場合について図13を用いて説明する。なお、図13には四つのメモリトランジスタを並列につなげたセクターを二つ図示しているが、この構成に限定する必要はない。

【0185】

図13(A)において、B1で示されるビット配線41には四つのメモリトランジスタ42〜45が接続されている。B2も同様である。また、メモリトランジスタ42〜45のそれぞれはW1〜W4で示されるワード配線47〜50を制御ゲート電極として制御される。

【0186】

なお、本明細書ではワード配線のうちTFTの活性層と重なる領域を特に制御ゲート電極と呼んでいる。また、図示されていないが、実際には制御ゲート電極の下には浮遊ゲート電極が存在する。

【0187】

図13(A)の回路図で示したNOR型フラッシュメモリを実際に素子パターンとして表すと図13(B)のようになる。使用した各符号は図13(A)のものと対応している。

【0188】

本実施例の構成は、実施例1〜8に示したいずれの構成とも自由に組み合わせて実施することが可能である。

【0189】

〔実施例10〕

本実施例では本願発明においてメモリ部を形成しうる不揮発性メモリの回路構成について説明する。具体的には、図7に示した液晶表示装置(液晶モジュール)において、メモリ部706をNAND型フラッシュメモリとした場合について図14を用いて説明する。なお、図14には八つのメモリトランジスタを直列につなげたセクターを二つ図示しているが、この構成に限定する必要はない。

【0190】

図14(A)において、B1で示されるビット配線55には二つの選択トランジスタ51、52及び八つのメモリトランジスタ56〜63が接続されている。B2も同様である。また、選択トランジスタ51、52はそれぞれS1、S2で示される選択用ゲート配線53、54で制御され、メモリトランジスタ56〜63のそれぞれはW1〜W8で示されるワード配線64〜71を制御ゲート電極として制御される。

【0191】

なお、本明細書ではワード配線のうちTFTの活性層と重なる領域を特に制御ゲート電極と呼んでいる。また、図示されていないが、実際には制御ゲート電極の下には浮遊ゲート電極が存在する。

【0192】

図14(A)の回路図で示したNAND型フラッシュメモリを実際に素子パターンとして表すと図14(B)のようになる。使用した各符号は図14(A)のものと対応している。

【0193】

本実施例の構成は、実施例1〜8に示したいずれの構成とも自由に組み合わせて実施することが可能である。また、実施例9に示したNOR型フラッシュメモリと組み合わせてメモリ部を形成することもできる。

【0194】

〔実施例11〕

本実施例では、本願発明の電気光学装置においてメモリ部、駆動回路部又は画素部以外のその他の信号処理回路として、γ(ガンマ)補正回路を加えた場合について説明する。

【0195】

なお、γ補正回路とはγ補正を行うための回路である。γ補正とは画像信号に適切な電圧を付加することによって、画素電極に印加される電圧とその上の液晶又はEL層の透過光強度との間に線形関係を作るための補正である。

【0196】

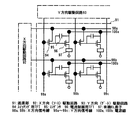

図15は本実施例の液晶表示装置(EL表示装置であっても良い)に用いるアクティブマトリクス基板のブロック図である。画素部75の周辺にソース配線駆動回路76、ゲート配線駆動回路77が設けられ、さらにγ補正回路78、不揮発性メモリ(本実施例ではフラッシュメモリ)79が設けられている。また、画像信号、クロック信号若しくは同期信号等は、FPC(フレキシブルプリントサーキット)80を経由して送られてくる。

【0197】

不揮発性メモリ79には、パソコン本体やテレビ受信アンテナ等から送られてきた画像信号にγ補正をかけるための補正データが格納(記憶)されており、その補正データを参照してγ補正回路78が画像信号に対してγ補正を行う。

【0198】

γ補正のためのデータは液晶表示装置を出荷する前に一度格納しておけば良いが、定期的に補正データを書き換えることも可能である。また、同じように作成した液晶表示装置であっても、微妙に液晶の光学応答特性(先の透過光強度と印加電圧の関係など)が異なる場合がある。その場合も、本実施例では液晶表示装置毎に異なるγ補正データを格納しておくことが可能なので、常に同じ画質を得ることが可能である。

【0199】

なお、不揮発性メモリ79に対してγ補正の補正データを格納する際、本出願人による特願平10−156696号に記載された手段を用いることは好ましい。また、γ補正に関する説明も同出願になされている。

【0200】

また、不揮発性メモリに格納する補正データはデジタル信号であるので、必要に応じてD/Aコンバータ若しくはA/Dコンバータを同一基板上に形成することが望ましい。

【0201】

なお、本実施例の構成は、実施例1〜10のいずれの構成とも自由に組み合わせて実施することができる。

【0202】

〔実施例12〕

本実施例では、本願発明の電気光学装置においてメモリ部、駆動回路部又は画素部以外のその他の信号処理回路として、メモリコントローラ回路を加えた場合について説明する。なお、ここでいうメモリコントローラ回路とは不揮発性メモリに画像データを格納したり読み出したりという動作を制御するための制御回路である。

【0203】

図16は本実施例の液晶表示装置(EL表示装置であっても良い)に用いるアクティブマトリクス基板のブロック図である。画素部81の周辺にソース配線駆動回路82、ゲート配線駆動回路83が設けられ、さらにメモリコントローラ回路84、不揮発性メモリ(本実施例ではフラッシュメモリ)85が設けられている。また、画像信号、クロック信号若しくは同期信号等は、FPC(フレキシブルプリントサーキット)86を経由して送られてくる。

【0204】

不揮発性メモリ85には、パソコン本体やテレビ受信アンテナ等から送られてきた画像信号が1フレーム毎に格納(記憶)されており、その画像信号を順次画素部に入力して表示を行う。不揮発性メモリ85には画素部81に表示される画像1フレーム分の画像情報が記憶される。例えば、6ビットのデジタル信号が画像信号として送られてくる場合、画素数×6ビットに相当するメモリ容量を必要とする。

【0205】

なお、不揮発性メモリに格納する補正データはデジタル信号であるので、必要に応じてD/Aコンバータ若しくはA/Dコンバータを同一基板上に形成することが望ましい。

【0206】

このように本実施例の構成とすることで、画素部81に表示された画像を常に不揮発性メモリ85に記憶しており、画像の一時停止などの動作を容易に行うことができる。即ち、メモリコントローラ回路84により不揮発性メモリ85に格納された画像信号を常に画素部81へ送るようにすることで、ビデオデッキ等に録画することなくテレビ放送を自由に一時停止することが可能となる。

【0207】

また、本実施例では1フレーム分を格納する例を示したが、さらに数百フレーム、数千フレーム分といった画像情報を格納しうる程度まで不揮発性メモリ85のメモリ容量を増やすことができたならば、一時停止だけでなく、数秒若しくは数分前の画像を再生(リプレイ)することも可能となる。

【0208】

なお、本実施例の構成は、実施例1〜10のいずれの構成とも自由に組み合わせて実施することができる。

【0209】

〔実施例13〕

実施例1に示した作製工程例では、nチャネル型TFTのゲート電極を形成する前に、前もってn型不純物領域(b)を形成することが前提となっている。そして、p型不純物領域(a)、n型不純物領域(c)はともに自己整合的に形成されることが特徴となっている。

【0210】

しかしながら、本発明の効果を得るためには最終的な構造が図5(C)のような構造となっていれば良く、そこに至るプロセスに限定されるものではない。従って、不純物領域の形成順序は実施者が適宜変更して構わない。また、場合によってはp型不純物領域(a)やn型不純物領域(c)を、レジストマスクを用いて形成することも可能である。即ち、最終的に図5(C)に示したように、各回路に応じて異なる構造TFTが形成されるのであれば、あらゆる組み合わせの工程順序を採用しても構わない。

【0211】

〔実施例14〕

本発明は従来のMOSFET上に層間絶縁膜を形成し、その上にTFTを形成する際に用いることも可能である。即ち、三次元構造の半導体装置を実現することも可能である。

【0212】

また、基板としてSIMOX、Smart−Cut(SOITEC社の登録商標)、ELTRAN(キャノン株式会社の登録商標)などのSOI基板を用い、単結晶半導体薄膜を活性層として用いることも可能である。

【0213】

なお、本実施例の構成は、実施例1〜13のいずれの構成とも自由に組み合わせることが可能である。

【0214】

〔実施例15〕

本発明によって作製された液晶表示装置は様々な液晶材料を用いることが可能である。そのような材料として、TN液晶、PDLC(ポリマー分散型液晶)、FLC(強誘電性液晶)、AFLC(反強誘性電液晶)、またはFLCとAFLCの混合物(反強誘電性混合液晶)が挙げられる。

【0215】

例えば、「H.Furue et al.;Charakteristics and Drivng Scheme of Polymer-Stabilized Monostable FLCD Exhibiting Fast Response Time and High Contrast Ratio with Gray-Scale Capability,SID,1998」、「T.Yoshida et al.;A Full-Color Thresholdless Antiferroelectric LCD Exhibiting Wide Viewing Angle with Fast Response Time,841,SID97DIGEST,1997」、「S.Inui et al.;Thresholdless antiferroelectricity in liquid crystals and its application to displays,671-673,J.Mater.Chem.6(4),1996」、または米国特許第5,594,569号に開示された材料を用いることができる。

【0216】

特に、電場に対して透過率が連続的に変化する電気光学応答特性を示す無しきい値反強誘電性混合液晶(Thresholdless Antiferroelectric LCD:TL−AFLCと略記する)にはV字型(またはU字型)の電気光学応答特性を示すものがあり、その駆動電圧が約±2.5V程度(セル厚約1μm〜2μm)のものも見出されている。そのため、画素回路用の電源電圧が5〜8V程度で済む場合があり、制御回路と画素回路を同じ電源電圧で動作させる可能性が示唆されている。即ち、液晶表示装置全体の低消費電力化を図ることができる。

【0217】

また、強誘電性液晶や反強誘電性液晶はTN液晶に比べて応答速度が速いという利点をもつ。本発明で用いるようなTFTは非常に動作速度の速いTFTを実現しうるため、強誘電性液晶や反強誘電性液晶の応答速度の速さを十分に生かした画像応答速度の速い液晶表示装置を実現することが可能である。

【0218】

また、一般に、無しきい値反強誘電性混合液晶は自発分極が大きく、液晶自体の誘電率が高い。このため、無しきい値反強誘電性混合液晶を液晶表示装置に用いる場合には、画素に比較的大きな保持容量が必要となってくる。よって、自発分極が小さな無しきい値反強誘電性混合液晶を用いるのが好ましい。そういった意味で実施例1の図1で示した保持容量は小さい面積で大きな容量を蓄積することができるので好ましい。

【0219】

なお、本実施例の液晶表示装置をパーソナルコンピュータ等の電子機器の表示ディスプレイとして用いることが有効であることは言うまでもない。

【0220】

また、本実施例の構成は、実施例1〜14のいずれの構成とも自由に組み合わせることが可能である。

【0221】

〔実施例16〕

本発明はアクティブマトリクス型EL(エレクトロルミネッセンス)ディスプレイ(EL表示装置ともいう)に適用することも可能である。その例を図17に示す。

【0222】

図17は本実施例のアクティブマトリクス型ELディスプレイの回路図である。91は表示領域を表しており、その周辺にはX方向(ソース側)駆動回路92、Y方向(ゲート側)駆動回路93が設けられている。また、表示領域91の各画素は、スイッチング用TFT94、コンデンサ95、電流制御用TFT96、EL素子97を有し、スイッチング用TFT94にX方向信号線(ソース信号線)98a(または98b)、Y方向信号線(ゲート信号線)99a(または99b、99c)が接続される。また、電流制御用TFT96には、電源線100a、100bが接続される。

【0223】

なお、本実施例のアクティブマトリクス型ELディスプレイに対して、実施例1、4、6〜13のいずれの構成を組み合わせても良い。

【0224】

〔実施例17〕

本実施例では、本願発明を用いてEL(エレクトロルミネセンス)表示装置を作製した例について説明する。なお、図18(A)は本願発明のEL表示装置の上面図であり、図18(B)はその断面図である。

【0225】

図18(A)において、4001は基板、4002は画素部、4003はソース側駆動回路、4004はゲート側駆動回路であり、それぞれの駆動回路は配線4005を経てFPC(フレキシブルプリントサーキット)4006に至り、外部機器へと接続される。

【0226】

このとき、画素部4002、ソース側駆動回路4003及びゲート側駆動回路4004を囲むようにして第1シール材4101、カバー材4102、充填材4103及び第2シール材4104が設けられている。

【0227】

また、図18(B)は図18(A)をA−A’で切断した断面図に相当し、基板4001の上にソース側駆動回路4003に含まれる駆動TFT(但し、ここではnチャネル型TFTとpチャネル型TFTを図示している。)4201及び画素部4002に含まれる電流制御用TFT(EL素子への電流を制御するTFT)4202が形成されている。

【0228】

本実施例では、駆動TFT4201には図1のnチャネル型TFT302とpチャネル型TFT303と同じ構造のTFTが用いられ、電流制御用TFT4202には図1のpチャネル型TFT303と同じ構造のTFTが用いられる。また、同一基板上にはメモリ部が形成され、図1のメモリトランジスタ301と同じ構造のTFTが用いられる。また、画素部4002には電流制御用TFT4202のゲートに接続された保持容量(図示せず)が設けられる。

【0229】

駆動TFT4201及び画素TFT4202の上には樹脂材料でなる層間絶縁膜(平坦化膜)4301が形成され、その上に画素TFT4202のドレインと電気的に接続する画素電極(陽極)4302が形成される。画素電極4302としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物または酸化インジウムと酸化亜鉛との化合物を用いることができる。

【0230】

そして、画素電極4302の上には絶縁膜4303が形成され、絶縁膜4303は画素電極4302の上に開口部が形成されている。この開口部において、画素電極4302の上にはEL(エレクトロルミネッセンス)層4304が形成される。EL層4304は公知の有機EL材料または無機EL材料を用いることができる。また、有機EL材料には低分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

【0231】

EL層4304の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。また、EL層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。

【0232】

EL層4304の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極4305が形成される。また、陰極4305とEL層4304の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空中で両者を連続成膜するか、EL層4304を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極4305を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。

【0233】

そして陰極4305は4306で示される領域において配線4005に電気的に接続される。配線4005は陰極4305に所定の電圧を与えるための配線であり、異方導電性フィルム4307を介してFPC4006に電気的に接続される。

【0234】

以上のようにして、画素電極(陽極)4302、EL層4304及び陰極4305からなるEL素子が形成される。このEL素子は、第1シール材4101及び第1シール材4101によって基板4001に貼り合わされたカバー材4102で囲まれ、充填材4103により封入されている。

【0235】

カバー材4102としては、ガラス材、金属材(代表的にはステンレス材)、セラミックス材、プラスチック材(プラスチックフィルムも含む)を用いることができる。プラスチック材としては、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

【0236】

但し、EL素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

【0237】

また、充填材4103としては紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材4103の内部に吸湿性物質(好ましくは酸化バリウム)を設けておくとEL素子の劣化を抑制できる。

【0238】

また、充填材4103の中にスペーサを含有させてもよい。このとき、スペーサを酸化バリウムで形成すればスペーサ自体に吸湿性をもたせることが可能である。また、スペーサを設けた場合、スペーサからの圧力を緩和するバッファ層として陰極4305上に樹脂膜を設けることも有効である。

【0239】

また、配線4005は異方導電性フィルム4307を介してFPC4006に電気的に接続される。配線4005は画素部4002、ソース側駆動回路4003及びゲート側駆動回路4004に送られる信号をFPC4006に伝え、FPC4006により外部機器と電気的に接続される。

【0240】

また、本実施例では第1シール材4101の露呈部及びFPC4006の一部を覆うように第2シール材4104を設け、EL素子を徹底的に外気から遮断する構造となっている。こうして図18(B)の断面構造を有するEL表示装置となる。なお、本実施例のEL表示装置は実施例1、4、6〜13、16のいずれの構成を組み合わせて作製しても構わない。

【0241】

ここで画素部のさらに詳細な断面構造を図19に、上面構造を図20(A)に、回路図を図20(B)に示す。図19、図20(A)及び図20(B)では共通の符号を用いるので互いに参照すれば良い。

【0242】

図19において、基板4401上に設けられたスイッチング用TFT4402は図1の画素部に設けられたnチャネル型TFT304を用いて形成される。従って、構造の説明はnチャネル型TFT304の説明を参照すれば良い。また、4403で示される配線は、スイッチング用TFT4402のゲート電極4404a、4404bを電気的に接続するゲート配線である。

【0243】

なお、本実施例ではチャネル形成領域が二つ形成されるダブルゲート構造としているが、チャネル形成領域が一つ形成されるシングルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。

【0244】

また、スイッチング用TFT4402のドレイン配線4405は電流制御用TFT4406のゲート電極4407に電気的に接続されている。なお、電流制御用TFT4406は図1のpチャネル型TFT303を用いて形成される。従って、構造の説明はpチャネル型TFT303の説明を参照すれば良い。なお、本実施例ではシングルゲート構造としているが、ダブルゲート構造もしくはトリプルゲート構造であっても良い。

【0245】

スイッチング用TFT4402及び電流制御用TFT4406の上には第1パッシベーション膜4408が設けられ、その上に樹脂からなる平坦化膜4409が形成される。平坦化膜4409を用いてTFTによる段差を平坦化することは非常に重要である。後に形成されるEL層は非常に薄いため、段差が存在することによって発光不良を起こす場合がある。従って、EL層をできるだけ平坦面に形成しうるように画素電極を形成する前に平坦化しておくことが望ましい。

【0246】

また、4410は透明導電膜からなる画素電極(EL素子の陽極)であり、電流制御用TFT4406のドレイン配線4411に電気的に接続される。画素電極4410としては酸化インジウムと酸化スズとの化合物もしくは酸化インジウムと酸化亜鉛との化合物からなる導電膜を用いることができる。

【0247】

画素電極4410の上にはEL層4412が形成される。なお、図19では一画素しか図示していないが、本実施例ではR(赤)、G(緑)、B(青)の各色に対応したEL層を作り分けている。また、本実施例では蒸着法により低分子系有機EL材料を形成している。具体的には、正孔注入層として20nm厚の銅フタロシアニン(CuPc)膜を設け、その上に発光層として70nm厚のトリス−8−キノリノラトアルミニウム錯体(Alq3)膜を設けた積層構造としている。Alq3に蛍光色素を添加することで発光色を制御することができる。

【0248】

但し、以上の例はEL層として用いることのできる有機EL材料の一例であって、これに限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わせてEL層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い。例えば、本実施例では低分子系有機EL材料をEL層として用いる例を示したが、高分子系有機EL材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪素等の無機材料を用いることも可能である。これらの有機EL材料や無機材料は公知の材料を用いることができる。

【0249】

次に、EL層4412の上には遮光性の導電膜からなる陰極4413が設けられる。本実施例の場合、遮光性の導電膜としてアルミニウムとリチウムとの合金膜を用いる。勿論、公知のMgAg膜(マグネシウムと銀との合金膜)を用いても良い。陰極材料としては、周期表の1族もしくは2族に属する元素からなる導電膜もしくはそれらの元素を添加した導電膜を用いれば良い。

【0250】

この陰極4413まで形成された時点でEL素子4414が完成する。なお、ここでいうEL素子4414は、画素電極(陽極)4410、EL層4412及び陰極4413で形成されたコンデンサを指す。

【0251】

次に、本実施例における画素の上面構造を図20(A)を用いて説明する。スイッチング用TFT4402のソースはソース配線4415に接続され、ドレインはドレイン配線4405に接続される。また、ドレイン配線4405は電流制御用TFT4406のゲート電極4407に電気的に接続される。また、電流制御用TFT4406のソースは電流供給線4416に電気的に接続され、ドレインはドレイン配線4417に電気的に接続される。また、ドレイン配線4417は点線で示される画素電極(陽極)4418に電気的に接続される。

【0252】

このとき、4419で示される領域には保持容量が形成される。保持容量4419は、電流供給線4416と電気的に接続された半導体膜4420、ゲート絶縁膜と同一層の絶縁膜(図示せず)及びゲート電極4407との間で形成される。また、ゲート電極4407、第1層間絶縁膜と同一の層(図示せず)及び電流供給線4416で形成される容量も保持容量として用いることが可能である。

【0253】

なお、本実施例の構成は、実施例1、4、6〜13、16のいずれの構成とも自由に組み合わせて実施することが可能である。

【0254】

〔実施例18〕

本実施例では、実施例17とは異なる画素構造を有したEL表示装置について説明する。説明には図21を用いる。なお、図19と同一の符号が付してある部分については実施例17の説明を参照すれば良い。

【0255】

図21では電流制御用TFT4501として図1のnチャネル型TFT302と同一構造のTFTを用いる。勿論、電流制御用TFT4501のゲート電極4502はスイッチング用TFT4402のドレイン配線4405に接続されている。また、電流制御用TFT4501のドレイン配線4503は画素電極4504に電気的に接続されている。

【0256】

EL素子にかかる電圧が10V以上になるとホットキャリア効果による劣化が顕著になるため、電流制御用TFT4501として図1のnチャネル型TFT302と同一構造のTFTを用いることは有効である。また、EL素子にかかる電圧が10V以下であればホットキャリア効果による劣化はさほど問題とならないのでnチャネル型TFT302からLDD領域114を省略した構造のTFTを用いても良い。

【0257】

本実施例では、画素電極4504がEL素子の陰極として機能し、遮光性の導電膜を用いて形成する。具体的には、アルミニウムとリチウムとの合金膜を用いるが、周期表の1族もしくは2族に属する元素からなる導電膜もしくはそれらの元素を添加した導電膜を用いれば良い。

【0258】

画素電極4504の上にはEL層4505が形成される。なお、図21では一画素しか図示していないが、本実施例ではG(緑)に対応したEL層を蒸着法及び塗布法(好ましくはスピンコーティング法)により形成している。具体的には、電子注入層として20nm厚のフッ化リチウム(LiF)膜を設け、その上に発光層として70nm厚のPPV(ポリパラフェニレンビニレン)膜を設けた積層構造としている。

【0259】

次に、EL層4505の上には透明導電膜からなる陽極4506が設けられる。本実施例の場合、透明導電膜として酸化インジウムと酸化スズとの化合物もしくは酸化インジウムと酸化亜鉛との化合物からなる導電膜を用いる。

【0260】

この陽極4506まで形成された時点でEL素子4507が完成する。なお、ここでいうEL素子4507は、画素電極(陰極)4504、EL層4505及び陽極4506で形成されたコンデンサを指す。

【0261】

なお、本実施例の電流制御用TFT4501はゲート電極4502とLDD領域4509a、4509bとの間にゲート容量と呼ばれる寄生容量を形成する。このゲート容量を調節することで図20(A)、(B)に示した保持容量4418と同等の機能を持たせることも可能である。特に、EL表示装置をデジタル駆動方式で動作させる場合においては、保持容量のキャパシタンスがアナログ駆動方式で動作させる場合よりも小さくて済むため、ゲート容量で保持容量を代用しうる。

【0262】

なお、本実施例の構成は、実施例1、4、6〜13、16のいずれの構成とも自由に組み合わせて実施することが可能である。

【0263】

〔実施例19〕

本実施例では、実施例17もしくは実施例18に示したEL表示装置の画素構造の例を図22(A)〜(C)に示す。なお、本実施例において、4601はスイッチング用TFT4602のソース配線、4603はスイッチング用TFT4602のゲート配線、4604は電流制御用TFT、4605はコンデンサ、4606、4608は電流供給線、4607はEL素子とする。

【0264】

図22(A)は、二つの画素間で電流供給線4606を共通とした場合の例である。即ち、二つの画素が電流供給線4606を中心に線対称となるように形成されている点に特徴がある。この場合、電流供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0265】

また、図22(B)は、電流供給線4608をゲート配線4603と平行に設けた場合の例である。なお、図22(B)では電流供給線4608とゲート配線4603とが重ならないように設けた構造となっているが、両者が異なる層に形成される配線であれば、絶縁膜を介して重なるように設けることもできる。この場合、電流供給線4608とゲート配線4603とで専有面積を共有させることができるため、画素部をさらに高精細化することができる。

【0266】

また、図22(C)は、図22(B)の構造と同様に電流供給線4608をゲート配線4603と平行に設け、さらに、二つの画素を電流供給線4608を中心に線対称となるように形成する点に特徴がある。また、電流供給線4608をゲート配線4603のいずれか一方と重なるように設けることも有効である。この場合、電流供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0267】

〔実施例20〕

本実施例では、実施例17もしくは実施例18に示したEL表示装置の画素構造の例を図23(A)、(B)に示す。なお、本実施例において、4701はスイッチング用TFT4702のソース配線、4703はスイッチング用TFT4702のゲート配線、4704は電流制御用TFT、4705はコンデンサ(省略することも可能)、4706は電流供給線、、4707は電源制御用TFT、4708は電源制御用ゲート配線、4709はEL素子とする。電源制御用TFT4707の動作については特願平11−341272号を参照すると良い。

【0268】

また、本実施例では電源制御用TFT4707を電流制御用TFT4704とEL素子4708との間に設けているが、電源制御用TFT4707とEL素子4708との間に電流制御用TFT4704が設けられた構造としても良い。また、電源制御用TFT4707は電流制御用TFT4704と同一構造とするか、同一の活性層で直列させて形成するのが好ましい。

【0269】

また、図23(A)は、二つの画素間で電流供給線4706を共通とした場合の例である。即ち、二つの画素が電流供給線4706を中心に線対称となるように形成されている点に特徴がある。この場合、電流供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0270】

また、図23(B)は、ゲート配線4703と平行に電流供給線4710を設け、ソース配線4701と平行に電源制御用ゲート配線4711を設けた場合の例である。なお、図23(B)では電流供給線4710とゲート配線4703とが重ならないように設けた構造となっているが、両者が異なる層に形成される配線であれば、絶縁膜を介して重なるように設けることもできる。この場合、電流供給線4710とゲート配線4703とで専有面積を共有させることができるため、画素部をさらに高精細化することができる。

【0271】

〔実施例21〕

本実施例では、実施例17もしくは実施例18に示したEL表示装置の画素構造の例を図24(A)、(B)に示す。なお、本実施例において、4801はスイッチング用TFT4802のソース配線、4803はスイッチング用TFT4802のゲート配線、4804は電流制御用TFT、4805はコンデンサ(省略することも可能)、4806は電流供給線、、4807は消去用TFT、4808は消去用ゲート配線、4809はEL素子とする。消去用TFT4807の動作については特願平11−338786号を参照すると良い。

【0272】

消去用TFT4807のドレインは電流制御用TFT4804のゲートに接続され、電流制御用TFT4804のゲート電圧を強制的に変化させることができるようになっている。なお、消去用TFT4807はnチャネル型TFTとしてもpチャネル型TFTとしても良いが、オフ電流を小さくできるようにスイッチング用TFT4802と同一構造とすることが好ましい。

【0273】

また、図24(A)は、二つの画素間で電流供給線4806を共通とした場合の例である。即ち、二つの画素が電流供給線4806を中心に線対称となるように形成されている点に特徴がある。この場合、電流供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0274】

また、図24(B)は、ゲート配線4803と平行に電流供給線4810を設け、ソース配線4801と平行に消去用ゲート配線4811を設けた場合の例である。なお、図24(B)では電流供給線4810とゲート配線4803とが重ならないように設けた構造となっているが、両者が異なる層に形成される配線であれば、絶縁膜を介して重なるように設けることもできる。この場合、電流供給線4810とゲート配線4803とで専有面積を共有させることができるため、画素部をさらに高精細化することができる。

【0275】

〔実施例22〕

本発明のEL表示装置は画素内にいくつのTFTを設けた構造としても良い。実施例20、21ではTFTを三つ設けた例を示しているが、四つ乃至六つのTFTを設けても構わない。本発明はEL表示装置の画素構造に限定されずに実施することが可能である。

【0276】

〔実施例23〕

本願発明の電気光学装置や半導体回路は電気器具の表示部や信号処理回路として用いることができる。そのような電気器具としては、ビデオカメラ、デジタルカメラ、プロジェクター、プロジェクションTV、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置などが挙げられる。それら電気器具の具体例を図25〜27に示す。

【0277】

図25(A)は携帯電話であり、本体2001、音声出力部2002、音声入力部2003、表示部2004、操作スイッチ2005、アンテナ2006で構成される。本願発明の電気光学装置は表示部2004に、本願発明の半導体回路は音声出力部2002、音声入力部2003またはCPUやメモリ等に用いることができる。

【0278】

図25(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本願発明の電気光学装置は表示部2102に、本願発明の半導体回路は音声入力部2103またはCPUやメモリ等に用いることができる。

【0279】

図25(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示部2205で構成される。本願発明の電気光学装置は表示部2205に、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0280】

図25(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アーム部2303で構成される。本願発明の電気光学装置は表示部2302に、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0281】

図25(E)はリアプロジェクター(プロジェクションTV)であり、本体2401、光源2402、液晶表示装置2403、偏光ビームスプリッタ2404、リフレクター2405、2406、スクリーン2407で構成される。本発明は液晶表示装置2403に用いることができ、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0282】

図25(F)はフロントプロジェクターであり、本体2501、光源2502、液晶表示装置2503、光学系2504、スクリーン2505で構成される。本発明は液晶表示装置2503に用いることができ、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0283】

図26(A)はパーソナルコンピュータであり、本体2601、映像入力部2602、表示部2603、キーボード2604等を含む。本願発明の電気光学装置は表示部2603に、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0284】

図26(B)は電子遊戯機器(ゲーム機器)であり、本体2701、記録媒体2702、表示部2703及びコントローラー2704を含む。この電子遊技機器から出力された音声や映像は筐体2705及び表示部2706を含む表示ディスプレイにて再生される。コントローラー2704と本体2701との間の通信手段または電子遊技機器と表示ディスプレイとの間の通信手段は、有線通信、無線通信もしくは光通信が使える。本実施例では赤外線をセンサ部2707、2708で検知する構成となっている。本願発明の電気光学装置は表示部2703、2706に、本願発明の半導体回路はCPUやメモリ等に用いることができる。

【0285】

図26(C)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤー(画像再生装置)であり、本体2801、表示部2802、スピーカ部2803、記録媒体2804及び操作スイッチ2805を含む。なお、この画像再生装置は記録媒体としてDVD(Digital VersatileDisc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本願発明の電気光学装置は表示部2802やCPUやメモリ等に用いることができる。

【0286】

図26(D)はデジタルカメラであり、本体2901、表示部2902、接眼部2903、操作スイッチ2904、受像部(図示せず)を含む。本願発明の電気光学装置は表示部2902やCPUやメモリ等に用いることができる。

【0287】

なお、図25(E)のリアプロジェクターや図25(F)のフロントプロジェクターに用いることのできる光学エンジンについての詳細な説明を図27に示す。なお、図27(A)は光学エンジンであり、図27(B)は光学エンジンに内蔵される光源光学系である。

【0288】

図27(A)に示す光学エンジンは、光源光学系3001、ミラー3002、3005〜3007、ダイクロイックミラー3003、3004、光学レンズ3008a〜3008c、プリズム3011、液晶表示装置3010、投射光学系3012を含む。投射光学系3012は、投射レンズを備えた光学系である。本実施例は液晶表示装置3010を三つ使用する三板式の例を示したが、単板式であってもよい。また、図27(A)中において矢印で示した光路には、光学レンズ、偏光機能を有するフィルム、位相差を調節するためのフィルムもしくはIRフィルム等を設けてもよい。

【0289】

また、図27(B)に示すように、光源光学系3001は、光源3013、3014、合成プリズム3015、コリメータレンズ3016、3020、レンズアレイ3017、3018、偏光変換素子3019を含む。なお、図27(B)に示した光源光学系は光源を2つ用いたが、一つでも良いし、三つ以上としてもよい。また、光源光学系の光路のどこかに、光学レンズ、偏光機能を有するフィルム、位相差を調節するフィルムもしくはIRフィルム等を設けてもよい。

【0290】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電気器具に適用することが可能である。また、本実施例の電気器具は実施例1〜22の構成を必要に応じて組み合わせることで実現できる。

【0291】

【発明の効果】

本願発明を用いることで同一基板上に、回路又は素子が要求する仕様に応じて適切な性能のTFTを配置することが可能となり、電気光学装置の動作性能や信頼性を大幅に向上させることができる。

【0292】

また、同一基板上に画素部、駆動回路部に加えてメモリ部を設けることが可能となるため、電気光学装置の性能を大幅に向上しうる。さらに、以上のような電気光学装置をディスプレイ(表示部)として有する電子機器は用途が大きく広がり、且つ、高い動作性能と高い信頼性を実現しうる。

【図面の簡単な説明】

【図1】 画素部、駆動回路及びメモリ部の構成を示す図。

【図2】 画素部、駆動回路及びメモリ部の作製工程を示す図。

【図3】 画素部、駆動回路及びメモリ部の作製工程を示す図。

【図4】 画素部、駆動回路及びメモリ部の作製工程を示す図。

【図5】 画素部、駆動回路及びメモリ部の作製工程を示す図。

【図6】 アクティブマトリクス型液晶表示装置の断面構造図。

【図7】 アクティブマトリクス型液晶表示装置の斜視図。

【図8】 駆動回路を示す図。

【図9】 画素部を示す図。

【図10】 画素部、駆動回路及びメモリ部の構成を示す図。

【図11】 画素部を示す図。

【図12】 画素部、駆動回路及びメモリ部の構成を示す図。

【図13】 フラッシュメモリの構成を示す図。

【図14】 フラッシュメモリの構成を示す図。

【図15】 アクティブマトリクス基板のブロック図。

【図16】 アクティブマトリクス基板のブロック図。

【図17】 アクティブマトリクス型EL表示装置の構成を示す図。

【図18】 EL表示装置の上面構造及び断面構造を示す図。

【図19】 EL表示装置の断面構造を示す図。

【図20】 EL表示装置の画素部の上面構造を示す図。

【図21】 EL表示装置の断面構造を示す図。

【図22】 EL表示装置の画素部の回路構成を示す図。

【図23】 EL表示装置の画素部の回路構成を示す図。

【図24】 EL表示装置の回路構成を示す図。

【図25】 電気器具の一例を示す図。

【図26】 電気器具の一例を示す図。

【図27】 光学エンジンの構成を示す図。[0001]

BACKGROUND OF THE INVENTION

The present invention relates to an electro-optical device formed by fabricating a semiconductor element (an element using a semiconductor thin film) on a substrate and an electronic apparatus (electronic device) having the electro-optical device. The present invention relates to a liquid crystal display device or an EL display device in which a thin film transistor (hereinafter referred to as TFT) is typically formed on a substrate, and an electronic apparatus having such a display device as a display (display unit).

[0002]

[Prior art]

In recent years, a technology for forming a TFT on a substrate has greatly advanced, and application development to an active matrix display device has been advanced. In particular, a TFT using a polysilicon film has a higher field effect mobility (also referred to as mobility) than a TFT using a conventional amorphous silicon film, and thus can operate at high speed. For this reason, it is possible to control a pixel, which has been conventionally performed by a drive circuit outside the substrate, with a drive circuit formed on the same substrate as the pixel.

[0003]

Such an active matrix display device has various advantages such as a reduction in manufacturing cost, a reduction in size of the display device, an increase in yield, and a reduction in throughput by forming various circuits and elements on the same substrate. It is attracting attention as.

[0004]